包含到有源区支柱的含金属互连件的集成式组合件以及形成集成式组合件的方法

文献发布时间:2023-06-19 11:14:36

技术领域

包含到有源区支柱的含金属互连件的集成式组合件以及形成集成式组合件的方法。

背景技术

存储器是一种类型的集成电路,且在计算机系统中使用以存储数据。实例存储器为DRAM(动态随机存取存储器)。DRAM单元可各自包括晶体管与电容器组合。DRAM单元可布置在阵列中;其中字线沿着阵列的行延伸,且数字线沿着阵列的列延伸。字线可与存储器单元的晶体管耦合。每一存储器单元可经由字线中的一个与数字线中的一个的组合来唯一地寻址。

需要开发用于制造高度集成的DRAM的新方法,且需要开发以此些方法制造的新架构。

附图说明

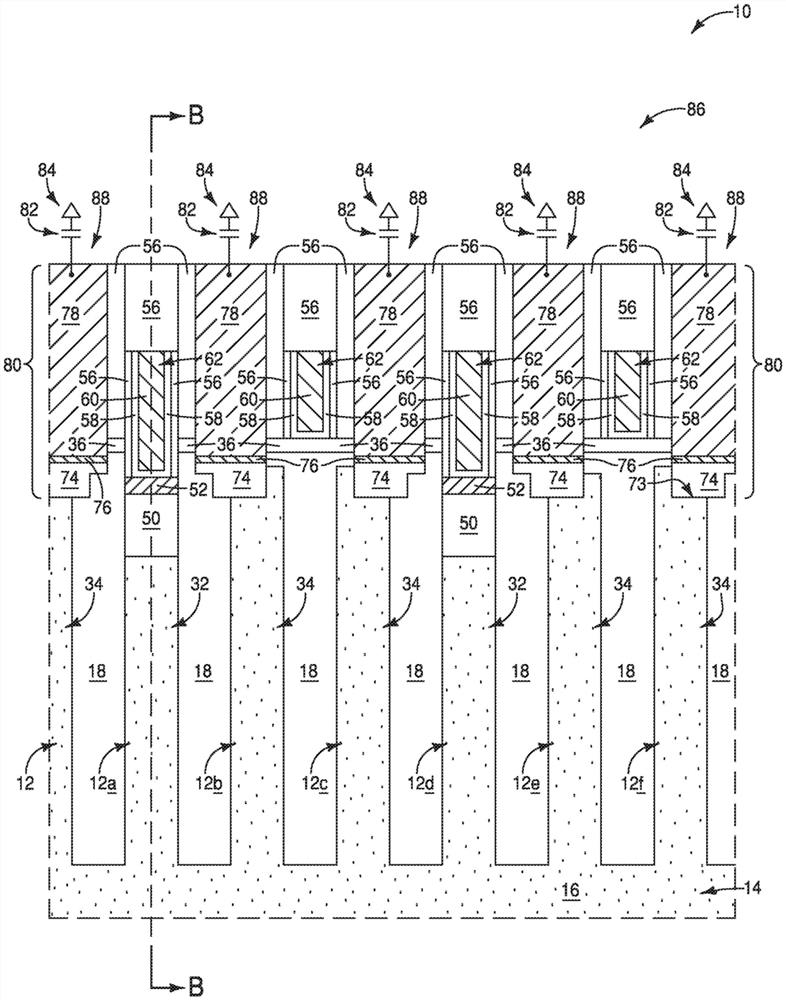

图1-1C是形成实例集成式组合件的实例方法的实例初始处理阶段处的实例构造的区的图解视图。图1是图解俯视图;图1C是图解横截面俯视图;且图1A和1B是图解横截面侧视图。图1A的视图是沿着图1、1B和1C的线A-A。图1B的视图是沿着图1、1A和1C的线B-B。图1C的视图是沿着图1A和1B的线C-C。

图2-2B是在图1-1C的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图2是图解俯视图;图2A是沿着图2和2B的线A-A的图解横截面侧视图;且图2B是沿着图2和2A的线B-B的图解横截面侧视图。

图3-3B是在图2-2B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图3是图解俯视图;图3A是沿着图3和3B的线A-A的图解横截面侧视图;且图3B是沿着图3和3A的线B-B的图解横截面侧视图。

图4-4B是在图3-3B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图4是图解俯视图;图4A是沿着图4和4B的线A-A的图解横截面侧视图;且图4B是沿着图4和4A的线B-B的图解横截面侧视图。

图5-5B是在图4-4B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图5是图解俯视图;图5A是沿着图5和5B的线A-A的图解横截面侧视图;且图5B是沿着图5和5A的线B-B的图解横截面侧视图。

图6-6B是在图5-5B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图6是图解俯视图;图6A是沿着图6和6B的线A-A的图解横截面侧视图;且图6B是沿着图6和6A的线B-B的图解横截面侧视图。

图7-7B是在图6-6B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图7是图解俯视图;图7A是沿着图7和7B的线A-A的图解横截面侧视图;且图7B是沿着图7和7A的线B-B的图解横截面侧视图。

图8-8B是在图7-7B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图8是图解俯视图;图8A是沿着图8和8B的线A-A的图解横截面侧视图;且图8B是沿着图8和8A的线B-B的图解横截面侧视图。

图9-9B是在图8-8B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图9是图解俯视图;图9A是沿着图9和9B的线A-A的图解横截面侧视图;且图9B是沿着图9和9A的线B-B的图解横截面侧视图。

图10-10B是在图9-9B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图10是图解俯视图;图10A是沿着图10和10B的线A-A的图解横截面侧视图;且图10B是沿着图10和10A的线B-B的图解横截面侧视图。

图11-11B是在图10-10B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图11是图解俯视图;图11A是沿着图11和11B的线A-A的图解横截面侧视图;且图11B是沿着图11和11A的线B-B的图解横截面侧视图。

图12-12B是在图11-11B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图12是图解俯视图;图12A是沿着图12和12B的线A-A的图解横截面侧视图;且图12B是沿着图12和12A的线B-B的图解横截面侧视图。

图13-13B是在图12-12B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图13是图解俯视图;图13A是沿着图13和13B的线A-A的图解横截面侧视图;且图13B是沿着图13和13A的线B-B的图解横截面侧视图。

图14-14B是在图13-13B的处理阶段之后的实例处理阶段处图1-1C的实例构造的区的图解视图。图14是图解俯视图;图14A是沿着图14和14B的线A-A的图解横截面侧视图;且图14B是沿着图14和14A的线B-B的图解横截面侧视图。

图15是实例存储器阵列的区的图解示意图。

图16-19是在可跟随图12A的处理阶段的实例方法的实例处理阶段处沿着与图12A相同的横截面的图解横截面侧视图。

具体实施方式

一些实施例包含形成到数字线接触区的连接的方法和/或形成到存储元件接触区的连接的方法。所述连接可包含具有金属硅化物上金属的互连件;且在一些实施例中,所述互连件可包含硅化钴上钌。互连件可直接接触数字线接触区和/或存储元件接触区的单晶硅。一些实施例包含具有导电互连件的集成式组合件,所述导电互连件包含硅化钴上的含金属材料(例如,铜、钼、钯、铂、钌、钨、钛等中的一或多个)。下文参考图1-19描述实例实施例。

参看图1-1C,展示实例集成式组合件10的一部分。此些组合件可利用任何合适的方法形成。组合件10包含从半导体基底14向上延伸的多个有源区12(在本文中也被称为有源区支柱)。一些有源区12标记为12a-f,使得其可彼此区分以及相对于其它有源区进行区分。所有有源区12可彼此大体上相同;其中术语“大体上相同”表示在合理的制造和测量容差内相同。有源区12在图1中以虚线(幻影图)示出以便指示它们在其它材料下方。

有源区12和半导体基底14包括半导体材料16。此半导体材料可包括任何合适的组成物;且在一些实施例中可包括硅、锗、III/V半导体材料(例如,磷化镓)、半导体氧化物等中的一或多个,基本上由它们组成,或由它们组成;其中术语III/V半导体材料指代包括选自周期表的族III和V的元素的半导体材料(其中族III和V为旧式命名法,且现被称作族13和15)。在一些实施例中,半导体材料16可包括经适当掺杂的硅,基本上由经适当掺杂的硅组成,或由经适当掺杂的硅组成。硅可呈任何合适的形式;且在一些实施例中可以是单晶硅。在一些实施例中,有源区的半导体材料16可被称为有源区材料。

基底14可被称为半导体衬底。术语“半导体衬底”意指包括半导体材料的任何构造,包含(但不限于)整体半导体材料,例如(单独或在包括其它材料的组合件中的)半导体晶片,及(单独或在包括其它材料的组合件中的)半导体材料层。术语“衬底”指代任何支撑结构,包含(但不限于)上文描述的半导体衬底。

有源区12通过包括绝缘材料18和28的介入区彼此间隔开。绝缘材料18可包括任何合适的组成物或组成物组合;且在一些实施例中,可包括二氧化硅、基本上由二氧化硅组成,或由二氧化硅组成。绝缘材料28可包括任何合适的组成物;且在一些实施例中可包括二氧化硅和/或氮化硅、基本上由二氧化硅和/或氮化硅组成,或由二氧化硅和/或氮化硅组成。绝缘材料28可以是与绝缘材料18相同的组成物,或可以是与绝缘材料18不同的组成物。

字线(即,存取线)20沿着第一方向(由图1和1C中展示的x轴表示)延伸。第一方向可对应于存储器阵列的行方向。字线20在图1中以虚线(幻影图)示出以便指示它们在其它材料下方。数字线(即,感测线、位线)将以本文中所描述的处理形成,且此些数字线将沿着可对应于存储器阵列的列方向的第二方向(由y轴表示)延伸。字线邻近于有源区支柱12。第二方向(即,列方向)可正交于第一方向(即,行方向),或可只是与第一方向交叉。

字线20包括导电材料24。导电材料24可包括任何合适的导电组成物;例如各种金属(例如,钛、钨、钴、镍、铂、钌等)、含金属组成物(例如,金属硅化物、金属氮化物、金属碳化物等),和/或导电掺杂半导体材料(例如,导电掺杂硅、导电掺杂锗等)中的一或多个。

绝缘材料28在字线20上方。

栅极介电材料30在字线20的下部区周围延伸,且在字线和有源区12之间。栅极介电材料30可包括任何合适的组成物;且在一些实施例中可包括二氧化硅,基本上由二氧化硅组成,或由二氧化硅组成。

字线20包括沿着有源区12的晶体管栅极。有源区(即,有源区支柱)12中的每一个可被视为在一对存储元件接触区34之间包括数字线接触区32(如图1A和1C中所展示)。在一些实施例中,区32和34可一般被称作接触区。

字线20包括晶体管栅极,其以选通方式将存储元件接触区34与数字线接触区32耦合。数字线接触区32和存储元件接触区34在图1C中指示以辅助读者理解字线20相对于数字线接触区32和存储元件接触区34的相对位置。然而,应理解,数字线接触区32和存储元件接触区34实际上相比于图1C的截面位于有源区上方更高处,如图1A和1B中指示。

数字线接触区32最终与数字线耦合,且存储元件接触区34最终与存储元件(例如,电容器)耦合,如下文更详细地描述。

在一些实施例中,材料16、18、24、28和30可被视为形成构造22。大片第一材料26形成为跨构造22延伸。在一些实施例中,第一材料26可包括氮化硅,基本上由氮化硅组成,或由氮化硅组成。

在所展示的实施例中,第一材料在绝缘材料36上方,绝缘材料36又在构造22上方。绝缘材料36可包括任何合适的组成物;包含例如二氧化硅、氧化铝、氧化铪、氧化锆等中的一或多个。

参看图2-2B,形成开口38以延伸到材料26中。可利用掩模(未图示)和任何合适的蚀刻使开口38图案化。举例来说,如果材料26包括氮化硅,则蚀刻可利用磷酸。

图案化材料26可被称为图案化模具40;其中此图案化模具具有延伸穿过其中的开口38。

尽管在俯视图中开口38展示为圆形,但应理解,在其它实施例中开口可具有其它形状。举例来说,在一些实例实施例中,在俯视图中,开口可为椭圆形、正方形、矩形、多边形等。开口38可具有任何合适的尺寸,且在一些实施例中可具有宽度W(例如,所示出的圆形开口的直径),在至少约2纳米(nm)到小于或等于约15nm的范围内;且在一些实施例中,此宽度可小于或等于约10nm。

参看图3-3B,开口38延伸穿过材料36,并进入构造22。开口38与数字线接触区32对准,且在所展示的实施例中延伸到数字线接触区32的半导体材料16中。开口38可利用任何合适的蚀刻延伸到半导体材料16中。举例来说,在一些实施例中,半导体材料16可包括硅(例如,单晶硅),且开口可使用利用硝酸、氢氧化钾和四甲基铵氢氧化物中的一或多种的蚀刻延伸到半导体材料中。

参看图4-4B,在开口38延伸到半导体材料12中之后,牺牲材料42形成于此些开口内。牺牲材料42可包括任何合适的组成物;且在一些实施例中可包括一或多种含碳聚合物,基本上由一或多种含碳聚合物组成,或由一或多种含碳聚合物组成。此些聚合物可包含碳和氢;且还可包含一或多个杂原子(例如,氮、氧等)。实例聚合物可以是传统地用作底部抗反射组成物(bottom antireflective composition,BARC)的组成物、用作下层(underlayer,UL)的组成物等。

在一些实施例中,聚合物42可初始跨组合件10的表面散布以填充开口38,且接着聚合物可利用合适的烘焙固化。可接着利用任何合适的处理移除过多的聚合物。在所示的实施例中,组合件10具有跨材料42和26延伸的平坦化上表面43。此平坦化表面可通过利用化学机械抛光(CMP)来移除过多的聚合物42而形成。

参看图5-5B,在图案化模具40内形成沟槽44-47。沟槽沿着由y轴表示的第二方向延伸。沟槽44-47具有宽度W

沟槽44-47可利用任何合适的处理形成;且在一些实施例中可利用材料26相对于材料36的选择性蚀刻(例如,氮化硅相对于二氧化硅的选择性蚀刻)形成。出于理解本公开和所附权利要求书的目的,如果一种材料比另一种材料更快地被移除,则该材料应被理解为相对于该另一种材料“选择性地移除”;这可包含(但不限于)一种材料相对于另一种材料为100%选择性的条件。

可在用于形成沟槽44-47的实例蚀刻中使用磷酸。在所示的实施例中,在形成沟槽44-47期间移除聚合材料42(图4-4B)以重新打开开口38;其中重新打开的开口位于沟槽44-47的底部处。在一些实施例中,利用蚀刻(例如,利用磷酸的蚀刻)继之以移除有机残余物的清洁来形成沟槽44-47,且牺牲材料42包括在此清洁期间移除的含碳聚合物。实例清洁可利用氨和过氧化氢。

数字线接触区32具有沿着重新打开的开口38的底部的暴露表面49。

参看图6-6B,硅(或其它合适的半导体材料)50从半导体材料16的暴露表面49外延地生长。外延生长的硅可形成到任何合适的厚度。在所示的实施例中,硅50生长到某一厚度使得其保持在图案化模具40的材料26下方。在其它实施例中,硅50可生长为足够厚而延伸到图案化模具40中。在一些实施例中,外延生长的硅50可省略。在一些实施例中,外延生长的硅50可用沉积在表面49上方的多晶硅替代。然而,在一些应用中,可能有利的是,利用外延生长的硅50代替多晶硅,因为外延生长的硅可提供比多晶硅可实现的更低的电阻和更好的均匀度,尤其是在高度集成的电路的严格界限内。外延生长的硅50可用一或多种合适的掺杂剂(例如,磷、硼等)进行导电掺杂。

导电含金属材料52形成于外延生长的硅50上且直接抵靠外延生长的硅50。在一些实施例中,含金属材料52可包括金属硅化物。举例来说,在一些实例实施例中,含金属材料52可包括硅化钴,基本上由硅化钴组成,或由硅化钴组成。在一些实施例中,含金属材料52可被视为直接抵靠数字线接触区32的硅;而与材料52直接抵靠外延生长的材料50还是直接抵靠半导体材料16无关。

间隔物54任选地形成为邻近于沟槽44-47的侧壁。间隔物包括绝缘材料56,其可被称为绝缘间隔物材料。材料56可包括任何合适的组成物;且在一些实施例中可包括二氧化硅、经掺杂碳的二氧化硅(SiOC,其中公式指示主要成分而非特定化学计量)、氮氧化硅(SiON,其中公式指示主要成分而非特定化学计量)等中的一或多种,基本上由它们组成,或由它们组成。在一些应用中,材料56可为低k(即,可具有小于二氧化硅的介电常数的介电常数)。低k材料的优点可以是,其可在后续蚀刻和清洁期间(例如,湿清洁期间)提供高选择性,尤其是在可避免干式蚀刻等离子体损坏的情况下。在一些实施例中,图案化模具40的材料26可被称为具有第一组成物的第一材料,且间隔物54的材料56可被称为具有不同于第一组成物的第二组成物的第二材料。

间隔物54可在硅50和金属硅化物52之后形成(如所展示);或者可在硅50和金属硅化物52之前形成,在此情况下,间隔物54可延伸到开口38中(开口38在图5-5B中标记)且沿着材料50和52的侧部延伸。

沟槽44-47由于间隔物54而变窄;且在一些实施例中在图6-6B的处理阶段处可具有小于或等于约10nm的宽度。

参看图7-7B,任选的势垒材料58设置于沟槽45-47内以为沟槽加衬。在所示的实施例中,势垒材料58沿着沟槽的底部和沟槽的侧部延伸,且直接抵靠金属硅化物52的上表面。势垒材料58可包括任何合适的组成物;且在一些实施例中可包括钌、钽和钛中的一或多个。

数字线材料60设置于沟槽44-47内且邻近于任选的势垒材料58。数字线材料60可包括任何合适的组成物;且在一些实施例中可包括金属。举例来说,在一些实施例中,数字线材料60可包括铜、钼、钯、铂、钌、钨、钛和其混合物,基本上由它们组成,或由它们组成。势垒材料58可在其中数字线材料包括铜的应用中特别适用以便阻止铜迁移。在其它实施例中,势垒材料58可省略,且数字线材料60的金属可直接接触金属硅化物52。举例来说,在一些应用中,数字线材料60可包括钌,基本上由钌组成,或由钌组成;且此钌可直接接触金属硅化物52的上表面(例如,可直接接触硅化钴52的上表面)。

参看图8-8B,材料56、58和60凹入在沟槽44-47内,且接着额外绝缘材料56形成于凹入材料56、58和60上并被用于填充沟槽44-47。在所示的实施例中,利用与间隔物54中利用的材料相同的绝缘材料56来填充沟槽44-47。这可能是有利的,因为这可使得能够容易地鉴定将相对于环绕数字线材料60的材料56选择性地移除模具40的材料26的蚀刻。在其它实施例中,用于填充沟槽44-47的绝缘材料可不同于间隔物54所用的材料。在一些实施例中,材料26和56可分别被称为第一和第二材料;其中第一材料包括氮化硅且第二材料包括二氧化硅。应注意,包括材料56的不同结构将彼此合并以形成包括材料56的单个构造。然而,所述结构示出为彼此分离使得所述结构在本文中所描述的组合件中清楚地划定界限;在某种程度上是为了辅助读者鉴定所附权利要求书中叙述的结构,且在某种程度上是因为申请还包含其中结构并不全部包括相同材料56的实施例。

图8-8B的凹入的数字线材料60可被视为被配置成沿着第二方向y轴延伸的数字线62。此些数字线与数字线接触区32电耦合。

参看图9-9B,相对于第二材料56选择性地移除第一材料26(图8-8B)。材料26的选择性移除可利用任何合适的条件;且在一些实施例中可利用磷酸来相对于二氧化硅选择性地移除氮化硅。

材料26的移除(图8-8B)形成沿着第二方向y轴延伸的沟槽63-67。在一些实施例中,沟槽63-67可被称为第二沟槽以将其与上文参考图5-5B所描述的第一沟槽44-47区分。数字线62在第二沟槽63-67之间,如图9A所示。

参看图10-10B,沿着第二沟槽63-67的侧壁形成间隔物68。在所示的实施例中,间隔物68包括第二材料56(例如,二氧化硅)。随后,用第一材料26(例如,氮化硅)填充沟槽63-67。

参看图11-11B,第一材料26图案化到与存储元件接触区34对准的第一材料支柱70中。在图11的俯视图中仅一些支柱70用数字70标记。然而,所有支柱70用“N”标记以标识此些支柱;其中标记“N”指示在一些实施例中支柱可包括氮化硅。第二材料56形成于沟槽63-67内(图10)且在支柱70之间的区中。在图11的俯视图中此些区用“O”标记以标识此些区;其中标记“O”指示在一些实施例中所述区可包括二氧化硅。

材料26可利用任何合适的处理图案化到支柱70中。举例来说,在一些实施例中,一或多个掩模可沿着x轴方向延伸且被用以结合一或多个合适的蚀刻将材料26图案化到支柱70中。

参看图12-12B,相对于第二材料56选择性地移除第一材料26(图11-11B)以形成与存储元件接触区34的部分对准的开口72。应注意,在一些实施例中,材料36可包括与第二材料56相同的组成物(例如,二氧化硅),且相应地材料36的区可被视为对应于第二材料的额外区。在图12的俯视图中利用标记“O”来辅助读者理解图11的标记为“N”的区相对于标记为“O”的区被选择性地移除。

参看图13-13B,开口72延伸穿过材料36并进入存储元件接触区34的半导体材料16。开口72可利用类似于上文参考图3-3B相对于开口38的延伸所描述的处理而延伸。

存储元件接触区34具有沿着延伸的开口72的底部的暴露表面73。

参看图14-14B,硅(或其它合适的半导体材料)74从半导体材料16的暴露表面73外延地生长。外延生长的硅可形成到任何合适的厚度。在一些实施例中,外延生长的硅74可省略。在一些实施例中,外延生长的硅74可用沉积在表面73上方的多晶硅替代。然而,在一些应用中,可能有利的是,利用外延生长的硅74代替多晶硅,因为外延生长的硅可提供比多晶硅可实现的更低的电阻和更好的均匀度,尤其是在高度集成的电路的严格界限内。外延生长的硅74可用一或多种合适的掺杂剂(例如,磷、硼等)进行导电掺杂。

导电含金属材料76形成于外延生长的硅74上且直接抵靠外延生长的硅74。在一些实施例中,含金属材料76可包括金属硅化物。举例来说,在一些实例实施例中,含金属材料76可包括硅化钴,基本上由硅化钴组成,或由硅化钴组成。在一些实施例中,含金属材料76可被视为直接抵靠存储元件接触区34的硅;而与材料76直接抵靠外延生长的材料74还是直接抵靠半导体材料16无关。

导电材料78设置于金属硅化物76上方且与金属硅化物76直接接触。导电材料78可包括任何合适的组成物;且在一些实施例中可包括金属。举例来说,在一些实施例中,导电材料78可包括铜、钼、钯、铂、钌、钨、钛和其混合物,基本上由它们组成,或由它们组成。在一些应用中,导电材料78可包括钌,基本上由钌组成,或由钌组成;且此钌可直接接触金属硅化物76的上表面(例如,可直接接触硅化钴76的上表面)。在一些实施例中,任选的势垒材料(类似于上文参考图7-7B所描述的任选的势垒材料58)可设置于导电材料78和金属硅化物76之间。

材料74、76和78一起形成与存储元件接触区34耦合的导电互连件80。存储元件82形成为与导电互连件80电耦合。所示出的实例存储元件82被配置成电容器。电容器82中的每一个具有与参考电压84连接的节点。参考电压可以是接地或任何其它合适的电压。

在一些实施例中,可利用其它存储元件代替电容器82。具有两个或更多个可检测状态的任何合适的装置可用作存储元件;包含例如包括相变材料、导电桥联材料等的装置。

图14-14B的配置可被视为对应于存储器阵列86(例如,DRAM阵列)的区。存储器阵列包括存储器单元88,其包含与存储元件(例如,电容器82)耦合的存取晶体管(例如,包括沿着字线20中的一个的栅极的晶体管)。参考图15描述实例存储器阵列86。存储器阵列包含对应于数字线62的数字线(DL1-DL4),且包含对应于字线20的字线(WL1-WL4)。存储器单元88包括与电容器82耦合的晶体管。存储器单元88中的每一个经由字线和数字线的组合唯一地寻址。

图15的存储器阵列86是DRAM阵列,其中存储器单元88中的每一个包括晶体管和电容器。在其它实施例中,可在其它存储器阵列中利用类似于本文中所描述的配置的配置。

在一些实施例中,可能需要形成邻近于导电互连件80的侧壁的空隙(气隙)(图14A)。这可通过(例如)减少相邻装置之间的寄生电容来改进跨存储器阵列的性能。形成邻近于导电互连件的侧壁的空隙的实例方法参考图16-19描述。

参看图16,展示可跟随图12A的处理阶段的处理阶段处的组合件10。任选地邻近于第二开口72的侧壁形成牺牲间隔物88,且接着开口72延伸到存储元件接触区34中以形成延伸的第二开口。间隔物包括间隔物材料90;其在一些实施例中可包括氮化硅,基本上由氮化硅组成,或由氮化硅组成。

参看图17,材料74、76和78形成于延伸的开口72内(图16)以形成与存储元件接触区34电耦合的导电互连件80。

参看图18,移除牺牲间隔物88(图17)以沿着导电互连件80的侧壁留下空隙(气隙)92。在所示的实施例中,空隙沿着含金属材料78和金属硅化物76的侧壁。在一些实施例中,空隙可或可不延伸为还沿着外延生长的半导体材料74的侧壁。在一些实施例中,空隙可沿着含金属材料78延伸而不沿着金属硅化物76延伸。

参看图19,可跨组合件10设置密封材料94以密封空隙(气隙)92。密封材料为电绝缘材料,且可包括任何合适的组成物。在一些实例实施例中,密封材料94可包括二氧化硅、氮化硅、经碳掺杂的二氧化硅、氮氧化硅等中的一或多个。在一些实施例中,密封材料94可为低k材料。

图19的互连件80可随后利用任何合适的处理与存储元件(例如,图14A的装置82)耦合。

上文所论述的组合件和结构可以在集成电路内利用(术语“集成电路”指由半导体衬底支撑的电子电路);并且可并入到电子系统中。这类电子系统可用于例如存储器模块、装置驱动器、功率模块、通信调制解调器、处理器模块和专用模块中,且可包含多层、多芯片模块。电子系统可以是以下广泛范围的系统中的任一个:例如相机、无线装置、显示器、芯片组、机顶盒、游戏、照明系统、交通工具、时钟、电视机、蜂窝电话、个人计算机、汽车、工业控制系统、飞机等等。本文中所描述的组合件可沿着多层级(例如,多层次、多层面)组合件的层级设置。一些层级可包括存储器,且一些层级可包括控制电路(例如,驱动器、感测放大器等)。在一些实施例中,存储器可在CMOS上方,其中CMOS并入到控制电路中。层级可在封装的单独裸片(晶片)内,或可以是同一裸片(晶片)的一部分。

除非另外规定,否则本文中所描述的各种材料、物质、组成物等可由现在已知或待开发的任何合适的方法形成,所述方法包含例如原子层沉积(ALD)、化学气相沉积(CVD)、物理气相沉积(PVD)等。

术语“介电”及“绝缘”可用于描述具有绝缘电学性质的材料。所述术语在本发明中被视为同义的。在一些情况下利用术语“介电”且在其它情况下利用术语“绝缘”(或“电绝缘”)可在本公开内提供语言变化以简化所附权利要求书内的前提基础,而非用于指示任何显著化学或电学差异。

图中各种实施例的特定定向仅出于说明的目的,且在一些应用中,实施例可相对于所展示的定向旋转。本文中所提供的描述和所附权利要求书涉及在各种特征之间具有所描述关系的任何结构,无关于结构是处于图式的特定定向还是相对于此定向旋转。

除非另外规定,否则附图说明的横截面图仅示展示横截面的平面内的特征,且不展示横截面的平面后面的材料,以便简化图式。

当一结构被称作“在另一结构上”、“邻近于另一结构”或“抵靠另一结构”时,所述结构可直接在所述另一结构上或还可能存在介入结构。相反地,当一结构被称作“直接在另一结构上”、“直接邻近于另一结构”或“直接抵靠另一结构”时,不存在介入结构。术语“正下方”、“正上方”等不指示直接物理接触(除非以其它方式明确地陈述),而是指示直立对准。

结构(例如,层、材料等)可被称为“竖直地延伸”以指示所述结构从下伏基底(例如,衬底)大体向上延伸。竖直延伸的结构可或可不相对于基底的上表面大体正交延伸。

一些实施例包含一种形成集成式组合件的方法。提供一种构造,其具有有源区支柱。每一有源区支柱具有一对存储元件接触区,且在所述对存储元件接触区之间具有数字线接触区。有源区支柱包含半导体材料。所述构造包含沿着有源区支柱且沿着第一方向延伸的字线。图案化模具形成于所述构造上方。图案化模具具有延伸穿过其中的开口。开口与数字线接触区对准。开口延伸到数字线接触区的半导体材料中。含碳聚合物形成于延伸的开口内。沟槽形成于图案化模具内。沟槽沿着第二方向延伸且越过数字线接触区。第二方向与第一方向交叉。从数字线接触区上方移除含碳聚合物以重新打开开口。重新打开的开口位于沟槽的底部处,且延伸到数字线接触区的半导体材料中。数字线接触区的表面在重新打开的开口内暴露。数字线材料形成于沟槽内且与数字线接触区电耦合。数字线材料被配置成沿着第二方向延伸的数字线。存储元件与存储元件接触区电耦合。

一些实施例包含一种形成集成式组合件的方法。提供一种构造,其具有有源区支柱。每一有源区支柱具有一对存储元件接触区,且在所述对存储元件接触区之间具有数字线接触区。有源区支柱包含单晶半导体材料。所述构造包含沿着有源区支柱且沿着第一方向延伸的字线。图案化模具形成于所述构造上方。图案化模具具有延伸穿过其中的开口。开口与数字线接触区对准。开口延伸到数字线接触区的单晶半导体材料中。牺牲材料形成于延伸的开口内。沟槽形成于图案化模具内。沟槽沿着第二方向延伸且越过数字线接触区。第二方向与第一方向交叉。从数字线接触区上方移除牺牲材料以重新打开开口。重新打开的开口位于沟槽的底部处,且延伸到数字线接触区的半导体材料中。数字线接触区的表面在重新打开的开口内暴露。硅从数字线接触区的暴露表面外延地生长。数字线材料形成于沟槽内且与外延生长的硅电耦合。数字线材料被配置成沿着第二方向延伸的数字线。存储元件与存储元件接触区电耦合。

一些实施例包含一种具有有源区支柱的集成式组合件。有源区支柱中的每一个具有接触区。接触区包含一对存储元件接触区,且在所述对存储元件接触区之间包含数字线接触区。有源区支柱包含硅。字线沿着有源区支柱且沿着第一方向延伸。硅化钴直接抵靠接触区中的一或多个的硅。含金属材料直接抵靠硅化钴。数字线与数字线接触区电耦合且沿着与第一方向交叉的第二方向延伸。存储元件与存储元件接触区电耦合。

- 包含到有源区支柱的含金属互连件的集成式组合件以及形成集成式组合件的方法

- 集成式组合件以及形成集成式组合件的方法