三相三线制电流采样电路及方法

文献发布时间:2023-06-19 11:17:41

技术领域

本申请涉及电子技术领域,尤其是一种三相三线制电流采样电路及方法。

背景技术

随着开关电源以及电机控制技术的发展,三相三线的电流采样在开关电源以及三相电机控制中必不可少,三相三线的电流影响着电源的功率因数和电机的控制参数。如何采集三相三线制的电流,从而实现对电源的功率因素进行校正和对电机的控制参数进行配置,是一直被研究的问题。

目前使用市面上有两种典型的三相三线制电流采样办法,一种是霍尔电流传感器电流采样;另一种是电流互感器电流采样。其中霍尔电流传感器是一种采用半导体材料制成的磁电转换器件,生产的工艺比较复杂,生成成本比较高;而电流互感器只能测量正弦波交流电流,当正弦波的波形失真或正弦波的频率改变时,电流互感器的响应时间比较长。

发明内容

基于上面所述的问题,本申请提供了一种三相三线制电流采样电路及方法,将两个电阻串联在任意两相的电线中,对任意两相的电线电流进行采样,使用运算电路获取剩余一相的电流,从而实现对三相三线制的电流进行采样,电流采样的响应时间短且生产成本低。

本申请提供了一种三相三线制电流采样电路,所述三相三线制电流采样电路包括第一采样电阻、第一电流采样电路、第二采样电阻、第二电流采样电路、第三电流采样电路以及处理芯片,三线包括第一电线、第二电线以及第三电线,其中:

所述第一采样电阻串联在所述第一电线中,所述第一电流采样电路包括第一整流电路,所述第一整流电路的输入端与所述第一采样电阻连接,所述第一整流电路的输出端与所述处理芯片连接;

所述第二采样电阻串联在所述第二电线中,所述第二电流采样电路包括第二整流电路,所述第二整流电路的输入端与所述第二采样电阻连接,所述第二整流电路的输出端与所述处理芯片连接,其中,所述第一采样电阻的阻值和所述第二采样电阻的阻值相同;

所述第三电流采样电路包括运算电路和第三整流电路,所述运算电路的输入端分别与所述第一整流电路的输入端和所述第二整流电路的输入端连接,所述运算电路的输出端与所述第三整流电路的输入端连接,所述第三整流电路的输出端与所述处理芯片连接。

在一种可能的实施例中,所述第一电流采样电路还包括第一隔离放大电路;所述第一隔离放大电路的输入端与所述第一采样电阻的两端连接。

可选的,所述第一电流采样电路还包括第一差分放大电路;

所述第一差分放大电路的输入端与所述第一隔离放大电路的输出端连接,所述第一差分放大电路的输出端与第一整流电路的输入端连接。

在一种可能的实施例中,所述第一电流采样电路还包括第一跟随电路;

所述第一跟随电路的输入端与所述第一整流电路的输出端连接,所述第一跟随电路的输出端与所述处理芯片的第一端口连接。

在一种可能的实施例中,所述第二电流采样电路还包括第二隔离放大电路;

所述第二隔离放大电路的输入端与所述第二采样电阻的两端连接。

可选的,所述第二电流采样电路还包括第二差分放大电路;

所述第二差分放大电路的输入端与所述第二隔离放大电路的输出端连接,所述第二差分放大电路的输出端与第二整流电路的输入端连接。

在一种可能的实施例中,所述第二电流采样电路还包括第二跟随电路;

所述第二跟随电路的输入端与所述第二整流电路的输出端连接,所述第二跟随电路的输出端与所述处理芯片的第二端口连接。

在一种可能的实现方式中,所述第一整流电路的输入端和所述第二整流电路的输入端与所述运算电路的同相输入端连接,所述运算电路输出的电压方向与所述第三电线的电流方向相反;

或者,所述第一整流电路的输入端和所述第二整流电路的输入端与所述运算电路的反相输入端连接,所述运算电路输出的电压方向与所述第三电线的电流方向相同。

在一种可能的实施例中,所述第三电流采样电路还包括第三跟随电路;

所述第三跟随电路的输入端与所述第三整流电路的输出端连接,所述第三跟随电路的输出端与所述处理芯片的第三端口连接。

本申请还提供了一种三相三线制电流采样方法,基于前面所述的三相三线制电流采样电路,所述方法包括:

第一电流采样电路获取第一采样电阻两端的电压,得到第一采样电压,第一整流电路将所述第一采样电压转换成第一直流脉动电压,并将所述第一直流脉动电压传输至处理芯片;

第二电流采样电路获取第二采样电阻两端的电压,得到第二采样电压,第二整流电路将所述第二采样电压转换成第二直流脉动电压,并将所述第二直流脉动电压传输至所述处理芯片;

运算电路将所述第一采样电压和所述第二采样电压进行相加,得到第三采样电压,第三整流电路将所述第三采样电压转换成第三直流脉动电压,并将所述第三直流脉动电压传输至所述处理芯片;

所述处理芯片获取所述第一直流脉动电压、所述第二直流脉动电压以及所述第三直流脉动电压,根据所述第一直流脉动电压和所述第一采样电阻确定所述第一电线的电流、根据所述第二直流脉动电压和所述第二采样电阻确定所述第二电线的电流以及根据所述第三直流脉动电压和所述第一采样电阻的阻值确定所述第三电线的电流。

本申请使用两个采样电阻对三相三线中任意两相进行电流采样,得到所述第一采样电压和所述第二采样电压,所述第三电流采样电路中的运算电路获取所述第一采样电压和所述第二采样电压,并将所述第一采样电压和所述第二采样电压进行相加,得到第三采样电压;所述第一整流电路将所述第一采样电压转换成第一直流脉动电压,所述第二整流电路将所述第二采样电压转换成第二直流脉动电压,所述第三整流电路将所述第三采样电压转换成第三直流脉动电压,所述处理芯片实时采集所述第一直流脉动电压、所述第二直流脉动电压和所述第三直流脉动电压,根据所述第一直流脉动电压和第一采样电阻值获取第一电线的电流,根据所述第二直流脉动电压和第二采样电阻值获取第二电线的电流,根据所述第三直流脉动电压和所述第一采样电阻的电阻值获取所述第三电线的电流。实施本申请实施例,将两个电阻串联在任意两相的电线中,对任意两相的电线电流进行采样,使用运算电路获取剩余一相的电流,从而实现对三相三线制的电流进行采样,电流采样的响应时间短且生产成本低。

附图说明

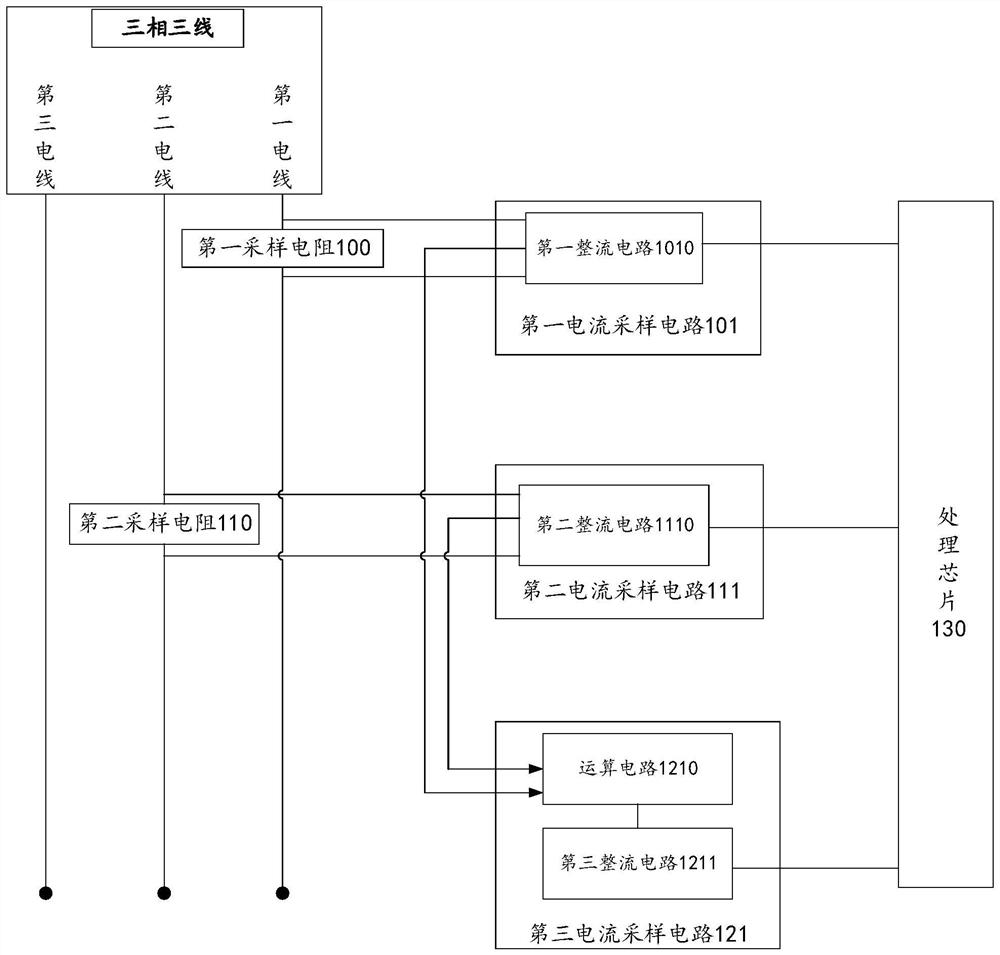

图1为本申请实施例提供的一种三相三线制电流采样电路的电路框图;

图2为本申请实施例提供的另一种三相三线制电流采样电路的电路框图;

图3为本申请实施例提供的再一种三相三线制电流采样电路的电路原理图;

图4为本申请实施例提供的一种三相三线制电流采样电路的波形示意图;

图5为本申请实施例提供的一种三相三线制电流采样方法的流程示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

下面结合附图来对本申请的技术方案的实施作进一步的详细描述。

首先参见图1,图1为本申请实施例提供的一种三相三线制电流采样电路的电路框图。如图1所示,所述三相三线制电流采样电路包括第一采样电阻100、第一电流采样电路101、第二采样电阻110、第二电流采样电路111、第三电流采样电路121以及处理芯片130,三线包括第一电线、第二电线以及第三电线,其中:

所述第一采样电阻100串联在所述第一电线中,所述第一电流采样电路101包括第一整流电路1010,所述第一整流电路1010的输入端与所述第一采样电阻100连接,所述第一整流电路1010的输出端与所述处理芯片130连接。具体的,由于所述第一电线的电流流过所述第一采样电阻100,在电阻两端形成压降,所述第一电流采样电路101获取所述第一采样电阻100两端的电压,得到第一采样电压。所述第一采样电压反映着第一电线的电流,在一种可能的实施例中,三相三线为一种市电的供电方式,所述第一电线、所述第二电线以及所述第三电线为交流电压,则所述第一采样电压也为交流电压。所述第一整流电路1010将所述第一采样电压转换成第一直流脉动电压,并将所述第一直流脉动电压传输至所述处理芯片130。由于所述处理芯片130识别的电压为正电压,而所述第一电流采样电路101获取的第一采样电压为交流电压,交流电压中包括负电压,则所述第一整流电路1010将所述第一采样电压中的负电压转换成正电压,即所述第一采样电压转换成所述第一直流脉动电压,以被所述处理芯片130识别。可以理解的是,所述第一直流脉动电压可以称为直流电压,所述第一直流脉动电压的电压值为正电压。

所述第二采样电阻110串联在所述第二电线中,所述第二电流采样电路111包括第二整流电路1110,所述第二整流电路1110的输入端与所述第二采样电阻110连接,所述第二整流电路1110的输出端与所述处理芯片130连接,其中,所述第一采样电阻100的阻值和所述第二采样电阻110的阻值相同。具体的,由于所述第二电线的电流流过所述第二采样电阻110,在电阻两端形成压降,所述第二电流采样电路111获取所述第二采样电阻110两端的电压,得到第二采样电压。所述第二采样电压反映着所述第二电线的电流。在一种可能的实施例中,所述第二采样电压为交流电压。所述第二整流电路1110将所述第二采样电压转换成第二直流脉动电压,并将所述第二直流脉动电压传输至所述处理芯片130。由于所述处理芯片130识别的电压为正电压,而所述第二电流采样电路111获取的第二采样电压为交流电压,交流电压中包括负电压,则所述第二整流电路1110将所述第二采样电压中的负电压转换成正电压,即所述第二采样电压转换成所述第二直流脉动电压,以被所述处理芯片130识别。可以理解的是,所述第二直流脉动电压可以称为直流电压,所述第二直流脉动电压为正电压。

所述第三电流采样电路121包括运算电路1210和第三整流电路1211,所述运算电路1210的输入端分别与所述第一整流电路1010的输入端和所述第二整流电路1110的输入端连接,所述运算电路1210的输出端与所述第三整流电路1211的输入端连接,所述第三整流电路1211的输出端与所述处理芯片130连接。具体的,所述运算电路1210将所述第一采样电压和所述第二采样电压进行相加,得到第三采样电压。根据基尔霍夫电流定律,在所述三相三线制的电路中,所述第一电线、所述第二电线和所述第三电线的电流之和为零。示例性的,所述第一电线的电流为I

在一种可能的实现方式中,所述第一整流电路1010的输入端和所述第二整流电路1110的输入端1110与所述运算电路1210的同相输入端连接,所述运算电路1210输出的电压方向与所述第三电线的电流方向相反。具体的,所述运算电路1210可以为同相加法运算放大器,所述第一整流电路1010将所述第一采样电压传输至所述加法运算放大器的同相输入端,所述第二整流电路1110将所述第二采样电压传输至所述加法运算放大器的同相输入端,则所述加法运算放大器的输出端为所述第一采样电压和所述第二采样电压之和,即所述第三采样电压为I

在另一种可能的实现方式中,所述第一整流电路1010的输入端和所述第二整流电路1110的输入端与所述运算电路1210的反相输入端连接,则所述运算电路1210输出的电压方向与所述第三电线的电流方向相同。具体的,所述运算电路1210可以为反相加法运算放大器,所述第一整流电路1010将所述第一采样电压传输至所述加法运算放大器的反相输入端,所述第二整流电路1110将所述第二采样电压传输至所述加法运算放大器的反相输入端,则所述加法运算放大器的输出端的绝对值为所述第一采样电压和所述第二采样电压之和,即所述第三采样电压为-(I

基于电路的实现效果来进行考虑,所述三相三线制电流采样电路除了以上结合图1的实施例包括的电路之外,还可以包括另外一些电路,下面对所述三相三线制还可以包括的电路进行详细说明。参见附图2,图2为本申请实施例提供的另一种三相三线制采样电路的电路框图。如图2所示:

在一种可能的实施例中,所述第一电流采样电路101还包括第一隔离放大电路1011;所述第一隔离放大电路1011的输入端与所述第一采样电阻100的两端连接。具体的,所述第一隔离放大电路1011将所述第一采样电阻100的电压进行放大,得到所述第一采样电压。所述第一隔离放大电路1011还具有将自身输入端口与自身输出端口进行隔离的功能,将连接至所述第一隔离放大电路1011的输入端的所述第一电线上的电磁干扰进行隔离,避免所述电磁干扰传输至所述处理芯片130。可选的,所述第一隔离放大电路1011可以为全差分隔离放大器,型号为AMC1200。可选的,所述第一采样电阻100和所述第二采样电阻110的阻值为5毫欧姆,则所述第一隔离放大电路1011获取到所述第一采样电阻100两端的电压的幅值为几百毫伏左右,所述第一隔离放大电路1011将所述第一采样电阻100两端的电压进行放大。可选的,所述全差分隔离放大器在所述第一采样电阻100两端的电压上叠加了2.5V的直流分量,作为所述第一采样电压。

进一步的,所述第一电流采样电路101还包括第一差分放大电路1012。

所述第一差分放大电路1012的输入端与所述第一隔离放大电路1011的输出端连接,所述第一差分放大电路1012的输出端与第一整流电路1010的输入端连接。具体的,所述第一差分放大电路1012将所述第一隔离放大电路1011中隔离放大的电压的直流成分进行去除,将去除了直流成分的隔离放大电压作为所述第一采样电压。示例性的,所述第一差分放大电路1012将所述第一隔离放大电路1011输出的电压进行差分运算,将所述第一隔离放大电路1011中输出的差分电压中的直流电压信号进行相减,减去了直流成分,剩余交流成分,将去除了直流成分的隔离放大电压作为所述第一采样电压。可选的,所述第一差分放大电路1012可以为差分运算放大器。

可选的,所述第一电流采样电路101还包括第一跟随电路1013。所述第一跟随电路1013的输入端与所述第一整流电路1010的输出端连接,所述第一跟随电路1013的输出端与所述处理芯片130的第一端口连接。具体的,所述第一跟随电路1013的输出电压大小与输入至所述第一跟随电路1013的电压大小相同,即所述第一整流电路1010的输出电压和所述第一跟随电路1013的输出电压相同。示例性的,所述第一跟随电路1013可以为电压跟随器,所述电压跟随器具有输入阻抗高输出阻抗低的特点。

在另一种可能的实施例中,所述第二电流采样电路111还包括第二隔离放大电路1111;所述第二隔离放大电路1111的输入端与所述第二采样电阻110的两端连接。具体的,所述第二隔离放大电路1111将所述第二采样电阻110的电压进行放大,得到所述第二采样电压。所述第二隔离放大电路1111还具有将自身的出入端口与自身输出端口进行隔离的功能,将连接至所述第二隔离放大电路1111的输入端的所述第二电线上的电磁干扰进行隔离,避免所述电磁干扰传输至所述处理芯片130。可选的,所述第二隔离放大电路1111可以为全差分隔离放大器,型号为AMC1200。在一种可能的实现方式中,所述第一采样电阻100和所述第二采样电阻110的阻值为5毫欧姆,则所述第二隔离放大电路1111获取到所述第二采样电阻110两端的电压的幅值为几百毫伏左右,所述第二隔离放大电路1111将所述第二采样电阻110两端的电压进行放大。可选的,所述全差分隔离放大器在所述第二采样电阻110两端的电压上叠加了2.5V的直流分量,作为所述第二采样电压。

进一步的,所述第二电流采样电路111还包括第二差分放大电路1112。所述第二差分放大电路1112的输入端与所述第二隔离放大电路1111的输出端连接,所述第二差分放大电路1112的输出端与第二整流电路1110的输入端连接。具体的,所述第二差分放大电路1112将所述第二隔离放大电路1111中隔离放大的电压的直流成分进行去除,将去除了直流成分的隔离放大电压作为所述第二采样电压。示例性的,所述第二差分放大电路1112将所述第二隔离放大电路1111输出的电压进行差分运算,将所述第二隔离放大电路1111中输出的差分电压中的直流电压信号进行相减,减去了直流成分,剩余交流成分,将去除了直流成分的隔离放大电压作为所述第二采样电压。可选的,所述第二差分放大电路1112可以为差分运算放大器。

可选的,所述第二电流采样电路111还包括第二跟随电路1113。所述第二跟随电路1113的输入端与所述第二整流电路1110的输出端连接,所述第二跟随电路1113的输出端与所述处理芯片130的第二端口连接。具体的,所述第二跟随电路1113的输出电压大小与输入至所述第二跟随电路1113的电压大小相同,即所述第二整流电路1110的输出电压和所述第二跟随电路1113的输出电压相同。示例性的,所述第二跟随电路1113可以为电压跟随器。所述电压跟随器具有输入阻抗高输出阻抗低的特点。

在又一种可能的实施例中,所述第三电流采样电路121还包括第三跟随电路1212。所述第三跟随电路1212的输入端与所述第三整流电路1211的输出端连接,所述第三跟随电路1212的输出端与所述处理芯片130的第三端口连接。具体的,所述第三跟随电路1212的输出电压大小与输入至所述第三跟随电路1212的电压大小相同,即所述运算电路1210的输出电压和所述第三跟随电路1212的输出电压相同。示例性的,所述第三跟随电路1212可以为电压跟随器,所述电压跟随器具有输入阻抗高输出阻抗低的特点。

在一种可能的实施例中,所述三相三线用于为充电机140提供电能。具体的,所述三相三线来自市电中的三相三线,三相的相位分别相差120°,分别为所述充电机140的三相提供电能。

下面结合附图对所述一种三相三线制电流采样电路的工作原理进行介绍,参见附图3和附图4。

首先参见图3,图3为本申请实施例提供的再一种三相三线制电流采样电路的电路原理图。如图3所示,所述三相三线制电流采样电路包括第一采样电阻300、第一电流采样电路301、第二采样电阻310、第二电流采样电路311、第三电流采样电路320以及处理芯片330,三线包括第一电线、第二电线以及第三电线,其中:

所述第一采样电阻300包括第一电阻R1,所述第一电阻R1串联在所述第一电线中;所述第二采样电阻310包括第二电阻R2,所述第二电阻R2串联在所述第二电线中。具体的,所述第一电阻R1和所述第二电阻R2的电阻值相同,可选的,所述第一电阻R1和所述第二电阻R2的阻值为5毫欧姆。所述第一电阻R1和所述第二电阻R2影响着所述三相三线制电流采样的精度,为了提高电流采样精度,应选用精度高,温漂小,寄生参数小的电阻,所述第一电阻R1和所述第二电阻R2的成本相对较高,本申请中利用基尔霍夫电流定律,使用两个采样电阻来采集三线的电流,避免使用生产成本较高的霍尔电流传感器来进行电流采样,还进一步节省了一个采样电阻和一个隔离放大器的生产成本。

所述第一电流采样电路301包括第一整流电路3011,所述第一整流电路3011包括第一运算放大器U1、第二运算放大器U2、第三电阻R3、第四电阻R4、第五电阻R5、第六电阻R6、第七电阻R7、第一二极管D1和第二二极管D2,可选的,所述第一整流电路3011还可以包括第八电阻R8和第九电阻R9。

在一种可能的实施例中,所述第一电流采样电路301还包括第一隔离放大电路3012,所述第一隔离放大电路3012包括第一全差分隔离放大器Q1。

进一步的,所述第一电流采样电路301还包括第一差分放大电路3013,所述第一差分放大电路3013包括第三运算放大器U3、第十电阻R10、第十一电阻R11、第十二电阻R12和第十三电阻R13。

更进一步的,所述第一电流采样电路301还包括第一跟随电路3014,所述第一跟随电路3014包括第四运算放大器U4,其中:

所述第一采样电阻300与所述第一隔离放大电路3012连接,具体的,所述第一全差分隔离放大器Q1包括8个端口,第一端口和第八端口为电源端口,第四端口和第五端口为接地端口,第二端口和第三端口为差分输入端口,第六端口和第七端口为差分输出端口,所述第一电阻R1的两端与所述第一全差分隔离放大器Q1的所述第二端口和所述第三端口连接。

为了更好的理解各个电路的功能实现,可以参见图4,图4为本申请实施例提供的一种三相三线制电流采样电路的波形示意图。可以理解的是,图4中的各个波形图为各个电路功能实现的示意性波形,并不代表各个电路输出的电压幅值和相位的关系。

如图4所示,所述第一全差分隔离放大器的输入端波形示意图如图4中的采样电压4a所示,采样电压4a为所述第一电阻R1两端的电压波形示意图,反映着所述第一电线的电流。经过所述第一全差分隔离放大器Q1,输出的波形如图4中的采样电压4b所示,所述第一全差分放大器Q1将所述第一采样电阻300两端的电压进行隔离放大,作为所述第一采样电压,所述第一采样电压经过所述第一隔离放大电路3012叠加了直流成分,示例性的,所述直流成分的幅值为2.5V。

所述第一隔离放大电路3012与所述第一差分放大电路3013连接,具体的,所述第一隔离放大电路3012包括第一全差分隔离放大器Q1,所述第一全差分隔离放大器Q1的第六端口与所述第十电阻R10的一端连接,所述第一全差分隔离放大器Q1的第七端口与所述第十一电阻R11的一端连接,所述第十一电阻R11的另一端与所述第十二电阻R12的一端以及所述第三运算放大器U3的同相输入端连接,所述第十二电阻R12的另一端与地连接,所述第十电阻R10的另一端与所述第十三电阻R13的一端以及所述第三运算放大器U3的反相输入端连接,所述第十三电阻R13的另一端与所述第三运算放大器U3的输出端连接。所述第一差分放大电路3013的输出波形如图4中的采样电压4c所示,所述第一差分放大电路3013的输入端与所述第一隔离放大电路3012的输出端连接,所述第一差分放大电路3013用于将所述第一隔离放大电路3012中隔离放大的电压的直流成分进行去除,将去除了直流成分的隔离放大电压作为所述第一采样电压,此时所述第一采样电压的波形如采样电压4c所示。

所述第一差分放大电路3013与所述第一整流电路3011连接,具体的,所述第一差分放大电路3013中的第三运算放大器U3的输出端与所述第五电阻R5的一端、第三电阻R3的一端连接,所述第三电阻R3的另一端与所述第一运算放大器U1的反相输入端、所述第一二极管D1的阴极和所述第四电阻R4的一端连接,所述第一二极管D1的阳极与所述第二二极管D2的阴极和所述第一运算放大器U1的输出端连接,所述第二二极管D2的阳极与所述第四电阻R4的另一端以及所述第六电阻R6的一端连接,所述第六电阻R6的另一端与所述第二运算放大器U2的反相输入端以及所述第七电阻R7的一端连接,所述第七电阻R7的另一端与所述第二运算放大器U2的输出端连接。可选的,所述第一运算放大器U1的同相输入端与所述第八电阻R8的一端连接,所述第八电阻R8的另一端与地连接,所述第八电阻R8可以稳定所述第一运算放大器U1的工作状态。同理,所述第二运算放大器U2的同相输入端与第九电阻R9的一端连接,所述第九电阻R9的另一端与地连接,用于稳定所述第二运算放大器U2的工作状态。所述第一整流电路3011用于将所述第一采样电压转换成第一直流脉动电压,所述第一电流采样电路301与所述处理芯片330连接,用于将所述第一直流脉动电压传输至所述处理芯片330,具体的,所述第一整流电路3011将波形如采样电压4c所示第一采样电压转换成如直流脉动电压4d所示的第一直流脉动电压。

所述第一整流电路3011与所述第一跟随电路3014连接,具体的,所述第二运算放大器U2的输出端与所述第四运算放大器U4的同相输入端连接,所述第四运算放大器U4的反相输入端与所述第四运算放大器U4的输出端连接,所述第四运算放大器U4的输出端与所述处理芯片330的第一端口连接。所述第一跟随电路3014将如4d所示的第一直流脉冲电压传输至所述处理芯片330。所述处理芯片330获取所述第一直流脉动电压,根据所述第一直流脉动电压和所述第一电阻R1的电阻值确定所述第一电线的电流。

在一种可能的实现方式中,所述第一运算放大器U1、第二运算放大器U2、第三运算放大器U3和第四运算放大器U4可以集成在一个集成运算放大器的芯片上。

所述第一电流采样电路301还可以包括第十四电阻R14和第一电容C1,所述十四电阻R14的一端与所述第一跟随电路3014中的第四运算放大器U4的输出端连接,所述第十四电阻R14的另一端与所述第一电容C1的一端以及所述处理芯片330的第一端口连接,所述第一电容C1的另一端与地连接。所述第十四电阻R14与所述第一电容C1组成RC低通滤波电路,防止高频信号干扰到所述处理芯片330。

所述第二电流采样电路311包括第二整流电路3111,所述第二整流电路3111包括第五运算放大器U5、第六运算放大器U6、第十五电阻R15、第十六电阻R16、第十七电阻R17、第十八电阻R18、第十九电阻R19、第三二极管D3和第四二极管D4,可选的,所述第二整流电路3111还可以包括第二十电阻R20和第二十一电阻R21。

在一种可能的实施例中,所述第二电流采样电路311还包括第二隔离放大电路3112,所述第二隔离放大电路3112包括第二全差分隔离放大器Q2。

进一步的,所述第二电流采样电路311还包括第二差分放大电路3113,所述第二差分放大电路3113包括第七运算放大器U7、第二十二电阻R22、第二十三电阻R23、第二十四电阻R24和第二十五电阻R25。

更进一步的,所述第二电流采样电路311还包括第二跟随电路3114,所述第二跟随电路3114包括第八运算放大器U8,其中:

所述第二采样电阻310与所述第二隔离放大电路3112连接,具体的,所述第二隔离放大电路3112包括第二全差分隔离放大器Q2,所述第二全差分隔离放大器Q2包括8个端口,第一端口和第八端口为电源端口,第四端口和第五端口为接地端口,第二端口和第三端口为差分输入端口,第六端口和第七端口为差分输出端口,所述第二电阻R2的两端与所述第二全差分隔离放大器Q2的所述第二端口和所述第三端口连接。

为了更好的理解各个电路的功能实现,可以参见图4,图4为本申请实施例提供的一种三相三线制电流采样电路的波形示意图。

如图4所示,所述第二全差分隔离放大器的输入端波形示意图如图4中的采样电压4a所示,采样电压4a为所述第二电阻R2两端的电压波形示意图,反映所述第二电线的电流。经过所述第二全差分隔离放大器Q2,输出的波形如采样电压4b所示,所述第二全差分放大器Q2将所述第二采样电阻310两端的电压进行隔离放大,作为所述第二采样电压,所述第二采样电压经过所述第二隔离放大电路3112叠加了直流成分,示例性的,所述直流成分的幅值为2.5V。

所述第二隔离放大电路3112与所述第二差分放大电路3113连接,具体的,所述第二全差分隔离放大器Q2的第六端口与所述第二十二电阻R22的一端连接,所述第二全差分隔离放大器Q2的第七端口与所述第二十三电阻R23的一端连接,所述第二十三电阻R23的另一端与所述第二十四电阻R24的一端以及所述第七运算放大器U7的同相输入端连接,所述第二十四电阻R24的另一端与地连接,所述第二十二电阻R22的另一端与所述第二十五电阻R25的一端以及所述第七运算放大器U7的反相输入端连接,所述第二十五电阻R25的另一端与所述第七运算放大器U7的输出端连接。所述第二差分放大电路3113的输出波形如采样电压4c所示,所述第二差分放大电路3113的输入端与所述第二隔离放大电路3112的输出端连接,所述第二差分放大电路3113用于将所述第二隔离放大电路3112中隔离放大的电压的直流成分进行去除,将去除了直流成分的隔离放大电压作为所述第二采样电压,此时所述第二采样电压的波形示意图如采样电压4c所示。

所述第二差分放大电路3113与所述第二整流电路3111连接,具体的,所述第二差分放大电路3113中的第七运算放大器U7的输出端与所述第十五电阻R15的一端以及第十七电阻R17的一端连接,所述第十五电阻R15的另一端与所述第五运算放大器U5的反相输入端、所述第三二极管D3的阴极以及所述第十六电阻R16的一端连接,所述第三二极管D3的阳极与所述第四二极管D4的阴极以及所述第五运算放大器U5的输出端连接,所述第四二极管D4的阳极与所述第十六电阻R16的另一端以及所述第十八电阻R18的一端连接,所述第十八电阻R18的另一端与所述第六运算放大器U6的反相输入端以及所述第十九电阻R19的一端连接,所述第十九电阻R19的另一端与所述第六运算放大器U6的输出端连接。可选的,所述第五运算放大器U5的同相输入端与所述第二十电阻R20的一端连接,所述第二十电阻R20的另一端与地连接,所述第二十电阻R20可以稳定所述第五运算放大器U5的工作状态。同理,所述第六运算放大器U6的同相输入端与第二十一电阻R21的一端连接,所述第二十一电阻R21的另一端与地连接,用于稳定所述第六运算放大器U6的工作状态。所述第二整流电路3111用于将所述第二采样电压转换成第二直流脉动电压,所述第二电流采样电路311与所述处理芯片330连接,用于将所述第二直流脉动电压传输至所述处理芯片330,具体的,所述第二整流电路3111将波形如采样电压4c所示第二采样电压转换成如直流脉动电压4d所示的第二直流脉动电压。

所述第二整流电路3111与所述第二跟随电路3114连接,具体的,所述第六运算放大器U6的输出端与所述第八运算放大器U8的同相输入端连接,所述第八运算放大器U8的反相输入端与所述第八运算放大器U8的输出端连接,所述第八运算放大器U8的输出端与所述处理芯片330的第二端口连接。所述第二跟随电路3114将如直流脉动电压4d所示的第二直流脉冲电压传输至所述处理芯片330。

可选的,所述第五运算放大器U5、第六运算放大器U6、第七运算放大器U7和第八运算放大器U8可以集成在一个集成运算放大器的芯片上。

所述第二电流采样电路311还可以包括第二十六电阻R26和第二电容C2,所述二十六电阻R26的一端与所述第二跟随电路3114中的第八运算放大器U8的输出端连接,所述第二十六电阻R26的另一端与所述第二电容C2的一端和所述处理芯片330的第二端口连接,所述第二电容C2的另一端与地连接。所述第二十六电阻R26与所述第二电容C2组成RC低通滤波电路,防止高频信号干扰到所述处理芯片330。

所述第三电流采样电路320包括运算电路3201和第三整流电路3202,所述运算电路3201包括第九运算放大器U9、第二十七电阻R27、第二十八电阻R28、第二十九电阻R29以及第三十电阻R30;所述第三整流电路3202包括第十运算放大器U10、第十一运算放大器U11、第三十一电阻R31、第三十二电阻R32、第三十三电阻R33、第三十四电阻R34、第三十五电阻R35、第五二极管D5以及第六二极管D6,可选的,所述第三整流电路3202还可以包括第三十六电阻R36和第三十七电阻R37。

可选的,所述第三电流采样电路320还包括第三跟随电路3203,所述第三跟随电路3203包括第十二运算放大器U12,其中:

所述第三电流采样电路320分别与所述第一电流采样电路301和所述第二电流采样电路311连接,具体的,所述第一电流采样电路301中的第一差分放大电路3013与所述第三电流采样电压320中的运算电路3201连接,则所述第三运算放大器U3的输出端与所述二十七电阻R27的一端连接,所述第二十七电阻R27的另一端与所述第九运算放大器U9的反相输入端以及所述第二十九电阻R29的一端连接;所述第二电流采样电路311中的第二差分放大电路3113与所述第三电流采样电路320中的运算电路3201连接,则所述第七运算放大器U7的输出端与所述第二十八电阻R28的一端连接,所述第二十八电阻R28的另一端与所述第九运算放大器U9的反相输入端以及所述第二十九电阻R29的一端连接。所述第二十九电阻R29的另一端与所述第九运算放大器U9的输出端连接,所述第三十电阻R30的一端与所述第九运算放大器U9的同相输入端连接,所述第三十电阻R30的另一端与地连接。所述第九运算放大器U9将所述第一采样电压和所述第二采样电压进行反相相加得到所述第三采样电压,则所述第九运算放大器U9的输出端输出的第三电线的电压波形与采样电压4a中的波形示意图的相位相反。

所述运算电路3201和所述第三整流电路3202连接,具体的,所述运算电路3201中的第九运算放大器U9的输出端与所述第三十一电阻R31的一端、第三十三电阻R33的一端连接,所述第三十一电阻R31的另一端与所述第十运算放大器U10的反相输入端、所述第五二极管D5的阴极和所述第三十二电阻R32的一端连接,所述第五二极管D5的阳极与所述第六二极管D6的阴极以及所述第十运算放大器U10的输出端连接,所述第六二极管D6的阳极与所述第三十二电阻R32的另一端以及所述第三十四电阻R34的一端连接,所述第三十四电阻R34的另一端与所述第十一运算放大器U11的反相输入端以及所述第三十五电阻R35的一端连接,所述第三十五电阻R35的另一端与所述第十一运算放大器U11的输出端连接。可选的,所述第十运算放大器U10的同相输入端与所述第三十六电阻R36的一端连接,所述第三十六电阻R36的另一端与地连接,所述第三十六电阻R36可以稳定所述第十运算放大器U10的工作状态。同理,所述第十一运算放大器U11的同相输入端与第三十七电阻R37的一端连接,所述第三十七电阻R37的另一端与地连接,用于稳定所述第十一运算放大器U11的工作状态。所述第三整流电路3202用于将所述第三采样电压转换成第三直流脉动电压,所述第三电流采样电路320与所述处理芯片330连接,用于将所述第三直流脉动电压传输至所述处理芯片330,示例性的,所述第三直流脉动电压的波形图如直流脉动电压4d所示。

所述第三整流电路3202与所述第三跟随电路3203连接,具体的,所述第十一运算放大器U11的输出端与所述第十二运算放大器U12的同相输入端连接,所述第十二运算放大器U12的反相输入端与所述第十二运算放大器U12的输出端连接,所述第十二运算放大器U12的输出端与所述处理芯片330的第三端口连接。所述第三跟随电路3203将如直流脉动电压4d所示的第三直流脉冲电压传输至所述处理芯片330。

在一种可能的实现方式中,所述第九运算放大器U9、第十运算放大器U10、第十一运算放大器U11和第十二运算放大器U12可以集成在一个集成运算放大器的芯片上。

所述第三电流采样电路320还可以包括第三十八电阻R38和第三电容C3,所述三十八电阻R38的一端与所述第三跟随电路3203中的第十二运算放大器U12的输出端连接,所述第三十八电阻R38的另一端与所述第三电容C3的一端以及所述处理芯片330的第三端口连接,所述第三电容C3的另一端与地连接。所述第三十八电阻R38与所述第三电容C3组成RC低通滤波电路,防止高频信号干扰到所述处理芯片330。

在本实施例,所述第一采样电阻300串联在第一电线中,所述第一隔离放大电路3012获取所述第一采样电阻300两端的电压,并将所述第一采样电阻300两端的电压进行隔离放大,并传输至所述第一差分运放电路3013中得到第一采样电压,所述第一整流电路3011将所述第一采样电压转换成第一直流脉动电压,所述处理芯片330实时采集所述第一直流脉动电压,根据所述第一直流脉动电压和所述第一采样电阻300的电阻值获取第一电线的电流;同理,所述第二采样电阻310串联在第二电线中,所述第二隔离放大3112电路获取所述第二采样电阻310两端的电压,并将所述第二采样电阻310两端的电压进行隔离放大,并传输至所述第二差分运放电路3113中得到第二采样电压,所述第二整流电路3111将所述第二采样电压转换成第二直流脉动电压,所述处理芯片330实时采集所述第二直流脉动电压,根据所述第二直流脉动电压和所述第二采样电阻310的电阻值获取所述第二电线的电流;所述第三电流采样电路320中的运算电路3201获取所述第一采样电压和所述第二采样电压,并将所述第一采样电压和所述第二采样电压进行相加,得到第三采样电压,将所述第三采样电压传输至所述第三整流电路3202,所述第三整流电路3202将所述第三采样电压转换成第三直流脉动电压,并传输至所述处理芯片330,所述处理芯片330实时采集所述第三直流脉动电压,根据所述第三直流脉动电压和所述第一采样电阻300的电阻值获取所述第三电线的电流。实施本实施例,将两个电阻串联在任意两相的电线中,对任意两相的电线电流进行采样,使用运算电路获取剩余一相的电流,从而实现三相三线制的电流采样,响应时间短且生产成本低。

基于前文结合图1所描述的三相三线制电流采样电路,本申请实施例还提供了一种三相三线制电流采样方法,参见图5,图5为本申请实施例提供的一种三相三线制电流采样方法的流程示意图,如图5所示,具体执行步骤如下:

S500、第一电流采样电路获取第一采样电阻两端的电压,得到第一采样电压,第一整流电路将所述第一采样电压转换成第一直流脉动电压,并将所述第一直流脉动电压传输至处理芯片。

具体的,所述第一电线的电流流过所述第一采样电阻,在电阻两端形成压降,所述第一电流采样电路获取所述第一采样电阻两端的电压,得到第一采样电压,所述第一采样电压反映着第一电线的电流。所述第一采样电压为交流电压。所述第一整流电路将所述第一采样电压转换成第一直流脉动电压,并将所述第一直流脉动电压传输至所述处理芯片。

S501、第二电流采样电路获取第二采样电阻两端的电压,得到第二采样电压,第二整流电路将所述第二采样电压转换成第二直流脉动电压,并将所述第二直流脉动电压传输至所述处理芯片。

具体的,所述第二电线的电流流过所述第二采样电阻,在电阻两端形成压降,所述第二电流采样电路获取所述第二采样电阻两端的电压,得到第二采样电压,所述第二采样电压反映着所述第二电线的电流。所述第二采样电压为交流电压。所述第二整流电路将所述第二采样电压转换成第二直流脉动电压,并将所述第二直流脉动电压传输至所述处理芯片。

S502、运算电路将所述第一采样电压和所述第二采样电压进行相加,得到第三采样电压,第三整流电路将所述第三采样电压转换成第三直流脉动电压,并将所述第三直流脉动电压传输至所述处理芯片。

S503、所述处理芯片获取所述第一直流脉动电压、所述第二直流脉动电压以及所述第三直流脉动电压,根据所述第一直流脉动电压和所述第一采样电阻确定所述第一电线的电流、根据所述第二直流脉动电压和所述第二采样电阻确定所述第二电线的电流以及根据所述第三直流脉动电压和所述第一采样电阻的阻值确定所述第三电线的电流。

具体的,所述处理芯片中的数模转换模块实时采集所述第一电流采样电路、所述第二电流采样电路和所述第三电流采样电路中输出的电压信号,包括所述第一直流脉动电压、第二直流脉动电压以及第三直流脉动电压。所述处理芯片中的运算模块根据所述第一直流脉动电压和所述第一采样电阻的电阻值获取所述第一采样电阻的电流,而所述第一采样电阻串联在所述第一电线中,根据串联电路中电流相等,可知所述第一采样电阻的电流为所述第一电线的电流;同理的,所述处理芯片中的运算模块根据所述第二直流脉动电压和所述第二采样电阻的电阻值获取所述第二采样电阻的电流,而所述第二采样电阻串联在所述第二电线中,所述第二采样电阻的电流为所述第二电线的电流;所述处理芯片中的数模转换模块可以实时采集所述第三直流脉动电压,所述处理芯片中的运算模块根据所述第三直流脉动电压和所述第一采样电阻的阻值获取所述第三电线的电流。示例性的,所述处理芯片实时采集到的所述第一直流脉动电压为U

需要说明的是,所述处理芯片包括多个端口,所述第一直流脉动电压、所述第二直流脉动电压和所述第三直流脉动电压传输至所述处理芯片的端口不一样,以保证所述第一直流脉动电压、所述第二直流脉动电压和所述第三直流脉动电压的采集准确性。由此可得,所述处理芯片根据所述第一直流脉动电压和所述第一采样电阻确定所述第一电线的电流,根据所述第二直流脉动电压和所述第二采样电阻确定所述第二电线的电流,根据所述第三直流脉动电压和所述第一采样电阻的阻值确定所述第三电线的电流。

实施本实施例,可以使用电阻对三相三线制中的任意两相进行电流采样,然后根据电流采样电路获取剩余一相的电流,从而实现对三相三线制的电流进行采样,降低了生产成本。

需要说明的是,上述术语“第一”、“第二”仅用于描述目的,而不能理解为指示或暗示相对重要性。可以理解的是,图3和图4对应的示例仅用于解释本申请实施例,不应构成限定,在可选方式中,图3和图4还可以有其他实现方式,例如可以将图3的运算放大器集成到一个运算放大器集成芯片、将图4的波形示意图进行反相输入处理等,在此不再列举。

本领域普通技术人员可以理解实现上述实施例方法中的全部或部分流程,是可以通过计算机程序来指令相关的硬件来完成,所述的程序可存储于一计算机可读取存储介质中,该程序在执行时,可包括如上述各方法的实施例的流程。其中,所述的存储介质可为磁碟、光盘、只读存储记忆体(Read-Only Memory,ROM)或随机存储记忆体(Random AccessMemory,RAM)等。

以上所揭露的仅为本申请较佳实施例而已,当然不能以此来限定本申请之权利范围,因此依本申请权利要求所作的等同变化,仍属本申请所涵盖的范围。

- 三相三线制电流采样电路及方法

- 一种带两个电流传感器的三相三线制逆变器功率管开路故障和电流传感器故障综合诊断方法