CMOS集成器件的制造方法

文献发布时间:2023-06-19 11:17:41

技术领域

本发明涉及半导体技术领域,特别涉及一种半CMOS集成器件的制造方法。

背景技术

随着集成电路制造技术的不断发展,对芯片集成度的要求也不断提高,在通过CMOS工艺平台制作的芯片中,要求同时集成有核心MOS器件(core MOS devices)和输入/输出MOS器件(I/O MOS devices)。尤其对于输入/输出MOS器件,在通过CMOS工艺平台制作的芯片中要求集成有多个,且多个输入/输出MOS器件需要具有不同的工作电压,以满足芯片适应性的需要。例如需要同时提供工作电压为1.5V、3.3V和5V的输入/输出MOS器件,或者工作电压为1.5V和5V的输入/输出MOS器件。并且,在集成电路亚微米以及深亚微米时代中,随着栅极长度/沟道长度的减小,在技术上需要面对的主要问题包括穿通和沟道电场,这些问题会导致的热载流子效应(Hot Carrier Injection,HCI)。即由于耗尽区宽度延展进入沟道,导致有效沟道长度变窄,等效加在沟道上的电场则增加,导致沟道载流子碰撞从而增加产生新电子空穴对,进而形成热载流子掺杂效应。为了抑制HCI,通过在高掺杂的源极/漏极上制作浅掺杂漏(Low Doped Drain,LDD)和晕环离子注入(Pocket Implant)以降低沟道区域的耗尽区宽度。

然而,对于以上具有不同工作电压的输入/输出MOS器件,其对制作工艺的要求是不同的,若且工艺之间兼容性较差,若单独制作则会使得光刻次数增多工艺成本增加。

现有技术中,为了降低具有不同工作电压的输入/输出MOS器件的制造成本,提出了通过3.3V的NMOS器件和1.5V的PMOS器件共用1.5V的PMOS器件的晕环离子注入光罩(Pocket Implant),以实现对3.3V的NMOS器件的光罩减版,进而达到降低工艺成本的目的。然而,为了保证3.3V的NMOS器件的阈值电压和饱和电流的要求,因此,在使用1.5V的PMOS器件的晕环离子注入工艺在形成的3.3V的NMOS器件的浅掺杂离子注入区LDD的过程中,将所述1.5V的PMOS器件的晕环离子注入的N型离子注入能量从120K eV改到160K eV,从而使N型离子能够直接穿过栅极,注入至沟道内,以此来调节3.3V NMOS器件的的阈值电压和饱和电流。

但是,由于如果采用注入能量为160K eV的1.5V的PMOS器件的晕环离子注入对5VNMOS器件进行离子注入,会打穿5VNMOS器件的栅极,从而引起5VNMOS器件的阈值电压和饱和电流无法满足设计要求。因此,在现有技术中,不能使用注入能量为160K eV的1.5V的PMOS器件的晕环离子注入对5VNMOS器件进行离子注入,而是需要额外添加一道LDD的光罩。

发明内容

本发明的目的在于提供一种CMOS集成器件的制造方法,以降低现有技术中CMOS集成器件的制造成本。

为解决上述技术问题,本发明提供一种CMOS集成器件的制造方法,包括:

提供一半导体衬底,所述半导体衬底包括所需工作电压依次增高的第一CMOS器件区、第二CMOS器件区和第三CMOS器件区,所述第一CMOS器件区包括正常阈值电压CMOS器件区和低阈值电压CMOS器件区,每个CMOS器件区均包括PMOS区和NMOS区;

在各个所述PMOS区和所述NMOS区的半导体衬底上形成有相应的栅极结构;

在所述半导体衬底的表面上形成图形化的第一光刻胶层,所述第一光刻胶层中形成有对准所述正常阈值电压CMOS器件区的PMOS区的第一注入窗口,以及,对准所述第二CMOS器件区的NMOS区的第二注入窗口;

以所述第一光刻胶层和所述栅极结构为掩膜,采用P型离子对所述第一注入窗口和所述第二注入窗口下方的半导体衬底进行离子注入,以在所述正常阈值电压CMOS器件区的PMOS区中形成第一P型浅掺杂离子注入区,在所述第二CMOS器件区的NMOS区中形成第一P型晕环离子注入区;

去除所述第一光刻胶层,并在所述半导体衬底的表面上形成图形化的第二光刻胶层,所述第二光刻胶层中形成有对准所述低阈值电压CMOS器件区的PMOS区的第三注入窗口,以及,对准所述第三CMOS器件区的NMOS区的第四注入窗口;

以所述第二光刻胶层和所述栅极结构为掩膜,采用N型离子对所述第三注入窗口和所述第四注入窗口下方的半导体衬底进行离子注入,以在所述低阈值电压CMOS器件区的PMOS区中形成第一N型晕环离子注入区,在所述第三CMOS器件区的NMOS区中形成第一N型浅掺杂离子注入区。

可选的,所述N型离子可以包括磷、砷和锑中的至少一种,所述P型离子可以包括硼、铟和镓中的至少一种。

可选的,所述第一CMOS器件区的工作电压可以为1.5V,所述第二CMOS器件区的工作电压可以为3.3V,所述第三CMOS器件区的工作电压可以为5V。

可选的,在形成所述第一N型晕环离子注入区和所述第一N型浅掺杂离子注入区之后,或者,在形成所述栅极结构之后且在形成所述第一光刻胶层之前,所述制造方法还可以包括:

在所述半导体衬底的表面上形成图形化的第三光刻胶层,所述第三光刻胶层中形成有对准所述正常阈值电压CMOS器件区的NMOS区的第五注入窗口,以及,对准所述第二CMOS器件区的PMOS区的第六注入窗口;

以所述第三光刻胶层和所述栅极结构为掩膜,采用N型离子对所述第五注入窗口和所述第六注入窗口下方的半导体衬底进行离子注入,以在所述正常阈值电压CMOS器件区的NMOS区中形成第二N型浅掺杂离子注入区,在所述第二CMOS器件区的PMOS区中形成第二N型晕环离子注入区;

去除所述第三光刻胶层,并在所述半导体衬底的表面上形成图形化的第四光刻胶层,所述第四光刻胶层中形成有对准所述低阈值电压CMOS器件区的NMOS区的第七注入窗口,以及,对准所述第三CMOS器件区的PMOS区的第八注入窗口;

以所述第三光刻胶层和所述栅极结构为掩膜,采用P型离子对所述第七注入窗口和所述第八注入窗口下方的半导体衬底进行离子注入,以在所述低阈值电压CMOS器件区的NMOS区中形成第二P型晕环离子注入区,在所述第三CMOS器件区的PMOS区中形成第二P型浅掺杂离子注入区。

可选的,在形成各个所述PMOS区和所述NMOS区所需的浅掺杂离子注入区之后,在各个所述栅极结构的侧壁上分别形成侧墙。

可选的,在形成所述侧墙之后,以所述侧墙和所述栅极结构为掩膜,在各个所述栅极结构两侧的半导体衬底内形成源区和漏区。

可选的,在各个所述PMOS区和所述NMOS区的半导体衬底上形成有相应的栅极结构的步骤,包括:

在所述半导体衬底上形成栅氧化层、控制栅层和硬掩膜层,并以所述硬掩膜层为掩膜刻蚀所述控制栅层,以形成所述多个分立的栅极结构。

可选的,在以所述第一光刻胶层和所述栅极结构为掩膜,采用P型离子对所述第一注入窗口和所述第二注入窗口下方的半导体衬底进行离子注入的步骤中所述P型离子注入的注入能量为:150KeV~190KeV,注入剂量为1E13~8E13。

可选的,在以所述第二光刻胶层和所述栅极结构为掩膜,采用N型离子对所述第三注入窗口和所述第四注入窗口下方的半导体衬底进行离子注入的步骤中所述N型离子注入的注入能量为:90KeV~130KeV,注入剂量为1E13~9E13。

与现有技术相比,本发明技术方案至少具有如下有益效果之一:

在本发明提供的CMOS集成器件的制造方法中,通过采用改良后的第一CMOS器件区中的低阈值电压PMOS管的晕环离子注入光罩,在打开第一CMOS器件区中低阈值电压PMOS管所在区域(第三注入窗口)的同时打开第三CMOS器件区的NMOS管所在区域(第四注入窗口),因此,在通过对所述第三注入窗口进行离子注入,形成低阈值电压PMOS管的第一N型晕环离子注入区的同时在所述第四注入窗口对应的半导体衬底上形成第三CMOS器件区的NMOS管的N型浅掺杂离子注入区,从而节省了一道形成第三CMOS器件区的NMOS管的浅掺杂离子注入光罩,进而节约了CMOS集成器件的生产成本、提高了生产效率。

进一步的,由于通过本发明提供的CMOS集成器件的制造方法在制造CMOS器件的过程中,先是工作电压为1.5V的正常阈值电压CMOS器件区的PMOS管与工作电压为3.3V的CMOS器件区的NMOS管共用一套PLDD光罩,实现对3.3V的CMOS器件的光罩减版;之后,在通过将工作电压为1.5V的低阈值电压CMOS器件区的PMOS管与工作电压为5V的CMOS器件区的NMOS管共用一套N型Pocket光罩,实现对5V的CMOS器件的光罩减版,即,通过多次光罩减版的方式,节省了多次光刻、离子注入等工艺步骤,从而在节约了生产成本和提高了生产效率,还可以有效提高晶圆厂和客户的竞争力。

附图说明

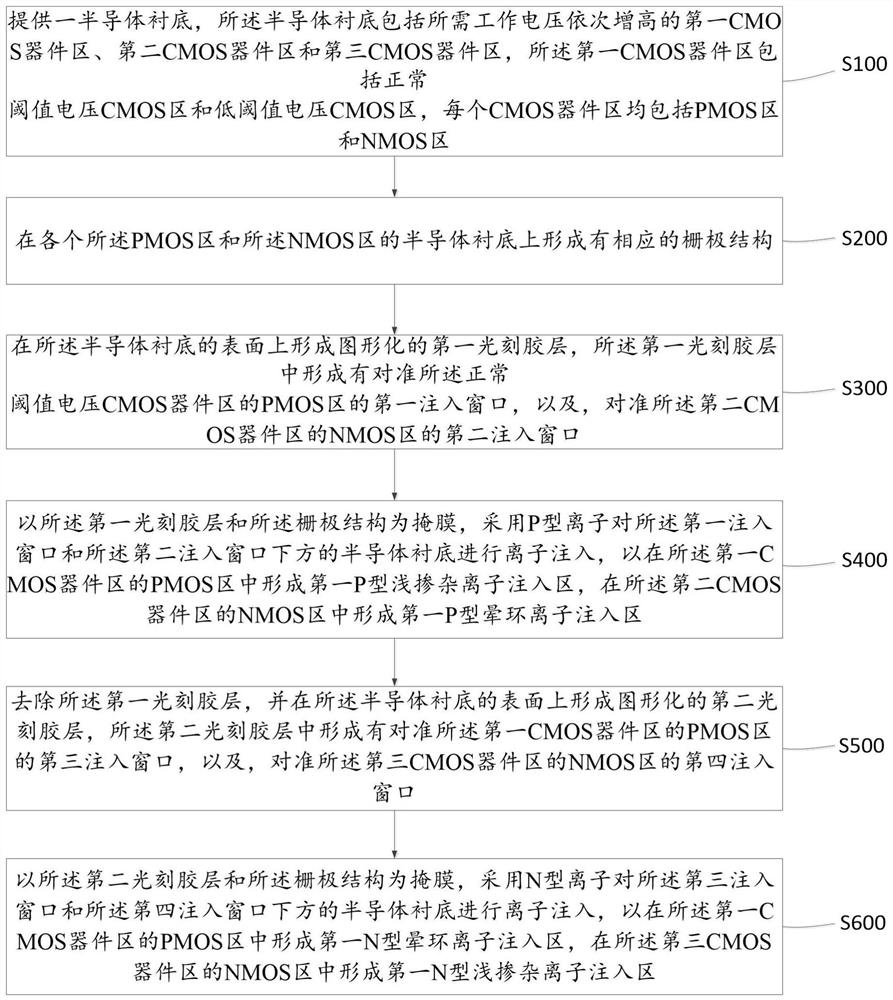

图1为本发明一实施例中的CMOS集成器件的制造方法的流程示意图;

图2a~图2d为本发明一实施例中的CMOS集成器件的制造方法在其制备过程中的结构示意图。

其中,附图标记如下:

100-衬底; 110-栅氧化层;

1-第一CMOS器件区; 2-第二CMOS器件区;

3-第一CMOS器件区; 1A-正常阈值电压CMOS器件区;

1B-低阈值电压CMOS器件区;

140n-第一CMOS器件区中的低阈值电压NMOS管;

140p-第一CMOS器件区的低阈值电压PMOS管;

150n-第一CMOS器件区的正常阈值电压NMOS管;

150p-第一CMOS器件区的正常阈值电压PMOS管;

260n-第二CMOS器件区的NMOS管;

260p-第二CMOS器件区的PMOS管;

370n-第三CMOS器件区的NMOS管;

370p-第三CMOS器件区的PMOS管;

120-图案化的第一光刻胶层; 130-图案化的第二光刻胶层;

151-第一P型浅掺杂离子注入区; 152-N型晕环离子注入区;

261-第一P型晕环离子注入区; 262-N型浅掺杂离子注入区262;

141-第一N型晕环离子注入区; 142-P型浅掺杂离子注入区;

371-第一N型浅掺杂离子注入区; 372-P型晕环离子注入区;

101-器件隔离结构; P-P型离子;

N-N型离子。

具体实施方式

承如背景技术所述,在现有技术中,为了降低具有不同工作电压的输入/输出MOS器件的制造成本,提出了通过3.3V的NMOS器件和1.5V的PMOS器件共用1.5V的PMOS器件的晕环离子注入光罩(Pocket Implant),以实现对3.3V的NMOS器件的光罩减版,进而达到降低工艺成本的目的。然而,为了保证3.3V的NMOS器件的阈值电压和饱和电流的要求,因此,在使用1.5V的PMOS器件的晕环离子注入工艺在形成的3.3V的NMOS器件的浅掺杂离子注入区LDD的过程中,将所述1.5V的PMOS器件的晕环离子注入的N型离子注入能量从120K eV改到160K eV,从而使N型离子能够直接穿过栅极,注入至沟道内,以此来调节3.3VNMOS器件的的阈值电压和饱和电流。

但是,由于如果采用注入能量为160K eV的1.5V的PMOS器件的晕环离子注入对5VNMOS器件进行离子注入,会打穿5VNMOS器件的栅极,从而引起5VNMOS器件的阈值电压和饱和电流无法满足设计要求。因此,在现有技术中,不能使用注入能量为160K eV的1.5V的PMOS器件的晕环离子注入对5VNMOS器件进行离子注入,而是需要额外添加一道LDD的光罩。

为此,本发明提供了一种的CMOS集成器件的制造方法,以解决现有技术中CMOS集成器件的制造成本高的问题。

参考图1所示,图1为本发明实施例中提供的CMOS集成器件的制造方法的流程示意图;其中,所述CMOS集成器件的制造方法可以包括如下步骤:

步骤S100,提供一半导体衬底,所述半导体衬底包括所需工作电压依次增高的第一CMOS器件区、第二CMOS器件区和第三CMOS器件区,所述第一CMOS器件区包括正常阈值电压CMOS器件区和低阈值电压CMOS器件区,每个CMOS器件区均包括PMOS区和NMOS区;

步骤S200,在各个所述PMOS区和所述NMOS区的半导体衬底上形成有相应的栅极结构;

步骤S300,在所述半导体衬底的表面上形成图形化的第一光刻胶层,所述第一光刻胶层中形成有对准所述正常阈值电压CMOS器件区的PMOS区的第一注入窗口,以及,对准所述第二CMOS器件区的NMOS区的第二注入窗口;

步骤S400,以所述第一光刻胶层和所述栅极结构为掩膜,采用P型离子对所述第一注入窗口和所述第二注入窗口下方的半导体衬底进行离子注入,以在所述正常阈值电压CMOS器件区的PMOS区中形成第一P型浅掺杂离子注入区,在所述第二CMOS器件区的NMOS区中形成第一P型晕环离子注入区;

步骤S500,去除所述第一光刻胶层,并在所述半导体衬底的表面上形成图形化的第二光刻胶层,所述第二光刻胶层中形成有对准所述低阈值电压CMOS器件区的PMOS区的第三注入窗口,以及,对准所述第三CMOS器件区的NMOS区的第四注入窗口;

步骤S600,以所述第二光刻胶层和所述栅极结构为掩膜,采用N型离子对所述第三注入窗口和所述第四注入窗口下方的半导体衬底进行离子注入,以在所述低阈值电压CMOS器件区的PMOS区中形成第一N型晕环离子注入区,在所述第三CMOS器件区的NMOS区中形成第一N型浅掺杂离子注入区。

即,在本发明提供的CMOS集成器件的制造方法中,通过采用改良后的第一CMOS器件区中的低阈值电压PMOS管的晕环离子注入光罩,在打开第一CMOS器件区中低阈值电压PMOS管所在区域(第三注入窗口)的同时打开第三CMOS器件区的NMOS管所在区域(第四注入窗口),因此,在通过对所述第三注入窗口进行离子注入,形成低阈值电压PMOS管的第一N型晕环离子注入区的同时在所述第四注入窗口对应的半导体衬底上形成第三CMOS器件区的NMOS管的N型浅掺杂离子注入区,从而节省了一道形成第三CMOS器件区的NMOS管的浅掺杂离子注入光罩,进而节约了CMOS集成器件的生产成本、提高了生产效率。进一步的,由于通过本发明提供的CMOS集成器件的制造方法在制造CMOS器件的过程中,先是工作电压为1.5V的正常阈值电压CMOS器件区的PMOS管与工作电压为3.3V的CMOS器件区的NMOS管共用一套PLDD光罩,实现对3.3V的CMOS器件的光罩减版;之后,在通过将工作电压为1.5V的低阈值电压CMOS器件区的PMOS管与工作电压为5V的CMOS器件区的NMOS管共用一套N型Pocket光罩,实现对5V的CMOS器件的光罩减版,即,通过多次光罩减版的方式,节省了多次光刻、离子注入等工艺步骤,从而在节约了生产成本和提高了生产效率,还可以有效提高晶圆厂和客户的竞争力。

以下结合附图和具体实施例对本发明提出的半导体器件及其形成方法作进一步详细说明。根据下面说明,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

图2a~图2d为本发明一实施例中的CMOS集成器件的制造方法在其制备过程中的结构示意图。

在步骤S100中,具体参考图2a所示,提供一半导体衬底100,在所述半导体衬底100中形成有器件隔离结构101以及通过所述器件隔离结构101隔离开的所需工作电压依次增高的第一CMOS器件区1、第二CMOS器件区2和第三CMOS器件区3,每个所述CMOS器件区均包括PMOS区和NMOS区。其中,所述半导体衬底100可以是本领域公知的任意合适的底材,例如可以是以下所提到的材料中的至少一种:硅(Si)、锗(Ge)、锗硅(SiGe)、碳硅(SiC)、碳锗硅(SiGeC)、砷化铟(InAs)、砷化镓(GaAs)、磷化铟(InP)或者其它III/V化合物半导体,还包括这些半导体构成的多层结构等,或者为绝缘体上硅(SOI)、绝缘体上层叠硅(SSOI)、绝缘体上层叠锗化硅(S-SiGeOI)、绝缘体上锗化硅(SiGeOI)以及绝缘体上锗(GeOI),或者还可以为双面抛光硅片(Double Side PolishedWafers,DSP),也可为氧化铝等的陶瓷基底、石英或玻璃基底等。示例性的,本实施例中半导体衬底100例如为硅晶圆。

其中,所述第一CMOS器件区的工作电压可以为1.5V,所述第二CMOS器件区的工作电压可以为3.3V,所述第三CMOS器件区的工作电压可以为5V。并且,在所述第一CMOS器件区1对应的半导体衬底100内还可以包括正常阈值电压CMOS器件区1A和低阈值电压CMOS器件区1B。

需要说明的是,在实际应用中,在通过CMOS工艺平台制作的芯片中要求集成有多个,且多个输入/输出CMOS器件需要具有不同的工作电压,以满足芯片适应性的需要。其中,有一些芯片设计中需要特殊的1.5V的CMOS器件,本发明实施例中称其为低阈值电压CMOS器件,其中,低阈值电压CMOS器件相比正常的1.5VCMOS器件(称为正常阈值电压CMOS器件)的阈值电压要小200mV-300mV,以便适用实际的设计需求。

本实施例中,在所述半导体衬底100内可以形成多个用于后续形成所述各个CMOS器件区中的PMOS区的N型阱(未图示)和用于形成NMOS区的P型阱(未图示),并且,相邻N型阱和P型阱通过浅沟槽隔离(未图示)。

在步骤S200中,继续参考图2a所示,在各个所述PMOS区和所述NMOS区的半导体衬底100上形成有相应的栅极结构。示例性的,在所述第一CMOS器件区1对应的半导体衬底100的表面上形成有四个独立的栅极结构,即分别为工作电压为1.5V的低阈值电压NMOS管的栅极结构140n、工作电压为1.5V的低阈值电压PMOS管的栅极结构140p、工作电压为1.5V的高阈值电压NMOS管的栅极结构150n和工作电压为1.5V的正常阈值电压PMOS管的栅极结构150p;在所述第二CMOS器件区2对应的半导体衬底100表面上形成有工作电压为3.3V的NMOS管的栅极结构260n和工作电压为3.3V的PMOS管的栅极结构260p;在所述第三CMOS器件区2对应的半导体衬底100表面上形成有工作电压为5V的NMOS管的栅极结构370n和工作电压为5V的PMOS管的栅极结构370p。

本实施例中,可以先在所述半导体衬底100的表面上依次形成栅氧化层110、控制栅层(未图示)和硬掩膜层(未图示),然后,在以所述硬掩膜层为掩膜刻蚀形成在所述栅氧化层110表面上的控制栅层,从而在各个所述PMOS区和所述NMOS区的半导体衬底100上形成有相应的栅极结构。

在步骤S300中,具体参考图2b所示,在所述半导体衬底100的表面上形成图形化的第一光刻胶层120,所述第一光刻胶层120中形成有对准所述正常阈值电压CMOS器件区1A的PMOS区(150p)的第一注入窗口,以及,对准所述第二CMOS器件区2的NMOS区(260n)的第二注入窗口。

本实施例中,在所述半导体衬底100上首先形成掩埋上述所述各个CMOS器件区的PMOS管和NMOS管的第一光刻胶层,然后,通过工作电压为1.5V的正常阈值电压CMOS器件区1A的PMOS管的PLDD光罩,对所述第一光刻胶进行曝光、显影,从而形成暴露出正常阈值电压CMOS器件区的PMOS区(150p)的第一注入窗口和暴露出第二CMOS器件区的NMOS区(260n)的第二注入窗口。由于本发明实施例中,通过将工作电压为1.5V的正常阈值电压CMOS器件区1A的PMOS管的PLDD光罩进行了改进,使其在形成第一注入窗口的同时,形成暴露出第二CMOS器件区的NMOS区(260n)的第二注入窗口,进而可以省去形成第二CMOS器件区的NMOS区(260n)的晕环离子注入区的光罩,以达到对工作电压为3.3V的第二CMOS器件区的光罩进行减版的目的。进一步的,由于通过本发明提供的CMOS集成器件的制造方法在制造CMOS器件的过程中,工作电压为1.5V的正常阈值电压CMOS器件区的PMOS管与工作电压为3.3V的CMOS器件区的NMOS管共用一套PLDD光罩,实现对3.3V的CMOS器件的光罩减版;因此,节省了多次光刻、离子注入等工艺步骤,从而在节约了生产成本和提高了生产效率,还可以有效提高晶圆厂和客户的竞争力。

在步骤S400中,具体参考图2c所示,以所述第一光刻胶层120和所述栅极结构(150p和260n)为掩膜,采用P型离子对所述第一注入窗口和所述第二注入窗口下方的半导体衬底100进行离子注入,以在所述正常阈值电压CMOS器件区的PMOS区(150p)中形成第一P型浅掺杂离子注入区151,在所述第二CMOS器件区的NMOS区(260n)中形成第一P型晕环离子注入区261。

其中,所述P型离子可以包括硼、铟和镓中的至少一种,并且,所述P型离子注入的注入能量为:150KeV~190KeV,注入剂量为1E13~8E13,且所述进行如上注入工艺的晶圆的倾斜角度为15°~60°,所述晶圆在离子注入过程中的旋转角度可以为30°~180°。

本实施例中,在上述步骤S300通过共享工作电压为1.5V的正常阈值电压CMOS器件区的PMOS区的PLDD光罩的方式,形成所述第一注入窗口和第二注入窗口之后,采用P型离子对所述第一注入窗口和所述第二注入窗口下方的半导体衬底100进行离子注入,以在所述正常阈值电压CMOS器件区的PMOS区(150p)两侧的半导体衬底100中形成第一P型浅掺杂离子注入区151,以及在所述第二CMOS器件区的NMOS区(260n)两侧的半导体衬底100中形成第一P型晕环离子注入区261。

此外,目前针对不同工作电压的CMOS器件,为了热电子注入效应HCI,通常需要在每个CMOS器件的MOS管两侧的半导体衬底中分别形成浅掺杂离子注入区LDD和晕环离子注入区Pocket。因此,在执行完上述步骤S400之后,可以再对所述第一注入窗口和第二注入窗口进行N型离子注入,以在所述正常阈值电压CMOS器件区的PMOS区(150p)两侧的半导体衬底100中形成N型晕环离子注入区152,同时在第二CMOS器件区的NMOS区(260n)两侧的半导体衬底100中形成N型浅掺杂离子注入区262。

在步骤S500中,具体参考图2d所示,去除所述第一光刻胶层120,并在所述半导体衬底100的表面上形成图形化的第二光刻胶层130,所述第二光刻胶层130中形成有对准所述低阈值电压CMOS器件区1B的PMOS区(140p)的第三注入窗口,以及,对准所述第三CMOS器件区3的NMOS区(370n)的第四注入窗口。

在步骤S600中,继续参考图2d所示,以所述第二光刻胶层130和所述栅极结构(140p和370n)为掩膜,采用N型离子对所述第三注入窗口和所述第四注入窗口下方的半导体衬底100进行离子注入,以在所述低阈值电压CMOS器件区1B的PMOS区(140p)中形成第一N型晕环离子注入区141,在所述第三CMOS器件区3的NMOS区中形成第一N型浅掺杂离子注入区371。

其中,所述N型离子包括磷、砷和锑中的至少一种,并且,所述N型离子注入的注入能量为:90KeV~130KeV,注入剂量为1E13~9E13,且所述进行如上注入工艺的晶圆的倾斜角度为15°~60°,所述晶圆在离子注入过程中的旋转角度可以为30°~180°。

本实施例中,由于通过步骤S600采用改良后的第一CMOS器件区中工作电压为1.5V的低阈值电压PMOS管(140p)的晕环离子注入光罩,在打开第一CMOS器件区1B中低阈值电压PMOS管(140p)所在区域(第三注入窗口)的同时打开第三CMOS器件区3的NMOS管(370n)所在区域(第四注入窗口),因此,在通过对所述第三注入窗口进行离子注入,形成低阈值电压PMOS管(140p)的第一N型晕环离子注入区的同时在所述第四注入窗口对应的半导体衬底100上形成第三CMOS器件区3的NMOS管(370n)的N型浅掺杂离子注入区,从而在提升所述NMOS管(370n)的HCL性能的同时,节省了一道形成第三CMOS器件区3的NMOS管的浅掺杂离子注入LDD光罩,进而节约了CMOS集成器件的生产成本、提高了生产效率。

同理,在执行完上述步骤S600中之后,还可以对所述第三注入窗口和第四注入窗口进行P型离子注入,从而在所述低阈值电压CMOS器件区1B的PMOS区(140p)两侧的半导体衬底100中形成P型浅掺杂离子注入区142,以对所述低阈值电压CMOS器件区1B的PMOS区(140p)的阈值电压和饱和电流进行调整,使其满足设计要求,并同时在所述第三CMOS器件区3的NMOS区(370n)中形成P型晕环离子注入区372。

由于通过本发明提供的CMOS集成器件的制造方法在制造CMOS器件的过程中,先是工作电压为1.5V的正常阈值电压CMOS器件区的PMOS管与工作电压为3.3V的CMOS器件区的NMOS管共用一套PLDD光罩,实现对3.3V的CMOS器件的光罩减版;之后,在通过将工作电压为1.5V的低阈值电压CMOS器件区的PMOS管与工作电压为5V的CMOS器件区的NMOS管共用一套N型Pocket光罩,实现对5V的CMOS器件的光罩减版,即,通过多次光罩减版的方式,节省了多次光刻、离子注入等工艺步骤,从而在节约了生产成本和提高了生产效率,还可以有效提高晶圆厂和客户的竞争力。

进一步的,在形成所述第一N型晕环离子注入区141和所述第一N型浅掺杂离子注入区371之后,或者,在形成所述栅极结构之后且在形成所述第一光刻胶层120之前,本发明提供的CMOS集成器件的制造方法还可以包括如下步骤:

首先,在所述半导体衬底100的表面上形成图形化的第三光刻胶层(未图示),所述第三光刻胶层中形成有对准所述正常阈值电压CMOS器件区1A的NMOS区(140n)的第五注入窗口,以及,对准所述第二CMOS器件区2的PMOS区(260p)的第六注入窗口;

接着,以所述第三光刻胶层和所述栅极结构为掩膜,采用N型离子对所述第五注入窗口和所述第六注入窗口下方的半导体衬底100进行离子注入,以在所述正常阈值电压CMOS器件区1A的NMOS区(140n)中形成第二N型浅掺杂离子注入区(未图示),在所述第二CMOS器件区2的PMOS区(260p)中形成第二N型晕环离子注入区(未图示);

其次,去除所述第三光刻胶层,并在所述半导体衬底100的表面上形成图形化的第四光刻胶层(未图示),所述第四光刻胶层中形成有对准所述低阈值电压CMOS器件区1B的NMOS区(140n)的第七注入窗口,以及,对准所述第三CMOS器件区3的PMOS区(370p)的第八注入窗口;

最后,以所述第三光刻胶层和所述栅极结构为掩膜,采用P型离子对所述第七注入窗口和所述第八注入窗口下方的半导体衬底100进行离子注入,以在所述低阈值电压CMOS器件区1B的NMOS区(140n)中形成第二P型晕环离子注入区(未图示),在所述第三CMOS器件区3的PMOS区(370p)中形成第二P型浅掺杂离子注入区(未图示)。

本实施例中,在采用上述步骤S100-步骤S600形成CMOS集成器件的过程中,只是对半导体衬底100上形成的三个CMOS器件区中的部分PMOS或者NMOS器件进行了离子注入,从而在其两侧形成相应的浅掺杂离子注入区和晕环离子注入区。因此,还需在上述步骤之后,采用如上所述的方法在其他剩余的部分的PMOS或者NMOS器件进行了离子注入,从而在其两侧形成相应的浅掺杂离子注入区和晕环离子注入区,由于此形成过程与上述步骤S100-步骤S600描述的方法相同,在此不做累述。

进一步的,在形成各个所述PMOS区和所述NMOS区所需的浅掺杂离子注入区之后,在各个所述栅极结构的侧壁上分别形成侧墙(未图示)。

进一步的,在形成所述侧墙之后,以所述侧墙和所述栅极结构为掩膜,在各个所述栅极结构两侧的半导体衬底100内形成源区(未图示)和漏区(未图示)。

综上所述,在本发明提供的CMOS集成器件的制造方法中,通过采用改良后的第一CMOS器件区中的低阈值电压PMOS管的晕环离子注入光罩,在打开第一CMOS器件区中低阈值电压PMOS管所在区域(第三注入窗口)的同时打开第三CMOS器件区的NMOS管所在区域(第四注入窗口),因此,在通过对所述第三注入窗口进行离子注入,形成低阈值电压PMOS管的第一N型晕环离子注入区的同时在所述第四注入窗口对应的半导体衬底上形成第三CMOS器件区的NMOS管的N型浅掺杂离子注入区,从而节省了一道形成第三CMOS器件区的NMOS管的浅掺杂离子注入光罩,进而节约了CMOS集成器件的生产成本、提高了生产效率。

进一步的,由于通过本发明提供的CMOS集成器件的制造方法在制造CMOS器件的过程中,先是工作电压为1.5V的正常阈值电压CMOS器件区的PMOS管与工作电压为3.3V的CMOS器件区的NMOS管共用一套PLDD光罩,实现对3.3V的CMOS器件的光罩减版;之后,在通过将工作电压为1.5V的低阈值电压CMOS器件区的PMOS管与工作电压为5V的CMOS器件区的NMOS管共用一套N型Pocket光罩,实现对5V的CMOS器件的光罩减版,即,通过多次光罩减版的方式,节省了多次光刻、离子注入等工艺步骤,从而在节约了生产成本和提高了生产效率,还可以有效提高晶圆厂和客户的竞争力。

需要说明的是,虽然本发明已以较佳实施例披露如上,然而上述实施例并非用以限定本发明。对于任何熟悉本领域的技术人员而言,在不脱离本发明技术方案范围情况下,都可利用上述揭示的技术内容对本发明技术方案作出许多可能的变动和修饰,或修改为等同变化的等效实施例。因此,凡是未脱离本发明技术方案的内容,依据本发明的技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均仍属于本发明技术方案保护的范围。

还应当理解的是,除非特别说明或者指出,否则说明书中的术语“第一”、“第二”、“第三”等描述仅仅用于区分说明书中的各个组件、元素、步骤等,而不是用于表示各个组件、元素、步骤之间的逻辑关系或者顺序关系等。

此外还应该认识到,此处描述的术语仅仅用来描述特定实施例,而不是用来限制本发明的范围。必须注意的是,此处的以及所附权利要求中使用的单数形式“一个”和“一种”包括复数基准,除非上下文明确表示相反意思。例如,对“一个步骤”或“一个装置”的引述意味着对一个或多个步骤或装置的引述,并且可能包括次级步骤以及次级装置。应该以最广义的含义来理解使用的所有连词。以及,词语“或”应该被理解为具有逻辑“或”的定义,而不是逻辑“异或”的定义,除非上下文明确表示相反意思。此外,本发明实施例中的方法和/或设备的实现可包括手动、自动或组合地执行所选任务。

- 应变Ge CMOS集成器件的制备方法及其CMOS集成器件

- BiCMOS集成电路器件的制造方法及器件