使用DCT2启用高层级标志的编码器、解码器和对应方法

文献发布时间:2023-06-19 11:21:00

相关申请案的交叉参考

本专利申请要求于2019年1月11日提交的申请号为62/791,674的美国临时专利申请的优先权,上述专利申请的公开内容通过全文引用的方式并入本文中。

技术领域

本申请(发明)的实施例大体涉及图像处理领域,更具体,涉及根据块形状自适应地选择变换类型的高层级控制。

背景技术

视频译码(视频编码和/或视频解码)广泛用于数字视频应用,例如广播数字电视、基于互联网和移动网络的视频传输、视频聊天、视频会议等实时会话应用、DVD和蓝光光盘、视频内容采集和编辑系统以及安全应用的可携式摄像机。

即使在视频较短的情况下也需要对大量的视频数据进行描述,当数据要在带宽容量受限的通信网络中发送或以其它方式发送时,这样可能会造成困难。因此,视频数据通常要先压缩然后在现代电信网络中发送。由于内存资源可能有限,当在存储设备中存储视频时,视频的大小也可能成为问题。视频压缩设备通常在信源侧使用软件和/或硬件,以在发送或存储之前对视频数据进行译码,从而减少用来表示数字视频图像所需的数据量。然后,压缩数据在目的地侧由用于对视频数据进行解码的视频解压缩设备接收。在有限的网络资源以及对更高视频质量的需求不断增长的情况下,需要改进压缩和解压缩技术,这些改进的技术能够在几乎不影响图像质量的情况下提高压缩比。

在VVC草稿3.0的草稿文本JVET-L1001中,MTS可以在序列层级中分别针对帧间和帧内条带启用。当禁用MTS时,DCT2应该作为变换核。然而,在JVET-M0303、JVET-M0140或JVET-M0102等现有技术中,引入了推断的DST7/DCT8变换。在所有情况下都不可能切换到纯DCT2变换。本发明解决了上述问题。

鉴于上述问题,本发明提供了一种缓解甚至消除上述问题的技术方案。

本发明的实施例由独立权利要求的特征定义,并且实施例的其它有利实现方式由从属权利要求的特征定义。

本发明提供:

一种对图像块进行视频译码的方法,包括:对于所述块的多个像素点中的一个像素点,

获取由帧间预测或帧内预测产生的残差信号;

推断对所述残差信号的序列使用离散余弦变换类型2(Discrete CosineTransform type 2,DCT2)变换核;

使用所述推断的变换核处理所述块的变换。

也就是说,本发明引入了其它DCT2启用标志,用于推断针对序列中的所有情况是否仅使用DCT2变换核,当DCT2启用标志为假(false)时,进一步指示序列层级MTS启用标志。当DCT2启用标志为真(true)时,应该仅使用DCT2变换核。在SPS中引入其它DCT2启用标志,从而在启用推断的MST工具时能够切换到DCT2。

根据上述方面,在所述方法的一种可能实现方式中,DCT2的使用是根据序列参数集(Sequence Parameter Set,SPS)中的序列层级DCT2启用标志推断的。

因此,本发明的实施例引入了可切换DCT2启用序列层级指示符,从而可能对于整个序列或条带,使用推断的变换工具切换到纯DCT2变换核。相比其它变换核,DCT2的计算相对简单,内存带宽较小。在现有技术中,使用简单DCT2变换的可能性被推断的变换核切断,本发明中的指示符使编码器和解码器能够在低成本/复杂性与高性能之间灵活切换。在实施例中,既提供了低层级变化可能性,又提供了高层级变化可能性,从而保证在多种变化下代码的一致性和译码性能。

根据上述方面,在所述方法的一种可能实现方式中,所述序列层级DCT2启用标志表示为sps_dct2_enabled_flag。

根据上述两个方面或上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,所述序列层级DCT2启用标志包含在如下SPS层级语法中:

其中,sps_dct2_enabled_flag表示所述序列层级DCT2启用标志。

根据上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,所述sps_mts_intra_enabled_flag等于1表示帧内译码单元的残差译码语法中可以存在tu_mts_flag;sps_mts_intra_enabled_flag等于0表示帧内译码单元的所述残差译码语法中不存在tu_mts_flag;当所述sps_mts_intra_enabled_flag不存在时,所述sps_mts_intra_enabled_flag被推断为0。

根据上述两个方面或上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,所述sps_mts_inter_enabled_flag表示帧间译码单元的所述残差译码语法中可以存在tu_mts_flag;sps_mts_inter_enabled_flag等于0表示帧间译码单元的所述残差译码语法中不存在tu_mts_flag;当所述sps_mts_intra_enabled_flag不存在时,所述sps_mts_intra_enabled_flag被推断为0。

根据上述五个方面或上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,

所述序列层级DCT2启用标志等于1表示使用DCT2变换核进行变换。

根据上述六个方面或上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,

所述序列层级DCT2启用标志等于1表示仅使用DCT2变换核进行变换。

根据上述七个方面或上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,所述序列层级DCT2启用标志等于1表示使用DCT2进行水平方向和垂直方向变换。

根据上述八个方面或上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,所述序列层级DCT2启用标志等于1表示使用DCT2进行子块变换。

根据上述方面,在所述方法的一种可能实现方式中,如果残差变换单元(Transform Unit,TU)的一个边大于32,则对应的变换被设置为DCT2。

根据上述十个方面或上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,如果所述序列层级DCT2启用标志等于1,表示仅使用所述DCT2变换核进行变换,则所述子块变换和多变换模式选择(Multiple Transform Selection,MTS)变换被推断禁用。

根据上述十一个方面或上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,

所述序列层级DCT2启用标志等于0表示使用除DCT2之外的其它变换核进行所述变换。

根据上述方面,在所述方法的一种可能实现方式中,

推断使用离散正弦变换类型7(Discrete Sine Transform type 7,DST7)和/或离散余弦变换类型8(Discrete Cosine Transform type 8,DCT8)进行变换。

根据两个上述方面或上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,所述序列层级DCT2启用标志等于0表示推断仅使用DST7/DCT8进行变换。

DCT2可以是编码器和解码器设计十分理想的选择。换言之,本发明的目的之一是实现DCT2、推断的DST7或DCT8以及MTS(RDO选择的变换核)之间的可切换性。

根据上述三个方面或上述方面的任一上述实现方式,在所述方法的一种可能实现方式中,

如果所述序列层级DCT2启用标志等于0,则通过标志确定是否启用序列参数集的多变换模式选择。

根据上述方面,在所述方法的一种可能实现方式中,

如果所述sps_mts_intra_enabled_flag存在,则

如果所述sps_mts_intra_enabled_flag等于1,则表示帧内译码单元的所述残差译码语法中存在变换单元(Transform Unit,TU)多变换模式选择(Multiple TransformSelection,MTS)标志,表示为tu_mts_flag;

如果所述sps_mts_intra_enabled_flag等于0,则表示帧内译码单元的所述残差译码语法中不存在tu_mts_flag;

如果所述sps_mts_intra_enabled_flag不存在,则所述sps_mts_intra_enabled_flag被推断为0。

本发明还提供一种编码器,包括处理电路,用于执行上述方面或上述方面的任一上述实现方式提供的方法。

本发明还提供一种解码器,包括处理电路,用于执行上述方面或上述方面的任一上述实现方式提供的方法。

本发明还提供一种解码器,包括:

获取单元,用于获取由帧间预测或帧内预测产生的残差信号;

推断单元,用于推断对所述残差信号的序列使用离散余弦变换类型2(DiscreteCosine Transform type 2,DCT2)变换核;

处理单元,用于使用所述推断的变换核处理所述块的变换。

根据上述方面,在所述解码器的一种可能实现方式中,所述推断单元用于根据序列参数集(Sequence Parameter Set,SPS)中的序列层级DCT2启用标志推断DCT2的使用。

根据上述方面,在所述解码器的一种可能实现方式中,所述序列层级DCT2启用标志表示为sps_dct2_enabled_flag。

根据上述两个方面或上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,所述序列层级DCT2启用标志包含在如下SPS层级语法中:

其中,sps_dct2_enabled_flag表示所述序列层级DCT2启用标志。

根据上述方面,在所述解码器的一种可能实现方式中,所述sps_mts_intra_enabled_flag等于1表示在帧内译码单元的残差译码语法中可以存在tu_mts_flag;sps_mts_intra_enabled_flag等于0表示帧内译码单元的所述残差译码语法中不存在tu_mts_flag;当所述sps_mts_intra_enabled_flag不存在时,所述sps_mts_intra_enabled_flag被推断为0。

根据上述两个方面或上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,所述sps_mts_inter_enabled_flag表示帧间译码单元的所述残差译码语法中可以存在tu_mts_flag;sps_mts_inter_enabled_flag等于0表示帧间译码单元的所述残差译码语法中不存在tu_mts_flag;当所述sps_mts_intra_enabled_flag不存在时,所述sps_mts_intra_enabled_flag被推断为0。

根据上述五个方面或上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,

所述序列层级DCT2启用标志等于1表示使用DCT2变换核进行变换。

根据上述六个方面或上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,

所述序列层级DCT2启用标志等于1表示仅使用DCT2变换核进行变换。

根据上述七个方面或上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,所述序列层级DCT2启用标志等于1表示使用DCT2进行水平方向和垂直方向变换。

根据上述八个方面或上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,所述序列层级DCT2启用标志等于1表示使用DCT2进行子块变换。

根据上述方面,在所述解码器的一种可能实现方式中,如果残差变换单元(Transform Unit,TU)的一个边大于32,则对应的变换被设置为DCT2。

根据上述十个方面或上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,如果所述序列层级DCT2启用标志等于1,表示仅使用所述DCT2变换核进行变换,则所述子块变换和多变换模式选择(Multiple Transform Selection,MTS)变换被推断禁用。

根据上述十一个方面或上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,

所述序列层级DCT2启用标志等于0表示使用除DCT2之外的其它变换核进行所述变换。

根据上述方面,在所述解码器的一种可能实现方式中,

所述推断单元用于推断使用离散正弦变换类型7(Discrete Sine Transformtype 7,DST7)和/或离散余弦变换类型8(Discrete Cosine Transform type 8,DCT8)进行变换。

根据上述两个方面或上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,所述序列层级DCT2启用标志等于0表示推断仅使用DST7/DCT8进行变换。

根据上述三个方面或上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,

如果所述序列层级DCT2启用标志等于0,则通过标志确定是否启用序列参数集的多变换模式选择。

根据上述方面的任一上述实现方式,在所述解码器的一种可能实现方式中,

当所述sps_mts_intra_enabled_flag存在时,

如果所述sps_mts_intra_enabled_flag等于1,则表示帧内译码单元的所述残差译码语法中存在变换单元(Transform Unit,TU)多变换模式选择(Multiple TransformSelection,MTS)标志,表示为tu_mts_flag;

如果所述sps_mts_intra_enabled_flag等于0,则表示在帧内译码单元的所述残差译码语法中不存在tu_mts_flag;

如果所述sps_mts_intra_enabled_flag不存在,则所述sps_mts_intra_enabled_flag被推断为0。

本发明还提供一种编码器,包括:

获取单元,用于获取由帧间预测或帧内预测产生的残差信号;

推断单元,用于推断对所述残差信号的序列使用离散余弦变换类型2(DiscreteCosine Transform type 2,DCT2)变换核;

处理单元,用于使用所述推断的变换核处理所述块的变换。

根据上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,所述推断单元用于从序列参数集(Sequence Parameter Set,SPS)中的序列层级DCT2启用标志推断DCT2的使用。

根据上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,所述序列层级DCT2启用标志表示为sps_dct2_enabled_flag。

根据上述两个方面或上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,所述序列层级DCT2启用标志包含在如下SPS层级语法中:

其中,sps_dct2_enabled_flag表示所述序列层级DCT2启用标志。

根据上述方面,在所述编码器的一种可能实现方式中,所述sps_mts_intra_enabled_flag等于1表示在帧内译码单元的残差译码语法中可以存在tu_mts_flag;sps_mts_intra_enabled_flag等于0表示帧内译码单元的所述残差译码语法中不存在tu_mts_flag;当所述sps_mts_intra_enabled_flag不存在时,所述sps_mts_intra_enabled_flag被推断为0。

根据上述两个方面或上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,所述sps_mts_inter_enabled_flag表示帧间译码单元的所述残差译码语法中可以存在tu_mts_flag;sps_mts_inter_enabled_flag等于0表示帧间译码单元的所述残差译码语法中不存在tu_mts_flag;当所述sps_mts_intra_enabled_flag不存在时,所述sps_mts_intra_enabled_flag被推断为0。

根据上述五个方面或上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,

所述序列层级DCT2启用标志等于1表示使用DCT2变换核进行变换。

根据上述六个方面或上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,

所述序列层级DCT2启用标志等于1表示仅使用DCT2变换核进行变换。

根据上述七个方面或上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,所述序列层级DCT2启用标志等于1表示使用DCT2进行水平方向和垂直方向变换。

根据上述八个方面或上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,所述序列层级DCT2启用标志等于1表示使用DCT2进行子块变换。

根据上述方面,在所述编码器的一种可能实现方式中,如果残差变换单元(Transform Unit,TU)的一个边大于32,则对应的变换被设置为DCT2。

根据上述十个方面或上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,如果所述序列层级DCT2启用标志等于1,表示仅使用所述DCT2变换核进行变换,则所述子块变换和多变换模式选择(Multiple Transform Selection,MTS)变换被推断禁用。

根据上述十一个方面或上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,

所述序列层级DCT2启用标志等于0表示使用除DCT2之外的其它变换核进行所述变换。

根据上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,

所述推断单元用于推断使用离散正弦变换类型7(Discrete Sine Transformtype 7,DST7)和/或离散余弦变换类型8(Discrete Cosine Transform type 8,DCT8)进行变换。

根据上述两个方面或上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,所述序列层级DCT2启用标志等于0表示推断仅使用DST7/DCT8进行变换。

根据上述三个方面或上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,

如果所述序列层级DCT2启用标志等于0,则通过标志确定是否启用序列参数集的多变换模式选择。

根据上述方面的任一上述实现方式,在所述编码器的一种可能实现方式中,

当所述sps_mts_intra_enabled_flag存在时,

如果所述sps_mts_intra_enabled_flag等于1,则表示帧内译码单元的所述残差译码语法中存在变换单元(Transform Unit,TU)多变换模式选择(Multiple TransformSelection,MTS)标志,表示为tu_mts_flag;

如果所述sps_mts_intra_enabled_flag等于0,则表示在帧内译码单元的所述残差译码语法中不存在tu_mts_flag;

如果所述sps_mts_intra_enabled_flag不存在,则所述sps_mts_intra_enabled_flag被推断为0。

本发明还提供一种计算机程序产品,包括程序代码,用于执行上述方面或上述方面的任一上述实现方式提供的方法。

本发明还提供一种解码器,包括:

一个或多个处理器;

非瞬时性计算机可读存储介质,与所述处理器耦合并存储由所述处理器执行的程序,其中,当所述处理器执行所述程序时,所述解码器用于执行上述方面或上述方面的任一上述实现方式提供的方法。

本发明还提供一种编码器,包括:

一个或多个处理器;

非瞬时性计算机可读存储介质,与所述处理器耦合并存储由所述处理器执行的程序,其中,当所述处理器执行所述程序时,所述编码器用于执行上述方面或上述方面的任一上述实现方式提供的方法。

本发明还提供一种存储程序的计算机可读非瞬时性介质,包括指令,当所述指令在处理器中执行时,所述处理器执行上述方面或上述方面的任一上述实现方式提供的方法。

附图说明

下文结合附图对本发明实施例进行详细描述。在附图中:

图1A为用于实现本发明实施例的视频译码系统的一个示例的框图;

图1B为用于实现本发明实施例的视频译码系统的另一示例的框图;

图2为用于实现本发明实施例的视频编码器示例的框图;

图3为用于实现本发明实施例的视频解码器的示例性结构的框图;

图4为示出编码装置或解码装置的一个示例的框图;

图5为示出编码装置或解码装置的另一示例的框图;

图6为每个SBT位置的水平和垂直变换的一个示例的框图;

图7为每个SBT位置的水平和垂直变换的另一示例的框图;

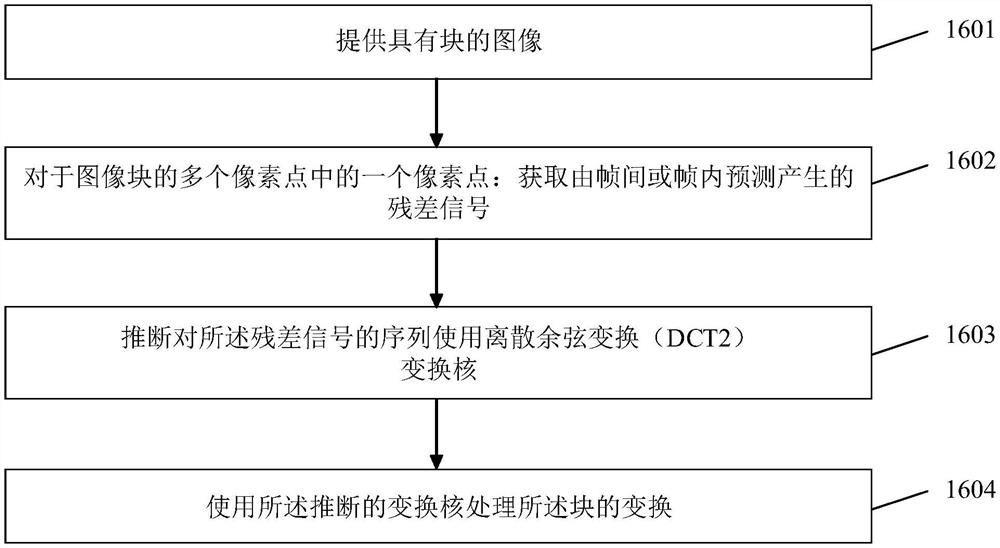

图8示出了本发明提供的对图像块进行视频译码的方法;

图9示出了编码器;

图10示出了解码器;

在下文中,除非另外明确说明,否则相同的附图标记是指相同或至少功能上等效的特征。

具体实施方式

以下描述中,参考形成本发明一部分并以说明的方式示出本发明实施例的具体方面或可以使用本发明实施例的具体方面的附图。应理解,本发明实施例可以在其它方面中使用,并且可以包括附图中未描绘的结构或逻辑变化。因此,以下详细描述不应以限制性的意义来理解,本发明的范围由所附权利要求书界定。

例如,应理解,结合所描述方法的公开内容对用于执行所述方法的对应设备或系统也可以同样适用,反之亦然。例如,如果描述一个或多个具体方法步骤,则对应的设备可以包括一个或多个单元(例如,功能单元)来执行所描述的一个或多个方法步骤(例如,一个单元执行一个或多个步骤,或多个单元分别执行多个步骤中的一个或多个),即使附图中未明确描述或说明该一个或多个单元。另一方面,例如,如果根据一个或多个单元(例如,功能单元)来描述具体装置,则对应的方法可以包括一个步骤来实现一个或多个单元的功能(例如,一个步骤实现一个或多个单元的功能,或多个步骤分别实现多个单元中一个或多个单元的功能),即使附图中未明确描述或说明该一个或多个步骤。此外,应理解,除非另有说明,否则本文中描述的各种示例性实施例和/或方面的特征可相互组合。

视频译码通常指对构成视频或视频序列的图像序列进行处理。在视频译码领域中,术语“帧(frame)”与“图像(picture/image)”可以用作同义词。视频译码(或通常为译码)包括视频编码和视频解码两部分。视频编码在源侧执行,通常包括处理(例如,压缩)原始视频图像以减少表示视频图像所需的数据量(从而更高效存储和/或发送)。视频解码在目的地侧执行,通常包括相对于编码器作逆处理,以重建视频图像。实施例涉及的视频图像(或通常称为图像)的“译码”应理解为涉及视频图像或相应视频序列的“编码”或“解码”。编码部分和解码部分的组合也称为编解码(编码和解码,CODEC)。

在无损视频译码情况下,可以重建原始视频图像,即重建的视频图像与原始视频图像具有相同的质量(假设存储或传输期间没有传输损耗或其它数据丢失)。在有损视频译码情况下,通过量化等进行进一步压缩来减少表示视频图像所需的数据量,而解码器侧无法完全重建视频图像,即重建的视频图像的质量比原始视频图像的质量更低或更差。

几个视频译码标准属于“有损混合视频编解码器”组(即,将像素点域中的空间预测和时间预测与变换域中用于应用量化的2D变换译码结合)。视频序列中的每个图像通常分割成不重叠的块集合,通常基于块级进行译码。换句话说,编码器通常在块(视频块)级对视频进行处理,即编码,例如,通过空间(帧内)预测和/或时间(帧间)预测来生成预测块;从当前块(当前处理/待处理的块)中减去预测块,获得残差块;在变换域中变换残差块并量化残差块,以减少待发送(压缩)的数据量,而解码器将相对于编码器的逆处理应用于经编码或压缩的块,以重建用于表示的当前块。此外,编码器重复解码器的处理步骤,使得编码器和解码器生成相同的预测(例如,帧内预测和帧间预测)和/或重建,用于对后续块进行处理(即译码)。

在以下实施例中,根据图1至图3描述了视频译码系统10、视频编码器20和视频解码器30。

图1A为示意性框图,示出了示例性译码系统10,例如可以利用本申请技术的视频译码系统10(或简称为译码系统10)。视频译码系统10中的视频编码器20(或简称为编码器20)和视频解码器30(或简称为解码器30)代表可用于根据本申请中描述的各种示例执行各技术的设备的示例。

如图1A所示,译码系统10包括源设备12,例如,所述源设备12用于将经编码的图像数据21提供到目的地设备14以对经编码的图像数据13进行解码。

源设备12包括编码器20,并且可以另外(即可选地)包括图像源16、预处理器(或预处理单元)18(例如图像预处理器18)和通信接口或通信单元22。

图像源16可以包括或可以是任何类型的图像捕获设备,例如用于捕获真实世界图像的摄像机,和/或任何类型的图像生成设备,例如用于生成计算机动画图像的计算机图形处理器,或用于获取和/或提供真实世界图像、计算机生成图像(例如,屏幕内容、虚拟现实(virtual reality,VR)图像)和/或其任何组合(例如,增强现实(augmented reality,AR)图像)的任何类型的其它设备。所述图像源可以为存储任一上述图像的任何类型的存储器(memory/storage)。

区别于预处理器18和预处理单元18执行的处理,图像或图像数据17也可以称为原始图像或原始图像数据17。

预处理器18用于接收(原始)图像数据17,对图像数据17进行预处理,以获得经预处理的图像19或经预处理的图像数据19。例如,预处理器18执行的预处理可包括修剪(trimming)、颜色格式转换(例如从RGB转换为YCbCr)、调色或去噪。可以理解的是,预处理单元18可以为可选组件。

视频编码器20用于接收经预处理的图像数据19并提供经编码的图像数据21(例如,下文根据图2进一步详细描述)。

源设备12的通信接口22可用于接收经编码的图像数据21并通过通信信道13将经编码的图像数据21(或其任何其它经处理版本)发送到其它设备,例如目的地设备14或用于存储或直接重建的任何其它设备。

目的地设备14包括解码器30(例如,视频解码器30),并且可以另外(即,可选地)包括通信接口或通信单元28、后处理器32(或后处理单元32)和显示设备34。

目的地设备14的通信接口28用于接收经编码的图像数据21(或其任何其它经处理版本),例如,直接从源设备12或任何其它源(例如,编码图像数据存储设备等存储设备)接收,并将经编码的图像数据21提供给解码器30。

通信接口22和通信接口28可以用于通过源设备12与目的地设备14之间的直接通信链路(例如,直接有线或无线连接),或通过任何类型的网络(例如,有线或无线网络或其任意组合,或任何类型的专用和公共网络),或其任意组合发送或接收经编码的图像数据21或编码数据13。

例如,通信接口22可用于将经编码的图像数据21封装为数据包等合适的格式,和/或采用任何类型的发送编码或处理来处理所述经编码的图像数据,以便通过通信链路或通信网络进行发送。

例如,与通信接口22对应的通信接口28可以用于接收传输数据并通过任何类型的对应传输解码或处理和/或解封装方式来处理传输数据,得到经编码的图像数据21。

通信接口22和通信接口28均可配置为单向通信接口(如图1A中从源设备12指向目的地设备14的通信信道13的箭头所表示),或双向通信接口,并可用于发送和接收消息等,例如,建立连接,确认和交互与通信链路和/或数据传输(例如,经编码的图像数据传输)相关的任何其它信息。

解码器30用于接收经编码的图像数据21并提供经解码的图像数据31或经解码图像31(例如,下文根据图3或图5进一步详细描述)。目的地设备14的后处理器32用于对经解码的图像数据31(也称为重建图像数据)(例如,经解码图像31)进行后处理,以获得经后处理的图像数据33(例如,后处理图像33)。例如,由后处理单元32执行的后处理可以包括颜色格式转换(例如从YCbCr转换为RGB)、颜色校正、修剪或重采样,或任何其它处理,例如,用于准备经解码的图像数据31以供显示设备34等显示。

目的地设备14的显示设备34用于接收经后处理的图像数据33,以向用户或观看者等显示图像。显示设备34可以是或包括用于显示重建图像的任何类型的显示器,例如,集成或外部的显示器或监视器。例如,显示器可以包括液晶显示器(liquid crystal display,LCD)、有机发光二极管(organic light emitting diode,OLED)显示器、等离子显示器、投影仪、微型LED显示器、硅基液晶显示器(liquid crystal on silicon,LCoS)、数字光处理器(digital light processor,DLP)或任意类型的其它显示器。

尽管图1A示出了源设备12和目的地设备14作为单独的设备,但是在实施例中,设备还可以同时包括源设备12和目的地设备14或同时包括源设备12和目的地设备14的功能,即源设备12或对应功能以及目的地设备14或对应功能。在这类实施例中,源设备12或对应功能以及目的地设备14或对应功能可以使用相同的硬件和/或软件或通过单独的硬件和/或软件或其任意组合来实现。

根据描述,技术人员显而易见的是,图1A所示的源设备12和/或目的地设备14中的不同单元或功能的存在和(精确)划分可以根据实际设备和应用而不同。

编码器20(例如视频编码器20)或解码器30(例如视频解码器30),或编码器20和解码器30两者都可通过如图1B所示的处理电路实现,如一个或多个微处理器、数字信号处理器(digital signal processor,DSP)、专用集成电路(application-specific integratedcircuit,ASIC)、现场可编程门阵列(field-programmable gate array,FPGA)、离散逻辑、硬件、视频编码专用处理器或其任意组合。编码器20可以由处理电路46实现,以体现结合图2的编码器20所述的各种模块和/或本文描述的任何其它编码器系统或子系统。解码器30可以由处理电路46实现,以体现结合图3的解码器30所述的各种模块和/或本文描述的任何其它解码器系统或子系统。所述处理电路可用于执行下文描述的各种操作。如图5所示,如果所述技术部分地以软件形式实现,则设备可以将软件的指令存储在合适的非瞬时性计算机可读介质中,并且可以使用一个或多个处理器执行硬件中的指令,以执行本发明的技术。视频编码器20和视频解码器30中的任一个可作为组合编解码器(encoder/decoder,CODEC)的一部分集成在单个设备中,如图1B所示。

源设备12和目的地设备14可以包括多种设备中的任一种,包括任何类型的手持或固定设备,例如,笔记本电脑或膝上型电脑、手机、智能手机、平板电脑(tablet/tabletcomputer)、摄像机、台式计算机、机顶盒、电视机、显示设备、数字媒体播放器、视频游戏机、视频流设备(如内容服务服务器或内容分发服务器)、广播接收器设备、广播发射器设备等,并且可以不使用或使用任何类型的操作系统。在某些情况下,可以配备源设备12和目的地设备14以用于无线通信。因此,源设备12和目的地设备14可以是无线通信设备。

在某些情况下,图1A所示的视频译码系统10仅仅是示例,本申请的技术可适用于在编码设备与解码设备之间不一定包括任何数据通信的视频译码设置(例如,视频编码或视频解码)。在其它示例中,从本地存储器中检索数据,通过网络发送,等等。视频编码设备可以对数据进行编码并将数据存储到存储器中,和/或视频解码设备可以从存储器检索数据并对数据进行解码。在一些示例中,编码和解码由相互不通信而只是将数据编码到存储器和/或从存储器中检索数据并对数据进行解码的设备来执行。

为便于描述,本文参考由ITU-T视频译码专家组(Video Coding Experts Group,VCEG)和ISO/IEC运动图像专家组(Motion Picture Experts Group,MPEG)的视频译码联合工作组(Joint Collaboration Team on Video Coding,JCT-VC)开发的高效视频译码(High-Efficiency Video Coding,HEVC)或通用视频译码(Versatile Video Coding,VVC)(下一代视频译码标准)参考软件等描述本发明实施例。本领域的普通技术人员应理解本发明的实施例不限于HEVC或VVC。

编码器和编码方法

图2为用于实现本申请技术的示例性视频编码器20的示意性框图。在图2的示例中,视频编码器20包括输入端201(或输入接口201)、残差计算单元204、变换处理单元206、量化单元208、反量化单元210和逆变换处理单元212、重建单元214、环路滤波单元220、解码图像缓冲器(decoded picture buffer,DPB)230、模式选择单元260、熵编码单元270和输出端272(或输出接口272)。模式选择单元260可以包括帧间预测单元244、帧内预测单元254和分割单元262。帧间预测单元244可以包括运动估计单元和运动补偿单元(未示出)。图2所示的视频编码器20也可以称为混合视频编码器或基于混合视频编解码器的视频编码器。

残差计算单元204、变换处理单元206、量化单元208和模式选择单元260可以组成编码器20的正向信号路径,而反量化单元210、逆变换处理单元212、重建单元214、缓冲器216、环路滤波器220、解码图像缓冲器(decoded picture buffer,DPB)230、帧间预测单元244和帧内预测单元254可以组成视频编码器20的反向信号路径。视频编码器20的反向信号路径与解码器(参见图3中的视频解码器30)的信号路径对应。反量化单元210、逆变换处理单元212、重建单元214、环路滤波器220、解码图像缓冲器(decoded picture buffer,DPB)230、帧间预测单元244和帧内预测单元254还组成视频编码器20的“内置解码器”。

图像和图像分割(图像和块)

编码器20可用于通过输入端201等接收图像17(或图像数据17),例如,形成视频或视频序列的图像序列中的图像。接收的图像或图像数据也可以是经预处理的图像19(或经预处理的图像数据19)。为简单起见,以下描述使用图像17。图像17也可以称为当前图像或待译码图像(特别是在视频译码中,以便将当前图像与其它图像(例如,同一视频序列(即,也包括当前图像的视频序列)的先前编码和/或解码的图像)区分开)。

(数字)图像为或可以看作具有强度值的像素点的二维阵列或矩阵。阵列中的像素点也可以称为像素(pixel或pel)(图像元素的简称)。图像的大小和/或分辨率由阵列或图像在水平和垂直方向(或轴)上的像素点数量定义。通常采用三种颜色分量来表示颜色,即该图像可表示为三个像素点阵列或包括三个像素点阵列。在RGB格式或颜色空间中,图像包括对应的红色、绿色和蓝色像素点阵列。然而,在视频译码中,每个像素通常由亮度和色度格式或在颜色空间中表示,例如,YCbCr,包括Y表示的亮度分量(有时也用L表示)和Cb和Cr表示的两个色度分量。亮度(luminance,简称luma)分量Y表示亮度或灰度级强度(例如,像灰度图像),而两个色度(chrominance,简称chroma)分量Cb和Cr表示色度或颜色信息分量。因此,YCbCr格式的图像包括亮度像素点值(Y)的亮度像素点阵列和色度值(Cb和Cr)的两个色度像素点阵列。RGB格式的图像可转换或变换成YCbCr格式,反之亦然,该过程也称为颜色转换或颜色变换。如果图像是单色的,则该图像可以仅包括亮度像素点阵列。相应地,例如,图像可以为单色格式的亮度像素点阵列或4:2:0、4:2:2和4:4:4彩色格式的亮度像素点阵列和两个对应的色度像素点阵列。

视频编码器20的实施例可包括图像分割单元(图2中未示出),所述图像分割单元用于将图像17分割成多个(通常不重叠)图像块203。这些块也可以称为根块、宏块(H.264/AVC)或译码树块(coding tree block,CTB),或译码树单元(coding tree unit,CTU)(H.265/HEVC和VVC)。图像分割单元可用于对视频序列的所有图像使用相同的块大小和定义块大小的对应网格,或者用于改变图像或图像子集或组之间的块大小,并将每个图像分割成对应块。

在其它实施例中,视频编码器可以用于直接接收图像17的块203,例如组成图像17的一个、几个或所有块。图像块203也可以称为当前图像块或待译码图像块。

与图像17类似,图像块203同样是或可以看作是具有强度值(像素点值)的像素点的二维阵列或矩阵,但是,图像块203的尺寸比图像17小。换句话说,例如,根据所应用的颜色格式,块203可以包括一个像素点阵列(例如,图像17是单色情况下的亮度阵列,或图像17是彩色情况下的亮度或色度阵列)或三个像素点阵列(例如,图像17是彩色情况下的一个亮度阵列和两个色度阵列)或任何其它数量和/或类型的阵列。块203的水平方向和垂直方向(或轴线)上的像素点数量决定了块203的大小。因此,块可以为M×N(M列×N行)个像素点阵列,或M×N个变换系数阵列等。

图2所示的视频编码器20的实施例可以用于逐块对图像17进行编码,例如,按块203进行编码和预测。

图2所示的视频编码器20的实施例还可以用于使用条带(也称为视频条带)对图像进行分割和/或编码,其中,可以使用一个或多个条带(通常为不重叠的)对图像进行分割或编码,并且每个条带可以包括一个或多个块(例如,CTU)。

图2所示的视频编码器20的实施例还可以用于使用分块组(也称为视频分块组)和/或分块(也称为视频分块)对图像进行分割和/或编码,其中,可以使用一个或多个分块组(通常为不重叠的)对图像进行分割或编码,每个分块组可以包括一个或多个块(例如,CTU)或一个或多个分块等,其中,每个分块可以为矩形等形状,可以包括一个或多个块(例如,CTU),例如完整或部分块。

残差计算

残差计算单元204可用于通过如下等方式根据图像块203和预测块265(下文详细描述预测块265)来计算残差块205(也称为残差205):逐个像素点(逐个像素)从图像块203的像素点值中减去预测块265的像素点值,以获得像素点域中的残差块205。

变换

变换处理单元206可以用于对残差块205的像素点值执行离散余弦变换(discretecosine transform,DCT)或离散正弦变换(discrete sine transform,DST)等变换,得到变换域中的变换系数207。变换系数207也可以称为变换残差系数,表示变换域中的残差块205。

变换处理单元206可用于应用DCT/DST的整数化近似,如针对H.265/HEVC指定的变换。与正交DCT变换相比,这种整数化近似通常通过某一因子进行缩放。为了保持经过正变换和逆变换处理的残差块的范数,在变换过程中应用了其它缩放因子。缩放因子通常是根据某些约束条件来选择的,例如缩放因子是用于移位运算的2的幂、变换系数的位深度、准确性与实现成本之间的权衡等。例如,通过逆变换处理单元212等为逆变换(以及在视频解码器30侧通过逆变换处理单元312等为对应的逆变换)指定具体的缩放因子;相应地,可以在编码器20侧,通过变换处理单元206等为正变换指定对应的缩放因子。

视频编码器20(具体是变换处理单元206)的实施例可以用于直接或通过熵编码单元270编码或压缩等输出变换参数(例如,一种或多种变换的类型),使得例如视频解码器30可以接收并使用变换参数进行解码。

量化

量化单元208可以用于通过应用标量量化或矢量量化等对变换系数207进行量化,以获得量化系数209。量化系数209也可以称为量化变换系数209或量化残差系数209。

量化过程可减少与部分或全部变换系数207有关的位深度。例如,可以在量化期间将n位变换系数向下舍入到m位变换系数,其中n大于m。可以通过调整量化参数(quantization parameter,QP)修改量化程度。例如,对于标量量化,可以应用不同程度的缩放来实现较细或较粗的量化。较小量化步长对应较细量化,而较大量化步长对应较粗量化。可通过量化参数(quantization parameter,QP)表示合适的量化步长。例如,量化参数可以为合适的量化步长的预定义集合的索引。例如,较小的量化参数可对应精细量化(较小量化步长),较大的量化参数可对应粗糙量化(较大量化步长),反之亦然。量化可以包括除以量化步长,而反量化单元210等执行的对应和/或反解量化可以包括乘以量化步长。根据HEVC等一些标准的实施例可以使用量化参数来确定量化步长。通常,可以根据量化参数使用包括除法的等式的定点近似来计算量化步长。可以引入其它缩放因子来进行量化和解量化,以恢复可能由于在用于量化步长和量化参数的等式的定点近似中使用的缩放而修改的残差块的范数。在一种示例性实现方式中,可以合并逆变换和解量化的缩放。或者,可以使用自定义量化表并在码流中等将其从编码器向解码器指示。量化是有损操作,其中量化步长越大,损耗越大。

视频编码器20(具体是量化单元208)的实施例可以用于直接或通过熵编码单元270编码等输出量化参数(quantization parameter,QP),使得例如视频解码器30可以接收并使用量化参数进行解码。

反量化

反量化单元210用于通过根据或使用与量化单元208相同的量化步长应用量化单元208所应用的量化方案的逆过程等,对量化系数应用量化单元208的反量化,以获得解量化系数211。解量化系数211也可以称为解量化残差系数211,对应于变换系数207,但是由于量化造成的损耗,解量化系数211通常与变换系数不同。

逆变换

逆变换处理单元212用于应用变换处理单元206应用的变换的逆变换,例如,逆离散余弦变换(discrete cosine transform,DCT)或逆离散正弦变换(discrete sinetransform,DST)或其它逆变换,以获得像素点域中的重建残差块213(或对应的解量化系数213)。重建残差块213也可称为变换块213。

重建

重建单元214(例如,加法器或求和器214)用于例如通过将重建残差块213的像素点值和预测块265的像素点值逐个像素点相加,将变换块213(即重建残差块213)添加到预测块265,以获得像素点域中的重建块215。

滤波

环路滤波单元220(或简称“环路滤波器”220)用于对重建块215进行滤波以获得滤波块221,或通常用于对重建像素点进行滤波以获得滤波像素点。例如,环路滤波单元用于平滑像素转变或提高视频质量。环路滤波单元220可以包括一个或多个环路滤波器,如去块效应滤波器、像素点自适应偏移(sample-adaptive offset,SAO)滤波器或一个或多个其它滤波器,例如双边滤波器、自适应环路滤波器(adaptive loop filter,ALF)、锐化滤波器、平滑滤波器或协作滤波器或其任意组合。虽然环路滤波单元220在图2中示出为环内滤波器,但是在其它配置中,环路滤波单元220可以实现为后环路滤波器。滤波块221也可以称为滤波重建块221。

视频编码器20(具体是环路滤波单元220)的实施例可用于直接或通过熵编码单元270编码等输出环路滤波器参数(如像素点自适应偏移信息),使得例如解码器30可以接收和应用相同的环路滤波器参数或相应的环路滤波器进行解码。

解码图像缓冲器

解码图像缓冲器(decoded picture buffer,DPB)230可以是存储参考图像或通常用于由视频编码器20对视频数据进行编码的参考图像数据的存储器。DPB 230可以由多种存储设备中的任一种组成,如动态随机存取存储器(dynamic random access memory,DRAM),包括同步DRAM(synchronous DRAM,SDRAM)、磁阻RAM(magnetoresistive RAM,MRAM)、电阻RAM(resistive RAM,RRAM)或其它类型的存储设备。解码图像缓冲器(decodedpicture buffer,DPB)230可用于存储一个或多个滤波块221。解码图像缓冲器230还可用于存储同一当前图像或不同图像(例如,先前重建的图像)的其它先前滤波块(例如,先前重建和滤波块221),并且可提供完整的先前重建(即解码)的图像(和对应的参考块和像素点)和/或部分重建的当前图像(和对应的参考块和像素点),用于帧间预测等。例如,在重建块215未被环路滤波单元220进行滤波时,解码图像缓冲器(decoded picture buffer,DPB)230还可用于存储一个或多个未经滤波的重建块215,或通常存储未经滤波的重建像素点,或重建块或重建像素点的任何其它未经进一步处理的版本。

模式选择(分割和预测)

模式选择单元260包括分割单元262、帧间预测单元244和帧内预测单元254,用于从解码图像缓冲器230或其它缓冲器(例如,行缓冲器,未示出)等接收或获得原始图像数据(例如,原始块203(当前图像17的当前块203))和重建图像数据(例如,相同(当前)图像和/或一个或多个先前解码图像的滤波和/或未经滤波的重建像素点或重建块)。重建图像数据用作参考图像数据进行帧间预测或帧内预测等预测,以获得预测块265或预测值265。

模式选择单元260可用于为当前块预测模式(包括不分割)和预测模式(例如帧内或帧间预测模式)确定或选择分割类型,并生成对应的预测块265,以对残差块205进行计算和对重建块215进行重建。

模式选择单元260的实施例可用于选择分割和预测模式(例如,从模式选择单元260支持或可用于模式选择单元260的预测模式中选择),所述预测模式提供最佳匹配或者说最小残差(最小残差意味着传输或存储中更好的压缩),或提供最小指示开销(最小指示开销意味着传输或存储中更好的压缩),或者同时考虑或平衡以上两者。模式选择单元260可用于根据率失真优化(rate distortion optimization,RDO)确定分割和预测模式,即选择提供最小率失真的预测模式。本上下文中如“最佳”、“最小”、“最优”等术语不一定指总体上“最佳”、“最小”、“最优”等,也可以指满足终止或选择标准,例如,值超过或低于阈值或其它约束条件,可能会进行“次优选择”,但是降低了复杂度和处理时间。

换句话说,分割单元262可以用于将块203分割成更小的分割块或子块(再次形成块),例如,使用四叉树(quad-tree,QT)分割、二叉树(binary-tree,BT)分割或三叉树(triple-tree,TT)分割或其任何组合迭代地进行,并例如,对每个分割块或子块进行预测,其中,所述模式选择包括选择分割块203的树形结构并将预测模式应用于每个分割块或子块。

下文详细描述由示例性视频编码器20执行的分割(例如,由分割单元260执行)和预测处理(例如,由帧间预测单元244和帧内预测单元254执行)。

分割

分割单元262可以将当前块203分割(或划分)成更小的分割块,例如正方形或矩形大小的较小块。可以将这些较小块(也可以称为子块)进一步分割为甚至更小的分割块。这也称为树分割或层次树分割,其中,可以递归地分割例如根树层次0(层次级别0,深度0)的根块,例如分割为两个或两个以上下一较低树层次的块,例如树层次1(层次级别1,深度1)的节点。可以再次将这些块分割为两个或两个以上下一较低层次,例如树层次2(层次级别2、深度2)的块等,直到例如因为满足结束标准,例如达到最大树深度或最小块大小,分割结束。未进一步分割的块也称为树的叶块或叶节点。分割为两个部分的树称为二叉树(binary-tree,BT),分割为三个部分的树称为三叉树(ternary-tree,TT),分割为四个部分的树称为四叉树(quad-tree,QT)。

如上所述,本文使用的术语“块”可以是图像的一部分,特别是正方形或矩形部分。例如,结合HEVC和VVC,块可以是或对应于译码树单元(coding tree unit,CTU)、译码单元(coding unit,CU)、预测单元(prediction unit,PU)和变换单元(transform unit,TU),和/或对应于对应块,例如,译码树块(coding tree block,CTB)、译码块(coding block,CB)、变换块(transform block,TB)或预测块(prediction block,PB)。

例如,译码树单元(coding tree unit,CTU)可以为或包括具有三个像素点阵列的图像的亮度像素点的一个CTB、色度像素点的两个对应CTB,或单色图像或使用用于对像素点进行译码的三个独立颜色平面和语法结构译码的图像的像素点的一个CTB。相应地,译码树块(coding tree block,CTB)可以为N×N个像素点块,其中N可以设为某个值从而将分量划分为多个CTB,这就是分割。译码单元(coding unit,CU)可以为或包括具有三个像素点阵列的图像的亮度像素点的一个译码块、色度像素点的两个对应译码块,或单色图像或使用用于对像素点进行译码的三个独立颜色平面和语法结构译码的图像的像素点的一个译码块。相应地,译码块(coding block,CB)可以为M×N个像素点块,其中M和N可以设为某个值从而将CTB划分为多个译码块,这就是分割。

在实施例中,例如根据HEVC,可以通过表示为译码树的四叉树结构将译码树单元(coding tree unit,CTU)划分为多个CU。在CU级决定使用帧间(时间)预测或帧内(空间)预测对图像区域进行译码。可以根据PU划分类型将每个CU进一步划分为一个、两个或四个PU。一个PU内应用相同的预测过程,并在PU的基础上向解码器发送相关信息。在根据PU划分类型应用预测过程获得残差块之后,可以根据与用于CU的译码树类似的另一种四叉树结构将CU分割为变换单元(transform unit,TU)。

在实施例中,例如根据当前开发的称为通用视频译码(Versatile Video Coding,VVC)的最新视频译码标准,例如使用组合的四叉树和二叉树(quad-tree and binarytree,QTBT)分割来分割译码块。在QTBT块结构中,CU可以为正方形或矩形。例如,首先通过四叉树结构分割译码树单元(coding tree unit,CTU)。通过二叉树或三叉树(ternary或triple)结构进一步分割四叉树叶节点。分割树叶节点称为译码单元(coding unit,CU),该分割用于预测和变换处理,而不进行任何进一步分割。这意味着在QTBT译码块结构中,CU、PU和TU的块大小相同。同时,可以将三叉树分割等多重分割与QTBT块结构结合使用。

在一个示例中,视频编码器20的模式选择单元260可以用于执行本文描述的分割技术的任意组合。

如上所述,视频编码器20用于从(例如预定的)预测模式集合中确定或选择最好或最优的预测模式。预测模式集合可以包括帧内预测模式和/或帧间预测模式等。

帧内预测

帧内预测模式集合可以包括35种不同的帧内预测模式,例如,如DC(或均值)模式和平面模式等非方向性模式,或如HEVC中定义的方向性模式,或者可以包括67种不同的帧内预测模式,例如,如DC(或均值)模式和平面模式等非方向性模式,或如针对VVC定义的方向性模式。

帧内预测单元254用于根据帧内预测模式集合中的帧内预测模式,使用同一当前图像中的邻块的重建像素点来生成帧内预测块265。

帧内预测单元254(或通常为模式选择单元260)还用于将帧内预测参数(或通常为指示块的所选帧内预测模式的信息)以语法元素266的形式输出到熵编码单元270,以包括到经编码的图像数据21中,使得例如视频解码器30可以接收并使用用于解码的预测参数。

帧间预测

(可能的)帧间预测模式的集合取决于可用参考图像(即,例如存储在DPB 230中的先前至少部分解码的图像)和其它帧间预测参数,例如取决于是否使用整个参考图像或只使用参考图像的一部分(例如当前块的区域附近的搜索窗口区域)来搜索最佳匹配参考块,和/或例如取决于是否应用像素插值(例如二分之一/半像素和/或四分之一像素插值)。

除上述预测模式外,还可以使用跳过模式和/或直接模式。

帧间预测单元244可以包括运动估计(motion estimation,ME)单元和运动补偿(motion compensation,MC)单元(两者在图2中未示出)。运动估计单元可用于接收或获取图像块203(当前图像17的当前图像块203)和经解码图像231,或至少一个或多个先前重建块,例如,一个或多个其它/不同先前解码图像231的重建块,以进行运动估计。例如,视频序列可以包括当前图像和先前解码图像231,或换句话说,当前图像和先前解码图像231可以为形成视频序列的图像序列的一部分或形成该图像序列。

例如,编码器20可用于从多个其它图像中的相同或不同图像的多个参考块中选择参考块,并将参考图像(或参考图像索引)和/或参考块的位置(x坐标,y坐标)与当前块的位置之间的偏移(空间偏移)作为帧间预测参数提供给运动估计单元。该偏移也称为运动矢量(motion vector,MV)。

运动补偿单元用于获取,例如接收帧间预测参数,并根据或使用帧间预测参数进行帧间预测,以获得帧间预测块265。由运动补偿单元执行的运动补偿可以包括根据通过运动估计确定的运动/块矢量来提取或生成预测块,还可能包括对子像素分辨率执行插值。插值滤波可以从已知像素的像素点中生成额外像素的像素点,从而可能增加可用于对图像块进行译码的候选预测块的数量。一旦接收到当前图像块的PU的运动矢量,运动补偿单元可以定位在其中一个参考图像列表中运动矢量指向的预测块。

运动补偿单元还可以生成与块和视频条带相关的语法元素,以供视频解码器30在解码视频条带的图像块时使用。除了条带和相应语法元素或作为条带和相应语法元素的替代,还可以生成或使用分块组(tile group)和/或分块(tile)以及相应语法元素。

熵编码

例如,熵编码单元270用于对量化系数209、帧间预测参数、帧内预测参数、环路滤波器参数和/或其它语法元素应用熵编码算法或方案(例如,可变长度译码(variablelength coding,VLC)方案、上下文自适应VLC(context adaptive VLC,CAVLC)方案、算术译码方案、二值化、上下文自适应二进制算术译码(context adaptive binary arithmeticcoding,CABAC)、基于语法的上下文自适应二进制算术译码(syntax-based context-adaptive binary arithmetic coding,SBAC)、概率区间分割熵(probability intervalpartitioning entropy,PIPE)译码或其它熵编码方法或技术)或旁路熵编码算法或方案(不压缩),以获得可以通过输出端272以经编码码流21等形式输出的经编码的图像数据21,使得例如视频解码器30可以接收并使用这些参数进行解码。可以将经编码码流21发送到视频解码器30,或将其存储在存储器中以供后续传输或由视频解码器30检索。

视频编码器20的其它结构变型可以用于对视频流进行编码。例如,基于非变换的编码器20可以在没有变换处理单元206的情况下直接量化某些块或帧的残差信号。在另一种实现方式中,编码器20中,量化单元208和反量化单元210可以组合成一个单元。

解码器和解码方法

图3示出了用于实现本申请技术的视频解码器30的示例。视频解码器30用于接收例如由编码器20编码的经编码的图像数据21(例如,经编码码流21)以获得经解码图像331。经编码的图像数据或码流包括用于对所述经编码的图像数据进行解码的信息,例如表示经编码视频条带(和/或分块组或分块)的图像块的数据和相关的语法元素。

在图3的示例中,解码器30包括熵解码单元304、反量化单元310、逆变换处理单元312、重建单元314(例如求和器314)、环路滤波器320、解码图像缓冲器(decoded picturebuffer,DPB)330、模式应用单元360、帧间预测单元344和帧内预测单元354。帧间预测单元344可以为或包括运动补偿单元。在一些示例中,视频解码器30可执行通常与针对图2的视频编码器100描述的编码过程相反的解码过程。

如针对编码器20的描述,反量化单元210、逆变换处理单元212、重建单元214、环路滤波器220、解码图像缓冲器(decoded picture buffer,DPB)230、帧间预测单元344和帧内预测单元354还组成视频编码器20的“内置解码器”。相应地,反量化单元310的功能可以与反量化单元110相同;逆变换处理单元312的功能可以与逆变换处理单元212相同;重建单元314的功能可以与重建单元214相同;环路滤波器320的功能可以与环路滤波器220相同;解码图像缓冲器330的功能可以与解码图像缓冲器230相同。因此,针对视频编码器20的相应单元和功能进行的描述对应地适用于视频解码器30的相应单元和功能。

熵解码

熵解码单元304用于解析码流21(或通常为经编码的图像数据21)并例如对经编码的图像数据21进行熵解码,以获得量化系数309和/或经解码的译码参数(图3中未示出)等,例如帧间预测参数(例如参考图像索引和运动矢量)、帧内预测参数(例如帧内预测模式或索引)、变换参数、量化参数、环路滤波器参数和/或其它语法元素中的任一个或全部。熵解码单元304可用于应用与针对编码器20的熵编码单元270所描述的编码方案相对应的解码算法或方案。熵解码单元304还可以用于向模式应用单元360提供帧间预测参数、帧内预测参数和/或其它语法元素,并向解码器30的其它单元提供其它参数。视频解码器30可以接收视频条带级和/或视频块级的语法元素。除了条带和相应语法元素或作为条带和相应语法元素的替代,还可以接收和/或使用分块组和/或分块以及相应语法元素。

反量化

反量化单元310可用于从经编码的图像数据21(例如,通过熵解码单元304等解析和/或解码)接收量化参数(quantization parameter,QP)(或通常为与反量化相关的信息)和量化系数,并根据所述量化参数对经解码的量化系数309应用反量化以获得解量化系数311,所述解量化系数311也可以称为变换系数311。反量化过程可以包括使用视频编码器20对视频条带(或分块或分块组)中的每个视频块确定的量化参数来确定量化程度,同样确定需要应用的反量化的程度。

逆变换

逆变换处理单元312可用于接收解量化系数311,也称为变换系数311,并对解量化系数311应用变换以获得像素点域中的重建残差块213。重建残差块213也可以称为变换块313。变换可以为逆变换,例如逆DCT、逆DST、逆整数变换或概念上类似的逆变换过程。逆变换处理单元312还可以用于从经编码的图像数据21接收变换参数或对应信息(例如,通过熵解码单元304等解析和/或解码),以确定将应用于解量化系数311的变换。

重建

重建单元314(例如,加法器或求和器314)可用于通过例如将重建残差块313的像素点值和预测块365的像素点值相加,将重建残差块313添加到预测块365,以获得像素点域中的重建块315。

滤波

环路滤波单元320(在译码环路中或译码环路之后)用于对重建块315进行滤波,以获得滤波块321,以平滑像素转变或提高视频质量等。环路滤波单元320可以包括一个或多个环路滤波器,如去块效应滤波器、像素点自适应偏移(sample-adaptive offset,SAO)滤波器或一个或多个其它滤波器,例如双边滤波器、自适应环路滤波器(adaptive loopfilter,ALF)、锐化滤波器、平滑滤波器或协作滤波器或其任意组合。虽然环路滤波单元320在图3中示出为环内滤波器,但是在其它配置中,环路滤波单元320可以实现为后环路滤波器。

解码图像缓冲器

然后,将图像的解码视频块321存储在解码图像缓冲器330中,所述解码图像缓冲器330存储作为参考图像的经解码图像331,这些参考图像用于其它图像的后续运动补偿和/或用于分别输出到显示器。

解码器30用于通过输出端312等输出经解码图像311,向用户呈现或供用户观看。

预测

帧间预测单元344的功能可以与帧间预测单元244(特别是运动补偿单元)相同,帧内预测单元354的功能可以与帧间预测单元254相同,并根据从经编码的图像数据21接收的分割和/或预测参数或相应信息(例如,通过熵解码单元304等解析和/或解码)决定划分或分割并执行预测。模式应用单元360可用于根据重建图像、块或相应像素点(经滤波或未经滤波)对每个块执行预测(帧内或帧间预测),以获得预测块365。

当将视频条带译码为帧内译码(I)条带时,模式应用单元360的帧内预测单元354用于根据指示的帧内预测模式和来自当前图像的先前解码块的数据生成当前视频条带的图像块的预测块365。当将视频图像译码为帧间译码(即,B或P)条带时,模式应用单元360的帧间预测单元344(例如,运动补偿单元)用于根据运动矢量和从熵解码单元304接收的其它语法元素产生当前视频条带的视频块的预测块365。对于帧间预测,可从其中一个参考图像列表中的其中一个参考图像产生这些预测块。视频解码器30可以根据存储在DPB 330中的参考图像,使用默认构建技术来构建参考帧列表:列表0和列表1。除了条带(例如视频条带)或作为条带的替代,相同或类似的过程可应用于使用分块组(例如视频分块组)和/或分块(例如视频分块)的实施例或由这些实施例应用,例如可以使用I、P或B分块组和/或分块对视频进行译码。

模式选择单元360用于通过解析运动矢量或相关信息和其它语法元素来确定当前视频条带的视频块的预测信息,并使用所述预测信息针对所解码的当前视频块生成预测块。例如,模式应用单元360使用接收到的一些语法元素确定用于对视频条带的视频块进行译码的预测模式(例如,帧内预测或帧间预测)、帧间预测条带类型(例如B条带、P条带或GPB条带)、条带的一个或多个参考图像列表的构建信息、条带的每个帧间编码视频块的运动矢量、条带的每个帧间译码视频块的帧间预测状态、以及其它信息,以对当前视频条带内的视频块进行解码。除了条带(例如视频条带)或作为条带的替代,相同或类似的过程可应用于使用分块组(例如视频分块组)和/或分块(例如视频分块)的实施例或由这些实施例应用,例如可以使用I、P或B分块组和/或分块对视频进行译码。

图3中所示的视频解码器30的实施例可用于使用条带(也称为视频条带)对图像进行分割和/或解码,其中,可以使用一个或多个条带(通常不重叠的)对图像进行分割或解码,并且每个条带可以包括一个或多个块(例如,CTU)。

图3所示的视频解码器30的实施例可以用于使用分块组(也称为视频分块组)和/或分块(也称为视频分块)对图像进行分割和/或解码,其中,可以使用一个或多个分块组(通常为不重叠的)对图像进行分割或解码,每个分块组可以包括一个或多个块(例如,CTU)或一个或多个分块等,其中,每个分块可以为矩形等形状,可以包括一个或多个块(例如,CTU),例如完整或部分块。

可以使用视频解码器30的其它变体对经编码的图像数据21进行解码。例如,解码器30可以在没有环路滤波单元320的情况下产生输出视频流。例如,基于非变换的解码器30可以在某些块或帧没有逆变换处理单元312的情况下直接反量化残差信号。在另一种实现方式中,视频解码器30中,反量化单元310和逆变换处理单元312可以组合成一个单元。

应理解,在编码器20和解码器30中,可以对当前步骤的处理结果做进一步处理,然后输出到下一步骤。例如,在插值滤波、运动矢量推导或环路滤波之后,可以对插值滤波、运动矢量推导或环路滤波的处理结果进行进一步运算,如修正(clip)或移位(shift)运算。

需要说明的是,可以对当前块的推导运动矢量(包括但不限于仿射模式的控制点运动矢量,仿射模式、平面模式、ATMVP模式的子块运动矢量,时间运动矢量等)进行进一步运算。例如,根据运动矢量的表示位将运动矢量的值限制在预定义范围内。如果运动矢量的表示位为bitDepth,则范围为–2^(bitDepth–1)至2^(bitDepth–1)–1,其中“^”表示幂次方。例如,如果bitDepth设置为16,则范围为–32768-32767;如果bitDepth设置为18,则范围为–131072-131071。例如,推导运动矢量的值(例如一个8×8块中的4个4×4子块的MV)被限制,使得所述4个4×4子块MV的整数部分之间的最大差值不超过N个像素,如不超过1个像素。这里提供了两种根据bitDepth限制运动矢量的方法。

方法1:通过平滑操作来去除溢出的最高有效位(most significant bit,MSB)

ux=(mvx+2

mvx=(ux>=2

uy=(mvy+2

mvy=(uy>=2

其中,mvx为图像块或子块的运动矢量的水平分量;mvy为图像块或子块的运动矢量的垂直分量;ux和uy表示中间值。

例如,如果mvx的值为–32769,则使用公式(1)和(2)之后得到的值为32767。在计算机系统中,以二进制补码的形式存储十进数。–32769的二进制补码为1,0111,1111,1111,1111(17位),这时丢弃MSB,那么得到的二进制补码为0111,1111,1111,1111(十进数为32767),这与使用公式(1)和(2)之后得到的输出结果相同。

ux=(mvpx+mvdx+2

mvx=(ux>=2

uy=(mvpy+mvdy+2

mvy=(uy>=2

这些运算可以在对mvp和mvd求和的过程中执行,如公式(5)至(8)所示。

方法2:对值进行修正来去除溢出的MSB:

vx=Clip3(–2

vy=Clip3(–2

其中,vx为图像块或子块的运动矢量的水平分量;vy为图像块或子块的运动矢量的垂直分量;x、y和z分别对应于MV修正过程的3个输入值,函数Clip3的定义如下:

图4为本发明实施例提供的视频译码设备400的示意图。视频译码设备400适用于实现本文描述的公开实施例。在一个实施例中,视频译码设备400可以是解码器(如图1A的视频解码器30)或编码器(如图1A的视频编码器20)。

视频译码设备400包括:入端口410(或输入端口410)和接收单元(Rx)420,用于接收数据;处理器、逻辑单元或中央处理单元(central processing unit,CPU)430,用于处理数据;发送单元(Tx)440和出端口450(或输出端口450),用于发送数据;存储器460,用于存储数据。视频译码设备400还可以包括与入端口410、接收单元420、发送单元440和出端口450耦合的光电(optical-to-electrical,OE)组件和电光(electrical-to-optical,EO)组件,用作光信号或电信号的出口或入口。

处理器430通过硬件和软件实现。处理器430可实现为一个或多个CPU芯片、核(例如多核处理器)、FPGA、ASIC和DSP。处理器430与入端口410、接收单元420、发送单元440、出端口450和存储器460通信。处理器430包括译码模块470。译码模块470用于实现上述公开的实施例。例如,译码模块470用于实施、处理、准备或提供各种译码操作。因此,包括译码模块470使得视频译码设备400功能得到了显著改进,实现了视频译码设备400不同状态的转换。或者,以存储在存储器460中并由处理器430执行的指令来实现译码模块470。

存储器460可以包括一个或多个磁盘、磁带机和固态硬盘,可用作溢出数据存储设备,以在选择执行程序时存储这类程序,并存储在程序执行期间读取的指令和数据。例如,存储器460可以是易失性和/或非易失性的,并且可以是只读存储器(read-only memory,ROM)、随机存取存储器(random access memory,RAM)、三态内容寻址存储器(ternarycontent-addressable memory,TCAM)和/或静态随机存取存储器(static random-accessmemory,SRAM)。

图5为示例性实施例提供的装置500的简化框图,其中,装置500可用作图1中的源设备12和目的地设备14中的任一个或两个。

装置500中的处理器502可以是中央处理单元。或者,处理器502可以是现有的或今后将开发出的能够操控或处理信息的任何其它类型的设备或多个设备。虽然可以使用如图所示的处理器502等单个处理器来实现所公开的实现方式,但使用一个以上处理器可以提高速度和效率。

在一种实现方式中,装置500中的存储器504可以是只读存储器(read onlymemory,ROM)设备或随机存取存储器(random access memory,RAM)设备。任何其它合适类型的存储设备都可以用作存储器504。存储器504可以包括处理器502通过总线512访问的代码和数据506。存储器504还可包括操作系统508和应用程序510,其中,应用程序510包括允许处理器502执行本文所述方法的至少一个程序。例如,应用程序510可以包括应用1至N,还可以包括执行本文所述方法的视频译码应用。

装置500还可以包括一个或多个输出设备,如显示器518。在一个示例中,显示器518可以是将显示器与触敏元件组合的触敏显示器,该触敏元件能够用于感测触摸输入。显示器518可以通过总线512耦合到处理器502。

虽然装置500的总线512在这里示为单个总线,但是总线512可以有多个。此外,辅助储存器514可以直接与装置500中的其它组件耦合或可以通过网络访问,并且可以包括单个集成单元(例如一个存储卡)或多个单元(例如多个存储卡)。因此,装置500可以通过多种配置实现。

在VVC草稿3.0的草稿文本JVET-L1001中,MTS可以在序列层级中分别针对帧间和帧内条带启用。当禁用MTS时,DCT2应该作为变换核。然而,在JVET-M0303、JVET-M0140或JVET-M0102等现有技术中,引入了推断的DST7/DCT8变换。在所有情况下都不可能切换到纯DCT2变换。本发明解决了上述问题。

本发明引入了其它DCT2启用标志,用于推断针对序列中的所有情况是否仅使用DCT2变换核,当DCT2启用标志为假时,进一步指示序列层级MTS启用标志。当DCT2启用标志为真时,应该仅使用DCT2变换核。

在SPS中引入其它DCT2启用标志,从而在启用推断的MST工具时能够切换到DCT2。

7.3.2.1序列参数集RBSP语法

在VVC草稿3.0的草稿文本JVET-L1001中,多变换模式选择(multiple transformselection,MTS)可以在序列层级中分别针对帧间和帧内条带启用。当禁用MTS时,DCT2应该作为变换核。然而,在JVET-M0303、JVET-M0140或JVET-M0102等现有技术中,引入了推断的DST7/DCT8变换。在MTS序列层级禁用的情况下,现有技术使用DST7/DCT8,并且根据块形状、位置或其它特征自适应地应用DCT2。然而,DCT2是编码器和解码器设计的理想选择。换言之,本发明实现了DCT2、推断的DST7或DCT8以及MTS(RDO选择的变换核)之间的可切换性。

在本发明中,在高层语法中引入了DCT2启用标志,以便解决1.1节中提到的问题。使用高层语法中的其它DCT2启用标志来推断对于序列中的所有情况是否只使用DCT2变换核,当DCT2启用标志为假时,进一步指示序列层级MTS启用标志以推断是否对序列启用MTS。当DCT2启用标志为真时,应该仅使用DCT2变换核。

对于禁用序列层级DCT2启用标志的情况,进一步指示序列层级MTS标志,如VVC草稿3.0(JVET-L1001)的现有技术一样。因此,与现有技术中一样,使用推断的DST7DCT8或自适应变换核译码工具(例如JVET-M0303、JVET-M0140或JVET-M0102)。

对于启用序列层级DCT启用标志的情况,应该只使用DCT2。因此,对于本来推断使用推断的DST7/DCT8或自适应变换核译码工具(如JVET-M0303、JVET-M0140或JVET-M0102)的情况,使用DCT2替代DST7/DCT8,或禁用DST7/DCT8。

本发明的第一实施例

在第一实施例中,在如下sps中指示序列层级DCT2启用标志,加粗部分由本发明设计。编码器将DCT2启用标志的指示符携带在码流中,解码器从码流中解析出DCT启用标志的指示符。

7.3.2.1序列参数集RBSP语法

sps_dct2_enabled_flag等于1表示仅使用DCT2变换核用于变换单元。sps_mts_intra_enabled_flag等于0表示可以在变换单元中使用DCT2之外的其它变换核。

sps_mts_intra_enabled_flag等于1表示帧内译码单元的残差译码语法中可以存在tu_mts_flag;sps_mts_intra_enabled_flag等于0表示帧内译码单元的残差译码语法中不存在tu_mts_flag。当sps_mts_intra_enabled_flag不存在时,sps_mts_intra_enabled_flag被推断为0。

sps_mts_inter_enabled_flag表示帧间译码单元的残差译码语法中可以存在tu_mts_flag;sps_mts_inter_enabled_flag等于0表示帧间译码单元的残差译码语法中不存在tu_mts_flag。当sps_mts_intra_enabled_flag不存在时,sps_mts_intra_enabled_flag被推断为0。

进一步在低层级语法中使用DCT2启用标志。例如,在形状自适应变换选择情况(JVET-M0303)下,当MTS标志在序列层级中指示为禁用时,将推导的DST7/DCT8用于矩形块的短边,将DST7用于方形块。如果对序列启用序列层级MTS,则在MTS标志为0时应用形状自适应,并且VTM使用DCT2用于水平和垂直方向。在MTS标志为1的情况下,遵循VTM变换选择过程。所使用的三种变换(DCT2、DST7和DCT8)与当前VTM中定义的变换相同。

在所提出的方法中,当DCT2启用标志指示为禁用时,自适应核选择与现有技术保持一致。

当DCT2启用标志指示为启用时,只能使用DCT2。推断禁用MTS功能。形状自适应变换选择只会推断使用DCT2,在本实施例中,它与禁用形状自适应变换选择相同。对应的低层级语法如下所示。

8.4.4缩放变换系数的变换过程

8.4.4.1概述

该过程的输入是:

–亮度位置(xTbY,yTbY),表示当前亮度变换块中的相对于当前图像的左上亮度像素点的左上像素点;

–变量nTbW,表示当前变换块的宽度;

–变量nTbH,表示当前变换块的高度;

–变量cIdx,表示当前块的颜色分量;

–缩放变换系数的(nTbW)×(nTbH)阵列d[x][y],其中,x=0……nTbW–1,y=0……nTbH–1。

该过程的输出是残差像素点的(nTbW)×(nTbH)阵列r[x][y],其中,x=0……nTbW–1,y=0……nTbH–1。

根据mts_idx[xTbY][yTbY][cIdx]推导表8-11中的表示水平变换核的变量trTypeHor和表示垂直变换核的变量trTypeVer。变量trAdaptHorEnabled和trAdaptVerEnabled推导如下:

表8-11:取决于mts_idx[x][y][cIdx]的trTypeHor和trTypeVer的说明

本发明的第二实施例

在第二实施例中,在如下sps中指示序列层级DCT2启用标志,加粗部分由本发明设计。编码器将DCT2启用标志的指示符携带在码流中,解码器从码流中解析出DCT启用标志的指示符。

7.3.2.1序列参数集RBSP语法

sps_dct2_enabled_flag等于1表示仅使用DCT2变换核用于变换单元。sps_mts_intra_enabled_flag等于0表示可以使用DCT2之外的其它变换核用于变换单元。

sps_mts_intra_enabled_flag等于1表示帧内译码单元的残差译码语法中可以存在tu_mts_flag;sps_mts_intra_enabled_flag等于0表示帧内译码单元的残差译码语法中不存在tu_mts_flag。当sps_mts_intra_enabled_flag不存在时,sps_mts_intra_enabled_flag被推断为0。

sps_mts_inter_enabled_flag表示帧间译码单元的残差译码语法中可以存在tu_mts_flag;sps_mts_inter_enabled_flag等于0表示帧间译码单元的残差译码语法中不存在tu_mts_flag。当sps_mts_intra_enabled_flag不存在时,sps_mts_intra_enabled_flag被推断为0。

进一步在低层级语法中使用DCT2启用标志。例如,在子块变换情况(JVET-M0140)下,根据子变换块的位置使用推断的DST7/DCT8。更具体地,图6和图7示出了每个SBT位置的水平和垂直变换。例如,SBT-V位置0的水平变换为DCT-8,垂直变换为DST-7。当残差TU的一个边大于32时,将对应的变换被设置为DCT-2。因此,子块变换联合指定了残差块的TU分块、CBF以及水平和垂直变换,这可以看作是块的主要残差位于块一个边时的一种语法快捷方式(syntax shortcut)。

在所提出的方法中,当DCT2启用标志指示为禁用时,子块变换选择与现有技术保持一致。

当DCT2启用标志指示为启用时,只能使用DCT2。推断禁用MTS功能。子块变换核只会推断使用DCT2。附上对应的低层级语法。

8.4.4缩放变换系数的变换过程

8.4.4.1概述

该过程的输入是:

–亮度位置(xTbY,yTbY),表示当前亮度变换块中的相对于当前图像的左上亮度像素点的左上像素点;

–变量nTbW,表示当前变换块的宽度;

–变量nTbH,表示当前变换块的高度;

–变量cIdx,表示当前块的颜色分量;

–缩放变换系数的(nTbW)×(nTbH)阵列d[x][y],其中,x=0……nTbW–1,y=0……nTbH–1。

该过程的输出是残差像素点的(nTbW)×(nTbH)阵列r[x][y],其中,x=0……nTbW–1,y=0……nTbH–1。

如果cu_sbt_flag[xTbY][yTbY]等于1,则根据cu_sbt_horizontal_flag[xTbY][yTbY]和cu_sbt_pos_flag[xTbY][yTbY]推导表中表示水平变换核的变量trTypeHor和表示垂直变换核的变量trTypeVer。

否则(cu_sbt_flag[xTbY][yTbY]等于0),根据mts_idx[xTbY][yTbY][cIdx]推导表8-16中表示水平变换核的变量trTypeHor和表示垂直变换核的变量trTypeVer。

变量nonZeroW和nonZeroH推导如下:

nonZeroW=Min(nTbW,32) (8-810)

nonZeroH=Min(nTbH,32) (8-811)

残差像素点的(nTbW)×(nTbH)阵列r推导如下:

1.通过对每一列x=0……nonZeroW–1调用第8.4.4.2小节中指定的一维变换过程,将缩放变换系数d[x][y](x=0……nonZeroW–1,y=0……nonZeroH–1)的每一(垂直)列变换为e[x][y](x=0……nonZeroW–1,y=0……nTbH–1),其中,将变换块的高度nTbH、缩放变换系数的非零高度nonZeroH、列表d[x][y](y=0……nonZeroH–1)以及设置为trTypeVer的变换类型变量trType作为输入,输出为列表e[x][y],其中,y=0……nTbH–1。

2.中间像素点值g[x][y](x=0……nonZeroW–1,y=0……nTbH–1)推导如下:

g[x][y]=Clip3(CoeffMin,CoeffMax,(e[x][y]+64)>>7) (8-812)

3.通过对每一行y=0……nTbH–1调用第8.4.4.2小节中指定的一维变换过程,将所得到的阵列g[x][y](x=0……nonZeroW–1,y=0……nTbH–1)的每一(水平)行变换为r[x][y](x=0……nTbW–1,y=0……nTbH–1),其中,将变换块的宽度nTbW、所得到的阵列g[x][y]的非零宽度nonZeroW、列表g[x][y](x=0……nonZeroW–1)以及设置为trTypeHor的变换类型变量trType作为输入,输出为列表r[x][y],其中x=0……nTbW–1。

表8-15:取决于cu_sbt_horizontal_flag[x][y]和cu_sbt_pos_flag[x][y]的trTypeHor和trTypeVer的说明

表8-16:取决于mts_idx[x][y][cIdx]的trTypeHor和trTypeVer的说明

本发明的第三实施例

在第三实施例中,在如下sps中指示序列层级DCT2启用标志,加粗部分由本发明设计。编码器将DCT2启用标志的指示符携带在码流中,解码器从码流中解析出DCT启用标志的指示符。

7.3.2.1序列参数集RBSP语法

sps_dct2_enabled_flag等于1表示仅使用DCT2变换核用于变换单元。sps_mts_intra_enabled_flag等于0表示可以使用DCT2之外的其它变换核用于变换单元。

sps_mts_intra_enabled_flag等于1表示帧内译码单元的残差译码语法中可以存在tu_mts_flag;sps_mts_intra_enabled_flag等于0表示帧内译码单元的残差译码语法中不存在tu_mts_flag。当sps_mts_intra_enabled_flag不存在时,sps_mts_intra_enabled_flag被推断为0。

sps_mts_inter_enabled_flag表示帧间译码单元的残差译码语法中可以存在tu_mts_flag;sps_mts_inter_enabled_flag等于0表示帧间译码单元的残差译码语法中不存在tu_mts_flag。当sps_mts_intra_enabled_flag不存在时,sps_mts_intra_enabled_flag被推断为0。

进一步在低层级语法中使用DCT2启用标志。例如,在子块变换情况(JVET-M0140)下,根据子变换块的位置使用推断的DST7/DCT8。更具体地,图6示出了每个SBT位置的水平和垂直变换。例如,SBT-V位置0的水平变换为DCT-8,垂直变换为DST-7。当残差TU的一个边大于32时,将对应的变换被设置为DCT-2。因此,子块变换联合指定了残差块的TU分块、CBF以及水平和垂直变换,这可以看作是块的主要残差位于块一个边时的一种语法快捷方式(syntax shortcut)。

在所提出的方法中,当DCT2启用标志指示为禁用时,子块变换选择与现有技术保持一致。

当DCT2启用标志指示为启用时,只能使用DCT2。推断禁用MTS功能。由于推断的MTS变换核不可用,因此推断禁用子块变换。

在JVET-M0140的基础上,对应的语法变化如下:

7.3.2.1序列参数集RBSP语法

本发明的实施例引入了可切换DCT2启用序列层级指示符,从而可能对于整个序列或条带,使用推断的变换工具切换到纯DCT2变换核。相比其它变换核,DCT2的计算相对简单,内存带宽较小。在现有技术中,使用简单DCT2变换的可能性被推断的变换核切断,本发明中的指示符使编码器和解码器能够在低成本/复杂性与高性能之间灵活切换。在实施例中,既提供了低层级变化可能性,又提供了高层级变化可能性,从而保证在多种变化下代码的一致性和译码性能。

换言之,本发明提供:一种对图像块进行视频译码的方法,包括:对于所述块的多个像素点中的一个像素点,获取由帧间预测或帧内预测产生的残差信号;推断对所述残差信号的序列使用离散余弦变换类型2(Discrete Cosine Transform type 2,DCT2)变换核;使用所述推断的变换核处理所述块的变换。

也就是说,本发明引入了其它DCT2启用标志,用于推断针对序列中的所有情况是否仅使用DCT2变换核,当DCT2启用标志为假时,进一步指示序列层级MTS启用标志。当DCT2启用标志为真时,应该仅使用DCT2变换核。在SPS中引入其它DCT2启用标志,从而在启用推断的MST工具时能够切换到DCT2。

这在图8中进一步说明。在图8中,在步骤1601中,提供包括块的图像。在步骤1602中,对于图像块的多个像素点中的一个像素点,获取由帧间预测或帧内预测产生的残差信号。在步骤1603中,推断对残差信号的序列使用离散余弦变换类型2(Discrete CosineTransform type 2,DCT2)变换核,其中,在步骤1602中获得所述残差信号。在步骤1604中,使用所述推断的变换核处理所述块的变换。

在本发明提供的方法中,如图8所示,DCT2的使用可以根据序列参数集(SequenceParameter Set,SPS)中的序列层级DCT2启用标志推断。

在本发明提供的方法中,如图8所示,序列层级DCT2启用标志表示为sps_dct2_enabled_flag。

本发明还提供了图9所示的编码器20。图9所示的编码器20包括获取单元22。获取单元22可以用于获取由帧间预测或帧内预测产生的残差信号。图9进一步示出了编码器20还包括推断单元24。推断单元24可以用于推断对所述残差信号的序列使用离散余弦变换类型2(Discrete Cosine Transform type 2,DCT2)变换核。这里,残差信号可以通过获取单元22获取。图9所示的编码器20还包括处理单元26。所述处理单元26可以用于使用所述推断的变换核处理所述块的变换。变换核可以通过推理单元24推断。

在图9所示的本发明提供的编码器20中,推断单元24可以用于根据序列参数集(Sequence Parameter Set,SPS)中的序列层级DCT2启用标志推断DCT2的使用。

在图9所示的本发明提供的编码器20中,序列层级DCT2启用标志可以表示为sps_dct2_enabled_flag。

本发明还提供了图10所示的解码器30。图10所示的解码器30包括获取单元32。获取单元32可以用于获取由帧间预测或帧内预测产生的残差信号。图10进一步示出了解码器30还包括推断单元34。推断单元34可以用于推断对所述残差信号的序列使用离散余弦变换类型2(Discrete Cosine Transform type 2,DCT2)变换核。这里,残差信号可以通过获取单元32获取。图10所示的解码器30还包括处理单元36。所述处理单元36可以用于使用所述推断的变换核处理所述块的变换。变换核可以通过推理单元34推断。

在本发明提供的图10所示的解码器30中,推断单元34可以用于根据序列参数集(Sequence Parameter Set,SPS)中的序列层级DCT2启用标志推断DCT2的使用。

在本发明提供的图10所示的解码器30中,序列层级DCT2启用标志可以表示为sps_dct2_enabled_flag。

数学运算符

本申请中使用的数学运算符与C编程语言中使用的数学运算符类似。然而,对整数除法和算术移位运算的结果进行了更准确的定义,并且定义了其它运算,如幂运算和实值除法。编号和计数规范通常从0开始,例如,“第一个”相当于第0个,“第二个”相当于第1个,等等。

算术运算符

以下算术运算符定义如下:

逻辑运算符

以下逻辑运算符定义如下:

关系运算符

以下关系运算符定义如下:

当一个关系运算符应用于一个已被赋值“na”(不适用,not applicable)的语法元素或变量时,值“na”被视为该语法元素或变量的不同值。值“na”被视为不等于任何其它值。

按位运算符

以下按位运算符定义如下:

赋值运算符

以下算术运算符定义如下:

范围表示法

以下符号用来说明值的范围:

x=y..z x取从y到z(包括端值)的整数值,其中x、y和z是整数,z大于y。

数学函数

定义了以下数学函数:

Asin(x)三角反正弦函数,对参数x运算,x在–1.0至1.0(包括端值)范围之间,输出值在–π÷2至π÷2(包括端值)范围之间,单位为弧度。

Atan(x)三角反正切函数,对参数x运算,输出值在–π÷2至π÷2(包括端值)范围之间,单位为弧度。

Ceil(x)大于或等于x的最小整数。

Clip1

Clip1

Cos(x)三角余弦函数,对参数x运算,单位为弧度。

Floor(x)小于或等于x的最大整数。

Ln(x)x的自然对数(以e为底的对数,其中e是自然对数底数常数2.718 281828……)。

Log2(x)x以2为底的对数。

Log10(x)x以10为底的对数。

Round(x)=Sign(x)*Floor(Abs(x)+0.5)

Sin(x)三角正弦函数,对参数x运算,单位为弧度。

Swap(x,y)=(y,x)

Tan(x)三角正切函数,对参数x运算,单位为弧度。

运算顺序优先级

当没有使用括号来显式指示表达式中的优先顺序时,适应以下规则:

-高优先级的运算在低优先级的任何运算之前计算。

-相同优先级的运算从左到右依次计算。

下表从最高到最低说明运算的优先级,表中位置越高,优先级越高。

对于C编程语言中也使用的运算符,本规范中使用的优先级顺序与在C编程语言中使用的优先级顺序相同。

表:从最高(表格顶部)到最低(表格底部)的运算优先级

逻辑运算的文本说明

在文本中,逻辑运算的语句用数学形式描述如下:

if(condition 0)

statement 0

else if(condition 1)

statement 1

...

else/*informative remark on remaining condition*/

statement n

可以采用如下方式描述:

……如下/……以下为准:

–如果条件0,则语句0

–否则,如果条件1,则语句1

-……

–否则(关于剩余条件的提示性说明),则语句n

文本中的每个“如果……否则,如果……否则,……”语句都以“……如下”或“……以下适用”开头,紧接“如果……”。“如果……,否则,如果……,否则,……”的最后一个条件始终是“否则,……”。中间的“如果……否则,如果……否则,……”语句可以通过使“……如下”或“……以下适用”与结尾“否则,……”匹配来识别。

在文本中,逻辑运算的语句用数学形式描述如下:

if(condition 0a&&condition 0b)

statement 0

else if(condition 1a||condition 1b)

statement 1

...

else

statement n

可以采用如下方式描述:

……如下/……以下为准:

-如果满足以下所有条件,则语句0:

–条件0a

–条件0b

–否则,如果满足以下一个或多个条件,则语句1:

–条件1a

–条件1b

-……

–否则,语句n

在文本中,逻辑运算的语句用数学形式描述如下:

if(condition 0)

statement 0

if(condition 1)

statement 1

可以采用如下方式描述:

当条件0,则语句0

当条件1,则语句1

尽管本发明实施例主要根据视频译码进行了描述,但需要说明的是,译码系统10、编码器20和解码器30(相应地,系统10)的实施例以及本文描述的其它实施例也可以用于静止图像处理或译码,即,对视频译码中独立于任何先前或连续图像的单个图像进行处理或译码。通常,如果图像处理译码限于单个图像17,仅帧间预测单元244(编码器)和344(解码器)可能不可用。视频编码器20和视频解码器30的所有其它功能(也称为工具或技术)同样可用于静态图像处理,例如残差计算204/304、变换206、量化208、反量化210/310、(逆)变换212/312、分割262/362、帧内预测254/354和/或环路滤波220/320、熵编码270和熵解码304。

编码器20和解码器30等的实施例,以及本文描述的与编码器20和解码器30等有关的功能可以硬件、软件、固件或其任意组合来实现。如果以软件来实现,则各种功能可作为一个或多个指令或代码存储在计算机可读介质中或通过通信介质传输,且由基于硬件的处理单元执行。计算机可读介质可以包括与有形介质(如数据存储介质)对应的计算机可读存储介质,或包括任何便于将计算机程序从一处传送到另一处的介质(例如根据通信协议)的通信介质。以此方式,计算机可读介质通常可以对应(1)非瞬时性的有形计算机可读存储介质,或(2)如信号或载波等通信介质。数据存储介质可以是通过一个或多个计算机或一个或多个处理器访问的任何可用介质,以检索用于实施本发明所述技术的指令、代码和/或数据结构。计算机程序产品可以包括计算机可读介质。

作为示例而非限制,这类计算机可读存储介质可以包括RAM、ROM、EEPROM、CD-ROM或其它光盘存储器、磁盘存储器或其它磁性存储设备、闪存或可以用于存储指令或数据结构形式的所需程序代码并且可以由计算机访问的任何其它介质。此外,任何连接都可以适当地称为计算机可读介质。例如,如果使用同轴电缆、光缆、双绞线、数字用户线(digitalsubscriber line,DSL)或如红外线、无线电和微波等无线技术从网站、服务器或其它远程资源传输指令,则在介质定义中包括同轴电缆、光缆、双绞线、DSL或如红外线、无线电和微波等无线技术。然而,应理解,计算机可读存储介质和数据存储介质并不包括连接、载波、信号或其它瞬时性介质,而是针对非瞬时性有形存储介质。本文所使用的磁盘和光盘包含压缩光盘(compact disc,CD)、激光光盘、光学光盘、数字多功能光盘(digital versatiledisc,DVD)和蓝光光盘,其中,磁盘通常以磁性方式再现数据,而光盘利用激光以光学方式再现数据。以上各项的组合也应包括在计算机可读介质的范围内。

可通过如一个或多个数字信号处理器(digital signal processor,DSP)、通用微处理器、专用集成电路(application specific integrated circuit,ASIC)、现场可编程逻辑阵列(field programmable logic array,FPGA)或其它等效集成或离散逻辑电路等一个或多个处理器来执行指令。因此,本文所使用的术语“处理器”可指前述结构或适合于实现本文描述的技术的任何其它结构中的任一者。另外,在一些方面中,本文描述的各种功能可以提供在用于编码和解码的专用硬件和/或软件模块内,或者并入在组合编解码器中。而且,这些技术可以在一个或多个电路或逻辑元件中完全实现。

本发明的技术可以在多种设备或装置中实现,这些设备或装置包括无线手机、集成电路(integrated circuit,IC)或一组IC(例如芯片组)。本发明描述了各种组件、模块或单元,以强调用于执行所公开技术的设备的功能方面,但未必需要由不同的硬件单元实现。实际上,如上所述,各种单元可以结合合适的软件和/或固件组合在编解码器硬件单元中,或者通过互操作硬件单元(包括如上所述的一个或多个处理器)的集合来提供。

- 使用DCT2启用高层级标志的编码器、解码器和对应方法

- 使用DCT2启用高层级标志的编码器、解码器和对应方法