一种用于AMOLED的ELVDD优化结构

文献发布时间:2023-06-19 11:26:00

技术领域

本发明属于电源技术领域,具体的说是涉及一种用于AMOLED的ELVDD优化结构。

背景技术

目前市面上基本所有的有线充电手机都采用如图1所示方案进行供电。即手机充电器Adapter接入220V家用电给手机供电,手机里面经过Charger芯片进行转换成系统所需的电压VSYS以及给手机电池Battery进行充电,VSYS然后再给扬声器Speaker、手机显示屏Mobile Phone Display、MCU以及其它设备供电。在手机开启应用越多时,VSYS可能会从4.15~4.6V反复变化,甚至变化的更大,这就导致手机显示屏LED Display的供电电压ELVDD和ELVSS抖动,出现通常所说闪屏的现象,这对用户体验是非常不友好的。

通常ELVDD的电压是4.6V,它是由PMIC里的一路DCDC(Boost)所产生的。所以为了使得电池的效率高,该路BOOST需支持4.45V转4.6V的输出。实际芯片还需保留余量,通常将工作在BOOST模式下的极限点设在4.5V~4.55V之间。由于BOOST受最小导通时间Min_on时间的限制,其不能支持4.6V输入4.6V输出的情况,否则输出电压ELVDD会出现振荡 。所以为了避免Adapter供电时ELVDD出现该现象,就需要此时从BOOST正常工作模式切换到DownMode工作模式。但是切入DownMode模式时如果不对ELVDD的Ripple做优化处理,就会出现闪屏的现象。BOOST模式就是DC-DC以BOOST方式进行升压;其中功率管PFET和NFET是工作在开关状态。电感电流上升斜率为VIN/L,下降斜率为(Vout-VIN)/L。DownMode模式就是DC-DC以类似BOOST方式进行升降压;其中NFET是工作在开关状态,PFET是工作在饱和区。电感电流上升斜率为VIN/L,下降斜率为(Vmax+VGS-VIN)/L。其中Vmax为取VIN和Vout中最大值。

如图所示2,为典型ELVDD电源产生电路。图3是DC-DC从BOOST模式切换到DownMode模式时电感L电流和负载电流曲线图;从图中不难看出当从BOOST模式切换到DownMode瞬间时间内电感电流会偏离负载电流很多,所以输出电压Vout(即ELVDD)就会又下冲Undershoot。而为了减小这个Ripple很多应用上都只是增大输出电容Cout,这样不仅增加了成本,而且浪费了面积,占用了空间。

发明内容

本发明针对上述问题,提出一种ELVDD的DCDC从BOOST模式切入到DownMode模式的纹波Ripple优化结构。

本发明的技术方案为:

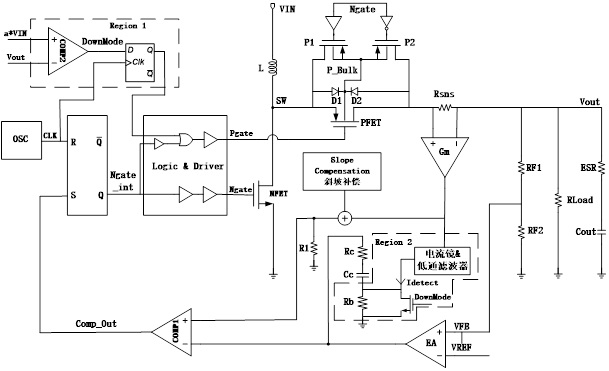

如图7所示,本发明的用于AMOLED的ELVDD优化结构,包括RS触发器、逻辑与驱动单元、电感、NFET、PFET、第一PMOS管、第二PMOS管、第一二极管、第二二极管、跨导放大器、第一电阻、第二电阻、第三电阻、第四电阻、第五电阻、电容、斜率补偿单元、加法器、误差放大器、第一比较器;其特征在于,还包括第二比较器、D触发器、电流镜和低通滤波单元、NMOS管、第六电阻;其中,

RS触发器的R输入和D触发器的时钟信号输入端接时钟信号,RS触发器的S输入端接第一比较器的输出端,RS触发器的Q输出端接逻辑与驱动单元的输入端作为第一输入信号,D触发器的Q输出端接逻辑与驱动单元的输入端作为第二输入信号,D触发器的D输入端接第二比较器的输出端,第二比较器的同相输入端接电源信号的采样电压(a是通过采样电阻确定的系数,即确定用于与Vout比较的采样电压值,从而确定进入DownMode的阈值),第二比较器的反相输入端接ELVDD的输出信号;

第一输入信号输入逻辑与驱动单元后经过两个串联的反相器作为逻辑与驱动单元的第一输出信号,第一输入信号输入逻辑与驱动单元后经过反相器与第二输入信号作为或门的两个输入信号,或门的输出经过反相器后作为逻辑与驱动单元的第二输出信号;

第一输出信号接NFET的栅极,NFET的源极接地,NFET的漏极经过电感后接电源;第二输出信号接PFET的栅极,PFET的源极经过电感后接电源,PFET的漏极接跨导放大器的同相输入端,第一电阻连接在跨导放大器的同相输入端和反相输入端之间;PFET的漏极通过第一电阻后作为ELVDD的输出端;

第一输出信号经过反相器后接第一PMOS管的栅极,第一PMOS管的漏极通过电感后接电源,第一PMOS管的源极接PFET的衬底;第一输出信号经过非门后接第二PMOS管的栅极,第二PMOS管的源极接PFET的衬底,第二PMOS管的漏极接PFET的漏极;第一PMOS管的漏极接第一二极管的正极,第一二极管的负极接PFET的衬底,第二PMOS管的漏极接第二二极管的正极,第二二极管的负极接PFET的衬底;

跨导放大器的输出端接加法器的一个输入端,加法器的另一个输入端接斜率补偿单元的输出,加法器的输出端接第一比较器的同相输入端,加法器的输出端还通过第二电阻后接地;

电流镜和低通滤波单元的输入端接跨导放大器的输出端,电流镜和低通滤波单元的输出端接NMOS管的漏极,NMOS管的源极接地,NMOS管的栅极接降压模式触发信号;NMOS管的漏极通过电容和第三电阻后接误差放大器的输出端,NMOS管的漏极通过第六电阻后接地;

误差放大器的同相输入端通过第四电阻后接ELVDD的输出端,误差放大器的同相输入端通过第五电阻后接地,误差放大器的反相输入端接基准电压,误差放大器的输出端接第一比较器的反相输入端。

本发明的有益效果是:减小DC-DC从BOOST模式切换到DownMode模式时所产生的纹波Ripple,明显优化了电流偏离负载电流的幅度,也即优化了输出电压Vout(ELVDD)的Ripple,从而很好的解决了手机可能出现闪屏的问题。

附图说明

图1为有线手机充电原理图。

图2为典型峰值电流模DC-DC电路结构示意图。

图3为典型ELVDD产生电路电感和负载曲线图。

图4为优化后电感电流波形图。

图5为优化前电感电流变化曲线。

图6为优化后电感电流变化曲线。

图7为ELVDD优化后电路图。

具体实施方式

下面结合附图对本发明进行详细的描述。

本发明的结构如图7所示,在传统结构上,增加了Region1和Region2部分,Region1作用是在切入和退出DownMode的时候和CLK进行同步。Region2的作用是在切入和退出DownMode的时候快速的调整PWM脉宽,进而减小输出电压Vout的Ripple。

本发明的原理是:

增加进入DownMode同步CLK电路,如图7中Region1所示;这样可以防止刚切入到DownMode时电感电流急剧下降,这样等效可以减小输出电压急剧下降,对比图3和图4的DownMode Start点可知。

增加DownMode快速PWM控制方法,如图7所示,Region2里面电流Idetect是和负载电流成正相关一个电流。通过该电流在Rb上产生一个电压,叠加到Comp1的负向端,进而控制切换瞬间的PWM脉宽宽度。当该电流Idetect选取合适时,就会产生合适PWM脉冲宽度,如果下所示,进而使得电流电感偏离负载电流较小,进而输出电压纹波Ripple很小。由于进入和退出DownMode的原理类似,这里不再赘述退出DownMode时原理和电感电流的波形图。

如图5所示,为典型ELVDD电源产生电路直接从BOOST模式切换到DownMode模式时电感L电流和负载电流曲线图;从图中不难看出当从BOOST模式切换到DownMode瞬间时间内电感电流会偏离负载电流很多,所以输出电压Vout(即ELVDD)就会又下冲Undershoot。而为了减小这个Ripple很多应用上都只是增大输出电容,这样不仅增加了成本,而且浪费了面积,占用了空间。

本发明是在外围条件一样的情况下,减小DC-DC从BOOST模式切换到DownMode模式时所产生的纹波Ripple。如图6所示,明显优化了电流偏离负载电流的幅度,也即优化了输出电压Vout(ELVDD)的Ripple,从而很好的解决了手机可能出现闪屏的问题。

- 一种用于AMOLED的ELVDD优化结构

- 一种用于AMOLED的ELVDD结构