将储存系统用作主存储器的方法和装置

文献发布时间:2023-06-19 11:27:38

优先权要求

本申请是2019年6月18日提交的PCT/US2019/037787的继续,要求其优先权和利益,本申请要求2018年6月18日提交的美国临时专利申请No.62/686,333的优先权和利益,其内容通过引用整体并入本文。

技术领域

本公开涉及集成电路和计算机系统,并且更特别地涉及计算机主存储器。

背景技术

计算设备(服务器、个人计算机、移动电话、平板电脑等)典型地包括处理器或片上系统(SoC)。图1示出了设备10的示例,该设备10包括处理器或SoC 12以及由一个或多个动态随机存取存储器(DRAM)14制成的主存储器。DRAM 14可以被实现为连接到SoC 12但与SoC12分开的一个或多个集成电路。设备10还可以包括连接到SoC 12的端口17的一个或多个储存驱动器16。储存驱动器16可以包括闪速存储器、固态驱动器、硬盘驱动器和/或混合驱动器。混合驱动器包括具有固态存储器的固态驱动器和具有旋转储存介质的硬盘驱动器。

SoC 12可以包括一个或多个图像处理设备20、系统总线22和存储器控制器24。每个图像处理设备20可以包括,例如:具有中央处理器(或中央处理单元(CPU))28的控制模块26;图形处理器(或图形处理单元(GPU))30;录像机32;相机图像信号处理器(ISP)34;以太网接口,诸如千兆比特(Gb)以太网接口36;串行接口,诸如通用串行总线(USB)接口38和串行高级技术附件(SATA)接口40;以及外围组件互连快速(PCIe)接口42。图像处理设备20经由系统总线22和存储器控制器24访问DRAM 14。DRAM 14用作主存储器。例如,当访问DRAM14之一中的对应物理位置时,图像处理设备20之一向存储器控制器24提供物理地址。图像处理设备20还可以经由系统总线22访问储存驱动器16。

SoC 12和/或存储器控制器24可以经由SoC 12的一个或多个访问端口44连接到DRAM 14。DRAM 14储存用户数据、系统数据和/或程序。SoC 12可以使用第一数据执行程序以生成第二数据。可以在执行程序之前将第一数据储存在DRAM 14中。SoC 12可以在执行程序期间和/或之后将第二数据储存在DRAM 14中。DRAM 14可以具有高带宽接口和每位低成本的存储器储存容量,并且可以处理广泛的应用。

SoC 12包括缓存存储器,其可以包括零级(L0)缓存、一级(L1)缓存、二级(L2)缓存或三级(L3)缓存中的一个或多个。L0-L3缓存被布置在SoC12上,紧邻图像处理设备20中的对应图像处理设备。在所示的示例中,控制模块26包括中央处理器28和L1-L3缓存50。中央处理器28包括L0缓存52。中央处理器28还包括存储器管理单元(MMU)54,其可以控制对缓存50、52的访问。

随着缓存级别的增加,缓存的访问等待时间和储存容量也会增加。例如,L1缓存典型地具有比L2缓存和L3缓存更少的储存容量。然而,L1缓存典型地具有比L2缓存和L3缓存更低的等待时间。

SoC 12内的缓存典型地被实现为静态随机存取存储器(SRAM)。由于缓存与图像处理设备20紧邻,因此缓存可以以与图像处理设备20相同的时钟频率操作。因此,缓存表现出比DRAM 14更短的等待时间段。

SoC 12中的缓存的数目和尺寸取决于应用。例如,入门级手机(或移动电话)可能不包括L3缓存,并且可以具有比个人计算机更小的L1缓存和L2缓存。相似地,每个DRAM 14的数目和尺寸取决于应用。例如,移动电话当前具有4-12千兆字节(GB)的DRAM,个人计算机当前具有8-32GB的DRAM,而服务器当前具有32GB-512GB的DRAM。通常,随着DRAM芯片的数目的增加,大量主存储器的成本增加。

除了DRAM的成本之外,对于等量的储存容量,减小DRAM的封装尺寸变得越来越困难。另外,随着设备中所包含的DRAM的尺寸和数量的增加,DRAM的电容增加,与DRAM相关联的导电元件的数目和/或长度增加,并且与DRAM相关联的缓冲增加。另外,随着DRAM的电容的增加,DRAM的操作频率降低且DRAM的等待时间段增加。

在操作期间,根据需要将程序和/或数据从DRAM 14传输到SoC 12中的缓存。与在(i)缓存与(ii)对应处理器和/或图像处理设备之间的数据交换相比,这些传输具有更高的等待时间。因此,通过使用较大的L3缓存构建SOC,可以使对DRAM 14的访问最小化。尽管具有越来越大的L3缓存,每年计算系统仍需要越来越多的DRAM(更大的主存储器)。在其他条件相同的情况下,具有较大主存储器的计算机将比具有较小主存储器的计算机具有更好的性能。在当今的操作系统下,具有4GB主存储器的现代PC即使配备有最快且最好的处理器,性能实际上也会非常差。接下来解释计算机主存储器尺寸随着时间的推移不断增加的原因。

在系统启动期间,可以程序将从储存驱动器16被传输到DRAM 14。例如,中央处理器28可以在系统启动期间将程序从储存驱动器16传输到DRAM 14。仅当程序完全加载到DRAM时,中央处理器28才可以执行DRAM中储存的指令。如果CPU需要一次运行一个程序,并且用户愿意在启动新程序之前等待CPU终止先前的程序,则计算机系统确实需要很少量的主存储器。然而,这对于现在在启动新程序和即时(on the fly)在程序之间切换时习惯于立即响应时间的消费者将是不可接受的。这就是每年计算机总是需要更多DRAM的原因,并且这建立了DRAM公司制造更大DRAM的优先级。

发明内容

为了克服现有技术的缺点并提供附加的益处,公开了一种与处理器一起使用的数据储存和访问系统。处理器被配置为生成对数据的数据请求,并且该数据请求可以包括物理地址。在该实施例中,FLC缓存系统用于虚拟化计算机主存储器,使得主存储器现在可以由诸如闪速存储器的成本低得多的存储器设备制成,并且可以使用比以前可能的容量小得多的DRAM来构建计算机。FLC系统包括具有第一FLC控制器和第一存储器的第一FLC模块,使得第一FLC模块从处理器接收数据请求。第二FLC模块包括第二FLC控制器和第二存储器。响应于第一FLC模块不具有由处理器请求的数据,第一FLC模块从第一FLC模块接收数据请求。一种储存驱动器被提供并被配置有用户文件储存部分/分区和主存储器部分/分区。当第二FLC模块不具有由第一FLC模块请求的数据时,储存驱动器接收数据请求。通过采用两阶段FLC系统,第一FLC模块现在自由地主要服务于处理器的请求,而第二FLC模块自由地将数据移入移出储存驱动器,而不会影响第一FLC模块的性能。

在一个实施例中,数据请求包括物理地址,并且第一FLC控制器包括查找表,被配置为如果第一FLC控制器包含物理地址条目,则将物理地址转换为第一虚拟地址。如果第一FLC控制器的查找表不包含物理地址条目,则将第一FLC控制器配置为将具有物理地址的数据请求转发到第二FLC控制器。术语物理地址和物理地址条目在本文中可以互换使用。第二FLC控制器可以包括被配置为将物理地址转换为第二虚拟地址的查找表。此外,如果第二FLC控制器的查找表不包含物理地址,则第二FLC控制器被配置为将具有物理地址的数据请求转发到储存驱动器。

在一个实施例中,第一FLC模块被优化为比第二FLC模块显著更快的访问时间、更低的等待时间和更低的功率消耗,但代价是相比传统DRAM主存储器的成本在每比特的基础上更高。然而,因为第一FLC模块存储器容量比第二FLC模块小得多,所以成本增加实际上可以忽略,并且更重要的是,已经通过将主存储器移入储存驱动器实现了显著的成本节省。在一个配置中,第一存储器是定制的DRAM并且包括第一存储器控制器,并且第二存储器由现成的商品DRAM制成并且包括第二存储器控制器。储存驱动器优选地使用合理的快速固态存储器,因为实际的主存储器现在物理上在储存驱动器中。当使用DRAM时,对第二FLC模块的任何未命中都将比传统的主存储器访问慢一千倍,并且必须将其影响最小化。这就是为什么提出FLC完全关联和大的缓存行技术的原因,并且这对于使未命中率(miss rate)保持可以忽略至关重要。第一FLC模块和第二FLC模块可以另外被配置为对储存在预计将来要访问的地址处的数据执行预测性获取。此外,FLC模块还可以被配置为从处理器或软件获取提示(指令),以执行将数据从现在驻留在储存驱动器中的最终主存储器预取到第一FLC模块和/或第二FLC模块中。在一个实施例中,在处理设备上执行的软件可以知道接下来需要什么数据(包括代码),并且可以向FLC系统提供指令以将该数据预取到DRAM缓存中,从而所需的数据在需要时存在。可以将其缓存在标准速度FLC或高速FLC中。在一个实施例中,数千缓存行被预取。准确的预取可以导致100%的命中率(hit rate)。

本文还公开了一种操作数据访问系统的方法。在该实施例中,数据访问系统包括具有处理器缓存的处理器、储存驱动器、包括第一FLC控制器和第一DRAM的第一FLC模块,以及包括第二FLC控制器和第二DRAM的第二FLC模块。该方法包括使用处理器生成对数据的请求,该请求包括物理地址,并且将对数据的请求提供给第一FLC模块。使用第一FLC模块,确定第一FLC控制器是否包含物理地址条目,并且响应于第一FLC控制器包含物理地址条目,从第一DRAM取回数据并将该数据提供给处理器。可替代地,响应于第一FLC控制器不包含物理地址条目,将对数据的请求和物理地址转发到第二FLC模块。在第二FLC模块处,确定第二FLC控制器是否包含物理地址条目,并且响应于第二FLC控制器包含物理地址条目,从第二DRAM取回数据(以与所请求的数据有关的完整缓存行条目的形式),并将所请求的缓存行数据(储存在缓存行中的数据)提供给第一FLC模块。

该方法还可以包括响应于第二FLC控制器不包含物理地址,将对数据的请求(以与所请求的数据相对应的缓存行的形式)和物理地址转发到储存驱动器。该方法还可以包括储存驱动器从储存驱动器的保留为附加主存储器的部分取回数据,并且然后将数据(缓存行)提供给第二FLC模块。此外,响应于第一FLC控制器包含物理地址并且将数据提供给处理器,FLC控制器更新状态寄存器,以反映包含数据的缓存行的最近使用。

在一个实施例中,从第二DRAM取回数据并且将该数据提供给第一FLC模块还包括,将物理地址储存在第一FLC控制器中,并且将数据储存在第一DRAM中。如果第一DRAM不具有可用空间,则从第一DRAM和第一FLC地址查找条目表中移除最近最少使用的数据,以为新数据腾出空间。在又一个实施例中,FLC模块可以主动使一部分DRAM可用于将来的处理器请求。第一FLC模块还可以主动使其DRAM的一部分是干净的,以便在需要时可以擦除储存在要清理的缓存行处的条目,以为新处理器请求的新条目腾出空间。这是通过将脏的缓存行写回到第二FLC模块来完成的。根据来自操作系统的提示(预取请求),不再需要的程序/数据可以进一步从FLC DRAM中擦除。这样可以节省时间和功率。此外,这还防止了每当不再使用的程序/数据被清除到SSD时意外写入SSD。在一个实施例中,第二阶段DRAM(在本文中称为DRAM-SS)比第一阶段DRAM大大约八倍。在一个实施例中,第二阶段DRAM的一部分被主动维持为干净(空),以为第一阶段DRAM的被移动到第二阶段DRAM的全部或一部分腾出空间。在一个实施例中,第二阶段DRAM的至少百分之十被维持为干净的或按需清理的,以用于预取数据或用于将第一阶段DRAM内容移动到第二阶段。在一个实施例中,第一阶段DRAM的尺寸的至少一半在第二阶段DRAM中维持为空或可清理。在一个实施例中,第二阶段DRAM比第一阶段DRAM大至少四倍。在一个实施例中,第二阶段DRAM比第一阶段DRAM大至少八倍。在一个实施例中,第二阶段DRAM比第一阶段DRAM大至少十六倍。

本文还公开了一种具有几个元件的数据存储和访问系统,包括具有处理器缓存的处理器。处理器被配置为生成对第一数据的第一数据请求。该系统的另一部分是与处理器通信的第一FLC缓存系统。第一FLC缓存系统被配置为用作具有极高命中率(99.9%)的超快速主存储器缓存(比第二FLC缓存系统更快),接收对第一数据的第一数据请求。在一个实施例中,第一FLC缓存(HS)的速度是第二FLC缓存(SS)的至少两倍。在一个实施例中,第一FLC缓存(HS)的速度是第二FLC缓存(SS)的至少四倍。第一FLC缓存系统还设计用于跟踪处理器将所需的成千上万个独立线程。提供了第二FLC缓存系统,并且其与第一FLC通信,并且被配置为用作第一FLC的辅助(备份)主存储器缓存,并接收对第二数据的第二数据请求。储存驱动器配置有用户文件储存分区和主存储器分区,使得储存驱动器的主存储器分区用作实际的主存储器。可替代地,可以将分开的且专用的储存驱动器用作实际的主存储器。此外,优选地,储存驱动器的主存储器分区被配置用于高可靠性。对于基于Nand闪速存储器的储存驱动器,主存储分区优选配置有单级单元(SLC),而不是传统三级或四级单元(TLC/QLC)。

该系统可以进一步包括系统总线,其中处理器通过系统总线与多个独立的FLC缓存模块切片进行通信。在一个配置中,如果由处理器请求的第一数据未包含在第一切片FLC缓存系统中,则第一数据请求被发送到储存驱动器以从储存驱动器的主存储器分区取回第一数据,并且又如果由处理器请求的不同的第一数据未包含在第二切片FLC缓存系统中,则第一数据请求被发送到储存驱动器,以从储存驱动器的主存储器分区取回第一数据。可以预期的是,第一切片FLC缓存系统可以包括第一阶段FLC模块和第二阶段FLC模块,并且第二切片FLC缓存系统可以包括第一阶段FLC模块和第二阶段FLC模块。此外,每个FLC模块应该包括专用的FLC控制器、地址查找表和存储器。

根据详细描述、权利要求和附图,本公开的其他应用领域将变得显而易见。详细描述和特定示例仅旨在用于说明的目的,并不旨在限制本公开的范围。

通过检查以下附图和详细描述,本发明的其他系统、方法、特征和优点对于本领域技术人员将是或将变得显而易见的。旨在将全部这样的附加系统、方法、特征和优点包括在本说明书内,在本发明的范围内,并由所附权利要求保护。

附图说明

附图中的组件不一定是按比例的,而是将重点放在说明本发明的原理上。在图中,贯穿不同的视图,同样的附图标记指定对应的部件。

图1是根据现有技术的设备的功能框图。

图2是根据本公开的实施例的数据访问系统的功能框图。

图3是图示图2的数据访问系统的DRAM和储存驱动器的条目的功能框图。

图4图示了操作图2的数据访问系统的方法。

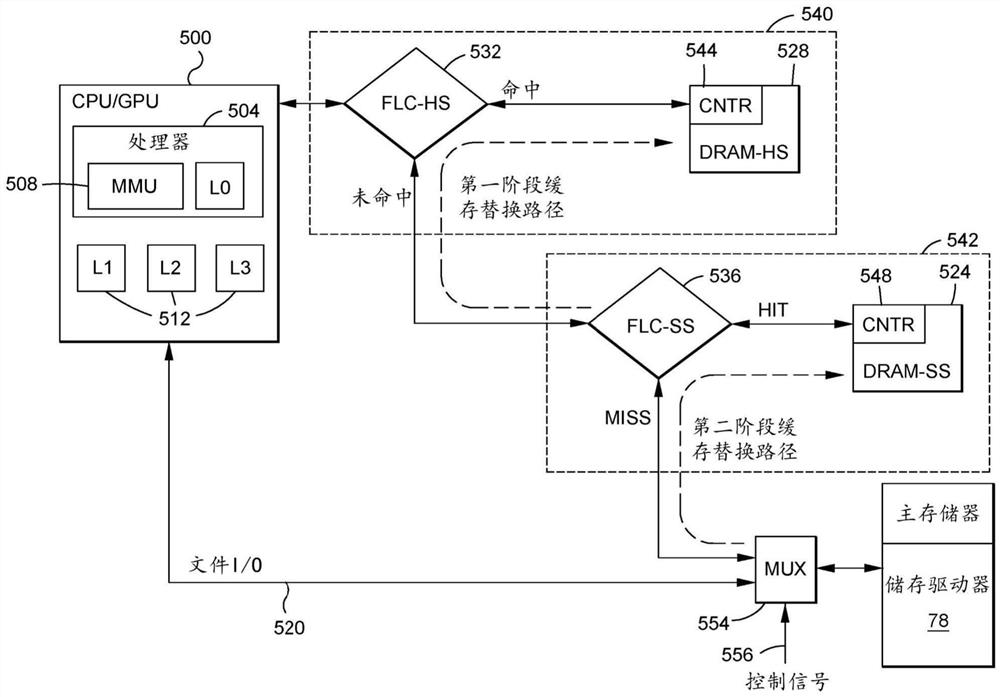

图5A是级联FLC系统的示例实施例的框图。

图5B是FLC控制器的示例实施例的框图。

图6是具有两个或更多个FLC模块的级联FLC模块的框图。

图7是如图5A所示的级联FLC模块的示例操作方法的操作流程图。

图8是具有两个或更多个分开的FLC模块的分离式FLC模块系统的框图。

图9是如图8所示的分离式FLC模块的示例操作方法的操作流程图。

图10是具有旁路路径的级联FLC系统的示例实施例的示例性框图。

图11是如图8所示的分离式FLC模块的示例操作方法的操作流程图。

图12是具有旁路路径和不可缓存数据路径的级联FLC系统的示例实施例的示例性框图。

图13提供了图12的实施例的示例性操作方法的操作流程图。

在附图中,附图标记可以被重复使用以标识相似和/或相同的元件。

具体实施方式

以下示例中的至少一些包括最终级缓存(FLC)模块和储存驱动器。FLC模块被用作主存储器缓存,并且储存驱动器被用作用户文件的物理储存,并且储存驱动器的一部分还被分区,以供FLC模块用作实际的主存储器。这与传统计算机不同,在传统计算机中,实际的主存储器由DRAM制成。数据首先尝试从FLC模块的DRAM中读取或写入到FLC模块的DRAM,物理储存驱动器的主存储器部分在来自FLC模块的未命中的情况下提供最后手段备份。FLC模块中的查找表在本文中称为内容可寻址存储器(CAM)。FLC模块的FLC控制器使用以下所述的各种CAM技术控制对FLC模块和储存驱动器中的存储器的访问。CAM技术和其他公开的特征降低了设备中DRAM所需的储存能力,同时最大化存储器访问速率且最小化功率消耗。设备可以是移动计算设备、台式计算机、服务器、网络设备或无线网络设备。设备的示例包括但不限于计算机、移动电话、平板电脑、相机等。以下示例中的DRAM通常不用作主存储器,而是用作慢得多的主存储器的缓存,该主存储器现在位于部分储存驱动器中。因此,储存驱动器的分区是主存储器,而DRAM是主存储器的缓存。

图2示出了数据访问系统70,其包括处理设备72、系统总线74、FLC模块76和储存驱动器78。数据访问系统70可以例如在计算机、移动电话、平板电脑、服务器和/或其他设备中实现。处理设备72可以包括,例如:中央处理器(或中央处理单元(CPU));图形处理器(或图形处理单元(GPU));录像机;相机信号处理器(ISP);以太网接口,诸如千兆比特(Gb)以太网接口;串行接口,诸如通用串行总线(USB)接口和串行高级技术附件(SATA)接口;以及外围组件互连快速(PCIe)接口;和/或其他图像处理设备。可以在一个或多个模块中实现处理设备72。作为示例,处理模块72中的第一个被示出为包括缓存存储器,诸如零级(L0)缓存、一级(L1)缓存、二级(L2)缓存或三级(L3)缓存中的一个或多个。在所示的示例中,第一处理设备可以包括中央处理器73和L1-L3缓存75。中央处理器73可以包括L0缓存77。中央处理器73还包括存储器管理单元(MMU)79,其可以控制对缓存75、77的访问。MMU 79也可以被认为是用于处理器缓存的存储器地址转换器。MMU负责将CPU虚拟地址转换为系统物理地址。大部分现代CPU使用物理地址缓存,这意味着L0/L1/L2/L3缓存是被物理寻址的。来自CPU的缓存未命中也使用物理地址发送到系统总线。

下面描述为由处理设备执行的任务可以由例如中央处理器73和/或MMU 79执行。

处理设备72经由系统总线74连接到FLC模块76。处理设备72经由总线和在处理设备72与系统总线74之间的接口(i)以及在系统总线74与储存驱动器78之间的接口(ii)而被连接到储存驱动器78。接口可以包括例如以,太网接口、串行接口、PCIe接口和/或嵌入式多媒体控制器(eMMC)接口。储存驱动器78可以位于世界上远离处理设备72和/或FLC控制器80的任何地方。储存驱动器78可以经由一个或多个网络(例如,WLAN、互联网网络或远程储存网络(或云))与处理设备72和/或FLC控制器80通信。

FLC模块76包括FLC控制器80、DRAM控制器82和DRAM IC 84。术语DRAM IC和DRAM可以互换使用。尽管为了理解而被称为DRAM,但是可以使用其他类型的存储器,包括任何类型的RAM、SRAM、DRAM或执行本文所述但具有不同名称的任何其他存储器。DRAM IC 84主要用作虚拟和临时储存,而储存驱动器78用作物理和永久储存。这意味着通常DRAM IC中的位置与处理器模块生成的物理地址不具有静态/固定关系。储存驱动器78可以包括被保留用作主存储器的分区,而储存驱动器的其余部分用作传统储存驱动器空间以储存用户文件。这不同于在计算机超出DRAM中的物理主存储器空间时将发生的现有技术的请求调页(demandpaging)操作。在这种情况下,来自DRAM的大块数据/程序将被传输到硬盘驱动器和从硬盘驱动器传输。这还需要解除分配和重新分配物理地址分派,这是由MMU和操作系统完成的,这是一个缓慢的处理,因为操作系统(OS)既不具有足够的、也不具有精确的关于储存在主存储器中的数据/程序的相对重要性的信息。处理设备72寻址DRAM IC 84和储存驱动器78的主存储器分区,好像它们是单个主存储器设备。用户无法访问并且不能查看储存在储存驱动器的主存储器分区中的数据或文件,就像用户在计算机操作期间不能看见储存在RAM中的文件一样。在读取和/或写入数据时,处理设备72将访问请求发送到FLC控制器80。FLC控制器80经由DRAM控制器82访问DRAM IC 84和/或访问储存驱动器78。FLC控制器80可以直接(如虚线所示)或经由系统总线74访问储存驱动器。从处理器和程序员的视角,对专用于主存储器的储存分区的访问是通过处理器本机加载和储存操作完成的,而不是作为I/O操作。

本文描述了数据访问系统70的各种示例。在第一示例中,FLC模块76在与处理设备72、系统总线74和储存驱动器78分开的SoC中实现。在另一个实施例中,这些元件在不同的集成电路上。在第二示例中,处理设备72之一是CPU实现的处理设备。处理设备72之一可以在与FLC模块76和储存驱动器78分开的SoC中实现。作为另一个示例,处理设备72和系统总线74在与FLC模块76和储存驱动器78分开的SoC中实现。在另一个示例中,处理设备72、系统总线74和FLC模块76在与储存驱动器78分开的SoC中实现。下面公开数据访问系统70的其他示例。

DRAM IC 84可以用作缓存的最终级。DRAM IC 84可以具有各种储存容量。例如,DRAM IC 84可以具有用于移动电话应用的1-2GB的储存容量,用于个人计算机应用的4-8GB的储存容量以及用于服务器应用的16-64GB的储存容量。

储存驱动器78可以包括NAND闪速SSD或其他非易失性存储器,诸如电阻RAM和相变存储器。储存驱动器78可以具有比DRAM IC 84更大的储存容量。例如,储存驱动器78可以包括比DRAM IC 84多8-16倍的储存。如果低任务等待时间切换时间是重要的,则DRAM IC 84可以包括高速DRAM,并且即使在将来,储存驱动器78也可以由超低成本和低速DRAM制成。最终,可以构建新类别的高容量串行/顺序大内存分页(large-page)DRAM(随机访问能力受限)以用于最终主存储器。这样的串行DRAM设备可以比传统DRAM多至少两倍的成本效益,因为裸芯(die)尺寸可以比传统DRAM小至少两倍。在一个实施例中,串行DRAM将具有可以一次取回或写入的最小块(组块)尺寸,诸如一个缓存行(4KB),但是在另一个实施例中,可以建立最小块尺寸。因此,数据不被读取或写入任何位置,而是替代地仅去往/来自某一块。此外,这样的串行DRAM可以与超高速串行接口一起封装,以使高容量DRAM能够远离处理器设备安装,这将使处理器能够以其全潜力运行而不必担心过热。如图所示,储存驱动器78的一部分被分区以用作主存储器,并且因此被FLC控制器80用作FLC DRAM 84的扩展。

储存在DRAM IC 84中的缓存行可以是最近最多、最经常访问的数据和/或具有最高关联优先级的数据。储存在DRAM IC 84中的缓存行可以包括锁入(locked in)的缓存行。锁入的缓存行是指总是保持在DRAM IC 84中的数据。即使已经长时间段未访问锁入的缓存行,锁入的缓存行也不能被其他缓存行踢出。然而,锁入的缓存行可以被更新(写入)。在一个实施例中,有缺陷的DRAM单元(及其对应的缓存行)可以通过移除具有(一个或多个)有缺陷的单元的DRAM地址条目而从FLC系统锁出(locked out)(映射出),以防止FLC地址查找引擎将缓存行条目分派给该有缺陷的DRAM位置。通常在设备制造期间发现有缺陷的DRAM条目。然而在另一个实施例中,操作系统可以使用映射出功能将DRAM的一部分置于其不能由处理器用于正常操作的临时状态。这样的功能允许操作系统在系统运行实际应用时发出命令以一次一个区段(section)地检查映射出的DRAM区段的健康状况。如果发现DRAM的区段具有弱单元,则操作系统然后可以主动禁用包含(一个或多个)弱单元的缓存行,并使所谓的“弱缓存行”停止服务。在一个实施例中,FLC引擎可以包括硬件诊断功能,以减轻处理器在软件中执行DRAM诊断的负担。

在一些示例实施例中,储存在DRAM IC 84中的数据不包括不频繁使用(例如,在预定时间段内被访问多于预定次数)的软件应用、字体、软件代码、替代代码和支持不同口语的数据等。这可以帮助最小化DRAM IC 84的尺寸要求。就FLC而言,很少使用或根本不使用的软件代码可以被视为“垃圾代码”,并且它们在系统启动处理中可能不会被FLC加载,并且如果它们被加载且仅被使用一次,例如被FLC清除且在将来再也不会被加载,因此释放了DRAM IC 84的空间以用于真正有用的数据/程序。随着DRAM IC 84的尺寸减小,DRAM性能增加,并且功率消耗、电容和缓冲减小。随着电容和缓冲减少,等待时间减少。而且,通过消耗较少的功率,相应设备的电池寿命增加。当然,随着更大的DRAM IC 84,整个系统的性能将提高,但这是以成本和功率的增加为代价的。

FLC控制器80响应于从处理设备72接收到请求而执行CAM技术。CAM技术包括将由处理设备72提供的请求的第一物理地址转换为虚拟地址。这些虚拟地址独立于并且不同于由处理设备72原始生成并由处理设备72映射到第一物理地址的虚拟地址。DRAM控制器82将由FLC控制器80生成的虚拟地址转换(或映射)为DRAM地址。如果DRAM地址不在DRAM IC 84中,则FLC控制器80可以(i)从储存驱动器78获取数据,或者(ii)可以指示(或发信号通知)处理设备72中的发生了缓存未命中的对应一个。从储存驱动器78获取数据可以包括将由FLC控制器80接收的第一物理地址映射到第二物理地址以访问储存驱动器78中的数据。当将物理地址转换为虚拟地址时,FLC控制器80可以检测缓存未命中。

然后,FLC控制器80可以在缓存未命中的处理设备72之一访问数据的储存驱动器78时,向其发信号通知。这可以包括通过将第一/原始物理地址映射到储存地址并然后基于所映射的储存地址访问储存驱动器78,来基于第一(原始)物理地址访问储存驱动器78中的数据。

CAM技术用于在FLC控制器中将第一物理地址映射到虚拟地址。CAM技术提供了完全关联地址转换。这可以包括将处理器物理地址与储存在FLC控制器80的目录中的全部虚拟地址条目进行逻辑比较。应该避免集合关联地址转换,因为其将导致更高的未命中率,从而将降低处理器性能。初始系统启动后,位于具有完全关联且大的缓存行架构(FLC)的DRAMIC 84中的数据的命中率可能高达99.9%,取决于DRAM IC 84的尺寸。通常,DRAM IC84的尺寸在处理器和/或处理设备的最小空闲时间情况下应确保接近100%的中期(几分钟的时间)平均命中率。例如,这可以使用用于移动电话应用的1-2GB DRAM IC、用于个人计算机应用的4-8GB DRAM IC和用于服务器应用的16-64GB DRAM IC来实现。

图3示出了数据访问系统70的DRAM IC 84和储存驱动器78的条目。DRAM IC 84可以包括DRAM条目

每个DRAM条目

在操作期间,处理设备72之一可以生成针对数据块(或该数据块的部分)的请求信号。如果数据块未位于DRAM IC 84中,则FLC控制器80可以访问储存驱动器78中的数据块。当FLC控制器80正在从储存驱动器78访问数据时,FLC控制器80可以将警报信号(诸如总线错误信号)发送回请求数据的处理设备。警报信号可以指示FLC控制器80在从慢速储存设备访存数据的处理中,并且因此系统总线74在一段时间内未准备好将数据传输到处理设备72。如果使用总线错误信号,则可以将总线错误信号的传输称为从FLC模块76到处理设备和/或处理设备72的SoC的“总线中止”。然后,处理设备72可以在等待FLC储存事务准备好的同时执行其他任务。然后,其他处理器任务可以通过使用已经储存在例如处理设备的SoC中的一个或多个缓存(例如,L0-L3缓存)中的数据和已经储存在FLC DRAM中的其他数据来继续进行。这也最小化了处理器和/或处理设备的空闲时间。

如果执行顺序访问,则FLC控制器80和/或DRAM控制器82可以对储存在预计将来要访问的地址处的数据执行预测性获取。这可能发生在系统启动期间和/或发生在系统启动之后。FLC控制器80和/或DRAM控制器82可以:跟踪数据和/或软件使用;以及评估即将要执行的代码线;跟踪存储器访问模式;并基于该信息预测预计要访问的数据的下一个地址。下一个地址可以是DRAM IC 84和/或储存驱动器78的地址。作为示例,独立于和/或未先前接收数据请求的FLC控制器80和/或DRAM控制器82可以访问储存在储存驱动器78中的数据,并将该数据传输到DRAM IC 84。

可以经由网络中的服务器(可以称为“云”)来实现上述示例。每个服务器可以包括FLC模块(例如,FLC模块76)并且彼此通信。服务器可以共享DRAM和/或储存在DRAM IC和储存驱动器中的存储器。每个服务器可以经由网络访问其他服务器中的DRAM和/或储存驱动器。每个FLC模块可以类似于图2的FLC模块来操作,并且还可以经由云访问每个其他服务器中的DRAM和/或存储器。在服务器与云之间传输的信号可以在传输之前被加密,并且在到达服务器和/或云的网络设备时被解密。服务器还可以共享和/或访问云中的存储器。作为示例,由服务器之一的FLC控制器生成的虚拟地址可以对应于以下物理地址:FLC控制器的FLC模块的DRAM;服务器之一的储存驱动器;其他服务器之一的FLC模块的DRAM;其他服务器之一的储存驱动器;或者云的储存设备。如果发生缓存未命中,则服务器之一的FLC控制器和/或处理设备可以访问其他FLC模块、储存驱动器和/或储存设备中的DRAM和/或存储器。简而言之,储存设备可以在云或网络中可访问。如果利用位于云中的储存驱动器,则这减小了计算设备的尺寸和成本,并且因此计算设备不需要储存驱动器。虽然使储存驱动器可在云或网络中访问可能比使储存驱动器与DRAM缓存和处理器共位要慢,但这允许储存驱动器在数个不同的处理设备和DRAM缓存之间共享。在一个示例环境中,汽车可以具有在车辆周围布置的众多处理器,并且每个处理器可以配置有DRAM缓存系统。代替每个处理器也具有SSD驱动器,可以在全部处理设备之间共享单个SSD驱动器。在本文公开的很高命中率的情况下,几乎不访问SSD驱动器。这样的布置具有较低成本、小整体尺寸和易于维护的益处。

上述示例还可以在数据访问系统中实现,该数据访问系统包括:具有多个芯片的多芯片模块;开关;以及具有主FLC模块的主芯片。多芯片模块经由开关连接到主芯片模块。每个FLC模块可以类似于图2的FLC模块来操作,但是还可以经由开关访问每个其他芯片中的DRAM和/或存储器。作为示例,由芯片之一的FLC控制器生成的虚拟地址可以对应于以下物理地址:FLC控制器的FLC模块的DRAM;芯片之一的储存驱动器;其他芯片之一的FLC模块的DRAM;其他芯片之一的储存驱动器;或者云的储存设备。如果发生缓存未命中,则芯片之一的FLC控制器和/或处理设备可以访问其他FLC模块、储存驱动器和/或储存设备中的DRAM和/或存储器。

作为示例,多芯片模块中的每个辅DRAM和主芯片中的主DRAM可以具有1GB的储存容量。主芯片中的储存驱动器可以具有例如64GB的储存容量。作为另一个示例,数据访问系统可以用在汽车中。主芯片可以是例如中央控制器、模块、处理器、引擎控制模块、变速器控制模块和/或混合控制模块。主芯片可以用于控制相关系统的对应方面,诸如节气门位置、火花正时、燃料正时、变速器档位之间的转换等。多芯片模块中的辅芯片可以各自与特定车辆系统相关联,诸如照明系统、娱乐系统、空调系统、排气系统、导航系统、音频系统、视频系统、制动系统、转向系统等,并用于控制对应系统的方面。

作为又一个示例,上述示例也可以在包括主机(或SoC)和混合驱动器的数据访问系统中实现。主机可以包括中央处理器或其他处理设备,并经由接口与混合驱动器通信。接口可以是例如GE接口、USB接口、SATA接口、PCIe接口或其他合适的接口。混合驱动器包括第一储存驱动器和第二储存驱动器。第一储存驱动器包括FLC模块(例如,图2的FLC模块76)。当确定是否从FLC模块的DRAM和第二储存驱动器读取数据和/或向其写入数据时,FLC模块的FLC控制器执行CAM技术。

作为另一示例,上述示例还可以在包括SoC、第一高速DRAM缓存(比第二DRAM缓存快)、第二较大的DRAM缓存(比第一DRAM缓存大)和非易失性存储器(储存驱动器)的储存系统中实现。SoC与第一DRAM、第二DRAM和非易失性存储器分开。第一DRAM可以储存高优先级和/或频繁访问的数据。高百分比的数据访问请求可以指向储存在第一DRAM中的数据。作为示例,99%或更多的数据访问请求可以指向储存在第一DRAM中的数据,并且其余0.9%或更少的数据访问请求可以指向储存在第二DRAM中的数据,并且小于0.1%的数据指向非易失性存储器(储存驱动器中的主存储器分区)。低优先级和/或较不频率访问的数据可以储存在第二DRAM和/或非易失性存储器中。例如,用户可以打开储存在第一DRAM(高速DRAM)中的多个网络浏览器。另一方面,第二DRAM具有更高的容量,以储存众多数目的空闲应用(诸如,空闲网络浏览器选项卡)或具有低占空比操作的应用程序。因此,第二DRAM应该通过使用标准型(commodity)DRAM进行低成本优化,并且因此,其将仅具有标准型DRAM性能,也将呈现比第一DRAM更长的等待时间。然后,不适合第二DRAM的真正旧的应用的内容将被储存在非易失性存储器中。而且,在深度休眠之前,仅第一和/或第二DRAM的脏缓存行内容可以被写入非易失性存储器。在从深度休眠唤醒时,仅立即需要的内容才会被带回到第二和第一FLCDRAM缓存。结果,从深度休眠的唤醒时间可能比使用传统DRAM主存储器解决方案的计算机快几个数量级。

SoC可以包括一个或多个控制模块、接口模块、缓存(或FLC)模块和图形模块。缓存模块可以类似于图2的FLC模块来操作。控制模块经由接口模块连接到缓存模块。缓存模块被配置为基于相应的层次级别来访问第一DRAM、第二DRAM和非易失性存储器。每个控制模块可以包括相应的L1、L2和L3缓存。每个控制模块还可以包括一个或多个附加缓存,诸如L4缓存或其他更高级别的缓存。SoC与第一DRAM之间可以存在许多信号线(或导电元件)。这允许在SoC与第一DRAM之间数据的快速并行和/或串行传输。SoC与第一DRAM之间的数据传输比(i)SoC与第二DRAM之间以及(ii)SoC与非易失性存储器之间的数据传输更快。

第一DRAM可以具有第一部分,该第一部分具有与L3缓存、L4缓存和/或最高级缓存相同或更高的层次级别。第一DRAM的第二部分可以具有与第二DRAM和/或非易失性存储器相同或更低的层次级别。第二DRAM可以具有比第一DRAM更高的层次级别。非易失性存储器可以具有与第二DRAM相同或更高的层次级别。控制模块可以基于例如缓存需要来改变第一DRAM、第二DRAM和/或非易失性存储器中的每一个的部分或全部的层次级别。

控制模块、连接到接口模块的图形模块和/或连接到接口模块的其他设备(SoC内部或外部)可以将请求信号发送到缓存模块,以在第一DRAM、第二DRAM和/或非易失性存储器中储存和/或访问数据。缓存模块可以控制对第一DRAM、第二DRAM和非易失性存储器的访问。作为示例,控制模块、图形模块和/或连接到接口模块的其他设备可能不知道连接到SoC的DRAM的数目和/或尺寸。

缓存模块可以将从控制模块、图形模块和/或连接到接口模块的其他设备接收的第一处理器物理地址和/或请求转换为第一DRAM和第二DRAM的虚拟地址和/或非易失性存储器的储存地址。缓存模块可以储存一个或多个查找表(例如,完全集合关联查找表),用于将第一处理器物理地址转换为第一和第二DRAM的虚拟地址和/或将第一处理器物理地址转换为储存地址。结果,缓存模块以及第一DRAM、第二DRAM和非易失性存储器(储存驱动器的主存储器分区)中的一个或多个可以作为相对于控制模块、图形模块和/或连接到接口模块的其他设备的单个存储器(主存储器)进行操作。图形模块可以控制从控制模块和/或SoC到显示器和/或另一视频设备的视频数据输出。

控制模块可以在(i)缓存模块与(ii)L1缓存、L2缓存和L3缓存之间交换(或传输)数据、数据集合、程序和/或其部分。缓存模块可以在第一DRAM、第二DRAM和非易失性存储器中的两个或更多个之间交换(或传输)数据、数据集合、程序和/或其部分。这可以独立于控制模块执行和/或在不从控制模块接收控制信号以执行传输的情况下执行。在第一DRAM、第二DRAM和非易失性存储器中的一个或多个中的数据、数据集合、程序和/或其部分的储存位置可以基于对应的优先级,使用频率,访问频率,和/或与数据、数据集合、程序和/或其部分相关联的其他参数。数据、数据集合、程序和/或其部分的传输可以包括传输数据块。每个数据块可以具有预定尺寸。作为示例,从第二DRAM到第一DRAM的数据交换可以包括多个传输事件,其中每个传输事件包括传输数据块(例如4KB数据)。

为了获得最佳性能,第一DRAM的缓存模块必须与大的缓存行尺寸完全关联(FLC缓存解决方案)。然而,对于可以忍受更高未命中率的应用,替代地可以将集合关联架构仅用于第一级DRAM缓存。但是即使那样,其仍然具有大的缓存行尺寸,以减少缓存控制器条目表的数目。至于第二级DRAM缓存,使用完全关联和大的缓存行缓存,因为任何其他情况都可能缩短非易失性主存储器的寿命。

第一DRAM可以具有第一预定量的储存容量(例如,0.25GB、0.5GB、1GB、4GB或8GB)。0.5GB的第一DRAM比典型的L2缓存大512倍。第二DRAM可以具有第二预定量的储存容量(例如,对于基于非服务器的系统为2-8GB或更多,或者对于基于服务器的系统为16-64GB或更多)。非易失性存储器可以具有第三预定量的储存容量(例如,16-256GB或更多)。非易失性存储器可以包括固态存储器,诸如闪速存储器或磁阻随机存取存储器(MRAM)和/或旋转磁介质。非易失性存储器可以包括SSD和HDD。尽管储存系统具有第二DRAM和非易失性存储器(储存驱动器的主存储器分区),但是第二DRAM和非易失性存储器中的任何一个都可以不包括在储存系统中。

作为另一示例,上述示例也可以在包括SoC和DRAM IC的储存系统中实现。SoC可以包括经由环形总线访问DRAM IC的多个控制模块(或处理器)。环形总线可以是使访问等待时间最小化的双向总线。如果成本比性能更重要,则环形总线可以是单向总线。中间设备可以位于控制模块与环形总线之间和/或环形总线与DRAM IC之间。例如,上述缓存模块可以位于控制模块与环形总线之间或环形总线与DRAM IC之间。

控制模块可以共享DRAM IC和/或具有DRAM IC的指定部分。例如,DRAM IC的第一部分可以被分配为第一控制模块的缓存。DRAM IC的第二部分可以被分配为第二控制模块的缓存。DRAM IC的第三部分可以被分配为第三控制模块的缓存。DRAM IC的第四部分可以不被分配为缓存。

作为另一示例,上述示例也可以在服务器系统中实现。服务器系统可以被称为储存系统,并且包括多个服务器。服务器包括相应的储存系统,它们经由网络(或云)彼此通信。一个或多个储存系统可以位于云中。每个储存系统可以包括相应的SoC。

SoC可以具有相应的第一DRAM、第二DRAM、固态非易失性存储器、非易失性存储器和I/O端口。I/O端口可以经由相应的I/O通道(诸如外围组件互连快速(PCIe)通道)和相应的网络接口(诸如诸如外围组件互连快速(PCIe)通道)与云通信。I/O端口、I/O通道和网络接口可以是以太网端口、通道和网络接口,并以预定速度(例如,1千兆比特每秒(Gb/s)、10Gb/s、50Gb/s等)传输数据。一些网络接口可以位于云中。多个储存系统的连接提供了低成本、分布式和可扩展的服务器系统。多个公开的储存系统和/或服务器系统可以彼此通信并且被包括在网络(或云)中。

固态非易失性存储器可以各自包括例如NAND闪速存储器和/或其他固态存储器。非易失性存储器可以各自包括固态存储器和/或旋转磁介质。非易失性存储器可以各自包括SSD和HDD。

服务器系统的架构提供DRAM作为缓存。DRAM可以被分配为相应的SoC的L4和/或最高级缓存,并且具有高带宽和大储存容量。堆叠的DRAM可以包括例如DDR3存储器、DDR4存储器、低功率双倍数据速率四型(LPDDR4)存储器、宽I/O2存储器、HMC存储器和/或其他合适的DRAM。每个SoC可以具有一个或多个控制模块。控制模块经由相应的环形总线与对应的DRAM通信。环形总线可以是双向总线。这在控制模块和对应的DRAM之间提供了高带宽和最小等待时间。

每个控制模块可以访问储存在以下中的数据和/或程序:在相同或不同SoC的控制模块中;任何DRAM中;在任何固态非易失性存储器中;和/或任何非易失性存储器中。

SoC和/或SoC的端口可以具有介质访问控制器(MAC)地址。SoC的控制模块(或处理器)可以具有相应的处理器集群地址。每个控制模块可以使用对应的MAC地址和处理器集群地址访问相同SoC或另一个SoC中的其他控制模块。SoC的每个控制模块可以访问DRAM。第一SoC的控制模块可以通过发送具有第二SOC的MAC地址和第二SoC中的第二控制模块的处理器集群地址的请求信号,来请求储存在连接到第二SoC的DRAM中的数据和/或程序。

每个SoC和/或SoC中的每个控制模块可以储存一个或多个地址转换表。地址转换表可以包括和/或提供以下转换:SoC的MAC地址;控制模块的处理器集群地址;DRAM、固态非易失性存储器和非易失性存储器中的存储器单元的处理器物理地址;和/或DRAM、固态非易失性存储器和非易失性存储器中的存储器单元的物理块地址。在一个实施例中,DRAM控制器生成形成虚拟地址的DRAM行和列地址位。

作为示例,数据和程序可以储存在固态非易失性存储器和/或非易失性存储器中。数据和程序和/或其部分可以通过网络分布到SoC和控制模块。控制模块执行所需的程序和/或数据可以本地储存在控制模块所位于的SoC的DRAM、固态非易失性存储器和/或非易失性存储器中。然后,控制模块可以从DRAM、固态非易失性存储器和/或非易失性存储器访问执行所需的程序和/或数据以及将其传输到控制模块中的缓存。SoC与网络之间和/或SoC之间的通信可以包括无线通信。

作为另一示例,上述示例也可以在包括SoC的服务器系统中实现。一些SoC可以并入相应的服务器中,并且可以称为服务器SoC。一些SoC(称为协同(companion)SoC)可以并入第一SoC的服务器中,也可以与第一SoC的服务器分开。服务器SoC包括相应的:控制模块(例如,中央处理模块)集群;集群内环形总线,FLC模块,存储器控制模块,FLC环形总线以及一个或多个跳跃总线。跳跃总线(i)经由芯片间总线成员和对应的端口在服务器SoC与协同SoC之间延伸,以及(ii)通过协同SoC延伸。跳跃总线可以指代延伸到跳跃总线站、适配器或节点以及一个或多个SoC的对应端口以及从其延伸的总线。跳跃总线可以延伸通过跳跃总线站和/或一个或多个SoC。到或从跳跃总线站的单个数据传输可以称为单个跳跃。当在发送设备和接收设备之间传输数据时,可以执行多个跳跃。数据可以在每个时钟周期在总线站之间传播,直到数据到达目的地。本文公开的每个总线站可以被实现为模块,并且包括基于时钟信号在设备之间传输数据的逻辑。而且,本文公开的每个总线可以具有用于数据的串行和/或并行传输的任意数目的通道。

每个控制模块集群具有对应的集群内环形总线之一。集群内环形总线是双向的,并且提供每个集群中的控制模块之间的通信。集群内环形总线可以具有环形总线站,以用于控制模块访问在集群内环形总线上传输的数据信号。环形总线站可以用作信号复示器和/或访问节点。控制模块可以经由环形总线站连接到集群内环形总线并访问集群内环形总线。数据可以在集群内环形总线周围从在环形总线站中的第一环形总线站处的第一控制模块传输到在环形总线站中的第二环形总线站处的第二控制模块。每个控制模块可以是中央处理单元或处理器。

每个存储器控制模块可以控制对相应的FLC模块之一的访问。FLC模块可以堆叠在服务器SoC上。每个FLC模块包括FLC(或DRAM),并且可以被实现为本文所公开的任何FLC模块和类似于本文所公开的任何FLC模块进行操作。存储器控制模块可以在FLC环形总线上的相应的环形总线站处访问FLC环形总线,并且在环形总线站与FLC模块之间传输数据。可替代地,FLC模块可以在相应的环形总线站处直接访问FLC环形总线。每个存储器控制模块可以包括存储器时钟,该存储器时钟生成用于相应的FLC模块之一和/或用于环形总线和/或跳跃总线的总线站的存储器时钟信号。总线站可以间接地经由环形总线和/或跳跃总线或者直接地从存储器控制模块接收存储器时钟信号。数据可以基于存储器时钟信号循环通过总线站。

FLC环形总线可以是双向总线,并且具有两种类型的环形总线站SRB和SRH。每个环形总线站可以用作信号复示器和/或访问节点。环形总线站SRB连接到除跳跃总线之外的设备。设备可以包括:集群间环形总线0;FLC模块和/或存储器控制模块;以及图形处理模块。集群间环总线提供(i)集群之间的连接,以及(ii)交叉环形站之间的连接。交叉环形总线站提供对集群间环形总线的访问,并且可以将集群间环形总线连接到在(i)集群与(ii)环形总线站之间延伸的环形总线扩展。环形总线站位于FLC环形总线上。集群间环形总线和交叉环形总线站提供(iii)第一集群与第二FLC环形总线的环形总线站之间的连接,以及(iv)第二集群与第一FLC环形总线的环形总线站之间的连接。这允许控制模块访问第二FLC模块的FLC,并且控制模块访问第一FLC模块的FLC。

集群间环形总线可以包括芯片内迹线和芯片间迹线。芯片内迹线延伸到服务器SoC内部并在(i)环形总线站之一与(ii)端口之一之间。芯片间迹线延伸到服务器SoC外部并在相应的端口对之间。

每个服务器SoC的环形总线站SRH连接到对应的FLC环形总线和跳跃总线之一。每个跳跃总线具有多个跳跃总线站SHB,其为相应的接口提供对对应的跳跃总线之一的访问。跳跃总线站SHB可以用作信号复示器和/或访问节点。

第一跳跃总线、环形总线站和第一跳跃总线站在(i)FLC环形总线与(ii)服务器SoC中的液晶显示器(LCD)接口以及协同SoC的接口之间提供连接。LCD接口可以连接到显示器,并且可以经由GPM进行控制。协同SoC的接口包括串行附接的小型计算机系统接口(SAS)接口和PCIe接口。协同SoC的接口可以是图像处理器(IP)接口。

接口连接到相应的端口,端口可以连接到设备(诸如外围设备)。SAS接口和PCIe接口可以经由端口分别连接到SAS兼容设备和PCIe兼容设备。例如,储存驱动器可以连接到端口。储存驱动器可以是硬盘驱动器、固态驱动器或混合驱动器。端口可以连接到图像处理设备。上面公开了图像处理设备的示例。第四SoC可以经由芯片间总线成员(也称为菊花链成员)菊花链接到第三SoC。芯片间总线成员是第一跳跃总线的成员。附加的SoC可以经由端口菊花链接到第四SoC,该端口连接到第一跳跃总线。服务器SoC、控制模块和FLC模块可以经由FLC环形总线、第一跳跃总线和/或第三SoC与第四SoC通信。作为示例,SoC可以是南桥芯片,并且控制(i)服务器SoC与(ii)连接到端口的外围设备之间的通信和中断的传输。

第二跳跃总线提供经由环形总线站和第二跳跃总线站的(i)FLC环形总线与(ii)服务器SoC中的接口之间的连接。服务器SoC中的接口可以包括以太网接口、一个或多个PCIe接口以及混合(或组合)接口。以太网接口可以是10GE接口,并经由第一以太网总线连接到网络。以太网接口可以经由第一以太网总线、网络和第二以太网总线与第二SoC通信。网络可以是以太网、云网络和/或其他以太网兼容网络。一个或多个PCIe接口可以包括例如第三代PCIe接口PCIe3和迷你PCIe接口(mPCIe)。PCIe接口可以连接到固态驱动器。混合接口可以是SATA和PCIe兼容的,以根据SATA和/或PCIe协议向SATA兼容设备和/或PCIe兼容设备传输数据以及从其传输数据。作为示例,PCIe接口可以连接到储存驱动器,诸如固态驱动器或混合驱动器。接口具有相应的端口,以用于连接到服务器SoC外部的设备。

第三跳跃总线可以经由环形总线站连接到环形总线,并且可以经由跳跃总线站连接到LCD接口和端口。LCD接口可以连接到显示器,并且可以经由GPM进行控制。端口可以连接到一个或多个协同SoC。第四跳跃总线可以经由环形总线站连接到(i)环形总线,并且经由跳跃总线站连接到(ii)接口。接口可以是以太网、PCIe和混合接口。接口具有相应的端口。

服务器SoC和/或其他服务器SoC可以经由集群间环形总线彼此通信。服务器SoC和/或其他服务器SoC可以经由相应的以太网接口和网络彼此通信。

协同SoC可以包括相应的控制模块。控制模块可以经由跳跃总线站访问接口和/或控制对接口的访问。在一个实施例中,不包括控制模块。控制模块可以连接到跳跃总线站中的对应的跳跃总线站和/或接口中的对应的接口并与其通信。

作为另一示例,上述示例也可以在移动设备的电路中实现。移动设备可以是计算机、蜂窝电话或其他无线网络设备。电路包括SoC。SoC可以称为移动SoC。SoC可以称为协同SoC。移动SoC包括:控制模块集群;集群内环形总线,FLC模块,存储器控制模块,FLC环形总线以及一个或多个跳跃总线。跳跃总线(i)经由芯片间总线成员和对应的端口在服务器SoC与协同SoC之间延伸,以及(ii)通过协同SoC延伸。

集群内环形总线是双向的,并且提供控制模块之间的通信。集群内环形总线可以具有环形总线站,以用于控制模块访问在集群内环形总线上传输的数据信号。环形总线站可以用作信号复示器和/或访问节点。控制模块可以经由环形总线站连接到集群内环形总线并访问集群内环形总线。数据可以在集群内环形总线周围从在环形总线站中的第一环形总线站处的第一控制模块传输到在环形总线站中的第二环形总线站处的第二控制模块。数据可以在每个时钟周期在总线站之间传播,直到数据到达目的地。每个控制模块可以是中央处理单元或处理器。

存储器控制模块可以控制对FLC模块的访问。在一个实施例中,不包括存储器控制模块。FLC模块可以堆叠在移动SoC上。FLC模块可以是FLC或DRAM,并且可以被实现为本文所公开的任何FLC模块和类似于本文所公开的任何FLC模块进行操作。存储器控制模块可以在FLC环形总线上的相应的环形总线站处访问FLC环形总线,并且在环形总线站与FLC模块之间传输数据。可替代地,FLC模块可以在相应的环形总线站处直接访问FLC环形总线。存储器控制模块可以包括存储器时钟,该存储器时钟生成用于FLC模块、环形总线和/或跳跃总线的总线站的存储器时钟信号。总线站可以间接地经由环形总线和/或跳跃总线或者直接地从存储器控制模块接收存储器时钟信号。数据可以基于存储器时钟信号循环通过总线站。

FLC环形总线可以是双向总线,并且具有两种类型的环形总线站SRB和SRH。每个环形总线站可以用作信号复示器和/或访问节点。环形总线站SRB连接到除跳跃总线之外的设备。设备可能包括:集群;FLC模块和/或存储器控制模块;以及图形处理模块。

移动SoC的环形总线站SRH连接到FLC环形总线和对应的跳跃总线之一。每个跳跃总线具有多个跳跃总线站SHB,其为相应的接口提供对对应的跳跃总线之一的访问。跳跃总线站SHB可以用作信号复示器和/或访问节点。

第一跳跃总线、环形总线站和第一跳跃总线站在(i)FLC环形总线与(ii)液晶显示器(LCD)接口、视频处理模块(VPM)以及协同SoC的接口之间被连接。LCD接口在服务器SoC中,并且可以连接到显示器,并且可以经由GPM进行控制。协同SoC的接口包括蜂窝接口、无线局域网(WLAN)接口和图像信号处理器接口。蜂窝接口可以包括用于与其他移动和/或无线设备进行无线通信的物理层设备。物理层设备可以根据长期演进(LTE)标准和/或第三代(3G)、第四代(4G)和/或第五代(5G)移动电信标准来操作和/或发送和接收信号。WLAN接口可以根据

协同SoC可以经由芯片间总线成员连接到移动SoC。芯片间总线成员是第一跳跃总线的成员。附加的SoC可以经由端口菊花链接到协同SoC,该端口连接到第一跳跃总线。移动SoC、控制模块和FLC模块可以经由FLC环形总线和第一跳跃总线与协同SoC通信。

第二跳跃总线提供经由环形总线站和第二跳跃总线站的(i)FLC环形总线与(ii)移动SoC中的接口之间的连接。移动SoC中的接口可以包括以太网接口、一个或多个PCIe接口以及混合(或组合)接口。以太网接口可以是10GE接口,并且经由端口连接到以太网。一个或多个PCIe接口可以包括例如第三代PCIe接口PCIe3和迷你PCIe接口(mPCIe)。PCIe接口可以连接到固态驱动器。混合接口可以是SATA和PCIe兼容的,以根据SATA和/或PCIe协议向SATA兼容设备和/或PCIe兼容设备传输数据以及从其传输数据。例如,PCIe接口可以经由端口连接到储存驱动器。储存驱动器可以是固态驱动器或混合驱动器。接口具有相应的端口,以用于连接到移动SoC外部的设备。

协同SoC可以包括控制模块。控制模块可以经由跳跃总线站访问VPM和接口和/或控制对VPM和接口的访问。在一个实施例中,不包括控制模块。控制模块可以连接到跳跃总线站、VPM和/或接口并与其通信。

在该示例实施例中,选择4KB的缓存行尺寸。在其他实施例中,可以利用其他缓存行尺寸。使用这种尺寸的缓存行的一个益处是,其与由操作系统典型地分派给应用或程序作为最小存储器分配尺寸的存储器页面尺寸的尺寸相匹配。结果,4KB缓存行尺寸与操作存储器分配尺寸匹配。

处理器通常一次仅读取或写入64B(字节)。因此,使用4KB作为示例,FLC缓存行尺寸要大得多。结果,当写入或读取请求导致FLC模块处的未命中时,系统首先从储存驱动器(即储存驱动器分区中主存储器的最终级)读取完整的4KB缓存行。发生这种情况之后,系统可以将处理器数据写入取回到的缓存行,并且将该缓存行储存在DRAM中。缓存行由虚拟地址识别。一次从存储器中取出整个缓存行。此外,整个缓存行都被转发,诸如从FLC-SS模块到FLC-HS模块。操作系统中可能存在100,000个甚至100万个甚至更多的缓存行。

将FLC模块缓存与CPU缓存进行比较,这些元素是分开的且不同的缓存。如图所示,CPU(处理器缓存)是处理器设备的一部分,并且按照现有技术进行配置。FLC模块用作缓存,用作主存储器,并且与CPU缓存分开且不同。FLC模块缓存跟踪在几分钟的操作中可能需要的全部数据,如主存储器和关联的控制器一样。然而,CPU缓存仅跟踪和储存处理器在接下来的几微秒或大概一毫秒中所需要或将使用的数据。

完全关联查找使大量真正随机的处理器任务/线程能够半永久地(当以几秒至几分钟的时间测量时)驻留在FLC缓存中。这是基本特征,因为处理器正在处理的数千个任务或线程否则可能很容易丢弃(破坏)本应保存在FLC缓存中的大量任务/线程。然而,鉴于硅面积、功率或两者,完全关联查找是昂贵的。因此,同样重要的是,最大化FLC缓存行尺寸以最小化完全关联查找表中的条目的数目。实际上,重要的是,应使其大于当前64B的CPU缓存行尺寸。同时,缓存行的尺寸不应太大,因为它将给操作系统(OS)带来不必要的困难。因为现代OS通常使用4KB页面尺寸,所以在一个示例实施例中,FLC缓存行尺寸设置为4KB。如果将来OS页面尺寸增加到16KB,则FLC缓存行尺寸理论上也可以设为16KB。

为了隐藏完全关联地址查找处理的能量成本,在一个实施例中,用于地址转换表的地址缓存被包括在FLC控制器中。重要的是注意到,地址缓存不缓存任何处理器数据。而是仅缓存最近最多看到的地址转换和物理地址到虚拟地址的转换。因此,可选地址缓存不必完全关联。对于地址缓存,简单集合关联缓存就足够了,因为即使5%的未命中率也已经将执行完全关联查找处理的需要减少了至少二十倍。地址缓存还将附加地导致较低的地址转换等待时间,因为其中使用的简单集合关联缓存通常可以在1个时钟周期内转换地址。这比可以执行类似CAM的地址转换操作的最快的多阶段哈希算法快大约十到二十倍。

储存驱动器78可以是传统非易失性储存设备,诸如磁盘驱动器、固态驱动器、混合驱动器、光盘驱动器或任何其他类型的储存设备。与FLC模块相关联的DRAM以及储存驱动器的分区部分用作主存储器。在本文公开的实施例中,DRAM的量少于传统现有技术计算系统。这提供了更少的功率消耗、更低的系统成本和降低的空间要求的益处。如果系统操作需要附加的主存储器,则储存驱动器78的一部分被分配或分区(保留)以用作附加的主存储器。储存驱动器78被理解为具有储存驱动器控制器,并且储存驱动器控制器将处理来自处理设备500的对传统文件请求的请求,并且还将处理来自FLC模块的对储存在作为主存储器的扩展而保留的储存驱动器的分区中的信息的请求。

图4图示了一种示例操作方法的示例性操作方法。这只是一种可能的操作方法,并且因此,可以预期不脱离权利要求范围的其他方法。该示例性操作方法代表了如图2所示的FLC控制器系统。尽管主要关于图2中的示例描述以下任务,但是任务可以应用于本公开中的其他实施例。任务可以迭代或并行执行。

该方法在步骤408处开始,其中可以初始化系统。在步骤412处,FLC控制器从处理设备(处理器)接收对读取或写入请求的请求。请求包括处理器用来识别数据位置或数据要写入的位置的物理地址。

在判定步骤416处,确定由处理器提供的物理地址是否位于FLC控制器中。FLC控制器的存储器(SRAM)储存物理到虚拟地址映射数据。将位于FLC控制器中的物理地址指定为命中,而不位于FLC控制器中的物理地址指定为未命中。仅如果FLC控制器在其存储器中具有物理地址条目,FLC模块才可以满足处理器对数据(具有该物理地址)的请求。如果物理地址未储存在FLC控制器的存储器中,则请求必须转发到储存驱动器。

在判定步骤416处,如果在FLC控制器中识别物理地址,则请求被视为命中,并且操作前进到步骤420。在步骤420处,FLC控制器基于使用查找表的查找操作将物理地址转换为虚拟地址,该查找表储存在FLC控制器的存储器中或储存在作为分配给FLC控制器使用的DRAM的部分的存储器中。虚拟地址可以与FLC DRAM中的物理地址相关联。FLC控制器可以包括一个或多个转换映射表,用于将物理地址(来自处理器)映射到虚拟地址。图5B更详细地图示了FLC控制器及其存储器。

在将物理地址转换为虚拟地址之后,操作前进到判定步骤424。如果在判定步骤416处物理地址不位于FLC控制器中,则发生未命中,并且操作前进到步骤428。在步骤428处,FLC控制器在FLC控制器中为要读取或写入的数据分配新(在这种情况下为空)的缓存行,该缓存行尚未在FLC模块(即,FLC模块的DRAM)中。如果没有其他可用空间,则现有的缓存行可以被覆盖。步骤428包括更新存储器映射以包括处理器提供的物理地址,从而将FLC控制器建立为具有该物理地址。接下来,在步骤432处,将物理地址转换为储存驱动器地址,该储存驱动器地址是储存驱动器用于取回数据的地址。在该实施例中,FLC控制器执行此步骤,但在其他实施例中,其他设备(诸如储存驱动器)可以执行转换。储存驱动器地址是储存驱动器使用或理解的地址。在一个实施例中,储存驱动器地址是PCI-e地址。

在步骤436处,FLC控制器将储存地址转发到储存驱动器,例如,基于PCI-e的设备、NVMe(非易失性存储器快速)类型的设备、SATTA SSD设备或现在已知或将来开发的任何其他储存驱动器。如上所述,储存驱动器可以是传统硬盘驱动器、SSD或混合驱动器,并且储存驱动器的一部分在传统意义上用于储存文件,诸如文档、图像、视频等。储存驱动器的一部分还被使用并分区为主存储器,以补充(多个)FLC模块的DRAM提供的储存容量。

前进到步骤440,储存驱动器控制器(未示出)从储存驱动器取回由处理器提供的物理地址处的缓存行,并将缓存行提供给FLC控制器。由缓存行地址识别的缓存行储存所请求的数据或被指定为数据被写入的位置。这可以以本领域中已知的方式发生。在步骤444处,FLC控制器将缓存行写入FLC DRAM,并且将其与物理地址相关联,使得该关联被维持在FLC控制器中的查找表中。

步骤444的另一部分是对FLC状态寄存器的更新,以指定最近最多使用的缓存行或数据。可以储存在DRAM中或分开的寄存器中的FLC状态寄存器是寄存器,其跟踪FLC DRAM中的缓存行或数据何时由处理器持续使用、访问或写入。作为缓存机制的一部分,最近使用的缓存行被维持在缓存中,以便当请求时最近使用的数据对于处理器再次随时可用。处理器最近最少使用、访问或写入的缓存行被覆盖,以为最近更多使用的缓存行/数据腾出空间。在这种布置中,缓存以最近最少使用的先进先出为基础进行操作。在步骤444之后,操作前进到步骤424。

在判定步骤424处,将来自处理器的请求评估为读取请求或写入请求。如果请求是写入请求,则操作前进到步骤448,并且将具有虚拟地址的写入请求发送到FLC DRAM控制器。如图2中所示并且在本领域中被理解,DRAM设备具有相关联的存储器控制器,以监督对DRAM的读取/写入操作。在步骤452处,DRAM控制器从虚拟地址生成DRAM行和列地址位,其在步骤456处用于将来自处理器的数据(处理器数据)写入FLC DRAM。然后,在步骤460处,FLC控制器更新用于缓存行或数据的FLC状态寄存器,以反映刚刚写入FLC DRAM的缓存行/数据的最近使用。因为物理地址被映射到FLC控制器存储器映射中,所以如果处理器请求,则FLC控制器现在拥有该物理地址。

可替代地,如果在判定步骤424处确定来自处理器的请求是读取请求,则操作前进到步骤464,并且FLC控制器将具有虚拟地址的读取请求发送到FLC DRAM控制器以供DRAM控制器处理。然后在步骤468处,DRAM控制器从虚拟地址生成DRAM行和列地址位,其在步骤472处用于从FLC DRAM读取(取回)数据,从而可以将数据提供给处理器。在步骤476处,将从FLCDRAM取回的数据提供给处理器,以满足处理器读取请求。然后,在步骤480处,FLC控制器更新用于数据(地址)的FLC状态寄存器,以反映从FLC DRAM读取的数据的最近使用。因为物理地址被映射到FLC控制器存储器映射中,所以如果处理器再次请求,则FLC控制器将存储器映射中的物理地址维持为随时可用。

图4的上述任务旨在为说明性示例;任务可以顺序地、并行地、同步地、同时地、连续地、在重叠时间段期间或取决于应用以不同的次序来执行。此外,取决于事件的示例和/或顺序,可能不执行或跳过任何任务。

如上所述,状态寄存器维持储存在FLC模块中的缓存行的状态。可以预期的是,可以跟踪关于缓存行和储存在缓存行中的数据的几个方面。一个这样的方面是不同缓存行相对于预设标准或相对于其他缓存行的相对重要性。在一个实施例中,最近最多访问的缓存行将被标记或定义为最重要,而最近最少使用的缓存行被标记或定义为最不重要。然后,被标记为最不重要的缓存行(诸如,最近最少使用的缓存行)将有资格被踢出FLC或被覆盖,以允许在FLC中创建新缓存行或储存新数据。本领域普通技术人员可以理解用于该任务的步骤,并且因此在本文中不进行详细描述。然而,与传统CPU缓存控制器不同,FLC控制器将附加地跟踪已由CPU/GPU写入的缓存行。发生这种情况是为了当已仅用于读取的缓存行最终从FLC中清除时,FLC控制器不会意外写入储存驱动器(诸如SSD)。在这种情况下,FLC控制器将已被写入的FLC缓存行标记为“脏(dirty)”。

在一个实施例中,某些缓存行可以被设计为锁定的FLC缓存行。可以锁定FLC中的某些缓存行,以防止从FLC中意外清除这样的缓存行。当这样的地址/数据不能容忍取回延迟时,这对于将数据的地址保留在FLC控制器中可能特别重要,并且因此将被锁定,并且因此维持在FLC中,即使其最近最少被使用。

还可以预期的是,可以实现用于锁定的缓存行的超时定时器。在该配置中,缓存行可以被锁定,但只能锁定定时器跟踪的某一时间段。定时器可以在从锁定创建的一段时间之后或者在使用缓存行之后重置。时间量可能基于缓存行、储存在缓存行中的数据或分派了缓存行的应用或程序而变化。

另外,可以预期将超时位提供给锁定的缓存行以用于以下目的:允许在很长一段不活跃之后将锁定的缓存行从FLC中清除,或者允许最终将锁定的缓存行清除为FLC模块的下一阶段或级别,并且同时继承下一FLC阶段的锁定的状态位,以最小化从高速FLC模块中清除先前锁定的缓存行所得到的缓存行/数据取回的时间损失。

图5A是级联FLC系统的示例实施例的框图。这只是级联FLC系统的一种可能的布置。不脱离权利要求范围的其他实施例是可能的。在该实施例中,提供了处理器500。处理设备500可以通常类似于图2所示的处理设备72。对于图5A的元件,并入并重复图2中元件的讨论。处理设备500可以是中央处理单元(CPU)、图形处理单元(GPU)或任何其他类型的处理系统,包括但不限于片上系统(SoC)。处理设备500包括处理器504,处理器504包括各种级别的处理器缓存512,诸如0级、1级、2级和3级缓存。还提供了存储器管理模块508,以将处理器504与处理器缓存512的各个级别接合,并将处理器(例如,用于数据请求)与处理设备500外部的元件接合。

图5A的实施例的另一部分也是储存驱动器78。储存驱动器78通常类似于图2的储存驱动器78,并且因此不再详细描述。储存驱动器78可以包括硬盘驱动器,诸如传统旋转设备或固态驱动器、组合式混合驱动器。储存驱动器78包括控制器(未示出)以监督输入和输出功能。文件输入/输出路径520通过多路复用器554将处理设备500连接到储存驱动器78。文件I/O路径520为处理器提供了直接访问储存驱动器78以进行写入操作的路径和机制,诸如将文件直接保存到储存驱动器,如在传统系统中可以发生的一样。多路复用器554是双向开关,其响应于控制信号输入556上的控制信号,选择性地通过来自FLC-SS 536或文件I/O路径520的输入。

在具有如图2、5A,6、8、10和12所示的FLC的实施例中,储存驱动器具有被分配、分区或保留为主存储器的扩展(RAM存储器的扩展)的区段。因此,储存驱动器78的一部分用于用户文件的传统储存,该用户文件诸如文档、图片、视频、音乐并可由用户在传统文件夹或目录结构中查看。储存驱动器78的另一部分被分配、分区或保留以供FLC系统用作DRAM主存储器的扩展,以储存处理器使用的活跃程序和指令,诸如操作系统、驱动程序、应用代码和处理设备正在处理的活跃数据。主存储器是计算机系统的短期数据储存,因为其储存计算机正活跃使用的信息。术语主存储器指代主存储器、主要存储器、系统存储器或RAM(随机存取存储器)。要储存在主存储器中但最近最少使用的数据(操作系统、驱动程序、应用代码和活跃数据)储存在储存驱动器的主存储器分区中。在图2、5A,6、8、10和12的实施例中,以及在本文描述的其他实施例中,系统总线可以位于处理设备与FLC模块之间,如图2所示。

尽管用对于I/O操作储存驱动器78的主存储器分区比RAM慢,但是FLC模块的命中率是如此之高(诸如99%或更高)以至于对储存驱动器中主存储器分区的I/O很少发生,并且因此不会降低性能。对储存驱动器78及其主存储器分区的讨论适用于其他图中所示的储存驱动器。在示出和描述的全部实施例中,储存驱动器的主存储器分区的内容可以被加密。可能发生加密以防止查看储存在储存驱动器78(非易失性)的主存储器分区中的个人信息、Internet历史、密码、文档、电子邮件、图像。通过加密,如果计算设备被丢弃、回收或丢失,则无法读取该敏感信息。与RAM断电后不维持储存的数据不同,即使在断电事件时,储存驱动器也将维持数据。

如图5A所示,是以级联配置布置的两个最终级缓存(FLC)模块540、542。每个模块540、542称为FLC阶段。尽管示出有两个级联阶段,但是可以级联更多阶段。每个FLC阶段(模块)540、542通常类似于图2中所示的FLC模块76,并且因此,在本文中不详细描述这些单元。在该级联配置中,FLC模块540是高速(HS)模块,其被配置为以比作为标准速度模块的其他FLC模块542更高的带宽、更低的等待时间和更低的功率使用来操作。由于与FLC-SS相比FLC-HS模块被更经常地利用,所以进一步增加了FLC-HS模块542的低功率、高速方面所实现的益处。其是主要使用的存储器,并且具有大于99%的命中率,因此可以在大多数主存储器访问中提供速度和功率节省。FLC模块542称为标准速度(SS),并且在仍然很快时相对操作速度针对更低成本进行优化。因为标准速度DRAM比高速DRAM具有更大的容量,所以成本节省被最大化,并且在这些FLC实施例中,标准速度DRAM的量少于通常配备8GB或16GB的RAM的现有技术计算机中所用的量。示例性FLC系统可以具有4GB的DRAM和32GB的储存驱动器分区。这将导致为具有8至16GB的RAM的典型便携式计算机节省约200美元的成本。此外,因为大部分存储器访问由高速FLC模块成功处理,所以标准速度FLC模块通常非活跃,并且因此不消耗功率。下面讨论了该配置的益处。可以预期的是,FLC-HS模块540的储存容量小于FLC-SS模块542的储存容量。在一个实施例中,FLC-SS模块的存储器量比FLC-HS模块中的存储器量大八(8)倍。然而,一些应用甚至可以容忍多于32倍的容量比。

注意到,FLC-HS控制器和DRAM-HS两者针对低功率消耗、高带宽和低等待时间(高速)进行优化。因此,两个元件均提供上述益处。另一方面,FLC-SS控制器和DRAM-SS两者针对更低成本进行优化。在一种配置中,FLC-HS控制器的查找表位于FLC-HS控制器中,并利用SRAM或其他高速/低功率存储器。然而,对于FLC-SS,查找表可以储存在DRAM-SS中。尽管具有该配置慢于具有储存在FLC-SS控制器中的查找表,但将DRAM-SS的一小部分分区用于FLC-SS所需的查找表更具成本效益。在一个实施例中,为了减少访问储存在DRAM-SS中的查找表的时间损失,可以包括DRAM-SS查找表的小的SRAM缓存以缓存最近最多看到(使用)的地址转换。这样的地址缓存不必完全关联,因为仅缓存地址转换表。集合关联的缓存(诸如在CPU L2和L3缓存中使用的缓存)就足够了,因为即使5%的未命中也已经将DRAM中进行地址转换的需要减少了20倍。这可以通过仅缓存小百分比(诸如64,000个中的1000个)的查找表条目来实现。地址缓存也可以基于最近最少使用/先进先出操作。

在该实施例中,FLC模块540包括FLC-HS控制器532和具有关联的存储器控制器544的DRAM-HS存储器528。FLC模块542包括FLC-SS控制器536和具有相关联的存储器控制器548的DRAM-SS存储器524。FCL-HS控制器532连接到处理设备500。如图所示,它们还连接到DRAM-HS 528以及FLC-SS控制器536。FLC-SS控制器536的输出连接到DRAM-SS 524,还连接到储存驱动器78。

每个DRAM 528、524的控制器544、548如本领域中所理解的进行操作以引导和控制对DRAM的读取和写入操作,并且因此,这些元件和相关操作未详细描述。尽管示出为DRAM,但是可以预期可以利用任何类型的RAM。控制器544、548与DRAM 528、524之间的连接使得能够在这些元件之间进行通信,并且允许从相应的DRAM取回数据以及将其储存到相应的DRAM。

在该示例实施例中,FLC控制器532、536包括一个或多个储存物理存储器地址的查找表,该物理存储器地址可以被转换为与DRAM 528、524中的位置相对应的地址。例如,物理地址可以被转换为虚拟地址,并且DRAM控制器可以使用虚拟地址来生成DRAM行和列地址位。DRAM 528、524用作缓存存储器。在该实施例中,查找表是完全关联的,因此具有一对一的映射,并且允许将数据储存在任何缓存块中,这不会导致两个或更多个存储器地址映射到单个缓存块之间发生冲突。

如图5A所示,标准速度FLC模块542不直接连接到处理设备500。通过仅使高速FLC模块540连接到处理设备500,标准速度FLC模块542是高速FLC模块540专用的。可以预期的是,一个高速FLC模块可以共享一个或多个标准速度FLC模块。该布置不通过必须将FLC-HS控制器532中的未命中重新路由回处理设备500而使处理器变慢,该未命中将被路由到标准速度FLC模块542,这将不可避免地消耗宝贵的系统总线资源并为处理设备500产生附加的开销。

通常,在存储器读取事件的操作期间,将具有用于所请求的数据的物理地址的数据请求从处理设备500发送到FLC-HS控制器532。FLC-HS控制器532将一个或多个可由FLC-HS控制器532访问的存储器地址表储存在关联的DRAM-HS 528中。FLC-HS控制器532确定其存储器表是否包含对应的物理地址。如果FLC-HS控制器532在其表中包含对应的存储器地址,则发生命中,即FLC-HS控制器532从DRAM-HS 528(经由控制器544)取回数据,该数据进而通过FLC-HS控制器被提供回处理设备500。

可替代地,如果FLC-HS控制器532不包含匹配的物理地址,则结果为未命中,并且请求被转发到FLC-SS控制器536。该处理在FLC-SS控制器536处重复,使得如果匹配的物理地址位于FLC-SS控制器536的存储器地址查找表中,则所请求的被转换或变换为虚拟存储器地址和经由存储器控制器548从DRAM-SS 524中取出的数据。DRAM控制器从虚拟地址生成DRAM行和列地址位。如果匹配的物理地址位于FLC-SS控制器536的存储器地址查找表中,则数据请求和物理地址由FLC-SS控制器536引导到储存驱动器。

如果所请求的数据在DRAM-HS 528中不可用,但被储存并从DRAM-SS中取回,则当取回的数据通过被传输到FLC-SS控制器536并然后到FLC-HS控制器并然后到处理器500来被提供给处理器时,将回填到DRAM-HS中。当回填数据时,如果DRAM-SS或DRAM-HS中没有可用空间,则将移除最近最少使用的数据或缓存行,或覆盖其中的数据。在一个实施例中,从高速缓存中移除的数据保留在标准速度缓存中,直到在标准速度缓存中需要附加的空间。还可以预期的是,在一些情况下,数据可以仅储存在高速FLC模块中,而不储存在标准速度FLC模块中,反之亦然。

如果所请求的数据在DRAM-HS 528中不可用,并且在DRAM-SS 524中也不可用,并且因此从储存驱动器78中取回,则当取回的数据被提供给处理器时,被回填到DRAM-HS、DRAM-SS或两者中。因此,最近最多使用的数据被储存在DRAM 528、524中,并且随着时间的推移,DRAM内容被最近最多使用的数据动态地更新。从DRAM 528、524中丢弃或覆盖最不经常使用的数据,以为最近更多使用的数据腾出空间。这些回填路径在图5A中示出为“第一阶段缓存替换路径”和“第二阶段缓存替换路径”。

图5B是FLC控制器的示例实施例的框图。这只是FLC控制器基本元件的一种配置。本领域的普通技术人员将理解,在本文公开的全部实施例的工作系统中存在附加的元件、数据路径和支持元件。这些元件、数据路径和支持元件未示出,而是聚焦于支持所公开的创新的元件。图5B中的FLC控制器532代表图5A的FLC控制器532或本文公开的其他FLC控制器。

在图5B中,示出了到处理器(500,图5A)的输入/输出路径564。处理器I/O路径564连接到FLC逻辑单元状态机(状态机)560。状态机500可以包括能够如本文所述的执行的任何设备,诸如但不限于ASIC、控制逻辑、状态机、处理器或这些元件或任何其他元件的任何组合。状态机560将系统物理地址转换为FLC虚拟地址。该状态机使用多个阶段的哈希函数执行完全关联查找处理。可替代地,状态机560可以是或使用内容可寻址存储器(CAM)来执行该转换,但这将是昂贵的。

状态机560连接到存储器576,诸如例如SRAM。存储器576储存查找表,该查找表包含储存在FLC控制器中的物理地址。这些物理地址可以转换或映射为识别可由FLC控制器532访问的缓存行的虚拟地址。存储器576可以储存地址映射和多个哈希表。使用多个哈希表降低功率消耗并减少操作延迟。

状态机560和存储器576一起操作以将来自处理设备的物理地址转换为虚拟地址。当发生“命中”时,虚拟地址通过命中I/O线568提供给DRAM。如果状态机560确定其存储器576不包含物理地址条目,则发生未命中。如果发生未命中,则FLC逻辑单元状态机将具有物理地址的请求提供给未命中I/O线572,该未命中I/O线通向储存驱动器或另一个FLC控制器。

图6是并行级联FLC模块的框图。与图5A相比,相同的元件使用相同的附图标记来标记,并且不再描述。向该实施例添加的是一个或多个附加的FLC模块550、552。在该示例实施例中,高速FLC模块550通常与高速FLC模块540相同,并且标准速度FLC模块552通常与标准速度FLC模块542相同。如图所示,高速FLC模块550连接到处理设备500,而标准速度FLC模块552通过多路复用器554连接到储存驱动器78。高速FLC模块540、550两者均诸如通过系统总线连接到处理设备500。

图6的实施例的操作通常类似于图5A和图8的实施例的操作。图7提供了图5A的实施例的操作流程图。与图5A的单个级联实施例相比,图6所示的配置具有众多益处。尽管成本更多且消耗更多空间,但具有多个并行布置的级联FLC模块提供将存储器地址分离到不同的且专用的FLC模块以及允许与两个或更多个FLC模块并行进行存储器操作的益处,同时仍然具有以上结合图5A讨论的多阶段的FLC的益处。

图7是如图5A所示的级联FLC模块的示例操作方法的操作流程图。这只是一种示例操作方法,并且本领域的普通技术人员将理解其他的操作方法。在步骤704处,将具有用于数据的物理地址的读取请求从处理设备(处理器)发送到FLC-HS模块,并且特别地发送到FLC-HS控制器。然后在判定步骤708处,FLC-HS控制器确定在FLC-HS控制器的查找表中是否识别物理地址。决策步骤708的结果可以是命中或未命中。

如果在步骤708处物理地址被定位,则结果是命中,并且操作前进到步骤712。在步骤712处,将具有虚拟地址的读取请求发送到DRAM-HS控制器。如图2中所示并且在本领域中被理解,DRAM设备具有相关联的存储器控制器,以监督对DRAM的读取/写入操作。在步骤716处,DRAM控制器从虚拟地址生成DRAM行和列地址位,其在步骤720处用于从DRAM-HS读取(取回)数据或缓存行。在步骤724处,FLC-HS控制器将数据提供给处理器以满足请求。然后,在步骤728处,FLC-HS控制器更新用于缓存行(地址或数据)的FLC状态寄存器,以反映缓存行的最近使用。在一个实施例中,数据被写入DRAM-HS,并且也被写入FLC-SS模块。

可替代地,如果在步骤708处在FLC-HS中未识别物理地址,则操作前进到步骤732,并且在FLC-HS控制器中分配新(空)的缓存行,诸如存储器查找表和DRAM-HS。因为在FLC-HS模块中未识别物理地址,所以必须为缓存行创建空间。然后,在步骤736处,FLC-HS控制器将数据请求和物理地址转发到FLC-SS模块。

如在FLC-HS模块中发生的一样,在判定步骤740处,确定在FLC-SS中是否识别物理地址。如果物理地址在FLC-SS模块中,如物理地址在FLC-SS控制器的查找表中存在所揭示的,则操作前进到步骤744。在步骤744处,将读取请求与虚拟地址一起发送到DRAM-SS控制器。在步骤748处,DRAM-SS控制器从虚拟地址生成DRAM行和列地址位,其在步骤752处用于从DRAM-SS读取(取回)数据。FLC-HS的虚拟地址与FLC-SS的虚拟地址不同,因此在每个FLC控制器中发生物理地址到虚拟地址的不同转换。

在步骤724处,FLC-HS控制器将所请求的缓存行转发到FLC-HS控制器,FLC-HS控制器进而将缓存行(具有数据)提供给DRAM-HS,从而将其缓存在FLC-HS模块中。最终,数据从FLC-HS提供给处理器。然后,在步骤760处,FLC-HS控制器更新用于数据(地址)的FLC状态寄存器,以反映提供给FLC-HS并然后提供给处理器的数据的最近使用。

如果在步骤740处在FLC-SS中未识别物理地址,则在FLC-SS控制器中发生未命中,并且操作前进到步骤764,并且在FLC-SS控制器中分配新(空)的缓存行。因为在FLC-SS控制器中未识别物理地址,所以然后必须为缓存行创建空间。在步骤768处,FLC-SS控制器将物理地址转换为储存驱动器地址,诸如例如PCI-e类型的地址。储存驱动器地址是由储存驱动器理解或由其使用以识别缓存行的位置的地址。接下来,在步骤772处,将从转换得到的储存驱动器地址转发到储存驱动器,例如PCI-e、NVMe或SATA SSD。在步骤776处,使用储存驱动器地址,储存驱动器控制器取回数据,并将取回的数据提供给FLC-SS控制器。在步骤780处,FLC-SS控制器将数据写入FLC-SS DRAM并更新FLC-SS状态寄存器。如上所述,发生更新状态寄存器以指定最近使用的缓存行,从而防止其被覆盖直到成为最近最少使用的。尽管以缓存行为基础跟踪最近最少使用状态的跟踪,但是可以预期的是,可以对于缓存行内的各个数据项跟踪最近最少使用的状态,但是这将增加复杂度和附加的开销负担。

在一个实施例中,如步骤764和752处所示,从储存驱动器取回缓存行。将整个缓存行提供给FLC-HS控制器。FLC-HS控制器将整个缓存行储存在DRAM-HS中。将处理器请求的数据储存在该缓存行中。为了满足处理器请求,FLC-HS控制器从缓存行中提取数据,并将数据提供给处理器。这可能发生在将缓存行写入DRAM-HS之前或之后。在一种配置中,仅从FLC-SS控制器向FLC-HS控制器提供缓存行,并且然后FLC-HS控制器从缓存行提取处理器请求的数据。在另一个实施例中,FLC-SS控制器首先提供所请求的数据,并且然后将缓存行提供给FLC-HS控制器。然后,FLC-HS控制器可以提供数据处理器,并且然后或并发地将缓存行写入FLC-HS。由于提取的数据首先提供给FLC-HS控制器,因此速度可能更快。

如上所述,FLC-HS控制器的虚拟地址与FLC-SS控制器的虚拟地址不相同。每个FLC控制器中的查找表是不同的,并且它们之间没有关系。结果,每个FLC控制器虚拟地址集合也是唯一的。虚拟地址可能在它们之间偶然具有相同的位,但是虚拟地址是不同的,因为他们旨在在其相应的DRAM(DRAM-HS和DRAM-SS)中使用。

图8是具有两个或更多个分开的FLC模块的分离式FLC模块系统的框图。这只是分离式FLC模块系统的一个可能的实施例,并且可以预期在不脱离权利要求的范围的情况下不同的布置是可能的。与图5A相比,相同的元件使用相同的附图标记来标记,并且这些重复的元件不再详细描述。

如图8所示,并行提供第一(a)、第二(b)直至数目n阶段的FLC模块802的级,以使得能够并行处理存储器请求。n的值可以是任何整数。参考第一FLC模块820A,FLCa控制器804A连接到处理单元500或与其通信以接收读取或写入请求。系统总线(未示出)可以驻留在FLC模块820和处理设备500之间,使得通信和请求路由可以通过系统总线发生。FLCa控制器804A还连接到与DRAMa 812A相关联的DRAM存储器控制器808A。FLCa控制器804A还直接连接到储存驱动器78或与其通信。其他FLC模块820B、820n中的每一个被类似地配置,其中每个元件共享相同的附图标记但是具有不同的标识符字母。例如,FLC模块820B包括FLCb控制器804B、DRAM存储器控制器808B和DRAMb 812B。如图所示,FLC模块820B还连接到处理设备500和储存驱动器78或与其通信。尽管示出有单个处理设备500,但是可以预期附加的处理设备(GPU/音频处理单元/……)也可以利用FLC模块820。

一个或多个FLC模块820可以被配置为具有高速/低等待时间/低功率DRAM的高速FLC模块,或者FLC模块可以是具有标准速度DRAM的标准速度模块。这允许对于不同的FLC模块不同的操作速度。这进而使处理模块500适应将重要的数据读取/写入请求引导到高速FLC模块的,而将较不重要的读取/写入请求路由到标准速度FLC模块。

在一个实施例中,每个FLC切片(FLCa、FLCb、FLCc)连接到SoC总线,并且每个FLC切片由处理设备分派地址。每个FLC切片是不同的元件,帮助分开的且不同的存储器查找表。总线地址查找表或哈希表可以用于将存储器地址映射到FLC切片。在一种配置中,物理地址中的某些比特定义了哪个FLC切片被分派给该地址。在另一个实施例中,可以在FLC切片与处理单元500之间提供双向多路复用器(未示出),以控制对每个FLC切片的访问,但是该布置可能产生使操作变慢的瓶颈。

还可以预期的是,图5A和图8的实施例可以组合,使得可以组装系统,该系统具有一个或多个具有单个FLC控制器804A的FLC模块820A以及如图5A所示的一个或多个级联FLC模块。组合这两种不同的布置的益处是实现两种布置的益处。从处理器到DRAM存在多种路径,从而增加了系统速度和带宽,同时还提供了高速两阶段FLC控制器的益处,以增加速度、带宽和降低功率消耗。可以以任何方式布置组合的系统以定制系统以满足设计需要。

图9是如图8所示的分离式FLC模块的示例操作方法的操作流程图。这只是一种示例操作方法,并且本领域的普通技术人员将理解其他的操作方法。在该方法开始之前,提供存储器查找表作为处理设备或系统总线的一部分。查找表被配置为储存来自处理器的地址与FLC模块之间的关联。在该实施例中,每个FLC模块可以称为切片,并且每个FLC切片可以具有多个FLC阶段。

在该实施例中,建立多个FLC切片以增加FLC容量和带宽。每个FLC切片被分配给系统总线存储器地址空间(区域)的一部分。此外,这些存储区域在FLC切片之间交错。交错粒度设置为与FLC缓存行尺寸匹配,以防止不同FLC控制器切片中的FLC查找表条目发生不必要的重复(通过重叠),并最终最大化FLC命中率。

在一个示例实施例中,映射以交错次序将FLC缓存行尺寸的地址块分派给FLC模块。例如,对于缓存行尺寸为4KB的FLC实现以及四个不同的FLC(FLCa、FLCb、FLCc、FLCd)的实现,由物理地址识别的存储器到FLC的以下映射(分派)如下:

第一4KB–FLCa

第二4KB–FLCb

第三4KB–FLCc

第四4KB–FLCd

第五4KB–FLCa

第六4KB–FLCb

第七4KB–FLCc

第八4KB–FLCd

第九4KB–FLCa。

该存储器映射分派方案继续遵循该模式。这可以被称为具有缓存行边界的存储器映射,以将数据分离到不同的FLC模块。就此而言,由处理设备使用的存储器地址在FLC切片之间划分,从而创建并行布置的FLC系统,该系统允许在没有任何瓶颈的情况下提高性能。这允许多个不同的程序仅利用一个FLC模块,或在全部FLC模块之间分配其存储器使用,从而增加操作速度并减少瓶颈。

在一个实施例中,每个FLC切片对应于存储器地址。在该示例操作方法中,存在四个FLC切片,定义为FLCa、FLCb、FLCc和FLCd。每个FLC切片具有唯一代码,该唯一代码标识FLC切片。例如,下面为FLC切片分派提供示例性存储器地址:

地址xxxx-00-xxxxx被分派给FLCa,

地址xxxx-01-xxxxx被分派给FLCb,

地址xxxx-10-xxxxx被分派给FLCc,

地址xxxx-11-xxxxx被分派给FLCd,

其中x是“0”和“1”的任意组合。在其他实施例中,可以利用其他寻址映射方案。

可以使用具有整数个FLC缓存行尺寸的任何其他地址块映射方案。对于部分或非整数块尺寸,在不同的FLC切片中可能存在查找表条目的重复。尽管这可能不是致命的,但仍会导致较少数目的不同地址查找表条目,并最终影响FLC缓存命中性能。

返回图9,在步骤912处,存储器地址被分派给每个FLC模块(在该实施例中,FLC1、FLC2、FLC3,但是其他实施例可以具有更多或更少数目的FLC模块)。可以如上所述以交错方式进行分派。然后,在步骤916处,处理设备生成对储存在存储器中的数据的读取请求。在其他实施例中,该请求可以是写入请求。在步骤920处,分析来自处理设备的数据请求,并且基于存储器映射,将数据请求(具有物理地址)路由到适当的FLC。这可能在系统总线中发生。基于以上提供的示例性存储器地址关联,如果物理存储器是xxxx-00-xxxxx,则该地址映射到FLCa,并且该地址被路由到分派给FLCa的处理器总线端口。然后,操作前进到步骤924,其中对于数据请求和物理地址发生图4的方法。如果存储器地址是xxxx-01-xxxxx,则该地址将映射到FLCb,并且操作前进到步骤928。如果物理存储器地址是xxxx-10-xxxxx,则其映射到FLCc,并且操作前进到步骤932,其中对于数据请求和物理地址发生图4的方法。如果物理存储器地址是xxxx-11-xxxxx,则该地址映射到FLCc,并且操作前进到步骤936,其中对于数据请求和物理地址发生图4的方法。图4的方法及其讨论并入图9的讨论中。

图10是具有旁路路径的级联FLC系统的示例实施例的示例性框图。与图5A相比,相同的元件使用相同的附图标记来标记。在该实施例中,旁路模块1004设置在高速FLC模块540与处理设备500之间并连接到高速FLC模块540与处理设备500。旁路模块1004的输入从处理设备500接收请求。旁路模块1004可以是能够分析来自处理器的请求并将其分类为要路由到旁路路径或路由到高速FLC模块540的请求的任何类型的设备。旁路模块1004可以包括但不限于状态机、处理器、控制逻辑、ASIC、任何其他类似或等效设备。

来自旁路模块1004的第一输出连接到FLC-HS控制器532。来自旁路模块1004的第二输出连接到多路复用器1008。多路复用器1008还在控制输入1012上接收控制信号。多路复用器1008可以是配置为响应于控制信号在特定时间输出输入信号之一的任何类型的开关。多路复用器1008的输出连接到标准速度FLC模块542的标准速度FLC控制器536。

下面在图11中讨论与图10所示的级联FLC模块有关的旁路模块1004和多路复用器1008的操作。通常,旁路模块1004分析来自处理设备500的请求,并确定请求是否符合应被旁路到标准速度FLC模块542或被引导到高速FLC模块540的请求。如果请求被确定为旁路类型请求,则请求由旁路模块1004重新引导到多路复用器1008,在多路复用器1008中其被选择性地切换到标准速度FLC模块536。

图11是如图8所示的分离式FLC模块的示例操作方法的操作流程图。这只是一种示例操作方法,并且本领域的普通技术人员将理解其他的操作方法。该方法在步骤1108处开始,其中处理设备生成对来自存储器的数据的读取请求。该步骤在传统情况下发生,如处理器从主存储器(诸如RAM)请求数据的处理一样。在步骤1112处,将来自处理设备的请求提供给旁路模块以进行处理。旁路模块处理请求,以确定该请求是否符合或分类为将旁路高速FLC模块的数据。出于多种不同的原因,可以对数据或某些地址进行分类以旁路高速FLC模块。

在一些实施例中,旁路数据是从性能的角度来看不够经常使用以符合储存在高速DRAM中的数据。在其他实施例中,来自处理设备的某些物理地址被指定为旁路模块路由到旁路路径的旁路地址。这称为固定地址映射,由此某些地址或地址块被引导到旁路路径。类似地,旁路判定可以基于处理器或其他软件/硬件功能指定的数据类型。

旁路指定也可以基于任务ID,该任务ID被定义为任务的重要性。定义任务重要性的任务ID可以由固定的标准集合设置,也可以基于DRAM-HS的可用容量或其他因素随着时间的推移而变化。软件引擎或算法也可以指定任务ID。旁路模块还可以被配置为在DRAM-HS中保留空间,使得仅某个任务ID可以放置在保留的DRAM-HS存储器空间中。为避免基于旁路模块控制永远不会结束或对DRAM-HS的缓存不必要地阻塞,任务ID或指定可以超时,这意味着旁路指定在固定或可编程的定时器段之后终止。任务ID还可以用于基于每个任务ID定义DRAM-HS缓存行分配容量。这是为了防止贪婪任务/线程清除非贪婪任务/线程,并且最终使整体系统性能更加均衡。操作系统还可以随着时间的推移而改变缓存行分配容量表,以反映在给定时间段期间需要同时操作的并发任务/线程的数目。

例如,示出活跃视频播放(电影)的屏幕显示具有不断改变的屏幕显示,但是当不播放视频时,该屏幕显示是静态的。结果,旁路模块可以被配置为由于视频没有重新显示到屏幕上一次或两次以上而将活跃视频显示旁路到旁路路径。然而,对于暂停的电影或在屏幕是静态的时的非视频播放期间,由于刷新屏幕时会反复使用显示数据,因此显示数据可以被(不旁路)缓存。因此,最好使数据在FLC-HS模块中形成静态显示,因为FLC-HS模块具有较低的功率消耗。这可以在软件或硬件中完成,以检测屏幕是否为重复屏幕显示。

在一个实施例中,旁路模块包括算法和机器学习引擎,该算法和机器学习引擎随着时间的推移监视哪些数据(很少使用或仅使用一次)应该从高速FLC模块旁路到标准速度FLC模块。随着时间的推移,旁路模块的具有人工智能的机器学习能力确定针对特定用户哪些数据很少使用或仅使用一次,并且因此应该被从高速FLC模块旁路。如果用户随着时间的推移更经常地使用该数据,则旁路模块的机器学习方面将进行调整并适应行为的改变,以将该数据引导到高速FLC模块进行缓存以最大化性能。

在一个实施例中,旁路模块不使用机器学习或不适应用户的行为,代替地,被旁路到除高速FLC模块之外的数据或地址是固定的、用户可编程的或软件控制的。这是一种不太复杂的方法。

还可以预期的是,处理设备可以将数据指定为旁路类型数据。这样,从处理设备到旁路模块的请求(读取或写入)将包括作为旁路类型数据的指定。这提供了另一种机制来控制哪些数据储存在高速FLC模块中,这具有软件控制的灵活性。

还可以预期并公开的是,用于数据的旁路指定可以具有定时器功能,该定时器功能在一段时间之后移除旁路指定,或者在一段时间之后,必须更新旁路指定以保持活跃。这可以防止将旁路指定应用到不再具有旁路指定的数据。

返回图11,在判定步骤1116处,确定数据是否为旁路数据。如果数据未由旁路模块指定为不应该被旁路的数据,则操作前进到步骤1120。在步骤1120处,操作执行上述方法图7。如上所述,图7的方法步骤不再重复,而是并入本申请的该部分。如图7中所解释的,该方法在这一点上的进展如同级联FLC系统。

可替代地,如果在判定步骤1116处旁路模块确定应当旁路数据,则操作前进到步骤1124,并且将具有物理地址的数据请求从旁路模块路由到旁路多路复用器。在其他实施例中,数据请求和物理地址可以被路由到旁路多路复用器。旁路多路复用器(以及本文中公开的其他多路复用器)是旁方向多路复用器,其响应于控制信号,将其输入之一传递到其输出,在该实施例中,该输出连接到标准速度FLC模块。旁路多路复用器的另一个输入来自高速FLC控制器,如图10所示。

在步骤1128处,响应于到旁路多路复用器的控制信号,旁路多路复用器将数据请求和物理地址路由到标准速度FLC-SS模块。在其他实施例中,来自旁路多路复用器的数据请求和物理地址可以被传输到不同的位置,诸如不同的高速FLC模块,或者直接传输到储存驱动器。然后,在步骤1132处,由标准速度FLC-SS模块以图4中描述的方式处理数据请求和物理地址。因为该数据被定义为旁路数据,所以不缓存在DRAM-HS或FLC-HS控制器中。图4的方法并入图11的该部分。

图12是具有旁路路径和不可缓存数据路径的级联FLC系统的示例实施例的示例性框图。与图5A和10相比,相同的元件使用相同的附图标记来标记。该示例实施例只是分开路由不可缓存数据的系统的一种可能配置,并且因此,本领域普通技术人员可以得出其他实施例和布置。除了图10的配置之外,在该实施例中还增加了不可缓存数据路径1204,该路径在旁路模块1004与第二多路复用器1208之间进行连接。第二多路复用器1208包括配置为向多路复用器提供控制信号的控制信号输入1212。第二多路复用器1208的控制信号1212确定第二多路复用器的两个输入中的哪一个被输出到DRAM-SS524。

在该实施例中,DRAM-SS 524的一部分被分区以被保留为不可缓存存储器。在DRAM-SS的不可缓存数据分区中,储存不可缓存数据。这样,不可缓存数据分区用作传统处理器/DRAM。如果处理器请求不可缓存数据,诸如通常观看一次的视频文件,则该文件由处理器通过文件I/O路径520从储存驱动器78中取回,并被提供给DRAM-SS的不可缓存分区。然后,处理器可以通过不可缓存数据路径以较小的块来取回现在储存在DRAM-SS中的该数据。视频文件(诸如电影)通常很大且通常仅观看一次,并且因此不进行缓存,因为缓存仅使用一次的数据不会带来性能上的益处。对存储器的一部分进行分区是本领域普通技术人员所理解的,并且因此,本文中不详细描述该处理。不可缓存数据也可以储存在储存驱动器78中。

在该实施例中,旁路模块1004还被配置为分析读取请求并确定读取请求是否用于被分类为不可缓存数据的数据。如果是这样,则来自处理设备500的数据读取请求通过不可缓存数据路径1204被路由到第二多路复用器1208。第二多路复用器1208响应于控制信号,确定是否将不可缓存数据读取请求或来自标准速度FLC-SS控制器536的请求传递给DRAM-SS 524。因为数据是不可缓存的,所以在将数据提供给处理器之后,数据不缓存在DRAM-HS528或DRAM-SS 524中,而是可以储存在DRAM-SS的不可缓存数据分区中。

图13提供了图12的实施例的示例性操作方法的操作流程图。这只是一种示例操作方法,并且本领域的普通技术人员将理解其他的操作方法。该操作方法类似于图11的方法,其中附加步骤指向处理不可缓存数据。在步骤1304处,处理设备生成对储存在存储器中的数据的读取请求。请求包括物理地址。然后在步骤1308处,将请求和物理地址提供给旁路模块,以确定请求是否应该路由到旁路路径,或者请求是否为用于不可缓存数据的请求,并且因此应该被路由到不可缓存数据路径。在判定步骤1312处,确定是否应该将数据请求路由到旁路路径。如果确定请求是旁路数据类型请求,则操作前进到步骤1316,并且旁路模块将数据请求和物理地址从旁路模块路由到旁路多路复用器。旁路多路复用器可以是能够接收两个或更多个输入并且将输入之一选择性地路由到输出的任何设备。旁路多路复用器是双向的,因此多路复用器单个输出处的信号可以路由到任一输入路径。输入1012上的旁路多路复用器控制信号控制旁路多路复用器的操作。

此后,在步骤1320处,响应于提供给旁路多路复用器的控制信号,将具有物理地址的数据请求从旁路多路复用器路由到FLC-SS模块。然后在步骤1324处,FLC-SS模块处理数据请求和物理地址,如图4所示。图4的方法并入图13。

可替代地,如果在判定步骤1312处确定不满足旁路标准,则操作前进到判定步骤1328,在步骤1328处判定所请求的是否为可缓存存储器请求。可缓存存储器请求是来自处理设备的对将在FLC模块之一中缓存的数据的请求,而不可缓存存储器请求是对将不缓存的数据的请求。如果请求是用于可缓存存储器的,则操作前进到步骤1332,并且基于数据请求和物理地址来执行图7的处理。图7的方法并入图13。

可替代地,如果在步骤1328处确定所请求的数据是不可缓存的,则操作前进到步骤1336。在步骤1336处,将包括物理地址的不可缓存数据请求从旁路模块路由到第二多路复用器。第二多路复用器可以通常类似于旁路多路复用器地被配置和操作。在步骤1340处,响应于第二多路复用器控制信号,将来自第二多路复用器的数据请求和物理地址提供给DRAM-SS控制器,该DRAM-SS控制器将请求引导到为不可缓存数据保留的DRAM-SS的分区。在步骤1344处,FLC-SS控制器从DRAM-SS不可缓存数据分区取回不可缓存数据,并且在步骤1348处,FLC-SS控制器将不可缓存数据提供给处理设备。取回的数据未缓存在DRAM-HS缓存或DRAM-SS缓存中,但可以维持在DRAM-SS的不可缓存分区中。因此,不可通过FLC-SS模块进行访问,而是通过不可缓存数据路径进行访问。

可以预期并公开的是,上述任何实施例、元件或变型可以以任何组合进行组装或布置以形成新实施例。例如,如图6所示,并行FLC模块布置(FLC切片)可以与两个或更多个阶段FLC模块组合。这些实施例中的任何一个都可以使用旁路模块特征和/或不可缓存数据路径来组装或要求保护。还可以预期的是,多于两个阶段的FLC模块(诸如三个或四个FLC模块阶段)可以与本文示出或描述的任何其他元件组合。

还可以理解的是,尽管相对于顺序操作示出和讨论了流程图和操作方法,但是可以理解并公开的是,各种操作可以并行发生。这可以增加操作速度、带宽并减少系统中的等待时间。

可以完全或部分地遵循IEEE标准802.11-2012、IEEE标准802.16-2009、IEEE标准802.20-2008和/或蓝牙核心规范v4.0来进行本公开中描述的无线通信方面。在各种实施方式中,蓝牙核心规范v4.0可以由蓝牙核心规范附录2、3或4中的一个或多个修改。在各种实施方式中,IEEE 802.11-2012可以由草案IEEE标准802.11ac、草案IEEE标准802.11ad和/或草案IEEE标准802.11ah补充。

尽管本文可以使用术语第一、第二、第三等来描述各种芯片、模块、信号、元件和/或组件,但是这些项目应该不由这些术语限制。这些术语可以仅用于区分一个项目和另一个项目。除非上下文明确指出,否则本文中使用的诸如“第一”、“第二”和其他数值术语的术语并不暗示顺序或次序。因此,在不脱离示例性示例的教导的情况下,下面讨论的第一项目可以被称为第二项目。

而且,各种术语用于描述组件之间的物理关系。当第一元件称为“连接到”、“接合到”或“耦合到”第二元件时,第一元件可以直接连接、接合、布置、施加或耦合到第二元件,或者可能存在中间元件。相反,当元件称为“直接连接到”、“直接接合到”或“直接耦合到”另一个元件时,可能不存在中间元件。陈述第一元件“连接到”、“接合到”或“耦合到”第二元件意味着第一元件可以“直接连接到”、“直接接合到”或“直接耦合到”第二元件。应该以类似的方式来解释用于描述元件之间的关系的其他词语(例如,“在……之间”与“直接在……之间”,“相邻”与“直接相邻”等)。

前述描述本质上仅是说明性的,并且绝不旨在限制本公开、其应用或用途。本公开的广泛教导可以以多种形式实现。因此,尽管本公开包括特定示例,但是本公开的真实范围不应被如此限制,因为在研究附图、说明书和所附权利要求之后,其他修改将变得显而易见。如本文中所使用的,短语A、B和C中的至少一个应该解释为意指使用非排他性逻辑OR的逻辑(A OR B OR C),并且不应该解释为意指“至少一个A、至少一个B和至少一个C”。应该理解的是,在不改变本公开的原理的情况下,可以以不同的次序(或并发地)执行方法内的一个或多个步骤。

在包括以下定义的本申请中,术语“模块”或术语“控制器”可以被术语“电路”代替。术语“模块”和术语“控制器”可以指代、属于或包括:专用集成电路(ASIC);数字、模拟或混合模拟/数字分立电路;数字、模拟或混合模拟/数字集成电路;组合逻辑电路;现场可编程门阵列(FPGA);执行代码的处理器电路(共享、专用或组);储存可由处理器电路执行的代码的存储器电路(共享、专用或组);提供上述功能的其他合适的硬件组件;或上述一些或全部的组合,诸如在片上系统中。

模块或控制器可以包括一个或多个接口电路。在一些示例中,接口电路可以包括连接到局域网(LAN)、互联网、广域网(WAN)或其组合的有线或无线接口。本公开的任何给定模块或控制器的功能可以分布在经由接口电路连接的多个模块和/或控制器之间。例如,多个模块和/或控制器可以允许负载平衡。在另一个示例中,服务器(也称为远程或云)模块或(远程或云)控制器可以代表客户端模块和/或客户端控制器来实现一些功能。

如上面所使用的,术语代码可以包括软件、固件和/或微代码,并且可以指代程序、例程、功能、类、数据结构和/或对象。术语共享处理器电路包括执行来自多个模块和/或控制器的一些或全部代码的单个处理器电路。术语组处理器电路包括处理器电路,该处理器电路与附加处理器电路组合,执行来自一个或多个模块和/或控制器的一些或全部代码。对多个处理器电路的引用包括分立裸芯上的多个处理器电路、单个裸芯上的多个处理器电路、单个处理器电路的多个核心、单个处理器电路的多个线程或上述的组合。术语共享存储器电路包括储存来自多个模块和/或控制器的一些或全部代码的单个存储器电路。术语组存储器电路包括存储器电路,该存储器电路与附加存储器组合,储存来自一个或多个模块和/或控制器的一些或全部代码。

术语存储器电路是术语计算机可读介质的子集。如本文中所使用的,术语计算机可读介质不包括传播通过介质(诸如在载波上)的暂时性电信号或电磁信号;因此,术语计算机可读介质可以被认为是有形的和非暂时性的。非暂时性有形计算机可读介质的非限制性示例是非易失性存储器电路(诸如闪速存储器电路、可擦除可编程只读存储器电路或掩码只读存储器电路),易失性存储器电路(诸如静态随机存取存储器电路或动态随机存取存储器电路),磁储存介质(诸如模拟或数字磁带或硬盘驱动器)和光储存介质(诸如CD、DVD或蓝光光盘)。

本申请中描述的装置和方法可以由通过将通用计算机配置为执行计算机程序中实施的一个或多个特定功能而创建的专用计算机来部分或完全实现。上述功能块和流程图元素用作软件规范,可以通过技术人员或程序员的例行工作将其转换为计算机程序。

计算机程序包括处理器可执行指令,该处理器可执行指令储存在至少一种非暂时性有形计算机可读介质上。计算机程序还可以包括或依赖于所储存的数据。计算机程序可以包括与专用计算机的硬件交互的基本输入/输出系统(BIOS),与专用计算机的特定设备交互的设备驱动程序,一个或多个操作系统,用户应用,后台服务,后台应用等。

计算机程序可以包括:(i)待解析的描述性文本,诸如HTML(超文本标记语言)或XML(可扩展标记语言),(ii)汇编代码,(iii)由编译器从源代码生成的目标代码,(iv)由解释器执行的源代码,(v)由即时编译器编译和执行的源代码等。仅作为示例,可以使用来自以下语言的语法编写源代码:C、C++、C#、Objective C、Haskell、Go、SQL、R、Lisp、

权利要求中记载的全部元件均不旨在为35USC§112(f)意义中的部件加功能元件,除非使用短语“用于……的部件”明确说明了该元件,或者在方法权利要求的情况下使用短语“用于……的操作”或“用于……的操作”。

于2018年6月18日提交的、题为“多路径或多阶段缓存改进(Multi-Path orMulti-Stage Cache Improvement)”的美国临时专利申请No.62/686,333通过引用整体并入本文,并且包括附图的并入的参考的内容应被视为本专利申请的一部分。

- 将储存系统用作主存储器的方法和装置

- 将闪存模块用作主存储器的电子系统和相关系统引导方法