一种面向存内运算的全展开非正交布线的存算阵列设计

文献发布时间:2023-06-19 11:29:13

技术领域

本发明公开了一种面向存内运算的全展开非正交布线的存算阵列设计,属于存算一体化以及类脑计算领域。

背景技术

传统计算机架构大多是冯-诺伊曼,即存算分离架构,此类架构不仅会导致数据在传输上有大量能量消耗,也会导致存储速率和运算速率的不同步,从而影响整体的运算速度。存内计算实现了存算一体化,打破了存算的“速度墙”和“功耗墙”。同时利用器件特性,单个器件可完成一次乘加操作,对于整个器件阵列拥有速度快、并行度高、能效比好的特点,适用于需要进行大量乘加运算的神经网络运算。

在存内计算的设计中,存算阵列主要完成卷积运算,全展开形式的存算阵列可以一次性对所有的数据完成卷积运算并输出卷积矩阵,但是所付出的代价是较大的面积冗余。整个存算阵列中参与运算的器件的稀疏度很高,本发明对此进行了优化,提供了一种全展开非正交布线的存算阵列设计,大幅降低了参与运算器件的稀疏度和整体存算阵列的面积。

发明内容

(一)解决的技术问题

针对现有技术的不足,本发明提供了一种面向存内运算的全展开非正交布线的存算阵列设计。

(二)技术方案

为实现上述目的,本发明提供如下技术方案:一种面向存内运算的全展开非正交布线的存算阵列设计,包括阵列,所述阵列内设置有存算单元,所述存算单元通过Data_In端口输入数据作为一运算量d,同时以在所述存算单元中预先编程的数据作为另一运算量w。在Data_In输入的数据和Bias_voltage口添加的偏置电压共同作用下使运算量d与运算量w完成乘法运算。

进一步的,所述存算阵列中的每个所述存算单元以非正交方式进行连接。

进一步的,所述存算阵列通过m×n个Data_In端口输入该阵列的输入矩阵,所述m代表输入矩阵的行数,n代表输入矩阵的列数。

进一步的,所述存算阵列可适配多种尺寸的卷积核的卷积运算。

进一步的,所述输入矩阵的数据为m*n,通过式(1)的方式展开成1×(m×n)的向量,所述式(1)为:

进一步的,所述1×(m×n)的向量由m×n个Data_In端口输入。

进一步的,所述阵列通过Data_out端口输出数据。

进一步的,所述阵列以式(2)的方式对输入矩阵完成二维卷积运算,所述式(2)为:

(三)有益效果

与现有技术相比,本发明公开的一种面向存内运算的全展开非正交布线的存算阵列设计,具备以下有益效果:

所述面向存内运算的全展开非正交布线的存算阵列设计,适用于存内计算中的卷积层运算,且可适配多种尺寸的卷积核。本发明利用二维卷积的特点,重新设计了针对全展开二维卷积的阵列设计和存算单元间连接关系,大幅降低整体存算阵列的冗余度与稀疏度,可在算力不变的情况下,有效降低整体阵列面积。

附图说明

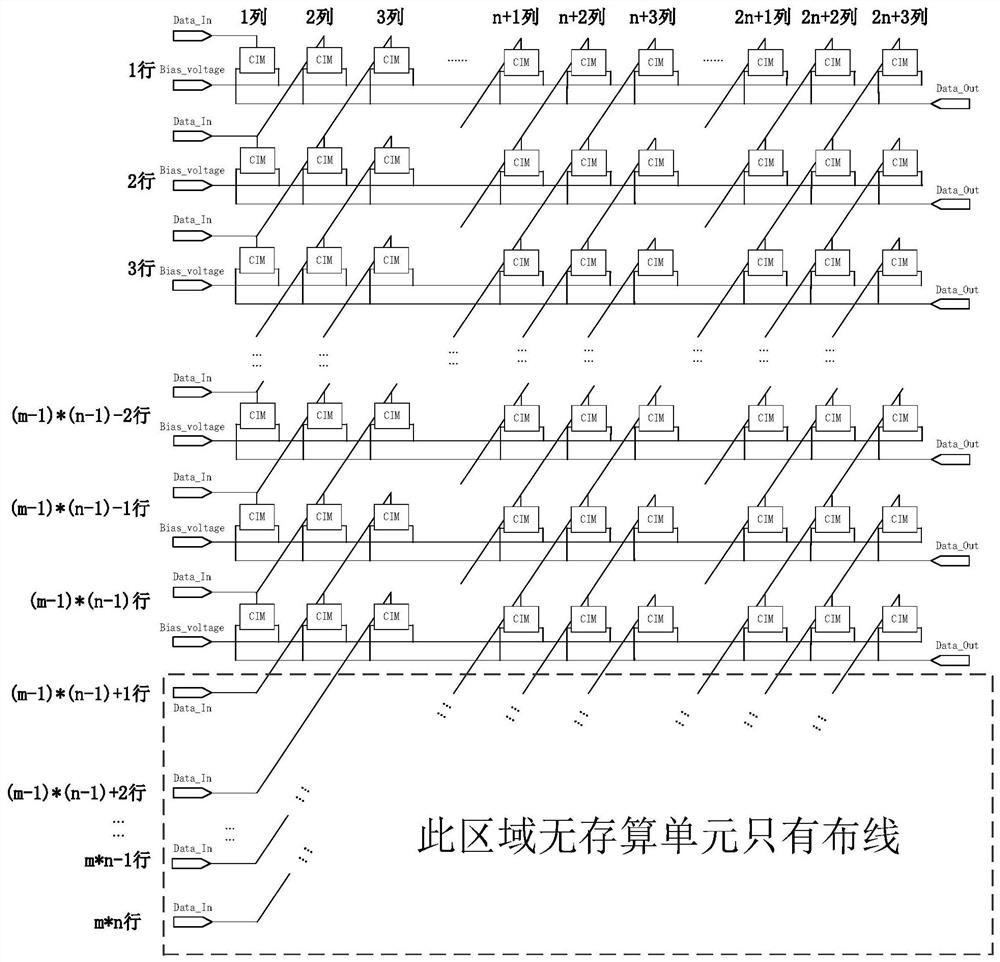

图1为本发明的整体结构框图。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

实施例1

请参阅图1,一种面向存内运算的全展开非正交布线的存算阵列设计,包括阵列,所述阵列内设置有存算单元,所述存算单元通过Data_In端口输入数据作为一运算量d,同时以在所述存算单元中预先编程的数据作为另一运算量w。在Data_In输入的数据和Bias_voltage口添加的偏置电压共同作用下使运算量d与运算量w完成乘法运算。

所述阵列中的每个所述存算单元的数据输入端按非正交布线。

下面结合具体附图和实施例对本发明作进一步说明。

图1为本发明所设计的存算阵列一实例,本实例中,输入数据为m×n的矩阵,卷积核采用3×3与2×2两种尺寸,相对应的卷积后输出矩阵尺寸为(m-2)×(n-2)与(m-1)×(n-1)。

图中标有CIM的方框为存算单元。存算单元通过Data_In端口输入数据作为一运算量d,同时以在存算单元中预先编程的数据作为另一运算量w。在Data_In输入的数据和Bias_voltage口添加的偏置电压共同作用下使运算量d与运算量w完成乘法运算。

本阵列共有2n+3列,m×n行,其中最多只有第1、2、3、n+1、n+2、n+3、2n+1、2n+2、2n+3列的存算单元预先编程有运算量w,其他运算单元只为占位用被称为冗余单元。放置冗余单元的目的一是为了后期版图布线方便,二是为了保证每个运算单元的一致性。同时只有第1到第(m-1)×(n-1)行布有存算单元,第(m-1)×(n-1)+1行至m×n行只有布线没有存算单元,此种设计一是为了满足输入矩阵与输出卷积矩阵的尺寸不匹配;二是为了后期版图的布线方便。

阵列中的每个存算单元之间的连接非正交布线,例如:第一行第一列的存算器件的数据输入口单独接出;第一行第二列与第二行第一列存算单元的数据输入端详连并接出;第一行第三列、第二行第二列与第三行第一列存算单元的数据输入端详连并接出以此类推至第(m-1)×(n-1)行的器件,由于最后行器件的数据输入端口经过斜向布线会超过第(m-1)×(n-1)行,所以本发明设置了m+n-2行的布线区,即阵列中的第(m-1)×(n-1)+1行至第m×n行,详细如图1所示。

本实例中,存算阵列可适配3×3与2×2两种尺寸的卷积核,满足了大部分卷积神经网络的运算需求。当卷积核尺寸为3×3时,使能第1、2、3、n+1、n+2、n+3、2n+1、2n+2、2n+3列的存算单元,并对其预先编程运算量w,此时输出经过加边的卷积矩阵。当卷积核尺寸为2×2时,使能第1、2、n+1、n+2列的存算单元,并对其预先编程运算量w,此时输出是不加边的卷积矩阵。

输入矩阵通过式(1)的方式展开成1×(m×n)的向量,并由m×n行的Data_In端口输入。同时,每一列存算单元会预先编程入相同的另一运算量w。

阵列中一行上每个运算单元输出的模拟量会汇集并由Data_out输出,最终该阵列可完成以式(2)的方式对输入矩阵完成二维卷积运算。

综上所述,所述一种面向存内运算的全展开非正交布线的存算阵列设计,在使用时,极大压缩了阵列的冗余度,本发明所设计的阵列面积为(2n+3)×m×n,传统方案所需的阵列面积为m

以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种面向存内运算的全展开非正交布线的存算阵列设计

- 一种用于矩阵乘法运算的权位分立存算阵列设计方法