用于产生高比率倍频时钟信号的数字时钟电路

文献发布时间:2023-06-19 11:32:36

技术领域

本发明涉及数据传输技术,更具体地,涉及一种用于在输入频率上自激高比率倍频产生时钟信号的数字时钟电路。

背景技术

对于时钟产生电路,一个困难的任务是如何形成具有超大倍频因子的锁相环(PLL)以产生高频时钟信号。在具有PLL设计的常规时钟电路中,倍频/分频因子(frequencymultiplier/divide factor)基本上被设置为16/32/64/128。很少有基于复杂级联算法的将倍频因子设置为约1000的设计。基本上,随着倍频/分频因子(multiplier/dividefactor)的增加,常规时钟电路的PLL输出中的抖动变得越来越大,从而迅速降低了时钟信号的质量。通常,时钟信号中的抖动不能超过时钟周期的5%,从而极大地限制了通过PLL设计获得超大倍频/分频因子的选择。因此,需要改进的数字时钟电路。

发明内容

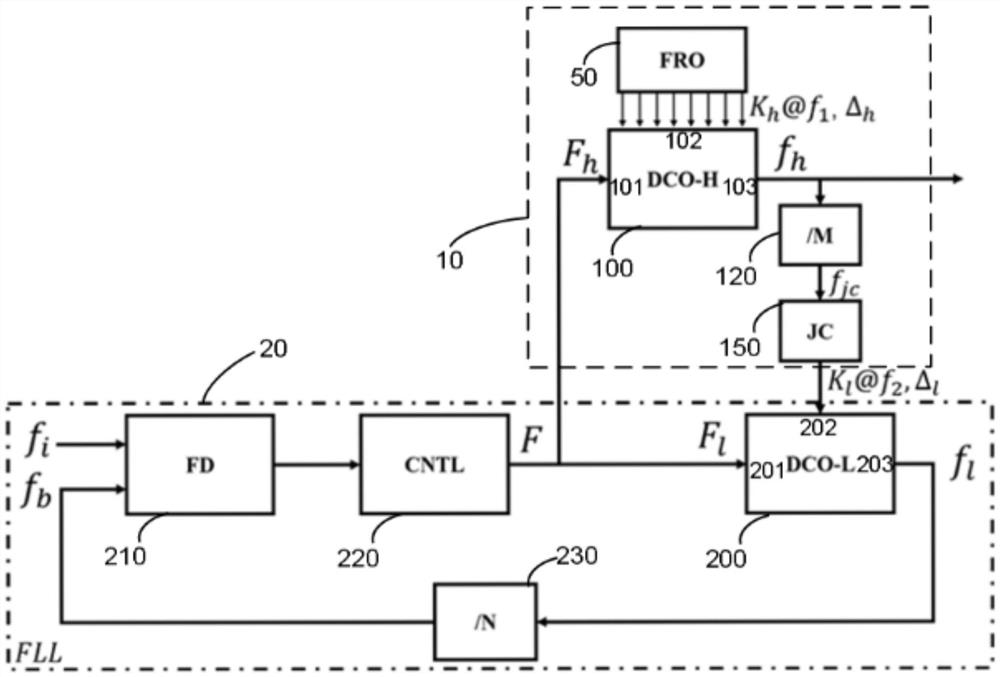

一方面,本公开提供一种用于产生高比率倍频时钟信号的数字时钟电路。所述数字时钟电路包括:第一子电路,其包括第一数控振荡器,所述第一数控振荡器被配置为由频率控制字F驱动以控制由多个第一脉冲合成的第一周期信号的第一输出频率。所述第一子电路还包括第一分频器,其用于产生具有频率等于所述第一输出频率的1/M的触发信号。此外,所述数字时钟电路包括:具有反馈回路的第二子电路。反馈回路包括:频率检测器,用于将输入频率与反馈频率进行比较;控制器,用于基于所述频率检测器的输出来调整所述频率控制字F;以及第二数控振荡器,其被配置为由所述频率控制字F加常数C来驱动,以控制由所述触发信号引起的多个第二脉冲合成的第二周期信号的第二输出频率。第二子电路还包括第二分频器,其用于将所述反馈频率设置为等于所述反馈回路中的所述第二输出频率的1/N。所述第一输出频率基本上比所述输入频率高出几个数量级。

可选地,所述第一子电路还包括自激振荡器,所述自激振荡器被配置为基于噪声产生振荡并且输出具有等间隔相移的第一频率的所述多个第一脉冲。

可选地,所述自激振荡器包括K

可选地,所述第一数控振荡器包括直接周期合成器,所述直接周期合成器包括:第一K

可选地,所述第一分频器包括L级级联的高频反转触发器,其被配置为在每一级输出端产生与每一级输入端的输入频率的1/2相等的输出频率。L级级联的高频反转触发器在最后的L级输出端输出触发信号,所述触发信号的输出频率为所述第一输出频率的1/M,其中M=2

可选地,所述第一子电路还包括由所述触发信号驱动的触发振荡器,以产生具有等间隔相移的第二频率的多个第二脉冲。

可选地,所述触发振荡器包括K

可选地,所述频率检测器包括:接收具有所述输入频率的输入信号的第一输入端口、接收来自所述反馈回路的具有所述反馈频率的反馈信号的第二输入端口、触发器子电路和组合逻辑子电路。触发器子电路包括四个D型触发器,该四个D型触发器通过1/2分频器耦接到所述第一输入端口并且部分地通过反相器耦接到所述第二输入端口,并且所述触发器子电路被配置为确定所述输入频率比所述反馈频率大还是小。组合逻辑子电路包括与所述触发器子电路耦接的两个异或门、两个反相器和两个与门。组合逻辑子电路被配置为:如果确定所述输入频率大于所述反馈频率,则在第一时间帧内将第一控制信号输出到第一控制端口,如果确定所述输入频率小于所述反馈频率,则在第二时间帧内将第二控制信号输出到第二控制端口。

可选地,所述控制器被配置为响应于所述第一控制信号、在所述第一时间帧中在每个反馈回路中将所述频率控制字F减小1,并且响应于所述第二控制信号、在所述第二时间帧中在每个反馈回路中将所述频率控制字F增大1,或者响应于没有接收到所述第一控制信号和所述第二控制信号而保持所述频率控制字F不变。

可选地,所述第二数控振荡器包括直接周期合成器,其包括第一K

可选地,在所述反馈回路中所述频率控制字F在整数I和I+1之间切换的情况下,所述第二输出频率被设置为时间平均频率。

可选地,所述反馈回路处于动态平衡中,以使所述反馈频率被锁定到所述输入频率,并且使所述第一输出频率基本上与所述输入频率线性相关,其中倍频因子为M·N乘以所述频率控制字F与所述常数C之和。

可选地,通过将所述常数选择为基本上大于所述整数I的整数,具有所述第一输出频率的所述第一周期信号被输出为具有精度提高的高频时钟信号。

可选地,所述第二分频器被配置为低频可编程计数器,其中N被设置为小于M。

另一方面,本公开提供一种用于产生高比率倍频时钟信号的数字时钟发生器。所述数字时钟发生器包括:频率检测器,其配置为将从输入端口接收的输入频率的输入信号与来自反馈回路的反馈频率的反馈信号进行比较以产生控制信号。所述数字时钟发生器还包括控制器,其耦接至所述频率检测器,以基于所述控制信号调节所述反馈回路中的频率控制字F。另外,所述数字时钟发生器包括第一数控振荡器,其耦接到控制器和第一振荡发生器,以接收具有等间隔相移的第一频率的多个第一脉冲,并且被配置为产生至输出端口的第一合成信号,所述第一合成信号具有由所述频率控制字F控制的第一输出频率。所述数字时钟发生器还包括第一分频器,其耦接至所述输出端口,以产生具有所述第一输出频率的1/M的触发信号。另外,所述数字时钟发生器包括第二振荡发生器,其由触发信号引起以产生具有等间隔相移的第二频率的多个第二脉冲。所述数字时钟发生器还包括第二数字振荡器,其耦接到所述控制器和所述第二振荡发生器,并且配置为产生至反馈回路第二合成信号,所述第二合成信号具有由所述频率控制字F加常数C控制的第二输出频率。此外,所述数字时钟发生器包括反馈回路中的第二分频器,产生所述反馈信号,所述反馈信号的反馈频率为第二输出频率的1/N。所述反馈回路使所述反馈频率被锁定至所述输入频率,从而使所述第一输出频率基本上与所述输入频率乘以M·N·(F+C)线性相关。

又一方面,本公开提供一种用于产生高比率倍频时钟信号的芯片,其包括本文所述的数字时钟电路。该芯片在FPGA或ASIC格式的数字集成电路中实现。

又一方面,本公开提供一种用于从低频输入信号产生高比率倍频时钟信号的方法。该方法包括:将低频输入信号与反馈回路中的反馈信号进行比较以产生控制信号的步骤。该方法还包括根据所述控制信号产生频率控制字F的步骤。另外,该方法包括使用所述频率控制字F的至少最低有效位来驱动第一数控振荡器,以基于具有等间隔相移的多个第一周期脉冲来产生第一输出频率的第一合成信号的步骤。该方法还包括将所述第一输出频率除以M以获得频率为第一输出频率的1/M的触发信号的步骤。此外,该方法包括使用所述频率控制字F加常数C来驱动第二数控振荡器,以基于由所述触发信号引起的具有等间隔相移的多个第二周期脉冲来产生第二输出频率的第二合成信号的步骤。该方法还包括将所述第二输出频率除以N,以获得至所述反馈回路的反馈频率,所述反馈频率为第二输出频率的1/N。另外,该方法包括将所述第一合成信号作为具有第一输出频率的时钟信号输出的步骤,其中所述第一输出频率基本上与所述低频输入信号的输入频率乘以M·N·(F+C)线性相关。

可选地,该方法还包括以下步骤:在没有任何外部时钟信号的情况下,使用数字自激振荡器来从随机噪声中产生第一频率的多个第一周期脉冲。

可选地,该方法还包括以下步骤:使用约翰逊计数器来产生由所述触发信号引起的第二频率的多个第二周期脉冲,所述第二频率等于所述第一输出频率的1/M。

可选地,当所述反馈回路达到动态平衡时、所述频率控制字F在I和I+1之间切换时,所述常数C被选择为基本上大于所述频率控制字F。

附图说明

以下附图仅仅是用于说明根据各种公开的实施例的示例,并且不旨在限制本发明的范围。

图1是根据本公开的一些实施例的用于产生高比率倍频时钟信号的数字时钟电路的框图。

图2是根据本公开的实施例的自激多级级联与非门振荡器(free-running multi-stage cascaded NAND-Gate oscillator)的电路图。

图3是示出根据本公开的实施例的要被加载到数控振荡器的具有基本时间单元△的等间隔相位的K个输入脉冲的示意图。

图4是根据本公开的实施例的用于时间平均频率直接周期合成的逻辑电路的功能图。

图5是根据本公开的实施例的具有分频因子M的高频分频器的电路图。

图6是根据本公开的实施例的K

图7是根据本公开的实施例的频率检测器的逻辑电路的示意图。

图8是示出根据本公开的实施例的输入/输出频率与频率控制字之间的关系图。

具体实施方式

现在将参照以下实施例更具体地描述本公开。应当注意,本文提供的一些实施例的以下描述仅用于说明和描述的目的。其不是穷举的或限于所公开的精确形式。

由于时钟信号中的抖动大,因此基于锁相环(PLL)设计的常规时钟电路在将其倍频/分频因子设置为不超过1000时存在局限性。大多数时钟电路依靠晶体振荡器等来提供输入时钟信号,这要求很高的功耗和较大的芯片面积以产生高比率倍频时钟信号,并且难以集成在芯片中。

因此,本公开尤其提供一种用于产生高比率倍频时钟信号的数字时钟电路、具有该数字时钟电路的IC芯片及其方法,其基本上消除了由于相关技术的限制和缺点而导致的一个或多个问题。

一方面,本公开提供了一种基于自激振荡的数字时钟电路,以产生高比率倍频时钟信号。图1示出了根据本公开的一些实施例的用于产生高比率倍频时钟信号的数字时钟电路的框图。参考图1,数字时钟电路主要由两部分组成。第一子电路10包含第一数控振荡器100。第一数控振荡器100被配置为基于来自自激振荡发生器的振荡信号来产生和输出高频时钟信号,并且第一子电路10被配置为将M分频信号提供给第二子电路20。第二子电路20包括时间平均频率锁频环(FLL),该时间平均频率锁频环被配置为接收低频输入信号并使用反馈回路来确定频率控制字F,以控制第二数控振荡器200基于M分频信号获得合成时钟信号,提供N分频信号作为FLL回路中的反馈信号。频率控制字F还用于控制第一子电路10中的第一数控振荡器。

参考图1,具体地,第一子电路10包括用于产生自激振荡频率的自激振荡器50。第一子电路10还包括第一数控振荡器100,其具有用于接收控制信号的控制端口101、用于接收多个输入脉冲的多个输入端口102、用于输出第一输出信号的输出端口103,并且第一数控振荡器100被配置作为为高频直接周期合成器。

在一个实施例中,自激振荡器50使用基于级联的NAND(与非)门单元的逻辑电路来实现自激振荡频率的产生,而无需使用任何电压脉冲源或晶体振荡器。图2示出了根据本公开的实施例的自激多级级联NAND门振荡器的电路图。参考图2,例如,该电路由交叉级联的8级NAND门单元(P0,P1,...至P15)构成。每一级包括一对NAND门单元。整个振荡器电路被配置为基于所有噪声来产生振荡,并且用作滤波器以逐渐允许在最终平衡状态下所有的振荡稳定在固定的频率值。此外,(图2中所有16个单元的)每个“NAND门”单元都被配置为输出一个周期脉冲,该周期脉冲具有相同的振荡频率和等于(这些脉冲的)周期的1/16的相移。

假设对于自激振荡器50中的K/2级级联结构的任何两个最近的相邻NAND门单元,相移为△,则产生具有第一频率f

再次参照图1,在一个实施例中,第一数控振荡器100被提供为时间平均频率直接周期合成器,其被配置为使用从控制端口101接收的控制信号(其为频率控制字F

从具有均匀间隔相移△

K个输入脉冲被分别输入到两个K至1多路复用器。本文中(图4),K=K

在转换时间t6处,与下部路径相关的累加器在时钟的每个上升沿执行累加计算,以处理频率控制字F为包括整数部分I和小数部分r的实数。下部路径中的K至1多路复用器将输出CLK1的逻辑"0"的长度控制在低电压电平。在第一转换时间t1处,SEL_LOW在CLK2的上升沿被馈送到第一(或下部)K至1多路复用器MUX_A。因此,将选择K

第二K至1多路复用器(MUX_B)耦接到由半频率控制字F

另外,参照图3,由CLK1控制的2至1多路复用器MUX_C控制上部路径和下部路径的转变。现在,来自上部路径或下部路径的仅一个信号到达反转触发器电路,该反转触发器电路包括D型触发器和两个反相器,以在时钟的每个上升沿将输出MUXOUT从"1"反转到"0"或从"0"反转到"1"。

在第二转换时间t2处,选中信号通过第一K至1多路复用器MUX_A,并被馈送到2至1多路复用器MUX-C。

在与t2同时发生的第三转换时间t3,当CLK2在上升沿之后处于逻辑"1"的状态时,CLK1处于逻辑"0"的状态。因此,2至1多路复用器MUX-C从上部路径选择第二输出MUXOUT_B作为被发送到反转触发器的MUXOUT。

在第四转换时间t4处,第二输出MUXOUT_B的上升沿到达从0到1的转变已完成的反转触发器。

在第五转换时间t5处,CLK1现在转变为1。因此2至1多路复用器MUX-C选择下部路径的第一输出MUXOUT_A以发送到反转触发器。整个过程在反馈回路中重复。

因此,第一数控振荡器100采用频率控制字F

返回参考图1,第一子电路10还包括耦接到输出端口103的第一分频器120,以接收具有第一输出频率f

可选地,M分频信号用作引发附加振荡脉冲的触发信号。在一个实施例中,进一步参考图1,第一子电路10还包括由触发信号驱动的触发振荡器150,以产生具有等间隔相移的第二频率的多个第二脉冲。图6示出根据本公开的实施例的被配置为K

再次参照图1,第二子电路20包括频率检测器(FD)210,其具有接收具有输入频率f

在一个实施例中,频率检测器210被配置为将输入频率f

在一实施例中,触发器子电路2101包括四个D型触发器,其经由分频器耦接到第一输入端口且部分地经由反相器耦接到第二输入端口。触发器子电路2101被配置为确定第一频率f

另外,第二子电路20包括耦接至频率检测器210以接收第一/第二控制信号的控制器220。在该实施例中,在每个循环操作中,第一控制信号fast驱动控制器220以将频率控制字F减小1,而第二控制信号slow驱动控制器220以将频率控制字F增大1。假设没有从频率检测器210接收到控制信号,控制器220被配置为保持频率控制字F不变。最后,当第一控制信号fast和第二控制信号slow交替产生并且频率控制字F在两个整数I和I+1之间切换时,整个反馈回路达到动态平衡。在这种平衡状态下,第二频率f

此外,参照图1,第二子电路20包括耦接到控制器220的第二数控振荡器200,以接收频率控制字F

此外,第二子电路20包括第二分频器230,第二分频器230耦接到第二数控振荡器200,以接收第二输出频率f

当反馈回路通过与由控制字F

f

R是输出频率与输入频率的倍频比,由三个乘数的乘积组成:分频因子M、分频因子N、和F

在本公开的另一实施例中,参考图1,控制器220被配置为将频率控制字F提供给第一子电路10中的第一数控振荡器100和第二子电路20中的第二数控振荡器200二者。换句话说,可以从控制器220产生的频率控制字F中提取被提供给第一数控振荡器100的频率控制字F

在实施例中,使用频率控制字F加上实质上加上较大常数C来驱动第二子电路中的第二数控振荡器200的时间平均频率反馈锁定环(FLL)被设计为增强时钟信号精度。在FLL反馈回路中,第二输出频率f

图8示出了示出根据本公开的实施例的输入/输出频率与频率控制字之间的关系的图。参考图8,示出了输入频率和输出频率与频率控制字F(具有固定的分频因子M和N)之间的关系是单调关系。当频率控制字F具有较大的值时,该关系基本上是线性的。因此,相对于输入频率具有高倍频的输出信号可以用作高频时钟信号。在一个特定的实验中,将频率为50Hz的输入信号加载到电路板上用FPGA芯片实现的时钟电路中,并通过Keysight53230A频率计进行测量,得到输出频率为124.148MHz,倍频比R大至2482968。通常,取决于用于设计数字时钟电路的分频因子M、N和频率控制字F加上常数C的选择,本公开的数字时钟电路的倍频比R至少大于2000,或大于10000,或大于50000,或大于100000,或大于500000,或大于1000000,或大于2000000。

在特定实施例中,本公开提供了一种用于产生高比率倍频时钟信号的数字时钟发生器。该数字时钟发生器包括频率检测器,该频率检测器被配置为将从输入端口接收的输入频率的输入信号与来自反馈回路的反馈频率的反馈信号进行比较以产生控制信号。数字时钟发生器还包括耦接到频率检测器的控制器,以基于控制信号调整反馈回路中的频率控制字F。另外,数字时钟发生器包括耦接到控制器和第一振荡发生器的第一数控振荡器,以接收具有等间隔相移的第一频率的多个第一脉冲,并且被配置为产生第一合成信号至输出端口,所述第一合成信号具有由控制字F控制的第一输出频率。数字时钟发生器还包括第一分频器,所述第一分频器耦接到输出端口以产生具有第一输出频率的1/M的触发信号。此外,数字时钟发生器包括由触发信号引起(induced)的第二振荡发生器,以产生具有等间隔相移的第二频率的多个第二脉冲。数字时钟发生器还包括第二数控振荡器,其耦接至控制器和第二振荡发生器,并被配置为产生到反馈回路的第二合成信号,该第二合成信号具有由频率控制字F加上常数C控制的第二输出频率。此外,数字时钟发生器在反馈回路中包括第二分频器,以产生反馈频率为第二输出频率的1/N的反馈信号。反馈回路使反馈频率被锁定至输入频率,从而使第一输出频率基本上与输入频率乘以M·N·(F+C)线性相关。第一合成信号被输出为相对于输入频率具有高比率倍频时钟频率的时钟信号。

在另一方面,本公开提供了一种用于产生高比率倍频时钟信号的芯片,该芯片包括本文所述的数字时钟电路。该数字时钟电路基于高效的纯数字电路设计和自激振荡产生架构,以实现高比例倍频时钟频率。该芯片可以在FPGA或ASIC数字集成电路中实现,用于各种电子应用。

在另一方面,本公开提供一种用于从低频输入信号产生高比率倍频时钟信号的方法。该方法包括将低频输入信号与反馈回路中的反馈信号进行比较以产生控制信号的步骤。该方法还包括基于控制信号产生频率控制字的步骤。另外,该方法包括使用频率控制字F的至少最低有效位来驱动第一数控振荡器以基于具有等间隔相移的多个第一周期脉冲来产生第一输出频率的第一合成信号的步骤。该方法还包括将第一输出频率除以M以获得具有第一输出频率的1/M的触发信号的步骤。此外,该方法包括以下步骤:使用频率控制字F加常数C来驱动第二数控振荡器,以基于由触发信号引起的具有等间隔相移的多个第二周期脉冲来产生第二输出频率的第二合成信号。该方法进一步包括以下步骤:将第二输出频率除以N以获得反馈回路中的具有第二输出频率的1/N的反馈频率。此外,该方法包括以下步骤:将第一合成信号作为时钟信号输出,其中第一输出频率基本上与低频输入信号的输入频率乘以M·N·(F+C)线性相关。

进一步地,在该实施例中,该方法还包括以下步骤:在无需任何外部时钟信号的情况下,使用数字自激振荡器来从随机噪声中产生第一频率的多个第一周期脉冲。

另外,在该实施例中,该方法包括以下步骤:使用约翰逊计数器来产生由触发信号引起的第二频率的多个第二周期脉冲,该第二频率等于第一输出频率的1/M。

此外,在执行该方法的实施例中,当反馈回路达到动态平衡且频率控制字F在I和I+1之间切换时,将常数C选择为基本上大于频率控制字F。

为了说明和描述的目的,已经给出了本发明的实施例的上述描述。其不是穷举的,也不是要将本发明限制为精确的形式或所公开的示例性实施例。因此,前面的描述应当被认为是说明性的而不是限制性的。显然,许多修改和变化对于本领域技术人员来说是显而易见的。选择和描述实施例是为了解释本发明的原理及其最佳模式的实际应用,从而使本领域技术人员能够理解本发明的各种实施例和各种修改,以适于特定的使用或预期的实现。本发明的范围由所附权利要求及其等同物限定,其中所有术语的含义都是其最宽的合理含义,除非另有说明。因此,术语"发明"、"本发明"等不一定将权利要求的范围限制为特定实施例,并且对本发明的示例性实施例的引用不意味着对本发明的限制,并且不应推断出这样的限制。本发明仅由所附权利要求的精神和范围来限定。此外,这些权利要求可以指使用名词或元素之后的"第一"、"第二"等。这些术语应当被理解为术语,并且不应当被解释为对由这些术语所修改的元件的数量给出限制,除非已经给出了特定的数量。所描述的任何优点和益处可能不适用于本发明的所有实施例。应当理解,在不脱离由所附权利要求限定的本发明的范围的情况下,本领域技术人员可以对所述实施例进行改变。此外,本公开中元件和部件不旨在贡献于公众的,无论元件或部件是否在以下权利要求中明确陈述。

- 用于产生高比率倍频时钟信号的数字时钟电路

- 一种全数字时钟产生电路及全数字时钟产生方法