具电流增益布局的设备

文献发布时间:2023-06-19 11:39:06

技术领域

所揭示的实施例涉及装置,且特定来说,所揭示的实施例涉及具电流增益布局的半导体装置。

背景技术

半导体装置(例如晶体管装置)可包含经配置以切换电子信号的半导体电路。晶体管装置可包含连接到外部电路的至少三个端子(例如栅极、源极及漏极)。为操作晶体管装置,控制跨一对端子的电压,其控制通过另一对端子的电流。因此,晶体管装置可在使电流能够跨端子流动的第一状态及限制电流流动的第二状态中操作。例如,在晶体管装置中,当在栅极与源极端子之间施加低于阈值电压的电压时,可限制从源极端子到漏极端子的电流。

晶体管装置可经配置以提供通过对应端子(例如漏极及源极)的电流(例如漏极-源极电流(I

图1A是第一晶体管单元102的平面图。第一晶体管单元102可为可用于设计半导体装置的电路的基本单元(例如单个晶体管及/或电流沟道)。第一晶体管单元102可包含充当电子的扩散区域或有源区域的衬底112(例如半导电材料,例如硅、锗等)。

第一晶体管单元102可包含附接到源极124与漏极126之间的衬底112的栅极122。栅极122可为供应控制电压(例如相对于源极124的特定电压)的端子或电连接件,控制电压调节第一晶体管单元102的操作状态。根据栅极电压,漏极-源极电流可流动于漏极126与源极124之间。为将电流转移进出电路,第一晶体管单元102可(例如)在接触区域116处包含形成及/或连接到漏极126及源极124的导电结构(例如端子垫、迹线等)。

第一晶体管单元102可进一步具有影响漏极-源极电流量的大小或尺寸。例如,第一晶体管单元102可对应于正交于跨源极124与漏极122之间的栅极122的电流流动方向134的第一宽度132(D1)。第一宽度132可表示电流廊道的大小或可同时跨源极124及漏极122行进的电子的数目。因此,晶体管的宽度可为影响其漏极-源极电流容量的参数。

图1B是包含第一晶体管单元102作为基本电路的第一晶体管装置152的平面图。例如,第一晶体管装置152可包含沿电流流动方向134组合以形成具有第一宽度132的单个晶体管装置的第一晶体管单元102的多个例子。因此,第一晶体管装置152可包含提供给定宽度(例如第一宽度132)的增大漏极-源极电流的多个沟道。晶体管装置中沟道的数目可为影响其漏极-源极电流容量的另一参数。

如图1B中所说明,第一晶体管装置152可包含第一晶体管单元102的四个重叠例子。因此,第一晶体管装置152可包含四个沟道。栅极122可延伸于每一源极-漏极组合之间。每一沟道(例如具有介于其间的栅极的一对相邻源极及漏极)可自身产生源极-漏极电流。源极124的触点可连结在一起(例如经由导电结构,例如迹线或垫)以形成源极124的单个端子,且漏极126的触点可连结在一起以形成漏极126的单个端子。因此,每一沟道的源极-漏极电流可经组合以提供第一晶体管装置152的总源极-漏极电流。

为了说明,第一晶体管单元102及晶体管装置152经展示为每个漏极及源极具有6个触点。还为了说明,第一晶体管装置152经展示为具有4个沟道。然而,应理解,第一晶体管单元102及晶体管装置152可具有任何数目个触点及/或沟道。

图2A说明第二晶体管单元202。作为图1A的第一晶体管单元102的替代,第二晶体管单元202可为可用于设计半导体装置的电路的基本单元。第二晶体管单元202可包含第一子单元204及第二子单元206,两者是彼此相同的沟道(例如N沟道或P沟道)。第一子单元204及第二子单元206可在衬底的其自身区段上各自包含其自身的栅极222、源极224及漏极226的组合。例如,第一子单元204可包含经掺杂以在栅极222的对置侧上形成源极224及漏极226的第一衬底区段212。第二子单元206可包含经掺杂以在栅极222的对置侧上形成源极224及漏极226的第二衬底区段214。导电结构可经连接以控制其栅极处的电压且从源极及漏极发送/接收电流。

第一子单元204及第二子单元206两者可具有沿正交于电流流动方向234的方向的第二宽度232(D2)。为了比较,第二宽度232可为图1的第一宽度132的一半,使得第二晶体管单元202的组合宽度相同于第一晶体管单元102。为了讨论,以下描述将第一宽度132假定为2μm且将第二宽度232假定为1μm;第一晶体管单元102及第二晶体管单元202两者可具有2μm的总宽度。然而,应理解,晶体管宽度可为任何大小。

尽管跨第一晶体管单元102及第二晶体管单元202的总宽度(连同其它特性,例如触点大小/间距、衬底特性、偏压特性等)可相同,但第二晶体管单元202可基于其内的额外沟道来提供增大源极-漏极电流。换句话说,第二晶体管单元202的电流增益可大于第一晶体管单元202。

图2B说明包含第二晶体管单元202作为基本电路的第二晶体管装置252。例如,第二晶体管装置252可包含沿电流流动方向234组合以形成具有第二宽度232的单个晶体管装置的第二晶体管单元202的多个例子。因此,第二晶体管装置252可包含提供给定宽度(例如第二宽度232)的增大漏极-源极电流的多个沟道。如图2B中所说明,第二晶体管装置252包含第二晶体管单元202的4个重叠例子。因此,第二晶体管装置252可包含跨共同衬底的8个沟道。

在比较图1B的第一晶体管装置152与第二晶体管装置252时,第二晶体管装置252可具有相同于第一晶体管装置152的总宽度(例如基于具有单元宽度的一半及沟道的数目的两倍)。类似于对应晶体管单元,归因于第二晶体管装置252中的较多沟道,第二晶体管装置252可具有大于第一晶体管装置152的漏极-源极电流。换句话说,当沟道的宽度增大(例如针对第一晶体管装置152)时,阈值电压变小,漏极-源极电流减小。然而,增加装置(例如第二晶体管装置252)中的沟道的数目,电力消耗增加。沟道的数目增加引起互连件(例如连接所有源极及所有漏极的导电结构等)增加,其进一步增大寄生电容。因此,第二晶体管装置252消耗比第一晶体管装置152多的电力。

附图说明

图1A是第一晶体管单元的平面图。

图1B是包含第一晶体管单元作为基本电路的第一晶体管装置的平面图。

图2A是第二晶体管单元的平面图。

图2B是包含第二晶体管单元作为基本电路的第二晶体管装置的平面图。

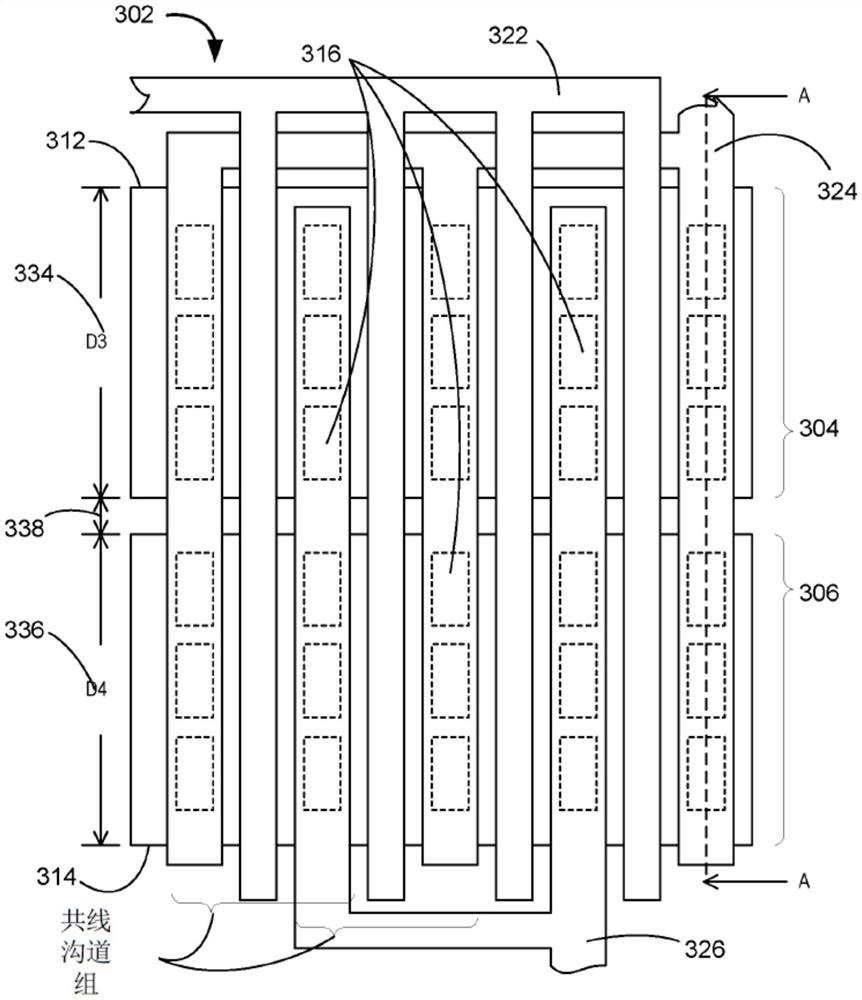

图3是根据本发明的实施例的设备的平面图。

图4是根据本发明的实施例的设备的沿图3中的线A-A的横截面图。

图5是根据本发明的实施例的设备的平面图。

图6是根据本发明的实施例的设备的平面图。

图7是根据本发明的实施例的输入缓冲器的实例性电路图。

图8是说明根据本发明的实施例的制造设备的实例性方法的流程图。

图9是根据本发明的实施例的包含存储器装置的系统的示意图。

具体实施方式

如下文将更详细描述,本文所揭示的技术涉及半导体装置、具有半导体装置的系统及用于提供半导体装置中的电流增益布局的相关方法。在下文将描述的实施例中,半导体装置(例如晶体管)可包含具有由用于其栅极、源极及漏极区域的连续及/或笔直导电结构链接的至少两个单独区段(例如衬底)的分段晶体管装置。换句话说,分段晶体管装置可包含串联连接的两个或两个以上沟道或晶体管单元。

图3是根据本发明的实施例的设备(例如分段晶体管装置302)的平面图。分段晶体管装置302可包含第一区段304及第二区段306。第一区段304及第二区段306可各自包含一或多个沟道(例如个别晶体管单元)。在一些实施例中,第一区段304及第二区段306可包含相同数目个沟道。

第一区段304可包含第一衬底(或有源区域)312且第二区段306可包含第二衬底(或有源区域)314,第一衬底312及第二衬底314彼此分离(例如半导电材料的非相连本体)。在一些实施例中,分段晶体管装置302可包含第一区段304与第二区段306之间的浅沟槽隔离(STI),其分离两个区段。第一衬底312及第二衬底314可各自包含经掺杂以形成源极及漏极的区域。分段晶体管装置302可包含连接到掺杂区域的导电结构(例如导线、迹线、垫等)。例如,栅极连接器322(例如具有多个支脚/延伸部的导电结构)可连接到每一对源极及漏极之间的栅极。另外,在各种触点316处,源极连接器324可直接接触衬底的源极区域且漏极连接器326可直接接触衬底的漏极区域。

另外,第一区段304及第二区段306可各自包含彼此平行布置(例如布置成行或列)的沟道。第一区段304可包含具有第一区段宽度334(D3)的沟道,且第二区段306可包含具有第二区段宽度336(D4)的沟道。此外,第一区段304及第二区段306可由分离距离338(例如STI)分离。

在一些实施例中,第一区段304及第二区段306可经布置使得第一区段304及第二区段306的沟道共线。例如,针对图3中所说明的实施例,第一区段304可位于第二区段306前面(例如在顶上,如图3中所说明),且第一区段304的源极、栅极、漏极可与第二区段306的源极、栅极、漏极对准。因此,栅极连接器322、源极连接器324及漏极连接器326可包含跨第一衬底312及第二衬底314两者(例如沿第一区段宽度334及第二区段宽度336)且在两个区段之间的间隔338上延伸的平行支脚。因而,每一连接器支脚可连接两个区段的沟道的对应组件(例如栅极、源极或漏极)。因此,第一衬底312上的沟道可与第二衬底314上的沟道串联电连接。

基于串联连接一组沟道,分段晶体管装置302可在不增加互连件的情况下提供增加的沟道数目。与图1B的第一晶体管装置152及图2B的第二晶体管装置252相比,第一区段宽度334及第二区段宽度336可相同于图2A的第二宽度232,其是图1A的第一宽度132的一半(即,D

图4是根据本发明的实施例的设备(例如分段晶体管装置302)的沿图3中的线A-A的横截面图。分段晶体管装置302的扩散区域(例如第一衬底312、第二衬底314等)可通过隔离机构402(例如STI)来彼此分离。在一些实施例中,一或多个额外隔离机构(例如额外STI)可形成于第一衬底312及/或第二衬底314的对置端上。隔离机构402可具有提供图3的分离距离338的尺寸(例如SIT的顶部上的宽度)。在一些实施例中,扩散区域可彼此完全分离。

图5是根据本发明的实施例的设备(例如分段晶体管装置502)的平面图。在一些实施例中,设备可具有分离扩散区域,其具有不同宽度。例如,分段晶体管装置502可包含第一区段504、第二区段506等。第一区段504可具有第一衬底512(例如扩展区域)且第二区段506(例如分离扩散区域)可具有第二衬底514。第一衬底512可对应于第一区段宽度534(D

由于共线组中沟道的总沟道宽度影响漏极-源极电流,所以第一区段宽度534及第二区段宽度536的差异不影响漏极-源极电流。作为了比较,为匹配图1A的第一晶体管单元102及/或图2A的第二晶体管单元202的2μm沟道宽度,在一些实施例中,第一区段宽度534可为0.66μm且第二区段宽度536可为1.34μm。

图6是根据本发明的实施例的设备(例如分段晶体管装置602)的平面图。设备可具有任何数目个分离扩散区域,例如两个、三个或三个以上扩散区域。例如,分段晶体管装置602可包含第一区段604、第二区段606、第三区段608等。第一区段604可具有第一衬底612,第二区段606可具有第二衬底614,第三区段608可具有第三衬底616,等。每一扩散区域可具有一宽度,使得第一衬底612可对应于第一区段宽度634(D

在一些实施例中,输入缓冲器700可用于存储器装置(例如动态随机存取存储器(DRAM))中的数据(DQ)连接处。图7是根据本发明的实施例的输入缓冲器700的实例性电路图。在一些实施例中,在其内的一或多个部分处包含分段晶体管装置302的输入缓冲器700可实施用于存储器装置(例如动态随机存取存储器(DRAM)装置)。例如,输入缓冲器700可包含于经配置以接收待写入到存储器位置中的数据(DQ)信号的一或多个数据端子(DQ)连接件中(例如在输入缓冲器内)。

输入缓冲器700可包含经配置以接收及处理对应输入信号(例如写入启用信号、DQ系统信号(例如DQSB、DQST等)、数据(DQ)信号或其组合)的一或多个晶体管(例如N沟道晶体管及/或P沟道晶体管)。在一些实施例中,DQ系统信号可包含对应于数据选通信号(DQS)的互补信号的DQSB信号、对应于DQS的真信号的DQST或其组合。因此,输入缓冲器700可基于接收及处理输入信号来产生输出信号。

在一些实施例中,输入缓冲器700可包含由写入启用信号(例如供应到M31的栅极)控制以将供应电压(VDD;例如连接到M31的源极)连接到其它晶体管的P沟道晶体管(M31)。例如,当写入启用信号处于非有效高电平时(例如当无待写入数据信号供应到输入缓冲器700时),M31可切断,借此减少泄漏电流。另一P沟道晶体管(M30;由供应到其栅极的DQSB控制)的源极可连接到M31的漏极。M30的漏极可连接到一或多个另外P沟道晶体管(M1及/或M2)的源极,P沟道晶体管(M1及/或M2)由连接到其栅极的DQ信号操作。在一或多个实施例中,M1及/或M2可为差动放大器或其一部分,使得M1的栅极连接到DQ信号的正连接且M2连接到DQ信号的负连接(例如参考节点(Vref))。M1及/或M2的漏极可通过对应预充电晶体管(例如分别为N沟道晶体管M7及M8)来连接到接地,预充电晶体管由连接到M7及/或M8的栅极的DQST信号操作。预充电晶体管(M7、M8、M30、M27、M28、M29或其组合)可根据数据选通信号(DQS)或其衍生物(例如DQST及/或DQSB信号)来操作以对相应节点预充电。

在一些实施例中,M1及/或M2的漏极可进一步连接到对应N沟道晶体管(分别为M26及M27)的栅极以进一步放大差动放大器(例如M1及M2)的输出。放大晶体管(M26及/或M27)的源极及漏极可连接到一系列晶体管,晶体管系列连接到M31的源极及M30的漏极。例如,放大晶体管M26及/或M27的源极可通过一或多个电流控制晶体管(例如N沟道晶体管M40及/或M41)来连接到接地。另外,放大晶体管M26及/或M27的漏极可连接到一或多个锁存晶体管(例如用于保持由M1、M2、M26及/或M27放大的逻辑电平的M14、M15、M16及/或M17)及/或一或多个预充电晶体管(例如M28及/或M29)。在一些实施例中,锁存晶体管及/或预充电晶体管(例如M14、M15、M28及/或M29)的源极可连接到M31的漏极及M30的源极。上游输出晶体管的漏极可产生输出信号。例如,M28及M14的漏极可产生输出信号的差动高部分(OUT+)且M29及M15的漏极可产生输出信号的差动负部分(OUT-)。一或多个上游输出晶体管(例如M14及/或M15)可根据连接到其栅极的相反差动输出来操作。例如,M14的栅极可连接到OUT-及/或M15的栅极可连接到OUT+。一些其它上游输出晶体管(例如M28及/或M29)可根据连接到其栅极的DQST信号来操作。在一些实施例中,对应于OUT+及/或OUT-的节点可进一步连接到一或多个下游晶体管(例如N沟道晶体管M16及/或M17)。例如,M16的漏极可连接到OUT+节点,且M17的漏极可连接到OUT-节点。另外,M16的源极可连接到M26的漏极,且M17的源极可连接到M27的漏极。下游晶体管的栅极可由相反差动输出操作,例如通过使M16的栅极连接到OUT-节点及使M17的栅极连接到OUT+节点。

输入缓冲器700可包含用于一或多个上述晶体管的分段晶体管装置302。例如,分段晶体管装置302可用于DQ输入缓冲器中的一或多个位置处,例如用于放大逻辑电平(例如增大增益以高速操作)。在一或多个实施例中,分段晶体管装置302可用于首先接收DQ信号,例如用于P沟道晶体管M1及/或M2,其中DQ信号连接到栅极连接器322。在一或多个实施例中,一或多组分段晶体管装置302可作为差动放大器(例如M1及/或M2)、第二级放大器(例如M26及M27)等实施于DQ输入缓冲器中。

图8是说明根据本发明的实施例的制造设备的实例性方法800的流程图。例如,方法800可用于制造图3的分段晶体管装置302、图5的分段晶体管装置502、图6的分段晶体管装置602或其一部分等。

在块802中,可提供半导体衬底(例如硅、锗等)。在块804中,可掺杂半导体衬底的各种区域以形成一或多个沟道。例如,可使用受体或p型掺杂物(例如硼、铝、镓等)、施体或n型掺杂物(例如磷、砷、锂等)或其它掺杂物来掺杂半导体衬底的不同区域。另外,可掺杂各种区域以形成掺杂衬底、阱、耗尽层及/或对应于源极、栅极、漏极等的其它掺杂区域。可形成沿共同方向延伸的各种区域(例如源极区域、栅极区域、漏极区域等),使得所得沟道彼此平行。例如,可掺杂衬底以形成交替源极及漏极列/行及一对邻接源极-漏极或漏极-源极之间的栅极区域。

在块806中,可分离半导体衬底以形成包含至少一第一衬底(例如图3的第一衬底312)及第二衬底(例如图3的第二衬底314)的目标数目个分离衬底。在一些实施例(例如块812中所表示)中,可基于形成跨沟道(例如垂直于沟道宽度)延伸的隔离机构(例如STI)且因此将沟道电及/或物理分离成分开区段来分离衬底。例如,可基于形成沟槽(例如经由遮蔽及干式或湿式蚀刻)且使用绝缘体(例如氧化物)填充沟槽来形成隔离机构。由于将现存线性沟道分成若干区段,所以经划分衬底上的沟道可彼此共线。

在一些实施例(例如块822中所表示)中,可在对应于第一沟道及第二沟道的目标沟道宽度(例如第一沟道宽度、第二沟道宽度、第三沟道宽度等)的位置处形成隔离结构。此外,可形成具有对应于图3的分离距离338的尺寸的隔离机构。分段晶体管装置的目标总沟道宽度可基于经划分衬底的目标沟道宽度(例如经划分衬底的目标沟道宽度的总和)。

在块808中,可形成跨第一衬底及第二衬底电连接匹配或对应区域的一或多个导电结构。例如,可形成(例如经由沉积导电金属)连接经划分衬底上的一组或所有栅极区域的栅极连接器(例如迹线、触点、垫等)。类似地,可形成分别连接源极区域及漏极区域的源极连接器及漏极连接器。形成每一连接器可包含形成各自对应于沟道的一或多个支脚,例如块832中所说明。可形成沿一方向(例如平行于沟道宽度的方向)跨划分区段及隔离机构延伸的每一支脚。例如,每一支脚可直接位于一组共线沟道的对应区域上且沿所述对应区域延伸。

依实例性顺序说明使用一些处理步骤的方法800。然而,所属领域的一般技术人员应了解,方法800包含与半导体处理相关联的其它相关联步骤(例如掩蔽、平坦化等)。此外,在一些实施例中,制造方法可不同。例如,可单独提供、处理(例如掺杂)各种衬底且接着将其附接到隔离机构的对置侧以使沟道共线。

图9是根据本发明的实施例的包含设备(例如上述分段晶体管装置)的系统的示意图。上文参考图3到8所描述的前述实施例中的任一者可并入到各种较大及/或更复杂系统中,系统的代表性实例是图9所示意性展示的系统980。系统980可包含存储器装置900、电源982、驱动器984、处理器986及/或其它子系统或组件988。系统980可包含具有大体上类似于上文参考图3到8所描述的分段晶体管装置的特征的特征的装置/晶体管,且可因此包含用于执行来自主机装置的直接读取请求的各种特征。所得系统980可执行各种功能的任何者,例如存储器存储、数据处理及/或其它适合功能。因此,代表性系统980可包含(但不限于)手持装置(例如移动电话、平板计算机、数字读取器及数字音频播放器)、计算机、车辆、电器及其它产品。系统980的组件可容置于单个单元中或分布于多个互连单元上(例如通过通信网路)。系统980的组件还可包含远程装置及各种计算机可读媒体的任何者。

应从上文了解,本文已为了说明而描述本发明的特定实施例,但可在不背离本发明的情况下进行各种修改。另外,还可在其它实施例中组合或消除特定实施例的上下文中所描述的新技术的特定方面。此外,尽管已在所述实施例的上下文中描述与新技术的特定实施例相关联的优点,但其它实施例还可展现此类优点且落于本发明的范围内的所有实施例未必均展现此类优点。因此,本发明及相关联技术可涵盖本文未明确展示或描述的其它实施例。

在上文所说明的实施例中,已在CMOS装置的上下文中描述分段晶体管装置。然而,根据本发明的其它实施例所配置的晶体管装置除包含CMOS装置之外,还可包含其它类型的适合晶体管类型(例如FET、MOSFET或BJT装置等),或可包含所述其它类型的适合晶体管类型来替代CMOS装置。

本文所使用的术语“处理”包含操纵信号及数据,例如写入或编程、读取、擦除、刷新、调整或改变值、计算结果、执行指令、汇编、转移及/或操纵数据结构。术语“数据结构”包含布置为位、字或码字、块、文件、输入数据、系统产生数据(例如计算或产生数据)及程序数据的信息。此外,本文所使用的术语“动态”描述过程、功能、动作或实施方案发生于对应装置、系统或实施例的操作、使用或部署期间且发生于运行制造商或第三方固件之后或运行制造商或第三方固件时。动态发生过程、功能、动作或实施方案可发生于设计、制造及初始测试、设置或配置之后。

足够详细描述以上实施例以使所属领域的技术人员能够制造及使用实施例。然而,所属领域的技术人员应理解,本发明可具有额外实施例且可在无需上文参考图3到9所描述的实施例的若干细节的情况下实践本发明。

- 具电流增益布局的设备

- 立体式布局的高增益天线设备