半导体存储装置

文献发布时间:2023-06-19 11:39:06

本申请以2019年12月27日提出申请的先行日本专利申请第2019-238327号的优先权的利益为基础,且追求其利益,其全部内容以引用的形式包含在本文中。

技术领域

本发明的实施方式涉及一种半导体存储装置。

背景技术

业界正在使用一种半导体存储装置,其具有位线、字线、及与它们连接的存储单元(晶体管及电容器)。通过选择位线及字线施加电压,能够对存储单元写入数据以及从存储单元读出数据。

发明内容

实施方式的发明所要解决的问题是,提高设置在半导体存储装置的周边电路的布局的自由度。

实施方式的半导体存储装置具备:第1积层部,具有第1周边电路;以及第2积层部,具有存储单元、与存储单元连接的字线、与存储单元及第1周边电路连接的位线、以及选自由与位线连接的第2周边电路及与字线连接的第3周边电路所组成的群中的至少一个周边电路,且设置在第1积层部的上方。至少一个周边电路具备场效晶体管,该场效晶体管具有包含氧化物半导体的通道层。

附图说明

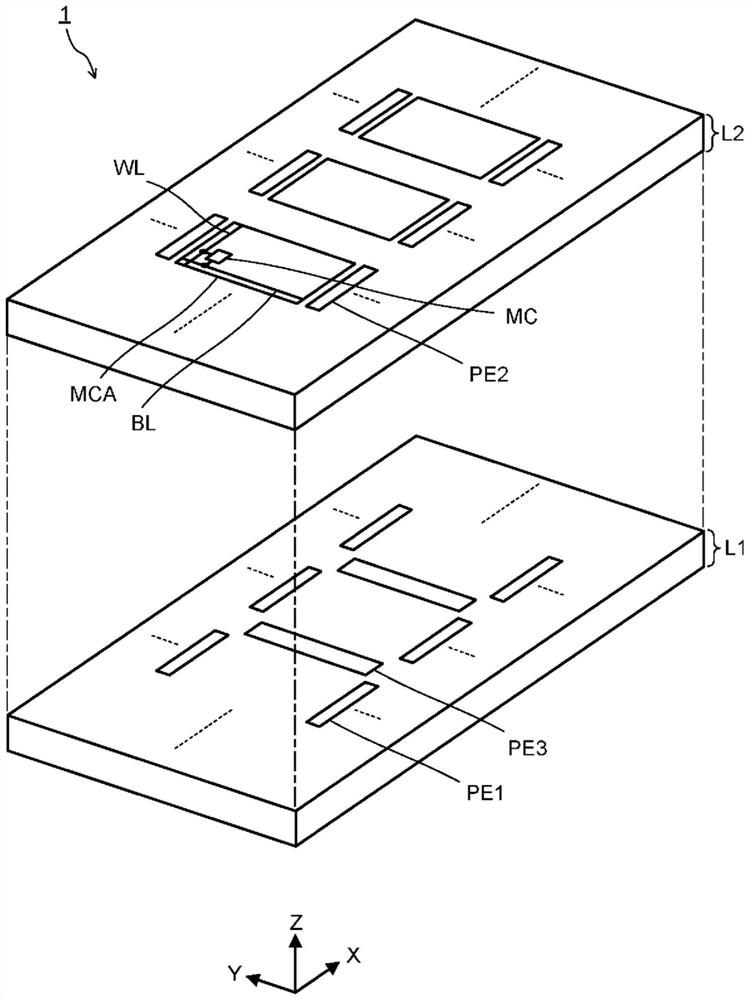

图1是用来说明半导体存储装置的构成例的示意图。

图2是用来说明半导体存储装置的电路构成例的框图。

图3是用来说明半导体存储装置的电路构成例的框图。

图4是用来说明半导体存储装置的电路构成例的框图。

图5是用来说明半导体存储装置的电路构成例的框图。

图6是用来说明半导体存储装置的电路构成例的示意图。

图7是用来说明段式字线驱动电路的动作例的示意图。

图8是用来说明段式字线驱动电路的动作例的真值表。

图9是用来说明半导体存储装置的构造例的俯视示意图。

图10是用来说明半导体存储装置的构造例的剖视示意图。

图11是用来说明半导体存储装置的构造例的剖视示意图。

图12是用来说明半导体存储装置的构造例的剖视示意图。

图13是用来说明垂直型晶体管的构造例的示意图。

图14是用来说明半导体存储装置的另一构造例的俯视示意图。

图15是用来说明半导体存储装置的另一构造例的俯视示意图。

图16是用来说明半导体存储装置的另一构造例的剖视示意图。

图17是用来说明半导体存储装置的另一构造例的剖视示意图。

图18是用来说明半导体存储装置的另一构造例的剖视示意图。

图19是用来说明半导体存储装置的另一构造例的剖视示意图。

图20是用来说明半导体存储装置的另一构成例的示意图。

图21是用来说明半导体存储装置的另一构造例的俯视示意图。

图22是用来说明半导体存储装置的另一构造例的俯视示意图。

图23是用来说明半导体存储装置的另一构造例的俯视示意图。

图24是用来说明半导体存储装置的另一构造例的俯视示意图。

图25是用来说明半导体存储装置的另一构造例的剖视示意图。

图26是用来说明半导体存储装置的另一构造例的剖视示意图。

具体实施方式

以下,参照附图对实施方式进行说明。附图中记载的各构成要素的厚度与平面尺寸的关系、各构成要素的厚度的比率等存在与实物不同的情况。另外,在实施方式中,对实质上相同的构成要素标上相同符号,并适当省略说明。

在本说明书中,“连接”不仅包含物理连接,也包含电连接。

(第1实施方式)

图1是用来说明半导体存储装置的构成例的示意图。图1所示的半导体存储装置1是动态随机存取存储器(DRAM),具备:积层部L1,具有周边电路PE1及周边电路PE3;积层部L2,具有存储单元阵列MCA及周边电路PE2,且设置在积层部L1的上方。存储单元阵列MCA、周边电路PE1、周边电路PE2、及周边电路PE3例如在X轴方向、或与X轴方向垂直的Y轴方向配置有多个。积层部L2沿与X轴方向及Y轴方向垂直的Z轴方向积层在积层部L1的上方。图1为了方便,将积层部L1与积层部L2分离图示。

存储单元阵列MCA具备多个存储单元MC。各存储单元MC与多个字线WL的一个及多个位线BL的一个连接。半导体存储装置1通过选择字线WL及位线BL施加电压,能够对存储单元MC写入数据以及从存储单元MC读出数据。

周边电路PE1例如包含感测放大器。周边电路PE1设置在存储单元阵列MCA的下方或周边电路PE2的下方。由此,能够减小半导体存储装置1的面积。此外,积层部L1可相对于一个存储单元阵列MCA具有多个感测放大器。另外,积层部L1也可具有与感测放大器不同的其它周边电路。

周边电路PE2与位线BL连接。周边电路PE2例如包含与位线BL连接的列选择电路。周边电路PE2例如设置在周边电路PE1的上方,但也可设置在存储单元MC的上方。由此,能够减小半导体存储装置1的面积。此外,积层部L2可具有多个列选择电路。另外,积层部L2也可具有与列选择电路不同的周边电路。

周边电路PE3与字线WL连接。周边电路PE3例如包含与字线WL连接的段式字线驱动电路或主字线驱动电路等字线驱动电路。周边电路PE3如图1所示例如设置在积层部L1,但并未限定在积层部L1,也可设置在积层部L2。此外,字线驱动电路可相对于一个存储单元阵列MCA设置有多个。另外,积层部L1也可具有与字线驱动电路不同的周边电路。

此处,对半导体存储装置1的电路构成例进行说明。图2至图5是用来说明半导体存储装置1的电路构成例的框图。半导体存储装置1如图2所示具有多个存储部MP。存储部MP如图3所示,具有多个存储单元阵列MCA,存储单元阵列MCA中的存储单元MC经由位线BL与周边电路PE1及周边电路PE2连接,经由字线WL与周边电路PE3连接。

图4是用来说明图3的区域2的电路构成例的框图,图5是用来说明图3的区域3的电路构成例的框图。图4图示存储单元MCA、感测放大器SA、列选择电路CSLG、及段式字线驱动电路SWD。图5图示存储单元阵列MCA、感测放大器SA、列选择电路CSLG、段式字线驱动电路SWD、及主字线驱动电路MWD。

图6是用来说明半导体存储装置1的电路构成例的电路图。图6图示多个感测放大器SA、多个存储单元MC、多个字线WL(字线WLn、字线WLn+1、字线WL'n、字线WL'n+1,n是整数)、多个位线BL(位线BLn、位线BLn+1、位线/BLn、位线/BLn+1,n是整数)、多个列选择电路CSLG、多个列选择线CSL(列选择线CSLm、列选择线CSLm+1,m是整数)、多个数据线DQ(数据线DQa、数据线DQa+1、数据线/DQa、数据线/DQa+1,a是整数)、及多个段式字线驱动电路SWD。

多个存储单元MC按矩阵方向排列,构成存储单元阵列MCA。存储单元MC具有作为场效晶体管(FET)的存储晶体管MTR、及存储电容器MCP。存储晶体管MTR的栅极与对应的字线WL连接,源极或漏极中的一个与对应的位线BL连接。存储电容器MCP的一电极与存储晶体管MTR的源极或漏极中的另一个连接,另一电极未图示,其与其它配线连接。存储单元MC能够通过存储晶体管MTR的切换,而将电荷储存在存储电容器MCP中,从而保存数据。

感测放大器SA设置在周边电路PE1。感测放大器SA与对应的位线BL连接。感测放大器SA具有包含P通道型场效晶体管(Pch-FET)及N通道型场效晶体管(Nch-FET)的电路。

列选择电路CSLG设置在周边电路PE2。列选择电路CSLG选择存储单元阵列MCA的列。列选择电路CSLG具有作为场效晶体管的列选择晶体管CSTR。列选择晶体管CSTR的栅极与对应的列选择线CSL连接,源极或漏极中的一个与对应的数据线DQ连接,源极或漏极中的另一个与对应的位线BL连接。列选择线CSL或数据线DQ通过未图示的另一电路,电位受到控制。图6图示2个列选择晶体管CSTR的栅极与1个列选择线CSL连接的例子。列选择电路CSLG能够通过列选择晶体管CSTR的切换而选择位线BL。

段式字线驱动电路SWD相对于一个存储单元阵列MCA设置有多个。段式字线驱动电路SWD与多个字线WL连接,选择存储单元阵列MCA的行。图6图示多个段式字线驱动电路SWD的一个与字线WLn连接、多个段式字线驱动电路SWD的另一个与字线WLn+1连接、多个段式字线驱动电路SWD的另一个与字线WL'n连接、多个段式字线驱动电路SWD的另一个与字线WL'n+1连接的例子。

主字线驱动电路MWD相对于每2个以上的段式字线驱动电路SWD设置有一个。主字线驱动电路MWD例如与多个段式字线驱动电路SWD的一个及多个段式字线驱动电路SWD的另一个连接。多个段式字线驱动电路SWD经由主字线驱动电路MWD与其它电路连接。半导体存储装置1通过主字线驱动电路MWD选择段式字线驱动电路SWD,通过所选择的段式字线驱动电路SWD选择字线WL,由此,选择存储单元阵列MCA的行。

图7是用来说明段式字线驱动电路SWD的动作例的示意图。图7图示构成段式字线驱动电路SWD的场效晶体管TR1、TR2、TR3、TR4。场效晶体管TR1至场效晶体管TR4例如为N通道型场效晶体管。此外,段式字线驱动电路SWD的构成并未限定在图7所示的构成。

对于场效晶体管TR1的栅极,从主字线驱动电路MWD输入控制信号MWLp,对于源极或漏极中的一个供给电源电位VPP,源极或漏极中的另一个与场效晶体管TR3的源极或漏极中的一个连接。对于场效晶体管TR2的栅极,从主字线驱动电路MWD输入控制信号MWLn,对于源极或漏极中的一个供给电源电位VSS或电源电位VNN,源极或漏极中的另一个与场效晶体管TR3的源极或漏极中的另一个连接。对于场效晶体管TR3的栅极输入控制信号WDRVp。对于场效晶体管TR4的栅极输入控制信号WDRVn,对于源极或漏极中的一个供给电源电位VSS或电源电位VNN,源极或漏极中的另一个与场效晶体管TR3的源极或漏极中的另一个连接。字线WL与场效晶体管TR2、场效晶体管TR3及场效晶体管TR4的连接部位(节点)连接。电源电位VPP高于电源电位VSS,电源电位VNN低于电源电位VSS。

图8是用来说明段式字线驱动电路SWD的动作例的真值表。当控制信号MWLp及控制信号WDRVp为高电平H、控制信号MWLn及控制信号WDRVn为低电平L时,场效晶体管TR1、TR3为接通状态,场效晶体管TR2、TR4为断开状态,字线WL因被供给电源电位VPP而为高电平H,成为选择状态。当控制信号MWLp或控制信号WDRVp为低电平L、控制信号MWLn或控制信号WDRVn为高电平H时,场效晶体管TR1或场效晶体管TR3为断开状态,场效晶体管TR2或场效晶体管TR4为接通状态,字线WL因被供给电源电位VSS或电源电位VNN而为低电平L,成为非选择状态。当控制信号MWLp或控制信号MWLn中的一个为低电平L时,控制信号MWLp或控制信号MWLn中的另一个为高电平H。另外,在控制信号WDRVp或控制信号WDRVn中的一个为低电平L时,控制信号WDRVp或控制信号WDRVn中的另一个为高电平H。通过所述动作,能够选择各字线WL。

图9是用来说明半导体存储装置1的构造例的俯视示意图,表示半导体存储装置1的X-Y平面的一部分。图10至图12是用来说明半导体存储装置1的构造例的剖视示意图,表示半导体存储装置1的Y-Z截面的一部分。图10是沿图9的线段A1-B1的Y-Z截面的示意图,图11是沿图9的线段A2-B2的Y-Z截面的示意图,图12是沿图9的线段A3-B3的Y-Z截面的示意图。

图9至图12图示周边电路PE1包含感测放大器SA并且周边电路PE2包含列选择电路CSLG的例子,为了方便,一部分构成要素的图示省略。

图9至图12所示的半导体存储装置1具备电路11、配线21、配线22、电容器30、氧化物导电层41、氧化物导电层42、氧化物导电层43、场效晶体管51、场效晶体管52、配线61、配线62、配线71、配线81、配线82、配线83、配线91、及配线92。各构成要素之间根据需要设置有绝缘体。各构成要素例如利用光刻技术而形成。

电路11设置在积层部L1,构成感测放大器SA。电路11例如可利用单晶硅衬底等半导体衬底而形成,Pch-FET及Nch-FET在半导体衬底上具有通道区域、源极区域及漏极区域。

配线21设置在积层部L2,经由通孔与电路11的Pch-FET的源极区域或漏极区域中的一个连接,并且经由通孔与Nch-FET的源极区域或漏极区域中的一个连接。

配线22设置在积层部L2,作为例如向存储电容器MCP的另一电极供给电位的配线发挥功能。配线22例如可通过加工一个导电层,而在与配线21同一个步骤中形成。

电容器30设置在积层部L2,构成图6所示的存储电容器MCP。电容器30是所谓柱型电容器、圆筒型电容器等三维电容器,具有板状电极31、绝缘膜32、及单元电极33。板状电极31作为存储电容器MCP的电极发挥功能,与配线22连接。图9及图10图示多个电容器30共用1个板状电极31的例子。绝缘膜32作为存储电容器MCP的介电层发挥功能,设置在板状电极31与单元电极33之间。单元电极33作为存储电容器MCP的一电极发挥功能。通过所述三维电容器,能够减小存储单元的面积。

氧化物导电层41如图10所示,在积层部L2中与单元电极33接触而设置。氧化物导电层41例如包含铟锡氧化物(ITO)等金属氧化物。

氧化物导电层42设置在积层部L2,包含与氧化物导电层41的氧化物相同的氧化物半导体。氧化物导电层42例如可通过加工一个氧化物层,而在与氧化物导电层41同一个步骤中形成。

氧化物导电层43设置在积层部L2,如图10所示,经由通孔与积层部L1的电路11的源极区域或漏极区域连接。氧化物导电层43包含与氧化物导电层41的氧化物相同的氧化物。氧化物导电层43例如可通过加工一个氧化物层,而在与氧化物导电层41及氧化物导电层42同一个步骤中形成。

场效晶体管51如图10所示,在积层部L2中设置在电容器30上,构成图6所示的存储晶体管MTR。场效晶体管51具有包含金属氧化物等氧化物半导体的通道层。场效晶体管51的通道层与氧化物导电层41接触。此时,氧化物导电层41设置在第2电极33与场效晶体管51的通道层之间,作为场效晶体管51的源极电极或漏极电极中的另一个发挥功能。场效晶体管51的通道层由于与氧化物导电层41同样包含金属氧化物,所以能够减小场效晶体管51与氧化物导电层41的连接电阻。

场效晶体管52如图10所示,在积层部L2中设置在电路11的上方,构成图6所示的列选择晶体管CSTR。场效晶体管52具有包含金属氧化物等氧化物半导体的通道层。场效晶体管52的通道层与氧化物导电层42接触。此时,氧化物导电层42作为场效晶体管52的源极电极或漏极电极中的一个发挥功能。场效晶体管52的通道层由于与氧化物导电层42同样包含金属氧化物,所以能够减小场效晶体管52与氧化物导电层42的连接电阻。

场效晶体管51及场效晶体管52各自为垂直型晶体管。图13是用来说明垂直型晶体管的构造例的示意图。图13所示的垂直型晶体管50具有包含氧化物半导体的通道层501、围绕通道层501的栅极绝缘膜502、及隔着栅极绝缘膜502与通道层501相对的栅极电极503。另外,通道层501的Z轴方向的一端作为源极或漏极中的一个发挥功能,另一端作为源极或漏极中的另一个发挥功能。图13所示的垂直型晶体管50是栅极电极503围绕通道层501配置的、所谓环栅晶体管(SGT,Surrounding Gate Transistor)。通过垂直型晶体管,能够减小半导体存储装置1的面积。

通道层501例如包含铟(In)。通道层501例如包含氧化铟及氧化镓、氧化铟及氧化锌或、氧化铟及氧化锡。作为一例,为铟、镓、及锌的氧化物(铟镓锌氧化物)、所谓的IGZO(InGaZnO)。

栅极绝缘膜502例如包含氧化物或氮氧化物(作为一例,为氧化硅)。

栅极电极503在X轴方向或Y轴方向延伸。图13图示在X轴方向延伸的栅极电极503。栅极电极503例如包含金属、金属化合物、或半导体。栅极电极503例如包含选自由钨(W)、钛(Ti)、氮化钛(TiN)、钼(Mo)、钴(Co)、及钌(Ru)所组成的群中的至少一种材料。

具有包含氧化物半导体的通道层的场效晶体管与设置在半导体衬底的场效晶体管相比,截止漏电流较低。由此,能够较长地保存例如保存在存储单元MC的数据,因此,能够减少更新动作的次数。另外,具有包含氧化物半导体的通道层的场效晶体管可通过低温工艺形成,因此,能够抑制对电容器30或周边电路PE1产生热应力。

配线61如图10所示,在积层部L2中在X轴方向延伸,构成字线WL。配线61也作为场效晶体管51的栅极电极(图13所示的垂直型晶体管50的栅极电极503)发挥功能。图9至图12图示多个配线61。

配线62在积层部L2中在X轴方向延伸,构成列选择线CSL。配线62也作为场效晶体管52的栅极电极(图13所示的垂直型晶体管50的栅极电极503)发挥功能。配线62例如可通过加工一个导电层,而在与配线61同一个步骤中形成。

配线71在积层部L2中设置在配线61的上方,与配线61交叉,在Y轴方向延伸,构成位线BL。配线71在积层部L2中延伸至配线21的上方,经由通孔与配线21连接。

配线71在场效晶体管51的上方与场效晶体管51的通道层(图13所示的垂直型晶体管50的通道层501)接触而设置,作为场效晶体管51的源极电极或漏极电极中的一个发挥功能。配线71在场效晶体管52的上方与场效晶体管52的通道层(图13所示的垂直型晶体管50的通道层501)接触而设置,作为场效晶体管52的源极电极或漏极电极中的一个发挥功能。图9图示多个配线71。

配线81在积层部L2中设置在配线71的上方,在X轴方向延伸。配线81构成连接段式字线驱动电路SWD与主字线驱动电路MWD的全域字线选择配线。图9为了方便,用虚线图示配线81。

配线82在积层部L2中在X轴方向延伸,构成图6所示的数据线DQ。配线82如图9及图10所示,经由通孔与氧化物导电层42连接。配线82例如可通过加工一个导电层,而在与配线81同一个步骤中形成。

配线82经由氧化物导电层42与场效晶体管52的源极或漏极中的另一个连接。由此,与在半导体衬底上设置场效晶体管52的情况相比,能够缩短场效晶体管52与数据线DQ的连接路径,因此,能够减小连接电阻。

配线83在积层部L2中在X轴方向延伸,经由通孔与氧化物导电层43连接。配线83例如可通过加工一个导电层,在与配线81及配线82同一个步骤中形成。

配线91在积层部L2中在Y轴方向延伸,构成列选择线CSL。配线91设置在配线81的上方及配线82的上方。配线91如图9及图11所示,经由通孔与配线62连接。

配线92在积层部L2中在Y轴方向延伸。配线92设置在配线83的上方。配线92如图9及图12所示,经由通孔与配线83连接。配线92未图示,其与供给电源电位VSS的电源线等连接。

如以上所述,本实施方式的半导体存储装置通过在具有包含感测放大器SA的周边电路PE1的积层部L1的上方设置具有包含列选择电路CSLG的周边电路PE2的积层部L2,减少设置在积层部L1的周边电路,能够提高周边电路的布局的自由度。

在以往的半导体存储装置中,列选择电路CSLG设置在与感测放大器SA同一个积层部L1。在该情况下,为了确保形成列选择电路CSLG的区域,需要增大半导体存储装置的面积。另外,列选择电路CSLG与数据线DQ的连接路径较长,需要高纵横比的通孔,而使连接电阻增加。与此相对,在本实施方式的半导体存储装置中,例如通过在感测放大器SA的上方设置列选择电路CSLG,能够减小半导体存储装置的面积,并且能够缩短列选择电路CSLG与数据线DQ的连接路径,从而减小连接电阻。

(第2实施方式)

图14及图15是用来说明半导体存储装置1的另一构造例的俯视示意图,表示半导体存储装置1的X-Y平面的一部分。图15用虚线图示图14的一部分构成要素。图16至图19是用来说明半导体存储装置1的另一构造例的剖视示意图,表示半导体存储装置1的Y-Z截面的一部分。图16是沿图14及图15的线段A1-B1的Y-Z截面的示意图,图17是沿图14及图15的线段A2-B2的Y-Z截面的示意图,图18是沿图14及图15的线段A3-B3的Y-Z截面的示意图,图19是沿图14及图15的线段A4-B4的Y-Z截面的示意图。

图14至图19图示周边电路PE1包含感测放大器SA并且列选择电路CSLG设置在存储单元MC的上方的例子,为了方便,一部分构成要素的图示省略。

图14至图19所示的半导体存储装置1具备电路11、配线21、配线22、电容器30、氧化物导电层41、场效晶体管51、场效晶体管53、配线61、配线71、配线81、配线82、配线83、配线84、配线91、配线92、配线93、及配线101。各构成要素之间根据需要设置有绝缘体。此外,电路11、配线21、配线22、电容器30、氧化物导电层41、场效晶体管51、配线61、及配线81分别与第1实施方式的电路11、配线21、配线22、电容器30、氧化物导电层41、场效晶体管51、配线61、及配线81相同,因此省略说明。

配线71在积层部L2中设置在配线61的上方,与配线61交叉,在Y轴方向延伸,构成位线BL。配线71在积层部L2中延伸至配线21的上方,经由通孔与配线21连接。

配线71在场效晶体管51的上方与场效晶体管51的通道层(图13所示的垂直型晶体管50的通道层501)接触而设置,作为场效晶体管51的源极电极或漏极电极中的一个发挥功能。图14图示多个配线71。

场效晶体管53如图16所示,在积层部L2中设置在配线71的上方,构成图6所示的列选择晶体管CSTR。场效晶体管53具有包含氧化物半导体的通道层(图13所示的垂直型晶体管50的通道层501)。场效晶体管53的通道层与配线71接触。场效晶体管53的其它说明可适当引用第1实施方式的场效晶体管52的说明。

配线101如图16所示,在积层部L2中设置在配线71的上方。配线101也作为场效晶体管53的栅极电极(图13所示的垂直型晶体管50的栅极电极503)发挥功能。图13及图15图示2个列选择晶体管CSTR11.88 Tf0共用一个配线101的例子。

配线82在积层部L2中在X轴方向延伸,构成图6所示的数据线DQ。配线82如图16所示,在场效晶体管53的上方与场效晶体管53的通道层(图13所示的垂直型晶体管50的通道层501)接触而设置,作为场效晶体管53的源极电极或漏极电极中的一个发挥功能。图14及图15图示多个配线82,图15用虚线图示配线82。配线82例如可通过加工一个导电层,在与配线81同一个步骤中形成。

配线83在积层部L2中在X轴方向延伸,如图16所示,经由通孔与电路11连接。配线83例如可通过加工一个导电层,在与配线81同一个步骤中形成。

配线84在积层部L2中在X轴方向延伸,如图16所示,经由通孔与电路11连接。配线84例如可通过加工一个导电层,在与配线81同一个步骤中形成。

配线91在积层部L2中在Y轴方向延伸,构成列选择线CSL。配线91设置在配线101的上方。图15用虚线图示配线91。配线91如图14、图15、及图17所示,经由通孔与配线101连接。

配线92在积层部L2中在Y轴方向延伸。配线92设置在配线81的上方至配线84的上方。图15用虚线图示配线92。配线92如图14、图15、及图18所示,经由通孔与配线84连接。配线92构成供给电源电位VDD的电源线。电源电位VDD高于电源电位VSS。

配线93在积层部L2中在Y轴方向延伸。配线93设置在配线8 120.281的上方至配线84的上方。图15用虚线图示配线93。配线93如图14、图15、及图19所示,经由通孔与配线83连接。配线93构成供给电源电位VSS的电源线。

如以上所述,本实施方式的半导体存储装置通过在具有包含感测放大器SA的周边电路PE1的积层部L1的上方设置具有列选择电路CSLG的积层部L2,减少设置在积层部L1的周边电路,能够提高周边电路的布局的自由度。

在以往的半导体存储装置中,列选择电路CSLG设置在与感测放大器SA同一个积层部L1。在该情况下,为了确保形成列选择电路CSLG的区域,需要增大半导体存储装置的面积。另外,列选择电路CSL与数据线DQ的连接路径较长,需要高纵横比的通孔,而使连接电阻增加。与此相对,在本实施方式的半导体存储装置中,例如通过在存储单元MC的上方设置列选择电路CSLG,能够进一步减小半导体存储装置的面积,并且能够缩短列选择电路CSL与数据线DQ的连接路径,从而减小连接电阻。

(第3实施方式)

图20是用来说明半导体存储装置的另一构成例的示意图。图20所示的半导体存储装置1与图1所示的半导体存储装置1相比,至少周边电路PE3设置在积层部L2这点不同。关于与图1所示的半导体存储装置1相同的部分,可适当引用第1实施方式的说明。

图21至图24是用来说明半导体存储装置1的另一构造例的俯视示意图,表示半导体存储装置1的X-Y平面的一部分。图22用虚线图示图21的一部分构成要素,图23用虚线图示图22的一部分构成要素,图24用虚线图示图23的一部分构成要素。图25及图26是用来说明半导体存储装置1的另一构造例的剖视示意图,表示半导体存储装置1的Y-Z截面的一部分。图25是沿图21至图24的线段A1-B1的Y-Z截面的示意图,图26是沿图21至图24的线段A2-B2的Y-Z截面的示意图。

图21至图26图示周边电路PE1包含感测放大器SA并且周边电路PE3包含段式字线驱动电路SWD的例子,为了方便,一部分构成要素的图示省略。

图21至图26所示的半导体存储装置1具备电路11、配线21、配线23、电容器30、氧化物导电层41、场效晶体管51、场效晶体管54、场效晶体管55、场效晶体管56、配线61、配线71、配线72、配线73、配线81、配线82、配线83、配线85、配线86、配线94、配线95、配线96、配线111、及配线112。各构成要素之间根据需要设置有绝缘体。此外,电路11、配线21、电容器30、氧化物导电层41、场效晶体管51、配线61、及配线81分别与第1实施方式的电路11、电容器30、氧化物导电层41、场效晶体管51、配线61、及配线81相同,因此省略说明。

配线23在积层部L2中在Y轴方向延伸。配线23例如具有作为信号线或电源线的功能。配线23例如可通过加工一个导电层,在与第1实施方式的配线21、22同一个步骤中形成。

场效晶体管54如图25所示,在积层部L2中设置在配线61的上方,在段式字线驱动电路SWD中,构成图7所示的场效晶体管TR1及TR3。场效晶体管54具有包含氧化物半导体的通道层。场效晶体管54的通道层与配线61接触。此时,配线61也作为场效晶体管54的源极电极或漏极电极发挥功能。

场效晶体管55如图25所示,在积层部L2中设置在配线61的上方,在段式字线驱动电路SWD中,构成图7所示的场效晶体管TR4。场效晶体管55具有包含氧化物半导体的通道层。场效晶体管55的通道层与配线61接触。此时,配线61也作为场效晶体管55的源极电极或漏极电极发挥功能。

场效晶体管56如图25所示,在积层部L2中设置在配线61的上方,在段式字线驱动电路SWD中,构成图7所示的场效晶体管TR2。场效晶体管56具有包含氧化物半导体的通道层。场效晶体管56的通道层与配线61接触。此时,配线61也作为场效晶体管56的源极电极或漏极电极发挥功能。

场效晶体管54至场效晶体管56各自为垂直型晶体管。垂直型晶体管例如为图13所示的垂直型晶体管50。垂直型晶体管的其它说明可适当引用第1实施方式的垂直型晶体管的说明。

配线72在积层部L2中设置在配线61的上方,与配线61交叉,在Y轴方向延伸。对于配线72,供给图7所示的控制信号WDRVp。配线72也作为场效晶体管54的栅极电极(图13所示的垂直型晶体管50的栅极电极503)发挥功能。图21至图24图示多个配线72。

配线73在积层部L2中设置在配线61的上方,与配线61交叉,在Y轴方向延伸。对于配线73,供给图7所示的控制信号WDRVn。配线73也作为场效晶体管55的栅极电极(图13所示的垂直型晶体管50的栅极电极503)发挥功能。图21至图24图示多个配线73。

配线85在积层部L2中设置在配线71的上方。对于配线85,供给图7所示的控制信号MWLp。配线85也作为场效晶体管54的栅极电极(图13所示的垂直型晶体管50的栅极电极503)发挥功能。

配线86在积层部L2中设置在配线61的上方。配线86例如与第1实施方式或第2实施方式的配线81连接。对于配线86,供给图7所示的控制信号MWLn。配线86也作为场效晶体管56的栅极电极(图13所示的垂直型晶体管50的栅极电极503)发挥功能。

配线94在积层部L2中在Y轴方向延伸。配线94设置在配线85的上方。配线94在场效晶体管54的上方与场效晶体管54的通道层(图13所示的垂直型晶体管50的通道层501)接触而设置,作为场效晶体管54的源极电极或漏极电极发挥功能。对于配线94,供给图7所示的电源电位VPP。

配线95在积层部L2中在Y轴方向延伸。配线95设置在配线73的上方。配线95在场效晶体管55的上方与场效晶体管55的通道层(图13所示的垂直型晶体管50的通道层501)接触而设置,作为场效晶体管55的源极电极或漏极电极发挥功能。对于配线95,供给图7所示的电源电位VSS或电源电位VNN。

配线96在积层部L2中在Y轴方向延伸。配线96设置在配线86的上方。配线96在场效晶体管56的上方与场效晶体管56的通道层(图13所示的垂直型晶体管50的通道层501)接触而设置,作为场效晶体管56的源极电极或漏极电极发挥功能。对于配线96,供给图7所示的电源电位VSS或电源电位VNN。

配线111在积层部L2中在X轴方向延伸,如图26所示,经由通孔与配线23连接。图21至图24图示多个配线111。配线111例如具有作为信号线或电源线的功能。

配线112在积层部L2中在X轴方向延伸,如图24所示,经由通孔与配线23连接。图21至图24图示多个配线112。配线112例如具有作为信号线或电源线的功能。

如以上所述,本实施方式的半导体存储装置通过在具有包含感测放大器SA的周边电路PE1的积层部L1的上方设置具有包含段式字线驱动电路SWD的周边电路PE3的积层部L2,减少设置在积层部L1的周边电路,能够提高周边电路的布局的自由度。

在以往的半导体存储装置中,段式字线驱动电路SWD设置在与感测放大器SA同一个积层部L1。在该情况下,为了确保形成段式字线驱动电路SWD的区域,需要增大半导体存储装置的面积。另外,段式字线驱动电路SWD与信号线的连接路径较长,需要高纵横比的通孔,而使连接电阻增加。与此相对,在本实施方式的半导体存储装置中,可在存储单元MC的下方设置周边电路PE1,例如通过在存储单元MC的下方设置感测放大器SA,能够减小半导体存储装置的面积,并且能够缩短段式字线驱动电路SWD与信号线的连接路径,从而减小连接电阻。

本实施方式可与其它实施方式适当组合。例如可与第1实施方式或第2实施方式同样地,在积层部L2进一步设置列选择电路CSLG。

以上说明了本发明的一些实施方式,但这些实施方式是作为例子而提出,并未意图限定发明的范围。这些新颖的实施方式可通过其它各种形态实施,在不脱离发明主旨的范围内,可进行各种省略、替换、变更。这些实施方式或其变化包含在发明的范围或主旨内,并且包含在权利要求书记载的发明及其均等的范围内。

- 半导体存储装置管理系统、半导体存储装置、主机装置、程序、半导体存储装置的管理方法

- 半导体存储装置及包括半导体存储装置的半导体系统