集成电路装置

文献发布时间:2023-06-19 11:44:10

技术领域

本公开涉及一种集成电路装置

背景技术

半导体集成电路(integrated circuit;IC)工业呈指数成长。在IC材料及IC设计的技术进步产生多个IC世代,每一个IC世代比上一个IC世代有更小及更复杂的电路。在IC发展过程中,工艺可作出的几何尺寸(例如:最小部件(或线路))会下降,而功能密度(例如:每一芯片区域的相连元件数量)通常都会增加。此微缩过程通过增加生产效率及降低相关成本提供了优势。此微缩亦增加了IC工艺及制造的复杂性,为实现这些进步,需要在IC工艺及制造有相似的发展。

举例来说,已经引入了多栅极装置,以通过增加栅极-通道耦合、减小关闭状态(OFF-state)电流以及减小短通道效应(short-channel effect;SCE)来改善栅极控制。一种这样的多栅极装置是环绕式栅极(gate-all-around;GAA)晶体管,其栅极结构延伸围绕通道层并提供对所有侧面的通道区的控制(access)。GAA晶体管与常规的互补金属氧化物半导体(complementary metal-oxide-semiconductor;CMOS)工艺相容,允许在保持栅极控制和减轻SCE的同时积极缩小尺寸。然而,常规的GAA装置可能具有过大的电阻和功函数变化,这可能不利地降低装置效能。另外,常规的GAA装置可能具有栅极形成余量问题(gateformation margin issue),其可能给可靠的工艺带来挑战。因此,尽管常规的GAA装置通常已经足以满足其预期目的,但它们并非在各个方面都令人满意。

发明内容

本公开提供一种集成电路装置。集成电路装置包括半导体基板、多个第一半导体层、第一栅极介电层、第一栅极电极、多个第二半导体层、第二栅极介电层、第二栅极电极。第一半导体层在具有半导体材料的半导体基板上方。第一栅极介电层圆周地围绕第一半导体层的第一层。第一栅极电极包括功函数金属层和第一填充金属层,功函数金属层具有圆周地围绕第一栅极介电层第一导电材料,并且第一填充金属层具有围绕功函数金属层的第二导电材料。第二多个半导体层在具有半导体材料的半导体基板上方。第二栅极介电层圆周地围绕第二多个半导体层的第二层。第二栅极电极包括第二填充金属层,第二填充金属层具有围绕并直接接触第二栅极介电层的第二导电材料,第二填充金属层的顶表面在第二多个半导体层的最顶层上方延伸。第一导电材料的功函数低于半导体材料的中间能隙,并且第二导电材料的功函数高于半导体材料的中间能隙。

本公开提供一种集成电路装置。集成电路装置包括半导体基板、第一源极特征和第一漏极特征、第二源极特征和第二漏极特征、多个第一半导体层、多个第二半导体层、第一栅极介电层、第二栅极介电层、第一栅极电极、第一栅极接点特征、第二栅极电极、第二栅极接点特征。半导体基板具有第一主动区和第二主动区。第一源极特征和第一漏极特征设置在第一主动区上。第二源极特征和第二漏极特征设置在第二主动区上。第一半导体层夹设于第一源极特征和第一漏极特征。第二多个半导体层夹设于第二源极特征和第二漏极特征。第一栅极介电层圆周地围绕第一半导体层的每一者。第二栅极介电层圆周地围绕第二多个半导体层的每一者。第一栅极电极包括圆周地围绕并直接接触第一栅极介电层的第一导电层。第一栅极接点特征在第一栅极电极上方并直接接触第一栅极电极。第二栅极电极包括功函数金属层和第二导电层,功函数金属层圆周地围绕第二栅极介电层的每一者,并且第二导电层圆周地围绕并直接接触功函数金属层。第二栅极接点特征在第二栅极电极上方并直接接触第二栅极电极。第一半导体层包括由第一导电层施加的压缩应力。

本公开提供一种集成电路装置的形成方法。集成电路装置的形成方法包括在半导体基板的第一区域中形成多个第一悬置半导体层,并且在半导体基板的第二区域中形成多个第二悬置半导体层,其中第一多个悬置半导体层和第二多个悬置半导体层中的每一者彼此间隔;形成栅极介电层以圆周地围绕第一多个悬置半导体层和第二多个悬置半导体层;在栅极介电层的一部分上方形成功函数金属层,以圆周地围绕第二多个悬置半导体层;以及通过在冷却时足够在第一多个悬置半导体层中产生压缩应力的高温下的沉积工艺,在第一区域中形成在栅极介电层上并直接接触栅极介电层的填充金属层,并且在第二区域中形成在功函数金属层上并直接接触功函数金属层的填充金属层,以及其中填充金属层包括选自钌、铱、锇和铑的第一金属材料。

附图说明

本公开实施例可通过阅读以下的详细说明以及范例并配合相应的附图以更详细地了解。需要注意的是,依照业界的标准操作,各种特征部件并未依照比例绘制,并且仅用于说明的目的。事实上,为了清楚论述,各种特征部件的尺寸可以任意地增加或减少。

图1、图2、图3、图4、图5、图6A、图7A和图8A是根据本公开实施例的在各个工艺站点的半导体装置的三维(three-dimensional;3D)示意图。

图6B、图7B、图8B和图10是根据本公开实施例的在各个工艺站点的半导体装置的X切割剖面图。

图6C是根据本公开实施例的在各个工艺站点的半导体装置的Y切割剖面图。

图6D是根据本公开实施例的在各个工艺站点的半导体装置的Z切割剖面俯视图或平面图。

图9A是显示用于栅极电极填充金属层的多种材料选择的电阻率和特征厚度之间的关系的示意图。

图9B是显示沉积后退火对栅极电极填充金属层的薄膜应力的影响的示意图。

图11是根据本公开实施例的半导体装置上方的互连结构的剖面图。

图12A和图12B是根据本公开实施例的制造半导体结构的方法的流程图。

附图标记说明:

100:环绕式栅极装置

105:基板

110:半导体层

120:半导体层

130:鳍片结构

131:鳍片结构

150:隔离结构

160:冗余栅极结构

170:栅极介电层

180:冗余栅极电极层

190:掩模层

200:栅极间隔物

205:源极/漏极间隔物

210:外延源极/漏极特征

220:接点蚀刻停止层

230:层间介电层

250:凹陷

300:通道释放工艺

310:空隙或间隙

100A:环绕式栅极装置

100B:环绕式栅极装置

105A:装置区

105B:装置区

250a:凹陷

250b:凹陷

350:沉积处理

352:沉积处理

370:介电层

380:介电层

390:第三层/功函数金属层

400a:填充金属层

400b:填充金属层

510a:金属栅极结构

510b:金属栅极结构

900:柱状图

910:柱状图

920:柱状图

232:层间介电层

234:层间介电层

240:阻挡层

410:接点特征

510:金属栅极

604:通孔特征

606:通孔特征

608:导轨

800:方法

810~900:操作

具体实施方式

本公开提供许多不同的实施例或范例以实施本公开的不同特征。以下的公开内容叙述各个构件及其排列方式的特定实施例,以简化说明。当然,这些特定的范例并非用以限定。举例来说,若是本公开叙述了一第一特征形成于一第二特征之上或上方,即表示其可能包含上述第一特征与上述第二特征是直接接触的实施例,亦可能包含了有附加特征形成于上述第一特征与上述第二特征之间,而使上述第一特征与第二特征可能未直接接触的实施例。另外,以下本公开不同实施例可能重复使用相同的参考符号及/或标记。这些重复为了简化与清晰的目的,并非用以限定所讨论的不同实施例及/或结构之间有特定的关系。

此外,其与空间相关用词。例如“在…下方”、“下方”、“较低的”、“上方”、“较高的”及类似的用词,为了便于描述图示中一个元件或特征与另一个(些)元件或特征之间的关系。除了在附图中示出的方位外,这些空间相关用词意欲包含使用中或操作中的装置的不同方位。除此之外,设备可能被转向不同方位(旋转90度或其他方位),则在此使用的空间相关词也可依此相同解释。

此外,当数字或数字范围以“约”、“近似”等描述时,该术语旨在包括在合理范围内的数字(包括所描述的数字),例如在所述数量的+/-10%内或本技术领域中技术人员理解的其他值。举例来说,术语“约5nm”包括4.5nm至5.5nm的尺寸范围。

本公开通常涉及IC和半导体装置及其形成方法。随着技术朝着更小的技术节点(例如:20nm、16nm、10nm、7nm、5nm及以下)发展,IC和半导体装置效能的优化越来越受到形成不同必要特征的空间的竞争需求的限制。最近,GAA装置已被结合到IC和半导体装置中以解决此问题。GAA装置包括其栅极结构(或其一部分)形成在通道区的所有侧面上(例如:围绕通道区的一部分)的任何装置。GAA装置在半导体芯片的一个小区域上堆叠了多个通道,从而缓解了微缩的挑战。GAA装置也可以称为多桥通道装置。

然而,GAA装置具有其各自的挑战。举例来说,GAA装置通常具有有限的通道对通道间距(channel-to-channel spacing)。因此,在纳米范围(nanometer regime)内,在间隔内形成的特征(例如栅极结构的部分)也具有有限的尺寸。当导电特征具有纳米范围的尺寸时,与它们在整体尺寸(bulk dimension)下的电阻相比,它们的电阻通常会急剧增加。换句话说,对常规装置优化材料选择可能不是GAA装置的理想选择。另外,为了满足设计需要,材料选择进一步受到各种其他参数(例如功函数及/或通道层上方的应力)的限制。此外,随着装置结构变得越来越复杂,期望合并特征以执行多种功能,及/或整合工艺步骤以简化制造。在形成可靠的器件时,优化和平衡所有这些因素已是一个重要挑战。因此,本公开提出了新的装置结构和材料选择,其改善了上面所讨论的各种考虑因素。举例来说,本公开提供了在相关尺寸上具有低电阻、期望的应力效应以及合适的功函数的栅极填充金属材料。另外,所提供的栅极填充金属材料能够使简化的装置结构及/或整合工艺的制造成本降低。此外,此处所述的方法和材料允许无卤素工艺,从而提高由此制备的装置的可靠性。本公开包括多个实施例。不同的实施例可以具有不同的优点,并且任何实施例都不需要特定的优点。

如上面所述,GAA装置包括形成在通道区的所有侧面上的栅极结构。GAA装置的通道区可以包括纳米线通道、纳米片通道、纳米棒通道(nanobar channel)及/或其他合适通道配置。在实施例中,GAA装置的通道区可以具有垂直间隔的多个水平纳米线、纳米片、纳米棒及/或其他适当形状通道,使GAA装置成为堆叠的水平GAA(stacked horizontal GAA;S-HGAA)装置。此外,由于这样的通道通常具有纳米范围的尺寸,因此在下文中将它们统称为“纳米通道”。GAA装置可以包括P型金属氧化物半导体GAA装置或N型金属氧化物半导体GAA装置。此外,GAA装置可以具有与单一、连续的栅极结构或多个栅极结构相关的一或多个通道区。本技术领域中技术人员可以受益于本公开而可以认识到半导体装置的其他示例。举例来说,其他类型的金属氧化物半导体场效晶体管(metal-oxide semiconductor fieldeffect transistor;MOSFET)(例如平面MOSFET、鳍式场效晶体管(Fin Field-EffectTransistor;FinFET)、其他多栅极FET、互补式金属氧化物半导体晶体管(complementarymetal-oxide semiconductor transistor;CMOS))可获得与此处所述的GAA装置相似的技术优势。

图1至图8A是根据本公开实施例的在各个工艺站点的半导体装置的三维(3D)示意图。图6B至图8B和图10是根据本公开实施例的在各个工艺站点的半导体装置的X切割剖面图。图6C是根据本公开实施例的在各个工艺站点的半导体装置的Y切割剖面图。图6D是根据本公开实施例的在各个工艺站点的半导体装置的Z切割剖面俯视图或平面图。图9A是显示用于栅极电极填充金属层的多种材料选择的电阻率和特征厚度之间的关系的示意图。图9B是显示沉积后退火对栅极电极填充金属层的薄膜应力的影响的示意图。图11是根据本公开实施例的半导体装置上方的互连结构的剖面图。图12A和图12B是根据本公开实施例的制造半导体结构的方法的流程图。

在所示的实施例中,半导体装置包括GAA装置(例如:HGAA装置)。可以在IC(或其一部分)的工艺期间制造GAA装置,包括静态随机存取存储器(static random accessmemory;SRAM)及/或逻辑电路、被动部件(例如电阻、电容和电感)以及主动部件(例如P型场效晶体管(PFET)、N型FET(NFET)、多栅极FET(例如FinFET)、MOSFET、CMOS、双极型晶体管、高压晶体管、高频晶体管、其他存储器单元和其组合)。

参照图1,GAA装置100包括基板105。基板105包含半导体材料。在一些实施例中,基板105可以在不同区域中包括不同的掺杂物。多个半导体层110和120以交错或交替的方式垂直地(沿着图1所示的“Z”方向)堆叠在基板105上。举例来说,半导体层110设置在基板105上方,半导体层120设置在半导体层110上方,并且另一半导体层110设置在半导体层120上方,依此类推。半导体层120和110的材料组成被配置为使得它们在后续的蚀刻工艺中具有蚀刻选择性,如下面更详细的讨论。举例来说,在一些实施例中,半导体层110包含硅锗(SiGe),而半导体层120包含硅(Si)。在一些其他实施例中,半导体层120包含硅锗(SiGe),而半导体层110包含硅(Si)。

现在参照图2,对GAA装置100执行一或多个蚀刻工艺,以将半导体层110和120的堆叠图案化成为多个鳍片结构,例如成为鳍片结构130和131。鳍片结构130和131可以用作后续形成的装置的主动区。鳍片结构(或鳍片)可以通过任何合适方法来图案化。举例来说,可以使用一或多种光刻工艺来图案化鳍片,包括双重图案化或多重图案化工艺。通常来说,双重图案化或多重图案化工艺将光刻和自我对准工艺组合,从而允许产生间距小于使用单一、直接光刻工艺可获得之间距的图案。举例来说,在一个实施例中,在基板上方形成牺牲层,并且使用光刻工艺将牺牲层图案化。使用自我对准工艺在图案化的牺牲层旁边形成间隔物。接着移除牺牲层,并且接着可以使用剩余之间隔物或心轴(mandrel)来图案化鳍片。

因此,每一个鳍片结构130至131包括半导体层110和120的堆叠,其中半导体层110和120以彼此交替的方式设置。如图2所示,鳍片结构130和131各自在Y方向上水平地延伸并且在X方向上水平地彼此分开。应理解X方向和Y方向是彼此垂直的水平方向,并且Z方向是与由X方向和Y方向定义的水平平面正交的垂直方向。执行以形成鳍片结构130至131的蚀刻工艺也可以蚀刻掉基板105的一部分。后续形成隔离结构150以代替移除的基板105。在一些实施例中,隔离结构150包括浅沟槽隔离(shallow trench isolation;STI)。隔离结构150可以包含电性绝缘材料,例如氧化硅。

冗余栅极结构160形成在每一个鳍片结构130至131的一部分上方。冗余栅极结构160围绕每一个鳍片结构的顶表面和侧表面。冗余栅极结构160包括覆盖鳍片结构130至131的栅极介电层170和在栅极介电层170上方的冗余栅极电极层180。冗余栅极结构160还可包括一或多个掩模层190,其用于图案化栅极介电层170和冗余栅极电极层180。在一些实施例中,栅极介电层170包括氧化硅,并且冗余栅极电极层180包括多晶硅。

现在参照图3,栅极间隔物200可以形成在冗余栅极结构160的侧壁上。栅极间隔物200包含介电材料,例如氮化硅、氧化硅、碳化硅、碳氧化硅、氮碳氧化硅、低k介电材料或其组合。可以通过任何合适方法来形成栅极间隔物200,其可以包括沉积、蚀刻及/或化学氧化。

另外,在冗余栅极结构160外部的源极/漏极区中的鳍片结构130至131的部分被凹陷。通过外延成长工艺在凹陷区中形成外延源极/漏极特征210。在一些实施例中,外延源极/漏极特征可以合并在一起,如图3所示。外延源极/漏极特征210可以掺杂有合适的掺杂物。举例来说,用于N型装置的外延源极/漏极特征可以掺杂有N型掺杂物,例如磷(P)、砷(As)、其他N型掺杂物或其组合;而P型装置的外延源极/漏极特征可以掺杂有P型掺杂物,例如硼(B)、碳(C)、其他P型掺杂物或其组合。另外,外延源极/漏极特征210可以包括用于应力效应的合适半导体材料。在一些实施例中,源极/漏极间隔物205也形成在隔离结构150上方。源极/漏极间隔物205可以包括低k介电材料。

现在参照图4,在外延源极/漏极特征210上方形成层间介电(interlayerdielectric;ILD)层230。ILD层230可以包括介电材料,例如氧化硅、碳氧化硅、高k材料、低k材料或极低k材料。在其他功能中,ILD层230在GAA装置100的各种部件之间提供电性隔离。在许多实施例中,ILD层230具有在约50nm和约500nm之间的厚度。ILD层230的形成包括沉积步骤和化学机械研磨(chemical mechanical polishing;CMP)步骤。在一些实施例中,可以在外延源极/漏极特征210和ILD层230之间形成接点(contact)蚀刻停止层220。

参照图5,移除冗余栅极结构160。图5显示了在移除冗余栅极结构160之后的GAA装置100的三维(3D)示意图。如图所示,移除冗余栅极结构160会在GAA装置100中形成凹陷250。凹陷250部分地暴露鳍片结构130和131的顶表面和侧表面。

现在参照图6A至图6D,对GAA装置100执行通道释放工艺300。通道释放工艺300可以包括一或多个蚀刻工艺(例如湿式蚀刻工艺及/或干式蚀刻工艺)以移除半导体层110,但不移除半导体层120。如上面所述,由于半导体层110和120之间的材料组成不同,使得这成为可能。换句话说,当执行通道释放工艺300时,在半导体层110和120之间具有蚀刻选择性。举例来说,可以以比半导体层120更快的速率(例如:十倍或更多)蚀刻掉半导体层110。

移除半导体层110形成由GAA装置100中的空隙或间隙310围绕的悬置的半导体层120的堆叠。因此,每一个半导体层120圆周地(circumferentially)暴露。尽管以非常慢的速率被蚀刻,但是通道释放工艺300也可以重新塑形半导体层120。举例来说,通道释放工艺300可以使每一个半导体层120具有更圆的或弯曲的轮廓(见图6A和图6C)。应理解这些半导体层120可以用作GAA装置100的通道区。

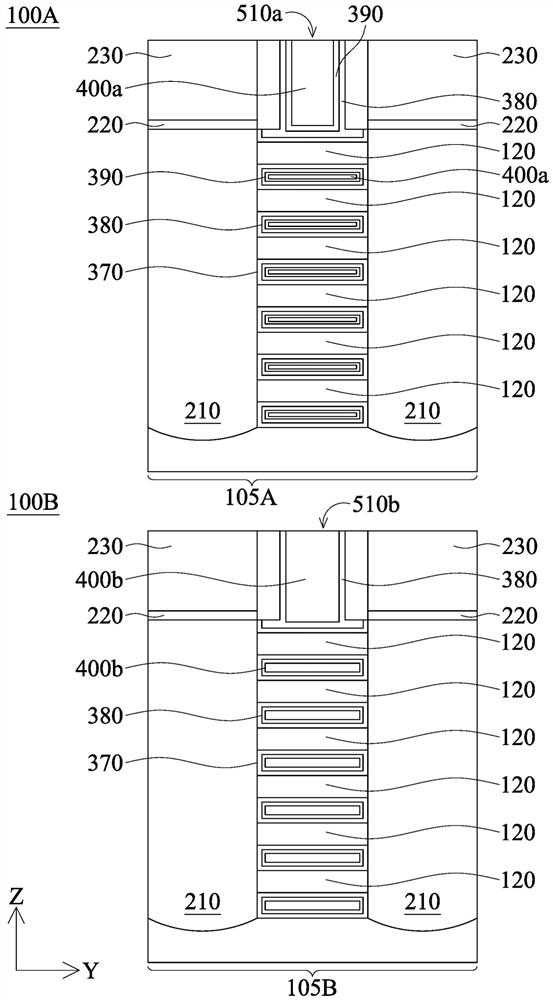

现在参照图7A至图7B,在不同装置区中的GAA装置可以接受相同或不同的后续工艺。举例来说,装置区105A中的GAA装置100(表示为100A)可以接受沉积处理350;而装置区105B中的GAA装置100(表示为100B)可以接受沉积处理352。沉积处理350和352各自包括多个沉积步骤并形成多个层,其至少部分地填充通过移除半导体层110而留下的空隙或间隙310。沉积处理350和沉积处理352可以是不同的处理工艺。可以通过在不做沉积处理(或沉积处理的沉积步骤)的区域上形成掩模层来实现不同的工艺,并在工艺完成之后移除掩模层。然而,在一些实施例中,沉积处理350的一些沉积步骤可以与沉积处理352的一些沉积步骤相同。另外,沉积处理350的一些沉积步骤可以与沉积处理352的一些沉积步骤同时执行。在一个实施例中,GAA装置100A是P型装置,并且GAA装置100B是N型装置。在另一个实施例中,GAA装置100A是N型装置,并且GAA装置100B是P型装置。沉积处理350及/或352可以是任何合适工艺,例如化学气相沉积(chemical vapor deposition;CVD)、物理气相沉积(physical vapor deposition;PVD)、等离子体辅助CVD(plasma-enhanced CVD;PECVD)、金属有机CVD(metal-organic CVD;MOCVD)、原子层沉积(atomic layer deposition;ALD)或其组合。

通过沉积处理350和352形成的多层可各自包括介电层,其在半导体层120上方共同形成栅极介电质。举例来说,如图7B所示,介电层370可以形成围绕每一个半导体层120的外表面,使得它以360度围绕每一个半导体层120。同样如图7B所示,介电层370形成为与外延源极/漏极特征210的侧壁直接接触。介电层370可以包括合适介电材料,并且可以用作界面层(IL),与用于常规晶体管的通道区和栅极结构之间的界面层相似。在一些实施例中,用于GAA装置100A的介电层370和用于GAA装置100B的介电层370是同时(或在相同沉积工艺中)形成的。换句话说,形成用于GAA装置100A和GAA装置100B的介电层370的沉积步骤是相同的,即使沉积处理350和352的其他方面彼此不同。

此外,沉积处理350和352各自进一步形成用于GAA装置100A和100B两者的介电层370上的介电层380,使得其以360度围绕介电层370。因此,两个介电层,介电层370和介电层380,在装置区两者中围绕半导体层120。同样如图7A的3D示意图和图7B的X切割剖面图所示,介电层380的一部分设置在栅极间隔物200的侧壁上。在一些实施例中,介电层380包含高k介电材料。应理解介电层380可以起到与常规晶体管中的高k栅极介电层相似的作用。在一些实施例中,用于GAA装置100A的介电层380和用于GAA装置100B的介电层380是同时或(在相同沉积工艺中)形成的。换句话说,形成用于GAA装置100A和GAA装置100B的介电层380的沉积步骤是相同的,即使沉积处理350和352的其他方面彼此不同。

在所示的实施例中,沉积处理350和352彼此的不同的处在于沉积处理350包括在装置区105A中形成用于GAA装置100A的第三层390,而沉积处理352不包括在装置区105B中的用于GAA装置100B的此沉积步骤。举例来说,在装置105A中,第三层390可以形成在介电层380上,使得第三层390以360度围绕介电层380。因此,对于GAA装置100A,现在三个层围绕半导体层120,即介电层370、介电层380和第三层390。相反地,对于GAA装置100B,没有形成第三层390。因此,仍然只有两个层围绕半导体层120,即介电层370和介电层380。

第三层390可以是功函数金属层。因此,第三层390可以可互换地称为功函数金属层390。在一个实施例中,GAA装置100A是N型装置,并且GAA装置100B是P型装置。换句话说,功函数金属层390形成在N型装置中而不形成在P型装置中。因此,功函数金属层390可以是N型功函数金属层。在一些实施例中,功函数金属层390包括钛(Ti)、铝(Al)、钽(Ta)、钛铝(TiAl)、氮化钛铝(TiAlN)、碳化钽(TaC)、氮碳化钽(TaCN)、氮化钽硅(TaSiN)或其组合。在一些实施例中,N型功函数金属层390的功函数小于半导体基板的中间能隙(或能隙的中点),例如小于约4.1eV至约4.3eV。

在另一个实施例中,GAA装置100A是P型装置,并且GAA装置100B是N型装置。换句话说,功函数金属层390形成在P型装置中而不形成在N型装置中。因此,功函数金属层390可以是P型功函数金属层。功函数金属层390包括氮化钛(TiN)、钌(Ru)、铱(Ir)、锇(Os)、铑(Rh)或其组合。在一些实施例中,P型功函数金属层390的功函数大于半导体基板的中间能隙(或能隙的中点),例如大于约4.1eV至约4.3eV。功函数金属层390可以被配置以调节栅极电极的功函数,从而通过掺入掺杂物来调节N型或P型区域中的晶体管的临界电压。功函数金属层390可以包括多个层,并且可以通过ALD、CVD及/或其他合适工艺来沉积。

现在参照图8A至图8B,在用于GAA装置100A和100B两者的半导体层120的顶层上方形成填充金属层400。GAA装置100A的填充金属层400表示为填充金属层400a;以及GAA装置100B的填充金属层400表示为填充金属层400b。填充金属层400a和400b可各自用作个别金属栅极电极的主要导电部分。填充金属层400a形成在GAA装置100A的功函数金属层390上方,并且填充金属层400b形成在GAA装置100B的介电层380上方。值得注意的是,在图8A至图8B中的填充金属层400a和400b显示为大部分透明的结构,以便更清楚地显示在其上方形成填充金属层400的各种部件。

如图8A至图8B所示,填充金属层400a从功函数金属层390的外表面垂直连续地延伸到栅极沟槽(例如凹陷250a)的顶部,并且从功函数金属层390的垂直表面(或侧壁)水平连续地延伸到功函数金属层390的相对的垂直表面。填充金属层400a和功函数金属层390共同形成金属栅极电极,作为金属栅极结构510a的一部分。相似地,填充金属层400b从介电层380的外表面垂直连续地延伸到栅极沟槽(例如凹陷250b)的顶部,并且从介电层380的垂直表面(或侧壁)水平连续地延伸到介电层380的相对的垂直表面。单独的填充金属层400b可以形成金属栅极电极,作为金属栅极结构510b的一部分。

填充金属层400a和400b可以包括任何合适填充金属材料,例如铝(Al)、铜(Cu)、钴(Co)、钨(W)、钌(Ru)、铱(Ir)、锇(Os)、铑(Rh)、钼(Mo)、镍(Ni)或其组合。可以使用任何合适方法来形成填充金属层400a和400b。这包括ALD、CVD、PVD、电镀及/或其他合适工艺。在一些实施例中,填充金属层400a及/或400b可以被掺杂以调节金属电极的功函数,从而调整GAA装置100A及/或100B的临界电压。举例来说,填充金属层400a及/或400b可以包括掺杂的钌(Ru)薄膜。钌(Ru)金属的功函数为约4.6eV至约4.8eV,并且包括氧掺杂物的钌(Ru)金属的功函数为约5.0eV至约5.2eV。因此,通过包括氧掺杂的钌(Ru)薄膜,可以实现用于填充金属层400a及/或400b的更高的功函数。在一些实施例中,可以引入铝(Al)及/或钇(Y)作为替代或额外掺杂物,以实现期望的功函数。

如上面所述,填充金属层400a和400b可以包括不同的材料。这可能基于不同GAA装置的不同设计需求。在一些实施例中,填充金属材料选自钌(Ru)、铱(Ir)、锇(Os)、铑(Rh)、钼(Mo)、镍(Ni)或其组合。这些填充金属材料具有以下一个或多个优点:(1)低电阻、(2)合适的应力效应、(3)简化的装置结构。这些优点将在下面更详细地描述。

在一些实施例中,钌(Ru)、铱(Ir)、锇(Os)、铑(Rh)、钼(Mo)及/或镍(Ni)的使用提供了具有较低电阻的填充金属层。如上面所述,常规GAA装置工艺面临的一个挑战是填充金属层中的导电材料的相对较高的电阻。高电阻会导致跨越导电特征的长度的电压下降很大(有时是无法忍受的),并导致可靠性、效能或甚至功能下降。高电阻可以是填充金属层的高电阻率的结果。虽然通常将电阻率参数考虑为特定材料在整体尺寸上的常数,但该近似值会在较小尺寸的极限崩溃(break down)。当特征尺寸接近特征材料的电子平均自由路径(mean free path;MFP)的数量级时,可以达到较小的尺寸限制。

就这一点来说,MFP是一种材料特性,定义为通过在连续碰撞(impact)(冲突(collision))之间移动电子的在整体材料(bulk material)中移动的平均距离,其调整了其方向或能量或其他粒子特性。当半导体特征的尺寸与MFP相似或在MFP之下时,散射会发生在材料界面和晶粒边界。举例来说,散射可能发生在与纳米通道相接的GAA装置的填充金属层的侧壁上,导致栅极电极的电阻率不期望的增加。尽管当特征尺寸大大超过MFP时,这种增加可以忽略,但是当特征尺寸接近MFP时,这种增加变得很大甚至是确定的。这就是所谓的标准电阻率尺寸效应(classical resistivity size effect)。此外,特征尺寸越小,散射效果对整体电阻率越重要。

不同的材料具有不同的MFP。根据数据,铜(Cu)的MFP为39.9nm,钴(Co)的MFP为7.77nm,钨(W)的MFP为15.5nm。因此,在具有小特征(例如尺寸为3nm或更小的特征)的GAA装置的情况下,标准电阻率尺寸效应在评估材料的实际电阻率很重要。某些填充金属材料的实际电阻率已基于电阻率模型评估(见图9A)。举例来说,厚度为约20nm的铜(Cu)、钴(Co)和钨(W)个别具有约7.5μΩ-cm、12μΩ-cm和10μΩ-cm的电阻率。相同材料在3nm厚的电阻率个别为约42μΩ-cm、51μΩ-cm和36μΩ-cm。相较之下,钌(Ru)在20nm厚的电阻率为约10μΩ-cm,并且在3nm厚的电阻率为约28μΩ-cm。因此,像钌(Ru)这样的金属提供了更好的电阻率分布,并且在这些小尺寸的情况下可能是填充金属层材料的更好的选择。随着尺寸进一步减小到3nm以下,钌(Ru)的优势在常规金属之上。

已经发现当特征尺寸为MFP的数量级或小于MFP时,具有较小r参数的金属提供较小的电阻率。r参数考虑了整体电阻率(ρ)和MFP(λ)两者,并且根据以下公式定义为两个因素的计算乘积:

r=ρ*λ

因此,即使此处公开的一些材料与常规材料相比不具有最低的整体电阻率ρ(例如:钌(Ru)、铑(Rh)的整体电阻率ρ个别为约7.8μΩ-cm和4.7μΩ-cm,而铜(Cu)的整体电阻率ρ为约1.7μΩ-cm),但它们的有利MFPλ主导了总体效果,并导致在相应小尺寸范围下的较低实际电阻率。已发现铱(Ir)、铑(Rh)、镍(Ni)、钌(Ru)和锇(Os)的参数r个别为约3.69μΩ-cm-nm、3.23μΩ-cm-nm、4.07μΩ-cm-nm、3.81μΩ-cm-nm和4.33μΩ-cm-nm。相较之下,铜(Cu)、钨(W)和钴(Co)的r参多个别为约6.7μΩ-cm-nm、8.2μΩ-cm-nm和4.82μΩ-cm-nm。通常来说,r参数越小,就电阻效能来说,材料越理想。通过理论和实验,已经发现需要低于约4.5μΩ-cm-nm的r参数来实现本实施例的益处。

在一些实施例中,此处公开的一些材料(例如钌(Ru))的使用提供了合适的应力效应,并且相对于增加P型装置中的空穴载子迁移率(hole carrier mobility)特别有利。可以理解金属栅极,特别是填充金属层在通道区上方施加应力,并且可能影响装置的载子迁移率,这与外延源极/漏极特征所产生的应力效应非常相似。通常来说,拉伸应力增加电子载子迁移率,因此对N型装置有利;而压缩应力增加了空穴载子迁移率,因此对P型装置有利。这种现象源自材料内能阶的变化。

钌(Ru)具有比半导体层120大的热膨胀系数(coefficient for thermalexpansion;CTE)。因此,钌(Ru)的填充金属层400a及/或400b在通道区上方施加压缩应力。压缩应力导致半导体层120内的半导体晶格失去对称性,其导致可用于空穴载子的能阶的分裂(splitting)。举例来说,之前由空穴载子的随机散射可进入的一些能阶被推高了能量,因此不再可由简单的随机散射进入。结果,抑制了随机散射。同时,空穴载子的定向运动(directional movement)中使用的一些能阶被推低能量,因此促进了定向运动。这两种效应导致钌(Ru)的填充金属层400a及/或400b内的总空穴传导增加。相反地,相同的应力对电子传导具有相反的影响,并且导致钌(Ru)的填充金属层400a及/或400b内的总电子传导减少。因此,期望增加P型GAA装置中的应力的大小,并且减小N型GAA装置中的应力的大小。

可以通过调整处理参数来调节由钌(Ru)的填充金属层400a及/或400b所施加的应力的大小,例如沉积温度、退火环境及/或沉积后退火的温度。通常来说,由于材料的高迁移率,半导体装置在沉积及/或退火温度下经受最小的应力。随着装置的冷却,不同的材料层由于其不同的CTE而收缩到不同的程度,并且在此过程中会产生应力。由于钌(Ru)具有比半导体层120更大的CTE,因此它比半导体层120收缩更多,从而在通道区上方施加压缩应力。同时,钌(Ru)的填充金属层400a及/或400b经受拉伸应力。如此产生的应力量是沉积与环境之间的温度下降幅度的函数,因此可以通过调整沉积及/或沉积后退火温度来调节。举例来说,假设钌(Ru)的填充金属层400b在升高的温度T

σ=Y·(T

其中,α

在一些实施例中,钌(Ru)、铱(Ir)、锇(Os)、铑(Rh)、钼(Mo)及/或镍(Ni)的使用为P型装置提供了简化的装置结构和最大化的形成余量(formation margin)。如上面所述,GAA装置100B不包括功函数金属层。而是,填充金属层400b直接与介电层380相接并接触。然而,填充金属层400b的底部可以执行功函数金属层的一些功能。举例来说,GAA装置100B是P型装置,并且填充金属层400b包括钌(Ru)。(Ru)具有约4.7eV的功函数,因此是适合执行P型功函数金属层的功能的材料。因此,P型GAA装置100B不需要另外的P型功函数金属层。而是,钌(Ru)的填充金属层400b同时提供P型功函数和填充金属层的双重功能。因此,通过将功函数金属层和填充金属层整合为一个连续层,简化了装置结构,并且降低了生产成本。

此外,这些材料的使用还消除了对额外辅助层(例如阻挡层、阻隔层、衬垫层、覆盖层及/或粘合层)的需要,并且进一步释放了用于较大填充窗口的空间。在常规方案中,需要各种额外层以防止不同材料之间的交叉扩散,或保护材料受氟及/或氧的侵入。然而,它们的存在占用了GAA装置内的宝贵空间,并且呈现出重大的制造挑战。举例来说,用于填充金属层400a及/或400b的填充金属材料可以比没有这种额外层的装置经受更大的流动阻力。例如在那米通道之间形成凹入特征(re-entrant feature)可能更具挑战性,因为由于开口尺寸的减小,填充金属在移动中受到更多的限制。结果,形成的填充金属层400b可能包括大量的缺陷(例如气隙)。然而,通过实验发现,当使用某些材料(例如Ru,Ir和Rh)作为填充金属材料时,即使没有这种额外层,交叉扩散或氟/氧侵入的问题也被最小化。这可能是由于它们与常规填充金属相比具有良好的扩散特性。因此,可以形成钌(Ru)填充金属层以直接接触N型或P型功函数金属层,而不需考虑层之间的交叉扩散。无需额外的层,允许更大的填充空间,并且可以改善电阻特性和装置可制造性。当然,如上面所述,除了由于消除功函数金属层的改善之外,还具有这种可制造性的改善。此外,与常规材料相比,此处公开的材料(例如钌(Ru)及/或铝(Al))也具有更好的回流特性。如此一来,可以进一步改善窄空间和凹入特征的填充。

替代地,在一些实施例中,填充金属层400a及/或400b可包括铝(Al)。铝(Al)还提供良好的回流特性和相对较低的电阻,并且允许调整N型装置中通道层上方的拉伸应力。举例来说,GAA装置100B是N型装置,并且填充金属层400b包括铝(Al)。可以通过任何合适工艺来形成填充金属层400b,例如上面对钌(Ru)所述的那些工艺。在填充金属层400b上进行注入工艺,使得填充金属层400b在通道层上方施加拉伸应力。与在钌(Ru)的情况下的压缩应力相似,由铝(Al)施加的拉伸应力增加了铝(Al)的填充金属层400b内的整体电子传导。注入的掺杂物可以选自铝(Al)、硅(Si)、锗(Ge)以及任何其他合适元素。可以通过调整注入物的剂量(dose)来调节由铝(Al)的填充金属层400b施加的应力的大小。

另外,铝的使用也相似地为N型装置提供了简化的装置结构和最大化的形成余量。在一个实施例中,GAA装置100B是N型装置,并且填充金属层400b包括铝(Al)。铝(Al)具有约4.2eV的功函数,因此是适合执行N型功函数金属层的功能的材料。因此,N型GAA装置100B不需要另外的N型功函数金属层。而是,铝(Al)的填充金属层400b同时提供N型功函数和填充金属层的双重功能。可以通过将掺杂物结合到填充金属层400b(例如:填充金属层400b的底部)中来实现金属电极的功函数的调节。

用于填充金属层400a和400b的材料选择取决于设计需要,并且需要平衡上面所述的各种特性,例如形成余量、电阻、功函数、应力效应、可制造性等。填充金属层400a和400b可以在彼此之间包括相同或不同的材料。通常来说,如果形成余量是GAA装置的主要考量,则装置可以采用GAA装置100B的结构,其中填充金属层400b包括具有合适功函数的填充金属材料,并且直接形成在介电层380上。相反地,如果具有合适功函数的填充金属材料不具有合适应力效应或合适电阻,则装置可以采用GAA装置100A的结构,并使用另外的材料来达到优化特性。举例来说,可能期望最大化P型装置的形成余量,并且还最大化N型和P型装置的填充金属层中的电导(conductance)。在这种情况下,填充金属层400a和400b两者可以使用相同的低电阻材料,例如钌(Ru)。填充金属层400a和400b可以是同时形成(例如:在单一工艺步骤中)或在不同时间(例如:在个别工艺步骤中)形成。如上面所述,钌(Ru)的填充金属层400a形成在P型的功函数金属层390上方,而钌(Ru)的填充金属层400b形成在介电层380上方。对于另一示例,可能期望最大化N型装置的形成余量,并且最大化P型装置的填充金属层中的电导。在这种情况下,GAA装置100B可以配置为具有铝(Al)填充金属层而没有另外的N型功函数金属层的N型装置,而GAA装置100A可以配置为具有钌(Ru)填充金属层和适当P型功函数金属层的P型装置。对于又一个示例,可能期望最大化N型装置的形成余量,而P型装置的电导可能非为关键。在这种情况下,GAA装置100B可以被配置为具有铝(Al)填充金属层而没有另外的N型功函数金属层的N型装置;以及GAA装置100A可以被配置为具有铝(Al)填充金属层和适当P型功函数金属层(例如:氮化钛(TiN)、钌(Ru)等)的P型装置。可以在单一步骤中同时形成用于两个装置的Al填充金属层,以降低制造成本。因此,填充金属层400a和400b可以包括相同或不同的材料,并且可以在相同或不同的工艺站点形成。在一些实施例中,金属栅极结构510b不含常规的填充金属材料,例如铜(Cu)、钴(Co)以及钨(W)。

尽管上面的描述主要集中在具有不同装置结构的GAA装置100A和GAA装置100B,并且沉积处理350和352是不同的工艺,但本公开还考虑两个具有相同结构的GAA装置(尽管具有不同的材料)。举例来说,如图10所示,GAA装置两者接受相同的沉积处理352。GAA装置100A是N型装置,并且具有包括铝(Al)并设置在介电层380上方并直接接触介电层380的填充金属层400a。同时,GAA装置100B是P型装置,并且具有包括钌(Ru)并设置在介电层380上方并直接接触介电层380的填充金属层400b。GAA装置100A或GAA装置100B均不包括个别的功函数金属层。此方案进一步整合了GAA装置的特征,并且在P型和N型区域最大化了形成余量。因此,可制造性可以被显着改善。然而,本公开还考虑了在N型和P型GAA装置两者中包括个别的功函数金属层的实施例,以实现这里所述的一些优点。

如上面所述,填充金属层400(包括填充金属层400a和填充金属层400b)、功函数金属层390(在N型区域中)、介电层380和介电层370可以各自以360度围绕每一个下方的表面。然而,本公开不限于此。替代地(未显示),介电层370可以仅围绕半导体层120的子集,而留下的剩余半导体层120“裸露(naked)”。相似地,介电层380可以仅围绕其下方的半导体层120的子集上方的表面(半导体层120本身的表面或介电层370(如果存在)的表面),而留下的剩余表面“裸露”。功函数金属层390和填充金属层400有相同应用。

在许多实施例中,方法继续形成额外的接点特征(contact feature),以及通过接点特征耦接主动区的互连结构的其他部件。在一些实施例中,相同的材料(例如钌(Ru))也可以用在这些额外的部件中,以进一步整合导电路径并改善装置的可制造性。举例来说,除了在填充金属层400b中使用Ru之外,Ru还可以用于接点、通孔特征及/或金属线中。相似的益处可被实现,例如更大的特征体积、更低的电阻、提升载子迁移率以及增加可靠性和减少成本。

图11显示了半导体装置上方的互连结构602的剖面图。互连结构602包括被配置以将各种装置耦接到功能电路(例如功能SRAM电路或包括SRAM电路的逻辑电路)的各种导电特征。在所示的实施例中,互连结构602被设置在半导体装置(例如GAA装置100A及/或GAA装置100B)上方。互连结构602包括在GAA装置100A及/或GAA装置100B的外延源极/漏极特征210上方的接点特征410(也称为MD接点)。可以在外延源极/漏极特征210求和点特征410之间设置一层自我对准硅化物材料(也称为硅化物层)。互连结构602还包括在接点特征410上方的通孔特征604(也称为VD)和在金属栅极510上方的通孔特征606(也称为VG)。通孔特征604和606将接点特征和金属栅极连接到金属线(例如VD导轨608),金属线进一步连接到电源。接点特征410、通孔特征604和606以及金属线608被嵌入在各种ILD层内,例如ILD层230和ILD层232至234,以在各种导电特征之间提供分隔和隔离。ILD层232设置在ILD层230上方,并且被接点蚀刻停止层(contact-etch stop layer;CESL)220分开;以及ILD层234设置在ILD层232上方,并且被接点蚀刻停止层(CESL)220分开。ILD层232至234在许多方面与ILD层230相似。在一些实施例中,互连结构602包括阻挡层240。值得注意的是,为了清楚和简单起见,图11中未显示各种装置特征及/或额外的金属层和ILD层。

如上面所述,在一些实施例中,接点特征410及/或通孔特征604和606可以包括与填充金属层400a/400b中相同的材料。举例来说,填充金属层400a/400b可以包括钌(Ru),并且接点特征410及/或通孔特征604和606也可以包括钌(Ru),使得钌(Ru)从栅极介电层的外表面延伸穿过填充金属层和通孔特征到通孔特征的顶表面。另外,Ru还可以从源极/漏极特征的顶表面延伸穿过接点特征和通孔特征到通孔特征的顶表面。如上面所述,通过使用相同的材料,可以整合各种导电层,并且大抵上简化了制造。结果,提高了与制造相关的效率、可靠性和成本。在一些实施例中,接点特征410可具有约0.5nm至约90nm的厚度。在一些实施例中,互连结构602还包括围绕接点特征410的低电阻界面阻挡金属层。界面阻挡金属层可以包括任何合适金属,例如钨(W)、钼(Mo)、铱(Ir)、铂(Pt)、锇(Os)。替代地,界面阻挡金属层可以包括氮化钛(TiN)或氮化钽(TaN)。界面阻挡金属层644可以具有约0.5nm至约5nm的厚度。然而,在一些其他实施例中,不存在阻挡金属。可以使用相似的方法来形成通孔特征604和606。在一些实施例中,可以形成没有阻挡层的通孔特征。通孔特征可具有约0.5nm至约60nm的厚度。取决于装置的目的和设计,可以形成金属线。

图12A和图12B显示了制造半导体结构(例如集成电路(IC)装置)的方法800的流程图。方法800包括操作810,在半导体基板的第一区域中形成第一半导体层和第二半导体层的第一堆叠,并且在半导体基板的第二区域中形成第一半导体层和第二半导体层的第二堆叠。第一半导体层和第二半导体层具有不同的材料组成并且在堆叠内彼此交替。方法800可以进一步包括操作820,在第一区域中的第一堆叠上方形成第一冗余栅极结构,并且在第二区域中的第二堆叠上方形成第二冗余栅极结构,其中第一冗余栅极结构和第二冗余栅极结构各自个别围绕第一堆叠和第二堆叠的顶表面和侧表面;操作830,在第一区域中的第一冗余栅极结构的两侧上成长第一对源极/漏极,并且在第二区域中的第二冗余栅极结构的两侧上成长第二对源极/漏极;操作840,个别在第一和第二区域中的第一对源极/漏极和第二对源极/漏极上方形成层间介电质(ILD);操作850,个别从第一区域和第二区域中移除第一冗余栅极结构和第二冗余栅极结构;操作860,执行通道释放工艺,以移除第一区域和第二区域中的第一半导体层,以个别形成第一多个悬置半导体层和第二多个悬置半导体层;操作870,在第一多个悬置半导体层上方和之间以及第二多个悬置半导体层上方和之间形成栅极介电层;操作880,在第二多个悬置半导体层上方和之间形成功函数金属层,而不在第一多个悬置的半导体层上方和之间形成功函数金属层;操作890,在第一区域中的栅极介电层上方形成填充金属层,并且在第二区域中的功函数金属层上方形成填充金属层。方法800可以进一步包括操作900,在装置上方形成互连结构。在一些实施例中,所制造的IC装置包括GAA装置。

填充金属层可以以无氟工艺形成。举例来说,填充金属层可以由无卤素的前驱物形成。使用基于卤素的前驱物(例如六氟化钨、六氯化钨)的工艺通常会在填充金属层中留下相对少量的卤化物(例如氟化物及/或氯化物)。然而,这些化学物质即使少量也已显示出会扩散到一或多个下方的层(例如功函数金属层、介电层)、鳍片(包括通道层)及/或装置的其他层及/或结构,并且对装置效能产生不利影响。举例来说,氟污染物扩散到下方的功函数金属层可以对功函数产生负面影响,因此对临界电压产生负面影响。此外,污染物的不均匀扩散可能导致装置的阈值电压不均匀,这降低了装置的可靠性。尽管已经使用阻挡层来减轻这些问题中的一些,但它们并不总是有效的。举例来说,已知氟渗透常见的阻挡层,例如氮化钛(TiN)或氮化钽(TaN)。另外,如上面所述,阻挡层的使用减少了必要层的形成余量,并且在制造的其他领域提出了挑战。相较之下,此处使用的一些前驱物不包含卤化物(例如氟或氯),而是基于羰基的或基于MOCVD的前驱物。因此,在这些实施例中,不将卤化物引入系统中,使得有效地消除这种担忧。举例来说,填充金属层400a及/或400b可以包括钌(Ru)。填充金属层400a及/或400b可以由十二羰基三钌(triruthenium dodecacarbonyl)(Ru3(CO)12)、三羰基[(1,2,4,5-.eta.)-1-甲基-1,4-环己二烯]钌(tricarbonyl[(1,2,4,5-.eta.)-1-methyl-1,4-cyclohexadiene]ruthenium)(C

填充金属层可以通过在相对较低但是升高的温度(高于室温)下的沉积工艺形成,以在冷却时在纳米通道中产生压缩应力。低温的使用减少了临界电压的变化,从而增加了工艺可靠性。举例来说,可以通过CVD在约100℃至约200℃之间的沉积温度下形成钌(Ru)的填充金属层400a及/或400b。在一个实施例中,十二羰基三钌(Ru

在一个实施例中,CVD或ALD沉积工艺包括多个沉积循环,每一个沉积循环形成钌(Ru)层。举例来说,每一个沉积循环可以使用载气将钌(Ru)前驱物引入反应腔室中,例如流率为约20sccm至约500sccm的氮气(N

在一个实施例中,在沉积循环内的吹扫工艺之后进行氧化处理,以便用氧(O)掺杂物掺杂钌(Ru)薄膜。举例来说,可以引入氧化剂(oxidizing agent)(例如具有RPS自由基、独立分子氧(stand-alone molecular oxygen)及/或其他合适氧化剂)以与钌(Ru)薄膜反应。替代地或额外地,吹扫工艺之后可以进行氨(NH

在一个实施例中,在填充金属层400a及/或400b上进行沉积后退火工艺,以在纳米通道上达到合适的压缩应力。举例来说,填充金属层400a及/或400b可以在约400℃至500℃的温度下经受退火处理,其中退火环境包括在约1%至约10%的百分比的氢气(H

在另一个实施例中,填充金属层400a及/或400b包括铝(Al)。举例来说,可以使用后续进行回流铝(Al)工艺的CVD Al沉积工艺来形成铝(Al)的填充金属层。铝(Al)的填充金属层可以掺杂有氮(N)、碳(C)及/或钛(Ti)以实现与纯铝(Al)不同的功函数。

应理解可以在操作810至900的之前、之中或之后执行额外工艺。举例来说,方法800可以包括形成接点开口、自我对准硅化物层、接点金属以及连接各种特征的各种接点、通孔、导线的操作,以形成可以包括一或多个多栅极装置的功能电路。当形成自我对准硅化物层时,它们可以包括钛(Ti)、钴(Co)、镍(Ni)、镍钴(NiCo)、铂(Pt)、镍铂(Ni(Pt))、铱(Ir)、铂铱(Pt(Ir))、铒(Er)、镱(Yb)、钯(Pd)、铑(Rh)、铌(Nb)、氮化钛硅(TiSiN)或其组合。

互连结构可以包括接点特征、通孔特征和金属线特征。这些特征可以通过任何合适方法来沉积,例如CVD、PVD、无电沉积(electroless deposition;ELD)、电化学电镀(electrochemical plating;ECP)或ALD。可以使用金属有机或无机前驱物(例如包含钌(Ru)、铱(Ir)、镍(Ni)、锇(Os)、铑(Rh)、铝(Al)、钼(Mo)、钨(W)、钴(Co)或其组合的那些金属有机或无机前驱物)与反应气体(例如氢(H

基于以上讨论,可以看出本公开的实施例提供了优于常规半导体装置的优点。然而,应理解不需特定的优点,其他实施例可以提供不同的优点,并且在此处不必公开所有优点。一个优点是降低了电阻。如上面所述,在常规的GAA装置中,典型的填充金属材料包括钴(Co)、铜(Cu)和钨(W)。由于特征的狭窄尺寸和固有的材料特性,这些填充金属材料不能提供足够低的电阻以提供期望的效能或甚至功能。在这里使用了新的填充金属材料,例如钌(Ru)。它在相应尺寸下提供了较低的电阻率。此外,不再需要阻挡层。因此,释放了特征之间的有限空间,从而有利于更大和更好的填充金属,有效地进一步减小了装置的电阻。另外,这些新颖的填充金属材料中的一些,例如钌(Ru)和铝(Al),也在通道层上施加合适类型和大小的应力,从而进一步增加了通道区中的载子的迁移率。这些金属还具有更好的回流特性,因此有利于形成各种特征,特别是凹入特征。此外,使用这些新颖的填充金属材料还可以实现无氟工艺。如此一来,本公开可以改善GAA装置的效能、可靠性及/或经济性。

本公开的一个实施例涉及一种集成电路(IC)装置。集成电路装置包括半导体基板、在具有半导体材料的半导体基板上方的多个第一半导体层、圆周地围绕第一半导体层的第一层的第一栅极介电层、以及第一栅极电极。第一栅极电极包括功函数金属层和第一填充金属层,功函数金属层具有圆周地围绕第一栅极介电层的第一导电材料,并且第一填充金属层具有围绕功函数金属层的第二导电材料。集成电路装置还包括在具有半导体材料的半导体基板上方的多个第二半导体层、圆周地围绕第二半导体层的第二层的第二栅极介电层、以及第二栅极电极。第二栅极电极包括第二填充金属层,第二填充金属层具有围绕并直接接触第二栅极介电层的第二导电材料。第二填充金属层的顶表面在第二多个半导体层的最顶层上方延伸。第一导电材料的功函数低于半导体材料的中间能隙,并且第二导电材料的功函数高于半导体材料的中间能隙。

在一些实施例中,第一半导体层接触N型掺杂源极特征和N型掺杂漏极特征;第二多个半导体层接触P型掺杂源极特征和P型掺杂漏极特征;以及第二导电材料的功函数等于或高于4.7eV。在一些实施例中,第二导电材料的热膨胀系数(CTE)大于半导体材料的热膨胀系数,并且第二层的通道区包括由第二导电材料施加的至少约70MPa至约80MPa的压缩应力。在一些实施例中,功函数金属层包括钛(Ti)、铝(Al)、钽(Ta)、钛铝(TiAl)、氮化钛铝(TiAlN)、碳化钽(TaC)、氮碳化钽(TaCN)、氮化钽硅(TaSiN)中的一者。在一些实施例中,半导体材料包括硅;第一栅极介电层和第二栅极介电层的每一者包括高k介电材料;以及第二导电材料包括钌(Ru)、铱(Ir)、锇(Os)、铑(Rh)或其组合。在一些实施例中,第二导电材料包括钌(Ru)。

在一些实施例中,第二多个半导体层的每一者在第一方向上延伸,并且具有在垂直于第一方向的第二方向上测量的第一横向尺寸。第二多个半导体层的每一者在第三方向上彼此堆叠设置,第三方向与由第一方向和第二方向定义的平面正交。第二栅极介电层的第一部分在第三方向上夹设在第二多个半导体层的相邻层之间。第二填充金属层直接接触第二栅极介电层的第二部分,并且从第二部分的第一侧壁水平连续地延伸到第二部分的第二侧壁。在一些实施例中,集成电路装置还包括互连结构,其中互连结构包括第二导电材料的栅极接点特征,并其栅极接点特征连续地延伸到第二填充金属层。

本公开的另一个实施例涉及一种集成电路(IC)装置。集成电路装置包括具有第一主动区和第二主动区的半导体基板、设置在第一主动区上的第一源极特征和第一漏极特征、以及设置在第二主动区上的第二源极特征和第二漏极特征。集成电路装置还包括夹设于第一源极特征和第一漏极特征的多个第一半导体层,以及夹设于第二源极特征和第二漏极特征的多个第二半导体层。集成电路装置还包括圆周地围绕第一半导体层的每一者的第一栅极介电层,以及圆周地围绕第二多个半导体层的每一者的第二栅极介电层。集成电路装置还包括包括了圆周地围绕并直接接触第一栅极介电层的第一导电层的第一栅极电极,以及在第一栅极电极上方并直接接触第一栅极电极的第一栅极接点特征。集成电路装置还包括第二栅极电极,第二栅极电极包括功函数金属层和第二导电层,功函数金属层圆周地围绕第二栅极介电层的每一者,并且第二导电层圆周地围绕并直接接触功函数金属层,以及在第二栅极电极上方并直接接触上第二栅极电极的第二栅极接点特征。第一半导体层包括由第一导电层施加的压缩应力。

在一些实施例中,功函数金属层具有第一侧壁和与第一侧壁相对的第二侧壁;第二栅极介电层具有第三侧壁和与第三侧壁相对的第四侧壁;其中第一导电层的上部从第一侧壁水平连续地延伸到第二侧壁;以及其中第二导电层的上部从第三侧壁水平连续地延伸到第四侧壁。在一些实施例中,第一导电层包括第一金属材料,其中第一金属材料的功函数等于或高于约4.7eV,并且第二导电层包括第一金属材料。在一些实施例中,第一金属材料的热膨胀系数(CTE)大于半导体基板的热膨胀系数,并且第二导电层在第二半导体层上方施加至少约70MPa至约80MPa的压缩应力。在一些实施例中,第一金属材料包括钌(Ru)、铱(Ir)、锇(Os)、铑(Rh)中的一者。

本公开的又一个实施例包括一种集成电路(IC)装置的形成方法。集成电路(IC)装置的形成方法包括在半导体基板的第一区域中形成多个第一悬置半导体层,并且在半导体基板的第二区域中形成多个第二悬置半导体层,其中第一悬置半导体层和第二悬置半导体层中的每一者彼此间隔。形成栅极介电层以圆周地围绕第一悬置半导体层和第二悬置半导体层。在栅极介电层的一部分上方形成功函数金属层,以圆周地围绕第二悬置半导体层。在第一区域中形成在栅极介电层上并直接接触栅极介电层的填充金属层,并且在第二区域中形成在功函数金属层上并直接接触功函数金属层的填充金属层。在一些实施例中,填充金属层通过在冷却时足够在第一悬置半导体层中产生压缩应力的高温下的沉积工艺形成。在一些实施例中,填充金属层包括选自钌(Ru)、铱(Ir)、锇(Os)和铑(Rh)的第一金属材料。

在一些实施例中,形成第一悬置半导体层和第二悬置半导体层的操作各自包括:形成多个第一半导体层和多个第二半导体层的半导体堆叠,其中第一半导体层和第二半导体层具有不同的材料组成并且在半导体堆叠内彼此交替;在半导体堆叠上方形成冗余栅极结构,其中冗余栅极结构围绕半导体堆叠的顶表面和多个侧表面;在冗余栅极结构的两侧上成长多个源极/漏极;在源极/漏极上方形成层间介电质;移除冗余栅极结构;以及在移除冗余栅极结构之后,执行通道释放工艺以移除第一半导体层。在一些实施例中,形成填充金属层的操作包括形成填充金属层,使得填充金属层的上部从栅极介电层的第一侧壁连续地延伸到与第一侧壁相对的栅极介电层的第二侧壁。在一些实施例中,第一金属材料包括钌(Ru)。在一些实施例中,形成填充金属层的操作包括在高于100℃的高温下在栅极介电层上方沉积第一金属材料。在一些实施例中,沉积第一金属材料的操作包括在约100℃至约200℃之间调节温度以调整通道区上方的压缩应力,使得压缩应力超过约70MPa至约80MPa。在一些实施例中,集成电路装置的形成方法还包括在第一悬置半导体层和第二悬置半导体层上方形成互连结构,其中互连结构包括具有第一金属材料的第一导电特征,并且第一导电特征连续地延伸到填充金属层。

前述内文概述了许多实施例的特征,使本技术领域中技术人员可以从各个方面优选地了解本公开。本技术领域中技术人员应可理解,且可轻易地以本公开为基础来设计或修饰其他工艺及结构,并以此达到相同的目的及/或达到与在此介绍的实施例等相同的优点。本技术领域中技术人员也应了解这些相等的结构并未背离本公开的发明构思与范围。在不背离本公开的发明构思与范围的前提下,可对本公开进行各种改变、置换或修改。

- 集成电路压板装置、集成电路热板装置及集成电路焊线装置

- 集成电路去毛刺装置、集成电路去毛刺辅助装置以及集成电路去毛刺方法