显示设备和包括该显示设备的多屏显示设备

文献发布时间:2023-06-19 11:52:33

相关申请的交叉引用

本申请要求于2019年12月31日提交的韩国专利申请No.10-2019-0180118的权益,通过引用将该专利申请并入本文,如同在本文完全阐述一样。

技术领域

本发明涉及一种显示设备和包括该显示设备的多屏显示设备。

背景技术

近来,随着多媒体的发展,显示设备的重要性日益增加。因此,诸如液晶显示(LCD)设备、有机发光显示设备和发光二极管显示设备之类的显示设备正在商业化。

显示设备具有诸如薄、轻和低功耗之类的优良特征,因而广泛用作电视(TV)、笔记本电脑和监视器以及诸如电子笔记本、电子书、便携式多媒体播放器(PMP)、导航装置、超级移动个人电脑(PC)、移动电话、智能电话、智能手表、平板个人电脑(PC)、手表电话和移动通讯终端之类的便携式电子装置的显示屏。

显示设备可包括:显示面板,显示面板包括具有与数据线和栅极线连接的薄膜晶体管(TFT)的多个像素;用于向数据线提供数据电压的数据驱动电路;和用于向栅极线提供扫描信号的栅极驱动电路。显示面板可包括显示区域和围绕显示区域的边框区域,显示区域包括显示图像的多个像素。

相关技术的显示设备需要用于覆盖设置在显示面板的边界(或边缘部分)处的边框区域的边框(或机构),由于这个原因,边框的宽度会增加。

近来,通过将多个显示设备布置为格子型来实现大屏幕的多屏显示设备已商业化。

然而,在相关技术的多屏显示设备中,由于多个显示设备的每一个的边框区域或边框,在相邻显示设备之间形成诸如接缝之类的边界部分。当在多屏显示设备的整个屏幕上显示一个图像时,边界部分导致图像的间断感(不连续性),由于这个原因,观看图像的观看者的沉浸感降低。

[现有技术文献]

[专利文献]

韩国专利授权No.10-1441956(发明名称:多面板显示设备,国际分类号:G02F/1335,G02F1/13357)

发明内容

因此,本发明旨在提供一种基本上克服了由于相关技术的局限性和缺点而导致的一个或多个问题的显示设备和包括该显示设备的多屏显示设备。

本发明的一个方面旨在提供一种未设置有边框的显示设备。

本发明的另一个方面旨在提供一种在没有间断感的情况下显示图像的多屏显示设备。

在下面的描述中将部分列出本发明的附加优点和特征,这些优点和特征的一部分在研究以下内容时对于所属领域普通技术人员将变得显而易见或者可通过本发明的实践领会到。本发明的这些目的和其他优点可通过说明书及其权利要求书以及附图中具体指出的结构来实现和获得。

为了实现这些和其他优点并根据本发明的意图,如在此具体化和概括描述的,提供了一种显示设备,包括:第一基板,所述第一基板包括设置在显示部分中的多个像素区域;接合至所述第一基板的第二基板;和设置在所述第一基板的外表面和所述第二基板的外表面上的布线部分,其中所述第一基板包括:设置在所述显示部分上的钝化层;在所述显示部分的边缘部分上实现在所述钝化层中的阻挡图案部分,所述阻挡图案部分包括阻挡金属图案;和发光器件层,所述发光器件层包括设置在所述阻挡图案部分和所述多个像素区域上的发光器件,并且所述发光器件被所述阻挡图案部分隔离。

根据本发明的一些实施方式的显示设备包括:第一基板,所述第一基板包括设置在显示部分中的多个像素区域;设置在所述多个像素区域之中的最外侧像素区域中的堰图案;设置在所述最外侧像素区域中并围绕所述堰图案的阻挡图案部分;发光器件层,所述发光器件层包括设置在所述多个像素区域上的公共电极和发光器件;和接合至所述第一基板的第二基板,其中所述阻挡图案部分包括用于将所述发光器件以及所述公共电极的每一个隔离的隔离结构。

根据本发明的一些实施方式的多屏显示设备包括:沿第一方向和与第一方向交叉的第二方向中的至少一个方向布置的多个显示模块,其中所述多个显示模块的每一个包括:第一基板,所述第一基板包括设置在显示部分中的多个像素区域;接合至所述第一基板的第二基板;和设置在所述第一基板的外表面和所述第二基板的外表面上的布线部分,其中所述第一基板包括:设置在所述显示部分上的钝化层;在所述显示部分的边缘部分上实现在所述钝化层中的阻挡图案部分,所述阻挡图案部分包括阻挡金属图案;和发光器件层,所述发光器件层包括设置在所述阻挡图案部分和所述多个像素区域上的发光器件,并且所述发光器件被所述阻挡图案部分隔离。

根据本发明的一些实施方式的多屏显示设备包括:沿第一方向和与第一方向交叉的第二方向中的至少一个方向布置的多个显示模块,其中所述多个显示模块的每一个包括:第一基板,所述第一基板包括设置在显示部分中的多个像素区域;设置在所述多个像素区域之中的最外侧像素区域中的堰图案;设置在所述最外侧像素区域中并围绕所述堰图案的阻挡图案部分;发光器件层,所述发光器件层包括设置在所述多个像素区域上的公共电极和发光器件;和接合至所述第一基板的第二基板,其中所述阻挡图案部分包括用于将所述发光器件以及所述公共电极的每一个隔离的隔离结构。

根据本发明的一些实施方式,可提供一种不包括边框的显示设备和包括该显示设备的多屏显示设备。

根据本发明的一些实施方式,显示设备可包括设置在显示部分的边缘部分处的阻挡图案部分,以将发光器件隔离,由此提供一种用于防止发光器件由于侧向方向的水分渗透而劣化并且提高发光器件的可靠性的显示设备和包括该显示设备的多屏显示设备。

根据本发明的一些实施方式,可提供一种在没有间断感的情况下显示图像的多屏显示设备。

应当理解,本发明前面的概括描述和下面的详细描述都是例示性的和解释性的,旨在对要求保护的本发明提供进一步的解释。

附图说明

给本发明提供进一步理解并且并入本申请组成本申请一部分的附图图解了本发明的实施方式,并与说明书一起用于解释本发明的原理。在附图中:

图1是图解根据本发明的显示设备的示图;

图2图1中所示的区域“A”的放大图;

图3是图解根据本发明一实施方式的显示设备的透视图;

图4是图解根据本发明一实施方式的显示设备的后表面的示图;

图5是图3中所示的区域“B”的放大图;

图6是图解图3中所示的显示区域中设置的栅极驱动电路的示图;

图7是图解图3中所示的一个像素的电路图;

图8是图解图4中所示的第二基板的示图;

图9是图8中所示的区域“C”的放大图;

图10是图解图6中所示的第i级电路单元的电路图;

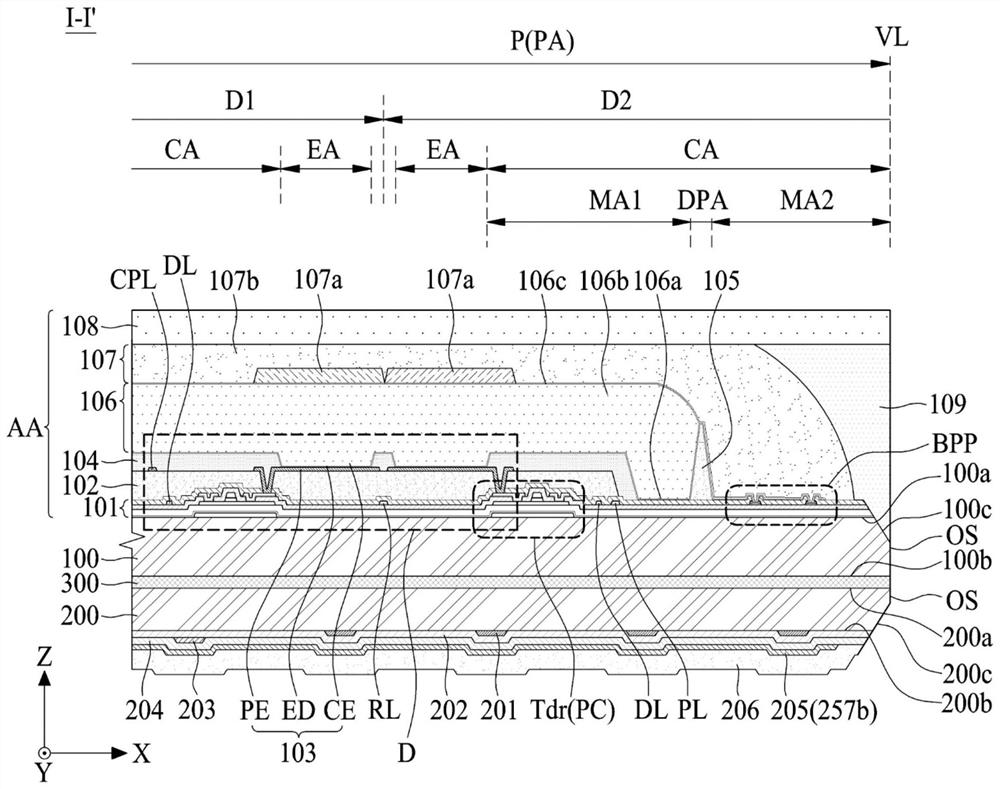

图11是沿图3中所示的线I-I’截取的剖面图;

图12是图11中所示的区域“D”的放大图;

图13是沿图3中所示的线II-II’截取的剖面图;

图14是图13中所示的区域“E”的放大图;

图15是图解图13中所示的第二基板的后表面的示图;

图16是图解根据本发明一实施方式的多屏显示设备的示图;

图17是图解对图16中所示的显示设备执行的铺设工艺的示图;

图18是沿图16中所示的线III-III’截取的剖面图;

图19A和图19B是图解分别由根据比较例的多屏显示设备和根据本发明的多屏显示设备显示的图像的示图。

具体实施方式

现在将详细参考本发明的示例性实施方式进行描述,附图中图解了这些实施方式的一些例子。尽可能地将在整个附图中使用相同的参考标记表示相同或相似的部分。

将通过参照附图描述的以下实施方式阐明本发明的优点和特征以及其实现方法。然而,本发明可以以不同的形式实施,不应解释为限于在此列出的实施方式。而是,提供这些实施方式是为了使本发明的公开内容全面和完整,并将本发明的范围充分地传递给所属领域技术人员。另外,本发明仅由权利要求书的范围限定。

为了描述本发明的实施方式而在附图中公开的形状、大小、比例、角度和数量仅仅是示例,因而本发明不限于图解的细节。相似的参考标记通篇指代相似的要素。在下面的描述中,当确定对相关已知功能或构造的详细描述会不必要地使本发明的重点模糊不清时,将省略该详细描述。在本申请中使用“包括”、“具有”和“包含”进行描述的情况下,可添加其他部分,除非使用了“仅”。

在解释一要素时,尽管没有明确说明,但该要素应解释为包含误差范围。

在描述位置关系时,例如,当两部分之间的位置关系被描述为“在……上”、“在……上方”、“在……下方”和“在……之后”时,可在这两部分之间设置一个或多个其他部分,除非使用了“正好”或“直接”。

在描述时间关系时,例如,当时间顺序被描述为“在……之后”、“随后”、“接下来”和“在……之前”时,可包括不连续的情况,除非使用了“正好”或“直接”。

将理解到,尽管在此可使用术语“第一”、“第二”等来描述各种要素,但这些要素不应受这些术语限制。这些术语仅仅是用来将一要素与另一要素区分开。例如,在不背离本发明的范围的情况下,第一要素可能被称为第二要素,类似地,第二要素可能被称为第一要素。

在描述本发明的要素时,可使用诸如第一、第二、A、B、(a)、(b)等之类的术语。这些术语仅用于将相应要素与其他要素区分开,这些术语不限制相应要素的本质、次序或优先顺序。将理解到,当称一要素或层在另一要素或层“上”或“连接至”另一要素或层时,该要素可直接在另一要素或层上或者直接连接至另一要素或层,或者可存在中间要素或层。此外,应当理解到,当一要素设置在另一要素上方或下方时,其可表示这些要素设置成彼此直接接触的情况,但也可表示这些要素彼此不接触地设置。

术语“至少一个”应当理解为包括相关所列要素中的一个或多个的任意和所有组合。例如,“第一要素、第二要素和第三要素中的至少一个”可表示选自第一要素、第二要素和第三要素中的两个或更多个要素的所有要素的组合以及第一要素、第二要素或第三要素。

所属领域技术人员能够充分理解到,本发明各实施方式的特征可彼此部分或整体地结合或组合,且可在技术上彼此进行各种互操作和驱动。本发明的实施方式可彼此独立实施,或者以相互依赖的关系共同实施。

下文中,将参照附图详细描述本发明的实施方式。在给每个附图的要素添加参考标记时,尽管相同的要素被示出在其他附图中,但相似的参考标记可指代相似的要素。此外,为了便于描述,附图中示出的每个要素的比例不同于实际比例,因而不限于附图中示出的比例。

图1是图解根据本发明的显示设备的示图,图2是图1中所示的区域“A”的放大图。

参照图1和图2,根据本发明的显示设备可包括第一基板100,第一基板100包括显示区域AA和在第一基板100的显示区域AA上以第一间隔D1布置的多个像素P。

第一基板100可包括第一表面、第二表面和外表面OS。第一基板100的第一表面可定义为面向显示设备的前表面(或向前方向)的前表面、顶表面或上表面。第一基板100的第二表面可定义为面向显示设备的背面(或向后方向)的背面、后表面、底表面或下表面。第一基板100的外表面OS可定义为沿第一表面与第二表面之间的外围延伸、面向显示设备的侧面(或侧向)并且暴露于空气的侧表面、侧面或侧壁。例如,当第一基板100具有六面体结构时,第一基板100的外表面OS可包括六面体结构的侧表面。

第一基板100的外表面OS可与显示设备的厚度方向Z平行地形成。例如,第一基板100的外表面OS可包括:与第一方向X平行的第一外表面、与第一外表面平行的第二外表面、与第二方向Y(第二方向Y与第一方向X横切(或交叉))平行并且连接在第一外表面的一端与第二外表面的一端之间的第三外表面、以及与第三外表面平行并且连接在第一外表面的另一端与第二外表面的另一端之间的第四外表面。第一方向X可以是第一基板100或显示设备的第一长度方向(例如,横向方向),第二方向Y可以是第一基板100或显示设备的第二长度方向(例如,纵向方向)。

第一基板100的显示区域AA可以是显示图像的区域并且可称为显示部分或有源部分。显示区域AA的尺寸可与第一基板100(或显示设备)相同或大致相同。例如,显示区域AA的尺寸可与第一基板100的第一表面的总尺寸相同。因此,显示区域AA可实现(或设置)在第一基板100的整个前表面上,因而第一基板100可不包括沿第一表面的边缘部分设置以围绕整个显示区域AA的不透明非显示区域。因此,显示设备的整个前表面可实现显示区域AA。

显示区域AA的端部(或最外侧部分)可以是第一基板100的外表面OS。例如,显示部分AA的侧表面可与第一基板100的外表面OS大致共面。换句话说,显示部分AA的侧表面和第一基板100的外表面OS可大致在相同位置对齐。显示部分AA的侧表面可不被单独的机构围绕,可仅由空气围绕。作为另一示例,显示部分AA的侧表面可与第一基板100的外表面OS交叠或者可与第一基板100的外表面OS大致对齐。就是说,显示部分AA的所有侧表面可设置为直接接触空气而不被单独机构围绕的结构。

相对于第一基板100的厚度方向Z,从第一基板100的外表面OS垂直延伸的垂直延伸线和显示区域AA的端部可交叠或可彼此对齐。例如,显示区域AA的第一端部(或上端部)可以是第一基板100的第一外表面(或上侧壁),显示区域AA的第二端部(或下端部)可以是第一基板100的第二外表面(或下侧壁),显示区域AA的第三端部(或左端部)可以是第一基板100的第三外表面(或左侧壁),并且显示区域AA的第四端部(或右端部)可以是第一基板100的第四外表面(或右侧壁)。因此,与显示区域AA的端部对应的第一基板100的外表面OS可被空气围绕,因而根据本发明的显示设备可具有空气边框(air-bezel)结构或无边框结构,其中显示区域AA可被空气围绕而不是被不透明非显示区域围绕。

根据一实施方式的显示区域(或显示部分)AA可包括多个像素区域PA。

多个像素区域PA可以以第一间隔D1布置(或设置)在显示区域AA中。

根据一实施方式的多个像素区域PA可在第一基板100的显示区域AA中以第一间隔D1布置(或设置)。沿第一基板100的第一方向X和第二方向Y彼此相邻的两个像素区域PA可在没有制造工艺的误差范围的情况下具有相同的第一间隔D1。第一间隔D1可以是两个相邻像素区域PA之间的节距(pitch)(或像素间距)。例如,第一间隔D1可以是两个相邻像素区域PA的中心部分之间的最短距离(或最短长度)。可选择地,像素间距可以是像素区域PA的与第一方向X平行的一端和另一端之间的尺寸。此外,作为另一示例,像素间距可称为像素区域PA的与第二方向Y平行的一端和另一端之间的尺寸。

多个像素区域PA的每一个可具有与第一方向X平行的第一长度L1和与第二方向Y平行的第二长度L2。第一长度L1和第二长度L2的每一个可与第一间隔D1相同。例如,第一长度L1可称为第一宽度、横向长度或横向宽度。第二长度L2可称为第二宽度、纵向长度或纵向宽度。像素区域PA的第一长度L1或第二长度L2可称为像素间距。

多个像素区域PA中的每个最外侧像素区域PAo与第一基板100的外表面OS之间的第二间隔D2可以是第一间隔D1的一半或更小,使得第一基板100的整个前表面(或显示设备的整个前表面)称为显示区域AA。例如,第二间隔D2可以是最外侧像素区域PAo的中心部分与第一基板100的外表面OS之间的最短距离(或最短长度)。

当第二间隔D2大于第一间隔D1的一半时,由于最外侧像素区域PAo(或显示区域AA)的端部与第一基板100的外表面OS之间的区域,第一基板100可具有比显示区域AA大的尺寸,因而最外侧像素区域PAo的端部与第一基板100的外表面OS之间的区域会设置为围绕整个显示区域AA的非显示区域。因此,第一基板100必然会包括基于围绕整个显示区域AA的非显示区域的边框区域。另一方面,当第二间隔D2是第一间隔D1的一半或更小时,最外侧像素区域PAo(或显示区域AA)的端部可与第一基板100的外表面OS交叠,或者可设置在第一基板100的外表面OS外侧的空间中,因而显示区域AA可实现(或设置)在第一基板100的整个前表面上。

根据一实施方式的显示区域(或显示部分)AA可包括最外侧像素区域PAo和内部像素区域(或内侧像素区域)PAi。

在多个像素区域PA之中,最外侧像素区域PAo可沿第一基板100的边缘部分(或外围部分)设置。例如,最外侧像素区域PAo可称为第一像素区域PA1。

内部像素区域PAi可以是多个像素区域PA之中的除了最外侧像素区域PAo以外的像素区域,或者可被最外侧像素区域PAo围绕。内部像素区域PAi可称为第二像素区域PA2。

多个像素P的每一个可设置在第一基板100的第一表面上限定的多个像素区域PA之中的相应像素区域PA中。例如,显示区域AA可以是包括布置在第一基板100上的多个像素P的像素阵列。像素阵列的像素P可沿第一方向X和第二方向Y彼此紧邻。例如,像素阵列的像素P可在没有分离空间(或分隔空间)的情况下沿第一方向X和第二方向Y彼此紧邻。作为另一示例,像素阵列的多个最外侧像素Po可彼此匹配以在第一基板100的外表面上交叠,或者可在同一平面对齐。例如,像素阵列的每个像素P可布置在第一基板100上,以沿第一方向X和第二方向Y具有像素间距D1,并且每个最外侧像素Po与第一基板100的外表面OS之间的间隔D2可以是像素间距D1的一半或更小。

根据一实施方式的显示区域(或显示部分)AA可包括最外侧像素Po和内部像素(或内侧像素)Pi。

最外侧像素Po可设置在多个像素区域PA之中的第一基板100的边缘部分(或外围部分)处。例如,最外侧像素Po可称为设置在最外侧像素区域PAo中的第一像素P1。

内部像素Pi可以是多个像素P之中的除了最外侧像素Po以外的像素,或者可设置为被最外侧像素Po围绕。例如,内部像素Pi可称为第二像素P2。内部像素Pi(第二像素P2)可实现为具有与最外侧像素Po(第一像素P1)不同的构造或结构。

多个像素P中的每个最外侧像素Po与第一基板100的外表面OS之间的第二间隔D2可以是第一间隔D1的一半或更小,使得第一基板100的整个前表面(或显示设备的整个前表面)称为显示区域AA。第一间隔D1可以是两个相邻像素P的中心部分之间的最短距离(或最短长度)。第二间隔D2可以是最外侧像素Po的中心部分与第一基板100的外表面OS之间的最短距离(或最短长度)。

根据一实施方式的多个像素P的每一个可包括中心部分Pc和围绕整个中心部分Pc的边缘部分(或外围部分)Pe,中心部分Pc包括多个发光区域PA。

中心部分Pc的中心可与像素P的中心部分CP交叠。中心部分Pc可称为像素P的开口区域或发光部分。

根据一实施方式的中心部分Pc可包括相对于像素P的中心部分CP设置的第一至第四发光区域EA1至EA4。例如,第一至第四发光区域EA1至EA4可沿第一方向X和第二方向Y彼此紧邻。例如,第一至第四发光区域EA1至EA4可在没有分离空间(或分隔空间)的情况下沿第一方向X和第二方向Y彼此直接接触。

第一至第四发光区域EA1至EA4可各自具有正方形形状并且可设置为2×2形式或四边形(quad)形式。根据另一实施方式,第一至第四发光区域EA1至EA4可各自具有包括与第一方向X平行的短边和与第二方向Y平行的长边的矩形形状,并且例如可设置为1×4形式或1×4条纹形式。

第一发光区域EA1可实现为发射第一颜色的光,第二发光区域EA2可实现为发射第二颜色的光,第三发光区域EA3可实现为发射第三颜色的光,并且第四发光区域EA4可实现为发射第四颜色的光。例如,第一至第四颜色的每一个可不同。例如,第一颜色可以是红色,第二颜色可以是蓝色,第三颜色可以是白色,第四颜色可以是绿色。作为另一示例,第一至第四颜色的一些颜色可相同。例如,第一颜色可以是红色,第二颜色可以是第一绿色,第三颜色可以是第二绿色,第四颜色可以是蓝色。

根据另一实施方式,中心部分Pc可包括相对于像素P的中心部分CP设置的第一至第三发光区域EA1至EA3。在这种情况下,第一至第三发光区域EA1至EA3可各自具有包括与第一方向X平行的短边和与第二方向Y平行的长边的矩形形状,并且例如可设置为1×3形式或1×3条纹形式。例如,第一颜色可以是红色,第二颜色可以是蓝色,第三颜色可以是绿色。

边缘部分Pe可设置在像素区域PA中以围绕整个中心部分Pc,因而可限定像素区域PA或像素P的中心部分Pc。边缘部分Pe可具有比中心部分Pc宽的尺寸。边缘部分Pe可称为像素P的非开口部分或像素分离部分。

根据另一实施方式的多个像素P的每一个可包括第一至第四子像素SP1至SP4。

第一至第四子像素SP1至SP4可在相应像素P或像素区域PA中具有相同尺寸或不同尺寸。根据一实施方式的第一至第四子像素SP1至SP4可具有均匀的四边形结构、非均匀的四边形结构、均匀的条纹结构或非均匀的条纹结构。可基于分辨率、发光效率或图像质量设定第一至第四子像素SP1至SP4的每一个的尺寸。例如,当一个像素P包括以非均匀的四边形结构或非均匀的条纹结构布置的红色子像素、绿色子像素、蓝色子像素和白色子像素时,绿色子像素可具有最小尺寸,白色子像素可具有最大尺寸。

第一子像素SP1可设置在像素区域PA的第一子像素区域中,第二子像素SP2可设置在像素区域PA的第二子像素区域中,第三子像素SP3可设置在像素区域PA的第三子像素区域中,第四子像素SP4可设置在像素区域PA的第四子像素区域中。例如,相对于P的中心部分CP,第一子像素SP1可以是像素区域PA的左上区域,第二子像素SP2可以是像素区域PA的右上区域,第三子像素SP3可以是像素区域PA的左下区域,第四子像素SP4可以是像素区域PA的右下区域。

第一至第四子像素SP1至SP4可分别包括多个发光区域EA1至EA4和多个电路区域CA1至CA4。

发光区域EA1至EA4可设置在像素P的中心部分Pc处,或者可靠近像素P的中心部分CP设置。

电路区域CA1至CA4的每一个可靠近发光区域EA1至EA4的相应发光区域设置。电路区域CA1至CA4的每一个可包括用于使相应子像素发光的信号线、电源线和电路。

可选择地,为了增加与发光区域EA1至EA4的尺寸对应的子像素SP1至SP4的开口率或者随着像素P的分辨率更高而减小像素间距D1,发光区域EA1至EA4可延伸至电路区域CA1至CA4,以与电路区域CA1至CA4的一些或全部交叠。在这种情况下,发光区域EA1至EA4可具有等于或大于电路区域CA1至CA4的尺寸。

根据本发明的显示设备可进一步包括焊盘部110,焊盘部110包括设置在显示区域AA中并且选择性地连接至多个像素P的多个焊盘。例如,焊盘部110可以是第一焊盘部或前焊盘部。

焊盘部110可包括在设置于第一基板100的第一表面中的与第一方向X平行的第一边缘部分处的最外侧像素Po中。就是说,设置在第一基板100的第一边缘部分处的最外侧像素Po可包括多个焊盘中的至少一个。因此,多个焊盘可设置或包括在显示区域AA内,因而在第一基板100上不会形成或不存在基于焊盘部110的非显示区域(或边框区域)。

例如,当焊盘部110未设置在最外侧像素Po内而是设置在最外侧像素Po与第一基板100的外表面OS之间时,第一基板100会包括与设置有焊盘部110的区域对应的非显示区域,由于非显示区域,最外侧像素Po与第一基板100的外表面OS之间的第二间隔D2会大于第一间隔D1的一半,整个第一基板100不会实现为显示区域AA,并且会需要用于覆盖非显示区域的单独边框(或单独结构)。另一方面,根据本发明的焊盘部110可设置在最外侧像素Po的发光区域EA1至EA4与第一基板100的外表面OS之间并且可包括在最外侧像素Po内,因而在最外侧像素Po与第一基板100的外表面OS之间不会形成或不会存在基于焊盘部110的非显示区域(或边框区域)。

因此,根据本发明的显示设备可具有空气边框(air-bezel)结构,其中包括焊盘部110的整个第一基板100实现为显示区域AA,因而与显示区域AA的端部对齐的第一基板100的所有外表面(或显示面板的外表面)OS被空气围绕。

图3是图解根据本发明一实施方式的显示设备的透视图,图4是图解根据本发明一实施方式的显示设备的后表面的示图。

参照图3和图4,根据本发明一实施方式的显示设备10可包括第一基板100、第二基板200、接合构件300和布线部分400。

第一基板100可称为显示基板、像素阵列基板、上基板、前基板或基础基板。第一基板100可包括玻璃材料或塑料材料。第一基板100可以是玻璃基板,或者可以是可弯曲或柔性的薄玻璃基板或塑料基板。根据一实施方式的第一基板100可以是玻璃基板或钢化玻璃。例如,钢化玻璃可包括蓝宝石玻璃和大猩猩玻璃之一或其堆叠玻璃。

根据一实施方式的显示设备10可包括设置在第一基板100上的多条像素驱动线和多个像素P。

像素驱动线可设置在第一基板100的第一表面100a上并且可传输多个像素P的每一个的驱动(发光)所需的信号。例如,像素驱动线可包括数据线DL、栅极线GL、像素驱动电源线(或第一电源线)PL、和像素公共电源线(或第二电源线)CPL。另外,基于设置在像素P的电路区域中的像素电路的驱动(或操作),像素驱动线可进一步包括基准电源线(或感测线)RL。

根据一实施方式的每条驱动电源线可与设置在第一基板100的第一表面100a的第一边缘部分处的第一焊盘部110电连接。第一焊盘部110可包括在设置于第一基板100的与第一方向X平行的第一边缘部分处的多个最外侧像素Po中。在此,第一基板100的第一表面100a的第一边缘部分可包括第一基板100的外表面OS中的第一外表面(或一侧表面)OS1a。

第一焊盘部110可包括多个第一焊盘,多个第一焊盘沿第一方向X彼此平行地设置在暴露于第一基板100的第一表面100a的第一边缘部分处的钝化层101d(见图12)上。

根据一实施方式的多个第一焊盘可划分(或分类)为多个第一数据焊盘、多个第一像素驱动电源焊盘、和多个第一像素公共电源焊盘。因此,第一焊盘部110可包括:第一数据焊盘部,第一数据焊盘部包括与多条数据线DL连接的多个第一数据焊盘;第一像素驱动电源焊盘部,第一像素驱动电源焊盘部包括与多条像素驱动电源线PL连接的多个第一像素驱动电源焊盘;和第一像素公共电源焊盘部,第一像素公共电源焊盘部包括与多条像素公共电源线CPL连接的多个第一像素公共电源焊盘。可选择地,第一焊盘部110可进一步包括第一基准电源焊盘部,第一基准电源焊盘部包括与多条基准电源线RL连接的多个第一基准电源焊盘。

多个像素P可分别设置在沿第一方向X和第二方向Y以第一间隔(或第一间距)D1布置的多个像素区域PA中。多个像素P的每一个可包括自发光器件(或自发光元件)和像素电路,自发光器件根据通过与其相邻的相应像素驱动线提供的信号,基于顶部发光型发射光并且将光照射到第一基板100的第一表面100a上方的部分上,像素电路连接至与其相邻的像素驱动线连接,以使自发光器件发光。例如,像素电路可包括驱动薄膜晶体管(TFT),驱动薄膜晶体管向自发光器件提供与通过数据线DL提供的数据信号对应的数据电流。

多个像素P中的最外侧像素与第一基板100的外表面OS之间的距离可以是第一间隔D1的一半或更小。最外侧像素的中心部分与第一基板100的外表面OS之间的第二间隔D2可以是第一间隔D1的一半或更小,因而第一基板100的整个前表面(或显示设备的整个前表面)可实现为显示区域AA。因此,根据本发明的显示设备10可具有显示区域AA被空气围绕的空气边框结构。

第一基板100可进一步包括设置在第一表面100a和外表面OS之间的拐角部分处的第一倒角(chamfer)。第一倒角可将由从外部施加的物理冲击导致的对第一基板100的拐角部分的损坏最小化并且可防止由第一基板100的拐角部分导致的布线部分400的断开。例如,第一倒角可具有45度的角,但不限于此。可通过使用切割轮或抛光轮的倒角工艺来实现第一倒角。因此,设置成与第一倒角接触的第一焊盘部110的第一焊盘的每个外表面可通过经由倒角工艺与第一基板100的拐角部分一起去除或抛光相应部分而包括倾斜表面,其中倾斜表面按照与第一倒角的角度对应的角度倾斜。例如,当在第一基板100的外表面OS和第一表面100a之间以45度的角度形成第一倒角时,第一焊盘的外表面可以以45度的角度形成。

第一基板100可进一步包括设置在显示区域AA中的栅极驱动电路150。

栅极驱动电路150可设置在显示区域AA中,以向设置在第一基板100上的像素P提供扫描信号(或栅极信号)。栅极驱动电路150可向设置在与第一方向X平行的水平行中的像素P同时提供扫描信号。例如,栅极驱动电路150可通过至少一条栅极线GL向设置在一个水平行中的像素P提供至少一个扫描信号。

根据一实施方式的栅极驱动电路150可利用移位寄存器实现,移位寄存器包括多个级电路单元1501至150m(m是2或更大的整数)。就是说,根据本发明的显示设备可包括设置在第一基板的显示区域AA中以向像素P提供扫描信号的移位寄存器。

多个级电路单元1501至150m的每一个可包括沿第一方向X彼此分隔地设置在第一基板100的每个水平行中的多个分支电路1511至151n,n是2或更大的整数。多个分支电路1511至151n可包括至少一个TFT(或分支TFT)并且可设置在沿第一方向X的一个水平行内的两个相邻像素P(或像素区域PA)之间。例如,分支电路1511至151n可逐个设置在沿第一方向X的一个水平行内的两个相邻像素P(或像素区域PA)之间。多个级电路单元1501至150m的每一个可响应于通过第一焊盘部110提供的栅极控制信号按预定顺序产生扫描信号,并且可将扫描信号提供至栅极线GL。例如,栅极控制信号可包括起始信号、多个移位时钟、至少一个栅极驱动电源和至少一个栅极公共电源。

第一基板100可进一步包括彼此分隔地设置在多个像素P之间并且连接至栅极驱动电路150的多个栅极控制线组GCL。每个栅极控制线组GCL可选择性地连接至分别设置在多个级电路单元1501至150m中的多个分支电路1511至151n。例如,多个栅极控制线组GCL可分散设置在多个像素P之间。

根据一实施方式的栅极控制线组GCL可包括起始信号线、多条移位时钟线、至少一条栅极驱动电源线和至少一条栅极公共电源线。根据一实施方式的多条移位时钟线可划分(或分类)为多条扫描时钟线和多条进位时钟线。在此,可省略多条进位时钟线。

第一焊盘部110可进一步包括第一栅极焊盘部,第一栅极焊盘部包括与栅极控制线组GCL连接的多个第一栅极焊盘。

根据一实施方式的多个第一栅极焊盘可划分(或分类)为:与起始信号线连接的第一起始信号焊盘、分别与多条移位时钟线连接的多个第一移位时钟焊盘、与至少一条栅极驱动电源线连接的至少一个第一栅极驱动电源焊盘、和与至少一条栅极公共电源线连接的至少一个第一栅极公共电源焊盘。因此,第一栅极焊盘部可包括第一起始信号焊盘、多个第一移位时钟焊盘、至少一个第一栅极驱动电源焊盘、和至少一个第一栅极公共电源焊盘。根据一实施方式的多个第一移位时钟焊盘可包括分别与多条扫描时钟线连接的多个第一扫描时钟焊盘、和分别与多条进位时钟线连接的多个第一进位时钟焊盘。在此,可省略多个第一进位时钟焊盘。

第二基板200可称为配线基板、连线基板、下基板、后基板或连线玻璃。第二基板200可包括玻璃材料或塑料材料。第二基板200可以是玻璃基板,或者可以是可弯曲或柔性的薄玻璃基板或塑料基板。根据一实施方式的第二基板200可包括与第一基板100相同的材料。

第二基板200可通过使用接合构件300接合(或连接)至第一基板100的第二表面。第二基板200可包括:前表面,前表面面对第一基板100的第二表面或接合至接合构件300;与前表面相对的后表面(或背面);和在前表面与后表面之间的外表面OS。第二基板200可向像素驱动线传输信号并且可增加第一基板100的刚度。

根据一实施方式的第二基板200可进一步包括第二焊盘部210。

第二焊盘部210可设置在第二基板200的后表面200b中的与设置在第一基板100上的第一焊盘部110交叠的第一边缘部分处。第二基板200的后表面200b的第一边缘部分可包括第二基板200的外表面OS中的第一外表面(或一个表面)OS1b。

第二焊盘部210可包括多个第二焊盘,多个第二焊盘沿第一方向X以一定间隔布置,从而分别与第一焊盘部110的焊盘交叠。

根据一实施方式的多个第二焊盘可划分(或分类)为多个第二数据焊盘、多个第二像素驱动电源焊盘、和多个第二像素公共电源焊盘。因此,第二焊盘部210可包括:包括多个第二数据焊盘的第二数据焊盘部、包括多个第二栅极焊盘的第二栅极焊盘部、包括多个第二像素驱动电源焊盘的第二像素驱动电源焊盘部、和包括多个第二像素公共电源焊盘的第二像素公共电源焊盘部。可选择地,第二焊盘部210可进一步包括第二基准电源焊盘部,第二基准电源焊盘部包括多个第二基准电源焊盘。

根据一实施方式的多个第二栅极焊盘可划分(或分类)为第二起始信号焊盘、多个第二移位时钟焊盘、至少一个第二栅极驱动电源焊盘、和至少一个第二栅极公共电源焊盘。因此,第二栅极焊盘部可包括第二起始信号焊盘、多个第二移位时钟焊盘、至少一个第二栅极驱动电源焊盘、和至少一个第二栅极公共电源焊盘。根据一实施方式的多个第二移位时钟焊盘可划分(或分类)为多个第二扫描时钟焊盘和多个第二进位时钟焊盘。在此,可省略多个第二进位时钟焊盘。

根据一实施方式的显示设备10可进一步包括设置在第二基板200上的第三焊盘部(或输入焊盘部)230和连线部分250。

第三焊盘部230可设置在第二基板200的后表面200b上。例如,第三焊盘部230可设置在第二基板200的后表面200b中的与第一边缘部分相邻的中间部分处。根据一实施方式的第三焊盘部230可包括彼此分隔开一定间隔的多个第三焊盘(或输入焊盘)。

连线部分250可在第二基板200的后表面200b上设置在第二焊盘部210与第三焊盘部230之间。例如,连线部分250可包括单独(或分别)将第二焊盘部210的第二焊盘连接至第三焊盘部230的第三焊盘的多条连线。

第二基板200可进一步包括设置在后表面200b与外表面OS之间的拐角部分处的第二倒角。第二倒角可将由从外部施加的物理冲击导致的对第二基板200的拐角部分的损坏最小化并且可防止由第二基板200的拐角部分导致的布线部分400的断开。例如,第二倒角可具有45度的角,但不限于此。

接合构件300可设置在第一基板100与第二基板200之间。第一基板100和第二基板200可通过接合构件300彼此相对地接合。例如,第一基板100的第二表面可接合至接合构件300的一个表面,并且第二基板200的前表面可接合至接合构件300的另一个表面。因此,通过接合构件300彼此相对地接合(或耦接)的第一基板100和第二基板200可称为显示面板。

布线部分400可设置成围绕第一基板100的外表面OS和第二基板200的外表面OS。根据一实施方式的布线部分400可包括多条布线,多条布线设置在第一基板100的外表面OS中的第一外表面(或一个表面)OS1a和第二基板200的外表面OS中的第一外表面(或一个表面)OS1b的每一个上。多条布线的每一条可形成为围绕第一基板100的第一外表面OS1a和第二基板200的第一外表面OS1b的每一个。例如,多条布线可分别(或单独)连接至设置在第一基板100上的像素驱动线并且可直接连接至像素驱动线。作为另一示例,多条布线可通过设置在第一基板100上的第一焊盘部110的焊盘分别(或单独)连接至像素驱动线,在这种情况下,由于基于焊盘的尺寸的增加,可减小每条像素驱动线的电阻和/或施加至像素驱动线的信号的压降(或IR降)。

根据一实施方式的多条布线可划分(或分类)为多条数据布线、多条栅极布线、多条像素驱动电源布线、和多条像素公共电源布线。

根据另一实施方式,布线部分400可包括数据布线部分、栅极布线部分、像素驱动电源布线部分和像素公共电源布线部分。

数据布线部分(或第一布线部分)可将第一焊盘部110的第一数据焊盘部电连接至第二焊盘部210的第二数据焊盘部。根据一实施方式的数据布线部分可包括多条数据布线410。多条数据布线(或第一布线)410可单独(或分别)将设置在第一焊盘部110中的多个第一数据焊盘连接至设置在第二焊盘部210中的多个第二数据焊盘。

栅极布线部分(或第二布线部分)可将第一焊盘部110的第一栅极焊盘部电连接至第二焊盘部210的第二栅极焊盘部。根据一实施方式的栅极布线部分可包括多条栅极布线430。多条栅极布线(或第二布线)430可单独(或分别)将设置在第一焊盘部110中的多个第一栅极焊盘连接至设置在第二焊盘部210中的多个第二栅极焊盘。

根据一实施方式的多条栅极布线430可划分(或分类)为起始信号布线、多条移位时钟布线、至少一条栅极驱动电源布线和至少一条栅极公共电源布线。因此,栅极布线部分可包括起始信号布线、多条移位时钟布线、至少一条栅极驱动电源布线、和至少一条栅极公共电源布线。根据一实施方式的多条移位时钟布线可划分(分类)为多条扫描时钟布线和多条进位时钟布线。在此,可省略多条进位时钟布线。

起始信号布线可将设置在第一焊盘部110中的第一起始信号焊盘电连接至设置在第二焊盘部210中的第二起始信号焊盘。

多条移位时钟布线可单独(或分别)将设置在第一焊盘部110中的多个第一移位时钟焊盘连接至设置在第二焊盘部210中的多个第二移位时钟焊盘。

根据一实施方式的多条移位时钟布线之中的多条扫描时钟布线可单独(或分别)将设置在第一焊盘部110中的多个第一扫描时钟焊盘连接至设置在第二焊盘部210中的多个第二扫描时钟焊盘。

根据一实施方式的多条移位时钟布线之中的多条进位时钟布线可单独(或分别)将设置在第一焊盘部110中的多个第一进位时钟焊盘连接至设置在第二焊盘部210中的多个第二进位时钟焊盘。

至少一条栅极驱动电源布线可将设置在第一焊盘部110中的至少一个第一栅极驱动电源焊盘电连接至设置在第二焊盘部210中的至少一个第二栅极驱动电源焊盘。

至少一条栅极公共电源布线可将设置在第一焊盘部110中的至少一个第一栅极公共电源焊盘电连接至设置在第二焊盘部210中的至少一个第二栅极公共电源焊盘。

像素驱动电源布线部分(或第三布线部分)可将第一焊盘部110的第一像素驱动电源焊盘部电连接至第二焊盘部210的第二像素驱动电源焊盘部。根据一实施方式的像素驱动电源布线部分可包括多条像素驱动电源布线450。多条像素驱动电源布线(或第三布线)450可单独(或分别)将设置在第一焊盘部110中的多个第一像素驱动电源焊盘连接至设置在第二焊盘部210中的多个第二像素驱动电源焊盘。

像素公共电源布线部分(或第四布线部分)可将第一焊盘部110的第一像素公共电源焊盘部电连接至第二焊盘部210的第二像素公共电源焊盘部。根据一实施方式的像素公共电源布线部分可包括多条像素公共电源布线470。多条像素公共电源布线(或第四布线)470可单独(或分别)将设置在第一焊盘部110中的多个第一像素公共电源焊盘连接至设置在第二焊盘部210中的多个第二像素公共电源焊盘。

根据一实施方式的布线部分400可进一步包括基准电源布线部分。

基准电源布线部分(或第五布线部分)可将第一焊盘部110的第一基准电源焊盘部电连接至第二焊盘部210的第二基准电源焊盘部。根据一实施方式的基准电源布线部分可包括多条基准电源布线490。多条基准电源布线(或第五布线)490可单独(或分别)将设置在第一焊盘部110中的多个第一基准电源焊盘连接至设置在第二焊盘部210中的多个第二基准电源焊盘。

根据本发明一实施方式的显示设备10可进一步包括驱动电路单元500。

驱动电路单元500可基于从显示驱动系统提供的数字视频数据和时序同步信号驱动设置在第一基板100上的像素P(或使像素P发光),以使显示区域AA显示对应于图像数据的图像。驱动电路单元500可连接至设置在第二基板200的后表面200b上的第三焊盘部230并且可向第三焊盘部230输出用于位于第一基板100上的像素P的驱动(或发光)的数据信号、栅极控制信号和驱动电源。例如,驱动电路单元500可具有小于第二基板200的尺寸,因而可被第二基板200覆盖并且可不暴露在第二基板200的外表面或第一基板100的外表面。

根据一实施方式的驱动电路单元500可包括柔性电路膜510、驱动集成电路(IC)530、印刷电路板(PCB)550和时序控制器570。

柔性电路膜510可连接至设置在第二基板200的后表面200b上的第三焊盘部230。根据一实施方式的柔性电路膜510可以是载带封装(TCP)或膜上芯片(COF)。例如,柔性电路膜510的一个边缘部分(或输出接合部分)可通过使用各向异性导电膜的膜附接工艺附接在设置于第二基板200上的第三焊盘部230上。柔性电路膜510的另一边缘部分(或输入接合部分)可通过使用各向异性导电膜的膜附接工艺附接在PCB 550上。

驱动IC 530可安装在柔性电路膜510上。驱动IC 530可接收从时序控制器570提供的子像素数据和数据控制信号,并且基于数据控制信号将子像素数据转换为模拟数据信号,以将模拟数据信号提供至相应数据线DL。例如,驱动IC 530可以是数据驱动IC或源极驱动IC。

根据一实施方式的驱动IC 530可通过使用从PCB 550提供的多个基准伽马电压产生多个灰度级电压,并且可从多个灰度级电压之中选择与子像素数据对应的灰度级电压,以输出数据信号。数据信号可经由柔性电路膜510的输出接合部分、第三焊盘部230、连线部分250、第二焊盘部210、布线部分400和第一焊盘部110提供至相应的数据线DL。

此外,驱动IC 530可通过使用多个基准伽马电压产生并输出像素P的驱动(或发光)所需的像素驱动电源和像素公共电源。例如,驱动IC 530可从多个基准伽马电压或多个灰度级电压之中选择并输出预定的基准伽马电压或预定的灰度级电压作为像素驱动电源和像素公共电源。

另外,驱动IC 530可基于设置在像素P的电路区域中的像素电路的驱动(或操作)附加地产生并输出基准电源。例如,驱动IC 530可从多个基准伽马电压或多个灰度级电压之中选择并输出预定的基准伽马电压或预定的灰度级电压作为基准电压。

像素驱动电源、像素公共电源和基准电源可具有不同的电压电平。像素驱动电源、像素公共电源和基准电源可经由柔性电路膜510的输出接合部分、第三焊盘部230、连线部分250、第二焊盘部210、布线部分400和第一焊盘部110分别提供至相应的像素驱动电源线PL、相应的像素公共电源线CPL和相应的基准电源线RL。

驱动IC 530可通过设置在第一基板100上的多条基准电源线RL感测设置在像素P中的驱动TFT的特征值,产生对应于感测值的感测原始数据并且将感测原始数据提供至时序控制器570。

PCB 550可连接至柔性电路膜510的另一边缘部分。PCB 550可在驱动电路单元500的元件之间传输信号和电源。

时序控制器570可安装在PCB 550上并且可通过设置在PCB 550上的用户连接器接收从显示驱动系统提供的数字视频数据和时序同步信号。或可选择地,时序控制器570可不安装在PCB 550上,而是可实现在显示驱动系统中或者可安装于连接在PCB 550与显示驱动系统之间的单独控制板上。

时序控制器570可基于时序同步信号排列数字视频数据,以产生与设置在显示区域AA中的像素布置结构匹配的像素数据并且可将产生的像素数据提供至驱动IC 530。

根据一实施方式,当像素P包括白色子像素SP时,时序控制器570可基于数字视频数据(即,要分别提供至相应像素P的红色输入数据、绿色输入数据和蓝色输入数据)提取白色像素数据,将基于提取的白色像素数据的偏移数据反映在红色输入数据、绿色输入数据和蓝色输入数据的每一个中,以计算红色像素数据、绿色像素数据和蓝色像素数据,并且根据像素布置结构排列所计算的红色像素数据、绿色像素数据和蓝色像素数据以及白色像素数据,以将排列后的像素数据提供至驱动IC 530。例如,时序控制器570可基于韩国专利申请公开No.10-2013-0060476号或10-2013-0030598中公开的数据转换方法将红色输入数据、绿色输入数据和蓝色输入数据转换为四色(例如,红色、绿色、蓝色和白色)数据。

时序控制器570可基于时序同步信号产生数据控制信号和栅极控制信号的每一个,基于数据控制信号控制驱动IC 530的驱动时序,并且基于栅极控制信号控制栅极驱动电路150的驱动时序。例如,时序同步信号可包括垂直同步信号、水平同步信号、数据使能信号和主时钟(或点时钟)。

根据一实施方式的数据控制信号可包括源极起始脉冲、源极移位时钟和源极输出信号。数据控制信号可经由柔性电路膜510的输入接合部分和柔性电路膜510提供至驱动IC530。

根据一实施方式的栅极控制信号可包括起始信号(或栅极起始脉冲)、多个移位时钟、正向驱动信号和反向驱动信号。在这种情况下,多个移位时钟可包括相位依次移位的多个扫描时钟以及相位依次移位的多个进位时钟。另外,根据一实施方式的栅极控制信号可进一步包括用于感测设置在像素P中的驱动TFT的特征值的外部感测线选择信号、外部感测复位信号和外部感测控制信号。栅极控制信号可经由柔性电路膜510的输入接合部分、柔性电路膜510、柔性电路膜510的输出接合部分、第三焊盘部230、连线部分250、第二焊盘部210、布线部分400和第一焊盘部110提供至栅极驱动电路150。

时序控制器570可在预定的外部感测时段期间基于外部感测模式驱动栅极驱动电路150和驱动IC 530的每一个,基于从驱动IC 530提供的感测原始数据(raw data)产生用于补偿每个像素P的驱动TFT的特征变化的补偿数据,并且基于产生的补偿数据调制像素数据。例如,时序控制器570可在与垂直同步信号的消隐时段(或垂直消隐时段)对应的每个外部感测时段,基于外部感测模式驱动栅极驱动电路150和驱动IC 530的每一个。例如,可在显示设备的通电过程、显示设备的断电过程、在长时间驱动之后将显示设备断电的过程、或者实时地或周期性地设定的帧的消隐时段中执行外部感测模式。

根据一实施方式的时序控制器570可基于外部感测模式将从驱动IC 530提供的每个像素P的感测原始数据存储在存储电路中。此外,在显示模式中,时序控制器570可基于存储在存储电路中的感测原始数据修正待提供至每个像素的像素数据并且可将修正后的像素数据提供至驱动IC 530。在此,每个像素的感测原始数据可包括与设置在相应子像素中的驱动TFT和自发光器件的每一个有关的依次变化信息(sequential variationinformation)。因此,在外部感测模式中,时序控制器570可感测设置在每个子像素中的驱动TFT的特征值(例如,阈值电压或迁移率)并且基于此,可修正待提供至每个子像素P的像素数据,由此最小化或防止由多个子像素SP的驱动TFT的特征值偏差导致的图像质量劣化。显示设备的外部感测模式可以是所属领域技术人员已知的技术,因而省略其详细描述。例如,根据本发明的显示设备可基于韩国专利申请公开No.10-2016-0093179、10-2017-0054654或10-2018-0002099中公开的感测模式来感测设置在每个子像素SP中的驱动TFT的特征值。

根据一实施方式的驱动电路单元500可进一步包括电源电路单元590。

电源电路单元590可安装在PCB 550上并且可通过使用从外部提供的输入电源产生用于在像素P上显示图像所需的各种源电压,以将产生的源电压提供至相应的电路。例如,电源电路单元590可产生并输出用于驱动时序控制器570和驱动IC 530的每一个所需的逻辑源电压、提供至驱动IC530的多个基准伽马电压、以及用于驱动栅极驱动电路150所需的至少一个栅极驱动电源和至少一个栅极公共电源。栅极驱动电源和栅极公共电源可具有不同的电压电平。

多个基准伽马电压的每一个可经由柔性电路膜510的输入接合部分和柔性电路膜510提供至驱动IC 530。至少一个栅极驱动电源和至少一个栅极公共电源的每一个可经由柔性电路膜510的输入接合部分、柔性电路膜510、柔性电路膜510的输出接合部分、第三焊盘部230、连线部分250、第二焊盘部210、布线部分400和第一焊盘部110提供至栅极驱动电路150。

图5是图3中所示的区域“B”的放大图,其是用于描述设置在第一基板上的像素的示图。

参照图3至图5,根据本发明的第一基板100可包括多条数据线DLo和DLe、多条栅极线GLo和GLe、多条像素驱动电源线PL、多条像素公共电源线CPL、多个像素P、公共电极CE(请参见图7)、多个公共电源接触部分CPCP、栅极控制线组GCL、栅极驱动电路150和第一焊盘部110。

多条数据线DLo和DLe可沿第二方向Y长长地延伸并且可沿第一方向X彼此分隔开预定间隔地设置在第一基板100的显示区域AA中。例如,在多条数据线DLo和DLe中,奇数数据线DLo可沿第二方向Y设置在布置于第一基板100上的多个像素区域PA的每一个的第一边缘部分处,偶数数据线DLe可沿第二方向Y设置在布置于第一基板100上的多个像素区域PA的每一个的第二边缘部分处。在此,相对于第一方向X,多个像素区域PA的每一个的第一边缘部分可以是相应像素区域PA的左边缘部分,并且多个像素区域PA的每一个的第二边缘部分可以是相应像素区域PA的右边缘部分。

多条栅极线GLo和GLe可沿第一方向X长长地延伸并且可沿第二方向Y彼此分隔开预定间隔地设置在第一基板100的显示区域AA中。例如,在多条栅极线GLo和GLe中,奇数栅极线GLo可沿第一方向X设置在布置于第一基板100上的多个像素区域PA的每一个的第三边缘部分处,偶数栅极线GLe可沿第一方向X设置在布置于第一基板100上的多个像素区域PA的每一个的第四边缘部分处。在此,相对于第二方向Y,多个像素区域PA的每一个的第三边缘部分可以是相应像素区域PA的上边缘部分,并且多个像素区域PA的每一个的第四边缘部分可以是相应像素区域PA的下边缘部分。

多条像素驱动电源线PL可沿第二方向Y长长地延伸并且可沿第一方向X彼此分隔开预定间隔地设置在第一基板100的显示区域AA中。例如,在多条像素驱动电源线PL中,奇数像素驱动电源线PL可设置在相对于第一方向X的奇数像素区域PA的第一边缘部分处,偶数像素驱动电源线PL可设置在相对于第一方向X的偶数像素区域PA的第二边缘部分处。

多条像素驱动电源线PL中的两条相邻的像素驱动电源线PL可连接至设置在沿第二方向Y布置的每个像素区域PA中的多条电源共用线PSL。例如,多条像素驱动电源线PL可通过多条电源共用线PSL彼此电连接,因而可具有梯子形结构(ladder structure)或网状结构。多条像素驱动电源线PL可具有梯子形结构或网状结构,因而可防止或最小化由多条像素驱动电源线PL的每一条的线电阻导致的像素驱动电源的压降(IR降)。因此,根据本发明的显示设备10可防止或最小化由提供至每个像素P的像素驱动电源的偏差导致的图像质量的劣化。

多条电源共用线PSL的每一条可与第一方向X平行地从相邻的像素驱动电源线PL分支并且可设置在每个像素区域PA的中间区域中。

多条像素公共电源线CPL可沿第二方向Y长长地延伸并且可沿第一方向X彼此分隔开预定间隔地设置在第一基板100的显示区域AA中。例如,多条像素公共电源线CPL的每一条可设置在相对于第一方向X的偶数像素区域PA的第一边缘部分处。

多个像素P可分别设置在第一基板100的显示区域AA中的被限定为具有相等尺寸的多个像素区域PA中。

多个像素P的每一个可包括至少三个子像素。例如,如图2中所示,多个像素P的每一个可包括第一至第四子像素SP1至SP4。

参照图2和图5,第一至第四子像素SP1至SP4的每一个可包括像素电路PC和发光器件ED。

根据一实施方式的像素电路PC可设置在像素区域PA的电路区域CA中并且可连接至与其相邻的栅极线GLo和GLe、与其相邻的数据线DLo和DLe、以及像素驱动电源线PL。例如,设置在第一子像素SP1中的像素电路PC可连接至奇数数据线DLo和奇数栅极线GLo,设置在第二子像素SP2中的像素电路PC可连接至偶数数据线DLe和奇数栅极线GLo,设置在第三子像素SP3中的像素电路PC可连接至奇数数据线DLo和偶数栅极线GLe,并且设置在第四子像素SP4中的像素电路PC可连接至偶数数据线DLe和偶数栅极线GLe。

第一至第四子像素SP1至SP4的每一个的像素电路PC可响应于从相应栅极线GLo和GLe提供的扫描信号采样从相应数据线DLo和DLe提供的数据信号,并且可基于采样的数据信号控制从像素驱动电源线PL流到发光器件ED的电流。例如,像素电路PC可通过使用至少两个TFT和至少一个电容器采样数据信号并且可基于采样的数据信号控制流入发光器件ED的电流。

第一至第四子像素SP1至SP4的每一个的像素电路PC可通过半导体制造工艺实现为像素驱动芯片,设置在相应像素区域PA的电路区域CA中并且连接至与其相邻的栅极线GLo和GLe、与其相邻的数据线DLo和DLe、以及像素驱动电源线PL。例如,像素驱动芯片可以是最小单元微芯片(minimum-unit microchip)或一个芯片组并且可以是包括两个或更多个晶体管以及一个或多个电容器并且具有细微尺寸的半导体封装器件。这种像素驱动芯片可响应于从相应栅极线GLo和GLe提供的扫描信号采样从相应数据线DLo和DLe提供的数据信号,并且可基于采样的数据信号控制从像素驱动电源线PL流到发光器件ED的电流。

发光器件ED可设置在像素区域PA的发光区域EA中,电连接至像素电路PC并且电连接至公共电极CE。发光器件ED可利用从像素电路PC流到公共电极CE的电流发光。例如,发光器件ED可基于顶部发光型发射光并且可将光照射到第一基板100的第一表面上方的部分上,但不限于此。

根据一实施方式的发光器件ED可包括自发光器件。例如,发光器件ED可包括有机发光器件或无机发光器件。无机发光器件可包括半导体发光二极管、微型发光二极管或量子点发光二极管。例如,当发光器件ED是无机发光器件时,发光器件ED可具有1μm至100μm的尺寸,但不限于此。

根据一实施方式的发光器件ED可发射红色光、绿色光、蓝色光和白色光中的一种光。例如,第一至第四子像素SP1至SP4的每一个的发光器件ED可实现为发射白色光,但不限于此。

再次参照图3至图5,公共电极CE可设置在第一基板100的显示区域AA中并且可电连接至多个像素P的每一个的发光器件ED。例如,公共电极CE可设置在第一基板100的显示区域AA中的、除了设置在第一基板100中的第一焊盘部110以外的区域中。

根据一实施方式的公共电极CE可包括透射从多个像素P的每一个的发光器件ED发射的光的透明导电材料。例如,透明导电材料可以是氧化铟锡(ITO)或氧化铟锌(IZO),但不限于此。

多个公共电源接触部分CPCP的每一个可设置在分别与多条像素公共电源线CPL交叠的多个像素P中的两个相邻像素P之间,并且可将公共电极CE电连接至多条像素公共电源线CPL中的相应像素公共电源线CPL。相对于第二方向Y,根据一实施方式的多个公共电源接触部分CPCP的每一个可在多个像素P之间的部分处或在多个像素P之间的边界部分处电连接至多条像素公共电源线CPL中的相应像素公共电源线CPL,并且可电连接至公共电极CE的一部分,因而可将公共电极CE电连接至多条像素公共电源线CPL中的相应像素公共电源线CPL。

多个公共电源接触部分CPCP的每一个可设置在多个像素P中的两个相邻像素P之间,以将公共电极CE电连接至多条像素公共电源线CPL中的相应像素公共电源线CPL,因而可防止或最小化由公共电极CE的表面电阻导致的像素公共电源的压降(IR降)。因此,根据本发明的显示设备10可防止或最小化由提供至布置在显示区域AA中的每个像素P的像素公共电源的偏差导致的图像质量的劣化。

栅极控制线组GCL可包括在第一基板100的显示区域AA中的栅极驱动电路150和多条栅极控制线。

根据一实施方式的栅极控制线组GCL可包括起始信号线、多条移位时钟线、至少一条栅极驱动电源线、和至少一条栅极公共电源线。栅极控制线组GCL的这些线可沿第二方向Y长长地延伸并且可沿第一方向X彼此分隔开预定间隔地设置在第一基板100的显示区域AA中。例如,栅极控制线组GCL的每条线可沿第一方向X设置在一个或多个像素P之间。

栅极驱动电路150可设置在第一基板100的显示区域AA中。因此,因为栅极驱动电路150设置在第一基板100的显示区域AA中,所以最外侧像素区域PAo的中心部分与第一基板100的每个外表面OS之间的第二间隔D2可以是相邻像素区域PA之间的第一间隔(或像素间距)D1的一半或更小。例如,当栅极驱动电路150不设置在第一基板100的显示区域AA中而是设置在最外侧像素区域PAo与第一基板100的外表面OS之间时,由于栅极驱动电路150占据的尺寸(或宽度),第二间隔D2不会是第一间隔D1的一半或更小。相应地,在本发明一实施方式中,因为栅极驱动电路150设置在第一基板100的显示区域AA内,所以第二间隔D2可实现为第一间隔D1的一半或更小。

参照图5和图6,根据一实施方式的栅极驱动电路150可利用移位寄存器实现,移位寄存器包括多个级电路单元1501至150m。

多个级电路单元1501至150m的每一个可沿第一方向X彼此分隔地设置在第一基板100的第一表面100a的每个水平行中,并且可沿第二方向Y彼此附属连接。多个级电路单元1501至150m的每一个可响应于通过第一焊盘部110和栅极控制线组GCL提供的栅极控制信号按预定顺序产生扫描信号,并且可将扫描信号提供至栅极线GL。

根据一实施方式的多个级电路单元1501至150m的每一个可包括多个分支电路1511至151n和分支网(branch network)153。

多个分支电路1511至151n可通过分支网153选择性地连接至栅极控制线组GCL的线并且可通过分支网153彼此电连接。多个分支电路1511至151n的每一个可基于通过栅极控制线组GCL的相应线和分支网153提供的栅极控制信号以及在分支网153之间传输的信号产生扫描信号,并且可将扫描信号提供至相应栅极线GL。

多个分支电路1511至151n的每一个可包括构成级电路单元1501至150m之一的多个TFT中的至少一个TFT。多个分支电路1511至151n的每一个可在第一基板100的每个水平行中设置在两个相邻像素P之间的电路区域中或者设置在两个像素P之间的电路区域中,但不限于此,基于构成级电路单元1501至150m的每一个的TFT的数量和设置在一个水平行中的像素P的数量,多个分支电路1511至151n的每一个可设置在一个或多个像素P之间的电路区域中。

分支网153可设置在第一基板100的每个水平行中并且可将多个分支电路1511至151n电连接。根据一实施方式的分支网153可包括网线和多个控制节点。

多个控制节点可设置在第一基板100的每个水平行中并且可选择性地连接至一个水平行中的多个分支电路1511至151n。例如,多个控制节点可设置在布置于第一基板100的每个水平行中的像素区域之中的上边缘区域(或下边缘区域)中。

网线可选择性地连接至设置在第一基板100中的栅极控制线组GCL的线并且可选择性地连接至多个分支电路1511至151n。例如,网线可将通过栅极控制线组GCL的线提供的栅极控制信号传输至相应的分支电路1511至151n并且可在多个分支电路1511至151n之间传输信号。

参照图3至图5,第一焊盘部110可设置在第一基板100的第一表面之中的与第一方向X平行的第一边缘部分处。第一焊盘部110可设置在位于第一基板100的第一边缘部分处的每个最外侧像素区域PAo的第三边缘部分处。相对于第二方向Y,第一焊盘部110的端部可与每个最外侧像素区域PAo的端部交叠或对齐。因此,第一焊盘部110可包括(或设置)在位于第一基板100的第一边缘部分处的每个最外侧像素区域PAo中,因而在第一基板100中不会形成或不会存在基于第一焊盘部110的非显示区域(或边框区域)。

第一焊盘部110可包括多个第一焊盘,多个第一焊盘沿第一方向X彼此平行地设置在第一基板100的第一边缘部分上。多个第一焊盘可划分(或分类)为多个第一数据焊盘DP1、多个第一栅极焊盘GP1、多个第一像素驱动电源焊盘PPP1、和多个第一像素公共电源焊盘CPP1。

根据一实施方式的第一焊盘部110可包括第一数据焊盘部、第一栅极焊盘部、第一像素驱动电源焊盘部和第一像素公共电源焊盘部。

第一数据焊盘部可包括多个第一数据焊盘DP1。多个第一数据焊盘DP1的每一个可单独(或分别)连接至设置在第一基板100上的多条数据线DLo和DLe的每一条的一端。

第一数据焊盘部可连接至设置在布线部分400中的数据布线部分。设置在第一数据焊盘部中的多个第一数据焊盘DP1的每一个可单独(或分别)连接至设置在布线部分400中的多条数据布线410的每一条的一端。因此,设置在第一基板100上的多条数据线DLo和DLe的每一条可通过多个第一数据焊盘DP1中的相应第一数据焊盘DP1电连接至多条数据布线410中的相应数据布线410。

第一栅极焊盘部包括多个第一栅极焊盘GP1。多个第一栅极焊盘GP1的每一个可单独(或分别)连接至设置在第一基板100上的栅极控制线组GCL中包括的栅极控制线之中的相应栅极控制线的一端。

第一栅极焊盘部连接至设置在布线部分400中的栅极布线部分。设置在第一栅极焊盘部中的多个第一栅极焊盘GP1的每一个可单独(或分别)连接至设置在布线部分400中的多条布线之中的多条栅极布线430的每一条的一端。因此,设置在第一基板100上的栅极控制线组GCL中包括的每条线可通过多个第一栅极焊盘GP1之中的相应第一栅极焊盘GP1电连接至多条栅极布线430中的相应栅极布线430。

根据一实施方式的多个第一栅极焊盘GP1可划分(或分类)为第一起始信号焊盘、多个第一移位时钟焊盘、至少一个第一栅极驱动电源焊盘、和至少一个第一栅极公共电源焊盘。

第一起始信号焊盘可电连接至设置在布线部分400的栅极布线部分中的起始信号布线。因此,设置在第一基板100上的起始信号线可通过第一起始信号焊盘电连接至起始信号布线。

多个第一移位时钟焊盘的每一个可电连接至设置在布线部分400的栅极布线部分中的多条移位时钟布线中的相应移位时钟布线。因此,设置在第一基板100上的多条移位时钟线的每一条可通过多个第一移位时钟焊盘中的相应第一移位时钟焊盘电连接至多条移位时钟布线中的相应移位时钟布线。

至少一个第一栅极驱动电源焊盘可电连接至设置在布线部分400的栅极布线部分中的至少一条栅极驱动电源布线。因此,设置在第一基板100上的至少一条第一栅极驱动电源线可通过至少一个第一栅极驱动电源焊盘电连接到至少一条栅极驱动电源布线。

至少一个第一栅极公共电源焊盘可电连接至设置在布线部分400的栅极布线部分中的至少一条栅极公共电源布线。因此,设置在第一基板100上的至少一条第一栅极公共电源线可通过至少一个第一栅极公共电源焊盘电连接到至少一条栅极公共电源布线。

第一像素驱动电源焊盘部可包括多个第一像素驱动电源焊盘PPP1。多个第一像素驱动电源焊盘PPP1的每一个可单独(或分别)连接至设置在第一基板100上的多条像素驱动电源线PL之中的相应像素驱动电源线PL的一端。

第一像素驱动电源焊盘部可电连接至设置在布线部分400中的像素驱动电源布线部分。设置在第一像素驱动电源焊盘部中的多个第一像素驱动电源焊盘PPP1的每一个可单独(或分别)连接至设置在布线部分400中的多条像素驱动电源布线450之中的相应像素驱动电源布线450的一端。因此,设置在第一基板100上的多条像素驱动电源线PL的每一条可通过多个第一像素驱动电源焊盘PPP1之中的相应第一像素驱动电源焊盘PPP1单独(或分别)连接至多条像素驱动电源布线450之中的相应像素驱动电源布线450的一端。

第一像素公共电源焊盘部可包括多个第一像素公共电源焊盘CPP1。多个第一像素公共电源焊盘CPP1的每一个可单独(或分别)连接至设置在第一基板100上的多条像素公共电源线CPL之中的相应像素公共电源线CPL的一端。

第一像素公共电源焊盘部可电连接至设置在布线部分400中的像素公共电源布线部分。设置在第一像素公共电源焊盘部中的多个第一像素公共电源焊盘CPP1的每一个可单独(或分别)连接至设置在布线部分400中的多条像素公共电源布线470之中的相应像素公共电源布线470的一端。因此,设置在第一基板100上的多条像素公共电源线CPL的每一条可通过多个第一像素公共电源焊盘CPP1之中的相应第一像素公共电源焊盘CPP1单独(或分别)连接至多条像素公共电源布线470之中的相应像素公共电源布线470的一端。

根据一实施方式的第一焊盘部110可包括沿第一方向X按照一个第一像素驱动电源焊盘PPP1、两个第一数据焊盘DP1、一个第一栅极焊盘GP1、一个第一像素公共电源焊盘CPP1、两个第一数据焊盘DP1和一个第一像素驱动电源焊盘PPP1的顺序布置的多个焊盘组PG。多个焊盘组PG的每一个可连接至沿第一方向X设置的两个相邻像素P。例如,多个焊盘组PG可包括第一焊盘组PG1和第二焊盘组PG2,第一焊盘组PG1包括沿第一方向X连续设置在奇数像素区域PA中的一个第一像素驱动电源焊盘PPP1、两个第一数据焊盘DP1和一个第一栅极焊盘GP1,第二焊盘组PG2包括沿第一方向X连续设置在偶数像素区域PA中的一个第一像素公共电源焊盘CPP1、两个第一数据焊盘DP1和一个第一像素驱动电源焊盘PPP1。

根据本发明的第一基板100可进一步包括多条辅助电源线SPL和多个辅助电源接触部分SPCP。

多条辅助电源线SPL的每一条可沿第二方向Y长长地延伸并且可与多条像素公共电源线CPL中的相应像素公共电源线CPL相邻设置。多条辅助电源线SPL的每一条可电连接至相邻的像素公共电源线CPL而不电连接至第一像素公共电源焊盘CPP1,并且可通过相邻的像素公共电源线CPL被提供像素公共电源。为此,根据本发明的第一基板100可进一步包括多个线连接图案LCP,多个线连接图案LCP将彼此相邻的像素公共电源线CPL和辅助电源线SPL电连接。

多个线连接图案LCP的每一个可设置在第一基板100上,使得线连接图案LCP与彼此相邻的像素公共电源线CPL和辅助电源线SPL彼此交叉并且可通过使用线跳接(jumping)结构将彼此相邻的像素公共电源线CPL和辅助电源线SPL电连接。例如,多个线连接图案LCP的每一个的一侧可通过形成在辅助电源线SPL上的绝缘层中的第一线接触孔电连接至辅助电源线SPL的一部分,并且多个线连接图案LCP的每一个的另一侧可通过形成在像素公共电源线CPL上的绝缘层中的第二线接触孔电连接至像素公共电源线CPL的一部分。

多个辅助电源接触部分SPCP的每一个可设置在分别与多条辅助电源线SPL交叠的多个像素P之间并且可将公共电极CE和多条辅助电源线SPL的每一条电连接。相对于第二方向Y,根据一实施方式的多个辅助电源接触部分SPCP的每一个可在多个像素P之间的部分处或在多个像素P之间的边界部分处电连接至多条辅助电源线SPL中的相应辅助电源线SPL,并且可电连接至公共电极CE的一部分,因而可将公共电极CE电连接至多条辅助电源线SPL的每一条。因此,公共电极CE可通过多个辅助电源接触部分SPCP的每一个附加连接至多条辅助电源线SPL的每一条。因此,根据本发明的显示设备10可防止或最小化由提供至布置在显示区域AA中的每个像素P的像素公共电源的偏差导致的图像质量的劣化。此外,在根据本发明的显示设备10中,尽管没有额外设置(或形成)与多条辅助电源线SPL的每一条连接的第一像素公共电源焊盘CPP1,但像素公共电源可提供至多个像素区域PA的每一个中的公共电极CE。

根据本发明的显示设备10可进一步包括多条基准电源线RL。

多条基准电源线RL可沿第二方向Y长长地延伸并且可沿第一方向X彼此分隔开预定间隔地设置在第一基板100的显示区域AA中。多条基准电源线RL的每一条可设置在沿第二方向Y布置的每个像素区域PA的中心区域。例如,多条基准电源线RL的每一条可设置在每个像素区域PA中的奇数数据线DLo和偶数数据线DLe之间。

多条基准电源线RL的每一条可被每个像素区域PA中的沿第一方向X相邻的两个子像素((SP1、SP2)、(SP3、SP4))共用。为此,多条基准电源线RL的每一条可包括基准分支线RDL。

基准分支线RDL可分支(或突出)到每个像素区域PA中的沿第一方向X相邻的两个子像素((SP1、SP2)、(SP3、SP4))并且可电连接至两个相邻子像素((SP1、SP2)、(SP3、SP4))。

根据本发明的第一焊盘部110可进一步包括第一基准电源焊盘部。

第一基准电源焊盘部可包括多个第一基准电源焊盘RPP1。多个第一基准电源焊盘RPP1的每一个可单独(或分别)连接至多条基准电源线RL中的相应基准电源线RL的一端。例如,多个第一基准电源焊盘RPP1的每一个可设置在位于多个最外侧像素区域PAo的每一个中的两个第一数据焊盘DP1之间,但不限于此。

第一基准电源焊盘部可连接至位于布线部分400中的基准电源布线部分。设置在第一基准电源焊盘部中的多个第一基准电源焊盘RPP1的每一个可单独(或分别)连接至设置在布线部分400中的多条基准电源布线490中的相应基准电源布线490的一端。因此,设置在第一基板100上的多条基准电源线RL的每一条可通过多个第一基准电源焊盘RPP1中的相应第一基准电源焊盘RPP1电连接至多条基准电源布线490中的相应基准电源布线490。

可选择地,多条基准电源线RL、基准分支线RDL、多个第一基准电源焊盘RPP1和多条基准电源布线490均可基于像素电路PC的电路构造省略。

图7是图解图3和图5中所示的一个像素的电路图,其是描述子像素的像素电路的示图。在描述图7时,与图3至图6的元件相同或对应的元件由相似的参考标记表示,并且在下面省略或将简要给出其重复描述。

参照图7,根据本发明的像素P可包括第一至第四子像素SP1至SP4,第一至第四子像素SP1至SP4的每一个包括像素电路PC、像素电极PE和发光器件ED。

设置在像素P的第一至第四子像素SP1至SP4的每一个中的像素电路PC可设置在电路区域中并且可连接至相邻的栅极线GLo和GLe、相邻的数据线DLo和DLe、基准电源线RL和像素驱动电源线PL。像素电路PC可响应于通过相邻的栅极线GLo和GLe提供的扫描信号向发光器件ED提供数据电流,从而使发光器件ED发光,其中数据电流对应于通过相邻的数据线DLo和DLe提供的数据信号与通过基准电源线RL提供的基准电压之间的差电压。

根据一实施方式的像素电路PC可包括第一开关TFT Tsw1、第二开关TFT Tsw2、存储电容器Cst和驱动TFT Tdr。在下面的描述中,薄膜晶体管可称为TFT。

第一开关TFT Tsw1、第二开关TFT Tsw2和驱动TFT Tdr中的至少一个可以是N型或P型TFT。第一开关TFT Tsw1、第二开关TFT Tsw2和驱动TFT Tdr中的至少一个可以是非晶硅(a-Si)TFT、多晶硅(poly-Si)TFT、氧化物TFT或有机TFT。例如,在像素电路PC中,第一开关TFT Tsw1、第二开关TFT Tsw2和驱动TFT Tdr中的一些TFT可以是具有包括低温多晶硅(LTPS)的半导体层(或有源层)的TFT,低温多晶硅具有优异的响应特征,并且第一开关TFTTsw1、第二开关TFT Tsw2和驱动TFT Tdr中的其他TFT可以是具有包括氧化物的半导体层(或有源层)的TFT,氧化物的截止电流特征出色。第一开关TFT Tsw1、第二开关TFT Tsw2和驱动TFT Tdr可具有不同的尺寸(或沟道尺寸)。例如,驱动TFT Tdr可具有比第一开关TFTTsw1和第二开关TFT Tsw2的每一个大的尺寸,并且第二开关TFT Tsw2可具有比第一开关TFT Tsw1大的尺寸。

第一开关TFT Tsw1可包括与相邻的栅极线GLo和GLe连接的栅极电极、与相邻的数据线DLo和DLe连接的第一源极/漏极电极、以及与第一节点(或驱动TFT Tdr的栅极电极)n1连接的第二源极/漏极电极。第一开关TFT Tsw1可利用通过相应的栅极线GLo和GLe提供的扫描信号导通并且可将通过相应的数据线DLo和DLe提供的数据信号传输至第一节点n1(即,驱动TFT Tdr的栅极电极n1)。

根据一实施方式,设置在第一子像素SP1和第二子像素SP2的每一个的像素电路PC中的第一开关TFT Tsw1的栅极电极可连接至奇数栅极线GLo,并且设置在第三子像素SP3和第四子像素SP4的每一个的像素电路PC中的第一开关TFT Tsw1的栅极电极可连接至偶数栅极线GLe。设置在第一子像素SP1和第三子像素SP3的每一个的像素电路PC中的第一开关TFTTsw1的第一源极/漏极电极可连接至奇数数据线DLo,并且设置在第二子像素SP2和第四子像素SP4的每一个的像素电路PC中的第一开关TFT Tsw1的第一源极/漏极电极可连接至偶数数据线DLe。

第二开关TFT Tsw2可包括与相邻的栅极线GLo和GLe连接的栅极电极、与相邻的基准电源线RL连接的第一源极/漏极电极、以及与第二节点(或驱动TFT Tdr的源极电极)n2连接的第二源极/漏极电极。第二开关TFT Tsw2可利用通过相应的栅极线GLo和GLe提供的扫描信号导通并且可将通过相应的基准分支线RDL和基准电源线RL提供的基准电压传输至驱动TFT Tdr的源极电极n2。

根据一实施方式,设置在第一子像素SP1和第二子像素SP2的每一个的像素电路PC中的第二开关TFT Tsw2的栅极电极可连接至奇数栅极线GLo,并且设置在第三子像素SP3和第四子像素SP4的每一个的像素电路PC中的第二开关TFT Tsw2的栅极电极可连接至偶数栅极线GLe。设置在第一至第四子像素SP1至SP4的每一个的像素电路PC中的第二开关TFTTsw2的第一源极/漏极电极可通过相应的基准分支线RDL连接至相邻的基准电源线RL。

提供至第一开关TFT Tsw1的栅极电极的扫描信号和提供至第二开关TFT Tsw2的栅极电极的扫描信号可以是相同的信号。例如,第一开关TFT Tsw1的栅极电极和第二开关TFT Tsw2的栅极电极可连接至相同的栅极线GLo和GLe。因此,设置在第一子像素SP1和第二子像素SP2的每一个的像素电路PC中的第一开关TFT Tsw1和第二开关TFT Tsw2可利用通过奇数栅极线GLo提供的扫描信号同时导通或截止。类似地,设置在第三子像素SP2和第四子像素SP4的每一个的像素电路PC中的第一开关TFT Tsw1和第二开关TFT Tsw2可利用通过偶数栅极线GLe提供的扫描信号同时导通或截止。

可选择地,提供至第一开关TFT Tsw1的栅极电极的扫描信号和提供至第二开关TFT Tsw2的栅极电极的扫描信号可以是不同的信号。例如,第一开关TFT Tsw1的栅极电极和第二开关TFT Tsw2的栅极电极可连接至不同的栅极线GLo和GLe。

根据一实施方式的奇数栅极线GLo和偶数栅极线GLe均可包括第一栅极线和第二栅极线。

奇数栅极线GLo的第一栅极线可连接至设置在第一子像素SP1和第二子像素SP2的每一个的像素电路PC中的第一开关TFT Tsw1的栅极电极,并且奇数栅极线GLo的第二栅极线可连接至设置在第一子像素SP1和第二子像素SP2的每一个的像素电路PC中的第二开关TFT Tsw2的栅极电极。

偶数栅极线GLe的第一栅极线可连接至设置在第三子像素SP3和第四子像素SP4的每一个的像素电路PC中的第一开关TFT Tsw1的栅极电极,并且偶数栅极线GLe的第二栅极线可连接至设置在第三子像素SP3和第四子像素SP4的每一个的像素电路PC中的第二开关TFT Tsw2的栅极电极。

因此,设置在第一子像素SP1和第二子像素SP2的每一个的像素电路PC中的第一开关TFT Tsw1和第二开关TFT Tsw2可利用通过奇数栅极线GLo的第一栅极线和第二栅极线提供的相同的扫描信号同时导通或截止,或者可利用通过奇数栅极线GLo的第一栅极线和第二栅极线提供的不同的扫描信号单独导通或截止。类似地,设置在第三子像素SP3和第四像素SP4的每一个的像素电路PC中的第一开关TFT Tsw1和第二开关TFT Tsw2可利用通过偶数栅极线GLe的第一栅极线和第二栅极线提供的相同的扫描信号同时导通或截止,或者可利用通过偶数栅极线GLe的第一栅极线和第二栅极线提供的不同的扫描信号单独导通或截止。例如,在第一至第四子像素SP1至SP4的每一个中,第一开关TFT Tsw1可基于通过第一栅极线提供的第一扫描信号导通,第二开关TFT Tsw2可基于通过第二栅极线提供的第二扫描信号导通。

设置在第一至第四子像素SP1至SP4的每一个的像素电路PC中的第二开关TFTTsw2可基于外部感测模式在数据充电时段(或区段)期间通过基准电源线RL向驱动TFT Tdr的源极节点n2传输基准电压,并且可在像素P的感测时段(或区段)期间将驱动TFT Tdr的源极节点n2中流动的电流传输至基准电源线RL,在这种情况下,驱动电路单元可感测提供至基准电源线RL的电流,以产生用于补偿驱动TFT Tdr的特征变化的补偿数据,并且驱动电路单元可基于产生的补偿数据调制像素数据。例如,驱动TFT Tdr的特征变化可包括阈值电压和/或迁移率的偏移。

存储电容器Cst可设置在驱动TFT Tdr的栅极节点n1和源极节点n2之间的交叠区域中。存储电容器Cst可包括与驱动TFT Tdr的栅极电极连接的第一电容器电极、与驱动TFTTdr的源极电极连接的第二电容器电极、以及形成在第一电容器电极与第二电容器电极之间的交叠区域中的介电层。存储电容器Cst可被充入驱动TFT Tdr的栅极节点n1和源极节点n2之间的差电压,然后可基于充入的电压使驱动TFT Tdr导通或截止。

驱动TFT Tdr可包括与第一开关TFT Tsw1的第二源极/漏极电极和存储电容器Cst的第一电容器电极连接的栅极电极(或栅极节点)n1;与第二开关TFT Tsw2的第二源极/漏极电极、存储电容器Cst的第二电容器电极和像素电极PE共同连接的源极电极(或源极节点);以及与相邻的像素驱动电源线PL连接的漏极电极(或漏极节点)。

设置在第一至第四子像素SP1至SP4的每一个的像素电路PC中的驱动TFT Tdr的漏极电极可通过电源共用线PSL连接至相邻的像素驱动电源线PL。电源共用线PSL可与第一方向X平行地从与其相邻的相邻像素驱动电源线PL分支并且可设置在像素P的中心区域中。驱动TFT Tdr可基于存储电容器Cst的电压导通并且可控制从像素驱动电源线PL流动到发光器件ED的电流量。

分别设置在第一至第四子像素SP1至SP4的像素电路PC中的驱动TFT Tdr可基于相应发光器件ED的发光效率而具有不同的尺寸(或沟道尺寸)。例如,第一子像素(或红色子像素)SP1的驱动TFT Tdr可具有比第二至第四子像素SP2至SP4的每一个的驱动TFT Tdr大的尺寸,第四子像素(或绿色子像素)SP4的驱动TFT Tdr可具有比第二子像素SP2和第三子像素SP2和SP3的每一个的驱动TFT Tdr大的尺寸,并且第二子像素(或蓝色子像素)SP2的驱动TFT Tdr可具有比第三子像素(或白色子像素)SP3的驱动TFT Tdr大的尺寸。

可选择地,在第一至第四子像素SP1至SP4的每一个中,包括第一开关TFT Tsw1、第二开关TFT Tsw2、存储电容器Cst和驱动TFT Tdr的像素电路PC可实现为像素驱动芯片,设置在相应像素区域PA的电路区域CA中,并且连接至与其相邻的栅极线GLo和GLe、与其相邻的数据线DLo和DLe、以及像素驱动电源线PL。这种像素驱动芯片可响应于从相应栅极线GLo和GLe提供的扫描信号采样从相应数据线DLo和DLe提供的数据信号并且可将与采样的数据信号对应的数据电流提供至像素电极PE。

像素电极PE可设置在第一至第四子像素SP1至SP4的每一个的发光区域中并且可连接至设置在相应像素电路PC中的驱动TFT Tdr的漏极电极。

基于显示设备10的分辨率,像素电极PE可设置在相应子像素区域中而不与像素电路PC交叠或者与像素电路PC的一部分或全部交叠。

根据一实施方式的像素电极PE可设置在子像素区域中而不与像素电路PC交叠。例如,像素电极PE可靠近像素P的中心部分设置在子像素区域中。

根据另一实施方式,像素电极PE可设置在子像素区域中并与像素电路PC的一部分交叠。例如,像素电极PE可靠近像素P的中心部分设置在子像素区域中并与像素电路PC的一部分交叠。

根据另一实施方式,像素电极PE可设置在子像素区域中并与整个像素电路PC交叠。例如,像素电极PE可设置在整个子像素区域中并与整个像素电路PC交叠。

发光器件ED可设置在像素电极PE上并且可电连接至像素电极PE。此外,发光器件ED可电连接至公共电极。就是说,发光器件ED可设置在像素电极PE与公共电极之间。发光器件ED可利用从相应像素电路PC提供的数据电流发光。发光器件ED可利用从相应像素电路PC提供的数据电流发光并且可将光照射到第一基板100的第一表面上方的部分上。根据一实施方式的发光器件ED可包括如上所述的自发光器件。

可选择地,在根据一实施方式的像素电路PC中,可基于像素P的驱动(或操作)方式省略第二开关TFT Tsw2,在这种情况下,也可省略设置在第一基板100上的基准电源线RL。

图8是图解图4中所示的第二基板的示图,图9是图8中所示的区域“C”的放大图。在描述图8和图9时,在下面省略或将简要给出对与图3至图7的元件相同或对应的元件的重复描述。

参照图3、图5、图8和图9,根据本发明的第二基板200可包括第二焊盘部210。

第二焊盘部210可设置在第二基板200的第二表面200b之中的与第一方向X平行的第一边缘部分处,并与设置在第一基板100上的第一焊盘部110交叠。第二焊盘部210可包括多个第二焊盘,多个第二焊盘沿第一方向X彼此平行地设置在第二基板200的第一边缘部分处。多个第二焊盘可划分(或分类)为多个第二数据焊盘DP2、多个第二栅极焊盘GP2、多个第二像素驱动电源焊盘PPP2、和多个第二像素公共电源焊盘CPP2。

根据一实施方式的第二焊盘部210可包括第二数据焊盘部、第二栅极焊盘部、第二像素驱动电源焊盘部和第二像素公共电源焊盘部。

第二数据焊盘部可通过布线部分400电连接至第一焊盘部110的第一数据焊盘部。

根据一实施方式的第二数据焊盘部可包括多个第二数据焊盘DP2。多个第二数据焊盘DP2的每一个可设置成单独(或分别)与设置在第一基板100的第一焊盘部110中的多个第一数据焊盘DP1中的相应第一数据焊盘DP1交叠。根据一实施方式的多个第二数据焊盘DP2的每一个可通过设置在布线部分400中的多条布线之中的多条数据布线410中的相应数据布线410,单独(或分别)连接至多个第一数据焊盘DP1中的相应第一数据焊盘DP1。因此,多个第二数据焊盘DP2的每一个可通过相应数据布线410和相应第一数据焊盘DP1电连接至相应数据线DLo和DLe。

第二栅极焊盘部可通过布线部分400电连接至第一焊盘部110的第一栅极焊盘部。

根据一实施方式的第二栅极焊盘部可包括多个第二栅极焊盘GP2。多个第二栅极焊盘GP2的每一个可设置成单独(或分别)与设置在第一基板100的第一焊盘部110中的多个第一栅极焊盘GP1中的相应第一栅极焊盘GP1交叠。根据一实施方式的多个第二栅极焊盘GP2的每一个可单独(或分别)连接至设置在布线部分400中的多条布线之中的多条栅极布线430中的相应栅极布线430的另一端。因此,多个第二栅极焊盘GP2的每一个可通过相应栅极布线430和相应第一栅极焊盘GP1电连接至栅极控制线组GCL中包括的相应栅极控制线。

根据一实施方式的多个第二栅极焊盘GP2可划分(或分类)为第二起始信号焊盘、多个第二移位时钟焊盘、至少一个第二栅极驱动电源焊盘、和至少一个第二栅极公共电源焊盘。

第二起始信号焊盘可电连接至设置在布线部分400的栅极布线部分中的起始信号布线。因此,第二起始信号焊盘可通过相应第一起始信号焊盘和多条栅极布线430之中的相应起始信号布线电连接至栅极控制线组GCL中包括的相应起始信号线。

多个第二移位时钟焊盘的每一个可电连接至设置在布线部分400的栅极布线部分中的多条移位时钟布线中的相应移位时钟布线。因此,多个第二移位时钟焊盘的每一个可通过相应第一移位时钟焊盘和多条栅极布线430之中的相应移位时钟布线电连接至栅极控制线组GCL中包括的多条移位时钟线中的相应移位时钟线。

至少一个第二栅极驱动电源焊盘可电连接至设置在布线部分400的栅极布线部分中的至少一条栅极驱动电源布线。因此,至少一个第二栅极驱动电源焊盘可通过相应第一栅极驱动电源焊盘和多条栅极布线430之中的相应栅极驱动电源布线电连接至栅极控制线组GCL中包括的栅极驱动电源线。

至少一个第二栅极公共电源焊盘可电连接至设置在布线部分400的栅极布线部分中的至少一条栅极公共电源布线。因此,至少一个第二栅极公共电源焊盘可通过相应第一栅极公共电源焊盘和多条栅极布线430之中的相应栅极公共电源布线电连接至栅极控制线组GCL中包括的栅极公共电源线。

第二像素驱动电源焊盘部可通过布线部分400电连接至第一焊盘部110的第一像素驱动电源焊盘部。

根据一实施方式的第二像素驱动电源焊盘部可包括多个第二像素驱动电源焊盘PPP2。多个第二像素驱动电源焊盘PPP2的每一个可设置成单独(或分别)与设置在第一基板100的第一焊盘部110中的多个第一像素驱动电源焊盘PPP1中的相应第一像素驱动电源焊盘PPP1交叠。根据一实施方式的多个第二像素驱动电源焊盘PPP2的每一个可通过设置在布线部分400中的多条布线之中的多条像素驱动电源布线450中的相应像素驱动电源布线450,单独(或分别)连接至多个第一像素驱动电源焊盘PPP1中的相应第一像素驱动电源焊盘PPP1。因此,多个第二像素驱动电源焊盘PPP2的每一个可通过相应像素驱动电源布线450和相应第一像素驱动电源焊盘PPP1电连接至相应像素驱动电源线PL。

第二像素公共电源焊盘部可通过布线部分400电连接至第一焊盘部110的第一像素公共电源焊盘部。

根据一实施方式的第二像素公共电源焊盘部可包括多个第二像素公共电源焊盘CPP2。多个第二像素公共电源焊盘CPP2的每一个可设置成单独(或分别)与设置在第一基板100的第一焊盘部110中的多个第一像素公共电源焊盘CPP1中的相应第一像素公共电源焊盘CPP1交叠。根据一实施方式的多个第二像素公共驱动电源焊盘CPP2的每一个可通过设置在布线部分400中的多条布线之中的多条像素公共电源布线470中的相应像素公共电源布线470、单独(或分别)连接至多个第一像素公共电源焊盘CPP1中的相应第一像素公共电源焊盘CPP1。因此,多个第二像素公共电源焊盘CPP2的每一个可通过相应像素公共电源布线470和相应第一像素公共电源焊盘CPP1电连接至相应像素公共电源线CPL。

根据一实施方式的第二焊盘部210可包括与设置在第一焊盘部110之中的焊盘的布置顺序相同(或匹配)地、沿第一方向X按照一个第二像素驱动电源焊盘PPP2、两个第二数据焊盘DP2、一个第二栅极焊盘GP2、一个第二像素公共电源焊盘CPP2、两个第二数据焊盘DP2和一个第二像素驱动电源焊盘PPP2的顺序布置的多个焊盘组PG。例如,多个焊盘组PG可包括第一焊盘组PG1和第二焊盘组PG2,第一焊盘组PG1包括沿第一方向X连续设置的一个第二像素驱动电源焊盘PPP2、两个第二数据焊盘DP2和一个第二栅极焊盘GP2,第二焊盘组PG2包括沿第一方向X连续设置的一个第二像素公共电源焊盘CPP2、两个第二数据焊盘DP2和一个第二像素驱动电源焊盘PPP2。

根据本发明的第二焊盘部210可进一步包括第二基准电源焊盘部。

第二基准电源焊盘部可通过布线部分400电连接至第一焊盘部110的第一基准电源焊盘部。

根据一实施方式的第二基准电源焊盘部可包括多个第二基准电源焊盘RPP2。多个第二基准电源焊盘RPP2的每一个可设置成单独(或分别)与设置在第一基板100的第一焊盘部110中的多个第一基准电源焊盘RPP1中的相应第一基准电源焊盘RPP1交叠。因此,多个第二基准电源焊盘RPP2的每一个可通过相应基准电源布线490和相应第一基准电源焊盘RPP1电连接至相应基准电源线RL。

根据本发明的第二基板200可进一步包括第三焊盘部230和连线部分250。

第三焊盘部230可设置在第二基板200的后表面200b上。例如,第三焊盘部230可设置在第二基板200的后表面200b中的与第一边缘部分相邻的中心部分处。

根据一实施方式的第三焊盘部230可包括沿第一方向X彼此分隔开一定间隔的多个第三焊盘(或输入焊盘)。多个第三焊盘可划分(或分类)为多个第三数据焊盘DP、第三像素驱动电源焊盘PPP3、多个第三栅极焊盘GP3、以及多个第三像素公共电源焊盘CPP3。

根据一实施方式的第三焊盘部230可包括第三数据焊盘部、第三像素驱动电源焊盘部、第三栅极焊盘部和第三像素公共电源焊盘部。

第三焊盘部230可包括:包括第三数据焊盘部和第三像素驱动电源焊盘部的第一区域(或中心区域)、包括第三栅极焊盘部的第二区域(或一个区域)、以及包括第三像素公共电源焊盘部的第三区域(或另一个区域)。

第三数据焊盘部可通过连线部分250电连接至第二焊盘部210的第二数据焊盘部。

根据一实施方式的第三数据焊盘部可包括多个第三数据焊盘DP3。多个第三数据焊盘DP3可沿第一方向X平行地且彼此分隔开一定间隔地设置在第三焊盘部230的第一区域中。

根据一实施方式的多个第三数据焊盘DP3的每一个可通过连线部分250单独(或分别)连接至设置在第二焊盘部210中的多个第二数据焊盘DP2之中的相应第二数据焊盘DP2。多个第三数据焊盘DP3的每一个可被提供来自驱动电路单元500的驱动IC 530的数据信号。根据一实施方式的数据信号可通过多个第三数据焊盘DP3之中的相应第三数据焊盘DP3和连线部分250提供至设置在第二焊盘部210中的多个第二数据焊盘DP2的每一个。

第三像素驱动电源焊盘部可通过连线部分250电连接至第二焊盘部210的第二像素驱动电源焊盘部。

根据一实施方式的第三像素驱动电源焊盘部可包括多个第三像素驱动电源焊盘PPP3。多个第三像素驱动电源焊盘PPP3可沿第一方向X平行地且彼此分隔开一定间隔地设置在第三焊盘部230的第一区域中。

根据一实施方式的多个第三像素驱动电源焊盘PPP3的每一个可通过连线部分250单独(或分别)连接至设置在第二焊盘部210中的多个第二像素驱动电源焊盘PPP2之中的相应第二像素驱动电源焊盘PPP2。例如,多个第三像素驱动电源焊盘PPP3的每一个可被提供来自驱动电路单元500的驱动IC 530的像素驱动电源。根据一实施方式的像素驱动电源可通过多个第三像素驱动电源焊盘PPP3之中的相应第三像素驱动电源焊盘PPP3和连线部分250提供至设置在第二焊盘部210中的多个第二像素驱动电源焊盘PPP2的每一个。

多个第三数据焊盘DP3和多个第三像素驱动电源焊盘PPP3可按照与设置在第二焊盘部210中的多个第二数据焊盘DP2和多个第二像素驱动电源焊盘PPP2的布置顺序相同的顺序平行地设置在第三焊盘部230的第一区域中。

第三栅极焊盘部可通过连线部分250电连接至第二焊盘部210的第二栅极焊盘部。

根据一实施方式的第三栅极焊盘部可包括多个第三栅极焊盘GP3。多个第三栅极焊盘GP3可沿第一方向X平行地且彼此分隔开一定间隔设置在第三焊盘部230的第二区域中。

根据一实施方式的多个第三栅极焊盘GP3的每一个可通过连线部分250单独(或分别)连接至设置在第二焊盘部210中的多个第二栅极焊盘GP2之中的相应第二栅极焊盘GP2。例如,多个第三栅极焊盘GP3的每一个可被提供来自驱动电路单元500的时序控制器570的栅极控制信号。根据一实施方式的栅极控制信号可通过多个第三栅极焊盘GP3之中的相应第三栅极焊盘GP3和连线部分250提供至设置在第二焊盘部210中的多个第二栅极焊盘GP2的每一个。

根据一实施方式的多个第三栅极焊盘GP3可划分(或分类)为第三起始信号焊盘、多个第三移位时钟焊盘、至少一个第三栅极驱动电源焊盘和至少一个第三栅极公共电源焊盘。

第三起始信号焊盘可通过连线部分250电连接至设置在第二焊盘部210中的第二起始信号焊盘。例如,第三起始信号焊盘可被提供来自驱动电路单元500的时序控制器570的起始信号(或脉冲)。根据一实施方式的起始信号可通过多个第三起始信号焊盘之中的相应第三起始信号焊盘和连线部分250提供至设置在第二焊盘部210中的第二起始信号焊盘。

多个第三移位时钟焊盘的每一个可通过连线部分250电连接至设置在第二焊盘部210中的多个第二移位时钟焊盘之中的相应第二移位时钟焊盘。例如,多个第三移位时钟焊盘的每一个可被单独提供来自驱动电路单元500的时序控制器570的多个栅极移位时钟之一。根据一实施方式的多个栅极移位时钟的每一个可通过多个第三移位时钟焊盘之中的相应第三移位时钟焊盘和连线部分250提供至设置在第二焊盘部210中的第二移位时钟焊盘。

至少一个第三栅极驱动电源焊盘可通过连线部分250电连接至设置在第二焊盘部210中的至少一个第二栅极驱动电源焊盘。例如,至少一个第三栅极驱动电源焊盘可被提供来自驱动电路单元500的电源电路单元590的栅极驱动电源。根据一实施方式的栅极驱动电源可通过多个第三栅极驱动电源焊盘之中的相应第三栅极驱动电源焊盘和连线部分250提供至设置在第二焊盘部210中的第二栅极驱动电源焊盘。

至少一个第三栅极公共电源焊盘可通过连线部分250电连接至设置在第二焊盘部210中的至少一个第二栅极公共电源焊盘。例如,至少一个第三栅极公共电源焊盘可被提供来自驱动电路单元500的电源电路单元590的栅极公共电源。根据一实施方式的栅极公共电源可通过多个第三栅极公共电源焊盘之中的相应第三栅极公共电源焊盘和连线部分250提供至设置在第二焊盘部210中的第二栅极公共电源焊盘。

第三像素公共电源焊盘部可包括至少一个第三像素公共电源焊盘CPP3。至少一个第三像素公共电源焊盘CPP3可设置在第三焊盘部230的第三区域中。

至少一个第三像素公共电源焊盘CPP3可通过连线部分250单独(或分别)连接至设置在第二焊盘部210中的相应第二像素公共电源焊盘CPP2。例如,至少一个第三像素公共电源焊盘CPP3可被提供来自驱动电路单元500的电源电路单元590的像素公共电源。根据一实施方式的像素公共电源可通过多个第三像素公共电源焊盘CPP3之中的相应第三像素公共电源焊盘CPP3和连线部分250提供至设置在第二焊盘部210中的多个第二像素公共电源焊盘CPP2的每一个。

第三焊盘部230可进一步包括设置在第一区域与第二区域之间并且包括多个虚拟焊盘的第一虚拟区域、以及设置在第一区域与第三区域之间并且包括多个虚拟焊盘的第二虚拟区域。

根据一实施方式的第三焊盘部230可进一步包括第三基准电源焊盘部。

第三基准电源焊盘部可通过连线部分250电连接至第二焊盘部210的第二基准电源焊盘部。

根据一实施方式的第三基准电源焊盘部可包括多个第三基准电源焊盘RPP3。多个第三基准电源焊盘RPP3可沿第一方向X平行地且彼此分隔开一定间隔地设置在第三焊盘部230的第一区域中。

根据一实施方式的多个第三基准电源焊盘RPP3的每一个可通过连线部分250单独(或分别)连接至设置在第二焊盘部210中的多个第二基准电源焊盘RPP2之中的相应第二基准电源焊盘RPP2。例如,多个第三基准电源焊盘RPP3的每一个可被提供来自驱动电路单元500的驱动IC 530的基准电源。根据一实施方式的基准电源可通过多个第三基准电源焊盘RPP3之中的相应第三基准电源焊盘RPP3和连线部分250提供至设置在第二焊盘部210中的多个第二基准电源焊盘RPP2的每一个。

第三焊盘部230的第一区域中的多个第三像素驱动电源焊盘PPP3、多个第三数据焊盘DP3和多个第三基准电源焊盘RPP3的每一个可按照与设置在第二焊盘部210中的多个第二像素驱动电源焊盘PPP2、多个第二数据焊盘DP2和多个第二基准电源焊盘RPP2的布置顺序相同的顺序平行地设置。

连线部分250可设置在第二焊盘部210与第三焊盘部230之间。连线部分250可包括单独(或分别)将第二焊盘部210的第二焊盘连接至第三焊盘部230的第三焊盘的多条连线。

根据一实施方式的多条连线可划分(或分类)为多条数据连线251、多条栅极连线253、多条像素驱动电源连线255、和像素公共电源连线257。因此,连线部分250可包括多条数据连线251、多条栅极连线253、多条像素驱动电源连线255、和像素公共电源连线257。

根据另一实施方式,连线部分250可包括数据连线部分、栅极连线部分、像素驱动电源连线部分和像素公共电源连线部分。

数据连线部分(或第一连线部分)可将第二焊盘部210的第二数据焊盘部电连接至第三焊盘部230的第三数据焊盘部。

根据一实施方式的数据连线部分可包括多条数据连线251。多条数据连线(或第一连线)251的每一条可单独(或分别)将设置在第二焊盘部210中的多个第二数据焊盘DP2中的相应第二数据焊盘连接至设置在第三焊盘部230中的多个第三数据焊盘DP3中的相应第三数据焊盘。因此,提供至多个第三数据焊盘DP3的每一个的数据信号可通过相应数据连线251提供至相应第二数据焊盘DP2并且可通过相应数据布线410和相应第一数据焊盘DP1提供至相应数据线DLo和DLe。

栅极连线部分(或第二连线部分)可将第二焊盘部210的第二栅极焊盘部电连接至第三焊盘部230的第三栅极焊盘部。

根据一实施方式的栅极连线部分可包括多条栅极连线253。多条栅极连线(或第二连线)253的每一条可单独(或分别)将设置在第二焊盘部210中的多个第二栅极焊盘GP2中的相应第二栅极焊盘连接至设置在第三焊盘部230中的多个第三栅极焊盘GP3中的相应第三栅极焊盘。因此,提供至多个第三栅极焊盘GP3的每一个的栅极控制信号可通过相应栅极连线253提供至相应第二栅极焊盘GP2并且可通过相应栅极布线430和相应第一栅极焊盘GP1提供至栅极控制线组GCL中包括的相应栅极连线。

根据一实施方式的多条栅极连线253可划分(或分类)为起始信号连线253a、多条移位时钟连线253b、至少一条栅极驱动电源连线253c和至少一条栅极公共电源连线253d。因此,栅极连线部分可包括起始信号连线253a、多条移位时钟连线253b、至少一条栅极驱动电源连线253c和至少一条栅极公共电源连线253d。

起始信号连线253a可将设置在第二焊盘部210中的第二起始信号焊盘电连接至设置在第三焊盘部230中的第三起始信号焊盘。因此,提供至第三起始信号焊盘的起始信号可通过起始信号连线提供至第二起始信号焊盘并且可通过起始信号布线和第一起始信号焊盘提供至栅极控制线组GCL中包括的相应起始信号线。

多条移位时钟连线253b的每一条可将设置在第二焊盘部210中的多个第二移位时钟焊盘中的相应第二移位时钟焊盘电连接至设置在第三焊盘部230中的多个第三移位时钟焊盘中的相应第三移位时钟焊盘。因此,提供至多个第三移位时钟焊盘的每一个的栅极移位时钟可通过相应移位时钟连线253b提供至相应第二移位时钟焊盘并且可通过移位时钟布线和第一移位时钟焊盘提供至栅极控制线组GCL中包括的相应移位时钟线。

至少一条栅极驱动电源连线253c可将设置在第二焊盘部210中的至少一个第二栅极驱动电源焊盘电连接至设置在第三焊盘部230中的至少一个第三栅极驱动电源焊盘。因此,提供至第三栅极驱动电源焊盘的栅极驱动电源可通过栅极驱动电源连线253c提供至第二栅极驱动电源焊盘并且可通过栅极驱动电源布线和第一栅极驱动电源焊盘提供至栅极控制线组GCL中包括的栅极驱动电源线。

至少一条栅极公共电源连线253d可将设置在第二焊盘部210中的至少一个第二栅极公共电源焊盘电连接至设置在第三焊盘部230中的至少一个第三栅极公共电源焊盘。因此,提供至第三栅极公共电源焊盘的栅极公共电源可通过栅极公共电源连线253d提供至第二栅极公共电源焊盘并且可通过栅极公共电源布线和第一栅极公共电源焊盘提供至栅极控制线组GCL中包括的栅极公共电源线。

像素驱动电源连线部分(或第三连线部分)可将第二焊盘部210的第二像素驱动电源焊盘部电连接至第三焊盘部230的第三像素驱动电源焊盘部。

根据一实施方式的像素驱动电源连线部分可包括多条像素驱动电源连线255。多条像素驱动电源连线(或第三连线)255的每一条可单独(或分别)将设置在第二焊盘部210中的多个第二像素驱动电源焊盘PPP2连接至设置在第三焊盘部230中的多个第三像素驱动电源焊盘PPP3。因此,提供至多个第三像素驱动电源焊盘PPP3的每一个的像素驱动电源可通过相应像素驱动电源连线255提供至相应第二像素驱动电源焊盘PPP2并且可通过像素驱动电源布线450和相应第一像素驱动电源焊盘PPP1提供至相应像素驱动电源线PL。

多条数据连线251、多条栅极连线253和多条像素驱动电源连线255可各自包括连接至第二焊盘部210的第一线部分、连接至第三焊盘部230的第二线部分、以及连接在第一线部分与第二线部分之间的第三线部分。第一线部分和第二线部分的每一个可具有直线形状,并且第三线部分可具有非直线形状。例如,第三线部分可具有与第一线部分和第二线部分之间的最短路径对应的斜线形状(diagonal shape)。

像素公共电源连线部分(或第四连线部分)可将第二焊盘部210的第二像素公共电源焊盘部电连接至第三焊盘部230的第三像素公共电源焊盘部。

根据一实施方式的像素公共电源连线部分可包括像素公共电源连线257。多条像素公共电源连线(或第四连线)257的每一条可将设置在第二焊盘部210中的多个第二像素公共电源焊盘CPP2共同地连接至设置在第三焊盘部230中的多个第三像素公共电源焊盘CPP3。因此,提供到至少一个第三像素公共电源焊盘CPP3的每一个的像素公共电源可通过像素公共电源连线257提供至多个第二像素公共电源焊盘CPP2,可通过多条像素公共电源布线470中的相应像素公共电源布线和多个第一像素公共电源焊盘CPP1中的相应第一像素公共电源焊盘提供至多条像素公共电源线CPL的每一条,并且可通过多个公共电源接触部分CPCP的每一个提供至公共电极CE。

根据一实施方式的像素公共电源连线257可包括第一公共连线257a、第二公共连线257b、和多条第三公共连线257c。

第一公共连线257a可共同地连接至设置在第三焊盘部230中的至少一个第三像素公共电源焊盘CPP3。例如,第一公共连线257a可设置在第二基板200的后表面200b的一个拐角部分处。

第一公共连线257a可设置或形成在第二焊盘部210与第三焊盘部230之间的第二基板200的后表面上,以具有相对较宽的尺寸(或区域),使得被施加的像素公共电源的压降被最小化。根据一实施方式的第一公共连线257a的尺寸可沿从其一侧到其另一侧的方向逐步增加。例如,根据一实施方式的第一公共连线257a的尺寸可沿从第三焊盘部230到第二基板200的外表面OS的方向逐步增加。

在根据一实施方式的第一公共连线257a中,与第三焊盘部230相邻的一侧可共同地连接至设置在第三焊盘部230中的至少一个第三像素公共电源焊盘CPP3,并且与第二焊盘部210相邻的另一侧可与第二公共连线257b交叠。例如,第一公共连线257a可与数据连线251或栅极连线253一起设置在第二基板200的后表面200b上。

第二公共连线257b可设置在第二基板200的后表面200b的第一边缘部分处,以与第一基板100的第一边缘部分交叠并且与第二焊盘部210相邻。根据一实施方式的第二公共连线257b可与第一方向X平行地设置,以面对设置在第二焊盘部210中的所有焊盘。例如,第二公共连线257b可具有尺寸(或区域)相对较宽的条形形状,用来将施加至像素公共电源连线257的像素公共电压的压降最小化。

第二公共连线257b可与多条像素驱动电源连线255、多条数据连线251和多条栅极连线253的每一条交叠。例如,数据连线251可设置在栅极连线253上,并且第二公共连线257b可设置在像素驱动电源连线255上。此外,像素驱动电源连线255可与数据连线251一起设置在栅极连线253上。

第二公共连线257b的一侧可通过连线接触孔257h电连接至第一公共连线257a的另一侧。

多条第三公共连线257c的每一条可共同地连接至第二公共连线257b并且可连接至多个第二焊盘之中的相应第二焊盘。根据一实施方式的多条第三公共连线257c的每一条可沿从第二公共连线257b的另一侧到设置在第二焊盘部210中的多个第二像素公共电源焊盘CPP2的方向延伸(或突出),并且可电连接至多个第二像素公共电源焊盘CPP2中的相应第二像素公共电源焊盘。例如,多条第三公共连线257c的每一条可与第二公共连线257b一起形成。此外,多条第三公共连线257c和第二公共连线257b可与第二焊盘部210的焊盘一起形成。

根据一实施方式的连线部分250可进一步包括基准电源连线部分。

基准电源连线部分(或第五连线部分)可将第二焊盘部210的第二基准电源焊盘部电连接至第三焊盘部230的第三基准电源焊盘部。

根据一实施方式的基准电源连线部分可包括多条基准电源连线259。多条基准电源连线(或第五连线)259的每一条可将设置在第二焊盘部210中的多个第二基准电源焊盘RPP2中的相应第二基准电源焊盘单独(分别)连接至设置在第三焊盘部230中的多个第三基准电源焊盘RPP3中的相应第三基准电源焊盘。因此,提供至多个第三基准电源焊盘RPP3的每一个的基准电压可通过相应基准电源连线259提供至相应第二基准电源焊盘RPP2并且可通过基准电源布线490和第一基准电源焊盘RPP1提供至相应基准电源线RL。

多条基准电源连线259可各自包括连接至相应第二基准电源焊盘RPP2的第一线部分、连接至第三基准电源焊盘RPP3的第二线部分、以及连接在第一线部分与第二线部分之间的第三线部分。第一线部分和第二线部分的每一个可具有直线形状,并且第三线部分可具有非直线形状。例如,第三线部分可具有与第一线部分和第二线部分之间的最短路径对应的斜线形状。

根据一实施方式的连线部分250可进一步包括栅极控制信号传输部分254。

栅极控制信号传输部分(或第六连线部分)254可绕过(bypass)第三焊盘部230并且可将第三栅极焊盘部电连接至栅极连线部分。

根据一实施方式的栅极控制信号传输部分254可包括多条栅极控制信号传输线。

多条栅极控制信号传输线(或第六连线)的每一条可选择性地将设置在第三焊盘部230中的多个第三栅极焊盘GP3中的相应第三栅极焊盘连接至多条栅极连线中的相应栅极连线。例如,多条栅极控制信号传输线和多条栅极连线253可设置在第二基板200的后表面200b上的不同层上,并且多条栅极连线253的每一条的另一侧可通过连线接触孔电连接至相应栅极控制信号传输线。可选择地,多条栅极连线253的每一条的另一侧可穿过两个相邻第三焊盘之间的区域并且可选择性地连接至多条栅极控制信号传输线而不与设置在第三焊盘部230中的第三焊盘交叠。

根据一实施方式的多条栅极控制信号传输线可划分(或分类)为起始信号传输线254a、多条移位时钟传输线254b、至少一条栅极驱动电源传输线254c和至少一条栅极公共电源传输线254d。因此,栅极控制信号传输部分254可包括起始信号传输线254a、多条移位时钟传输线254b、至少一条栅极驱动电源传输线254c和至少一条栅极公共电源传输线254d。

起始信号传输线254a可将第三起始信号焊盘电连接至起始信号连线253a。根据一实施方式的起始信号传输线254a可包括与第三起始信号焊盘电连接的一个线部分、与起始信号连线253a电连接的另一个线部分、以及电连接在其一个线部分与其另一个线部分之间并绕过第三焊盘部230的中间线部分。

起始信号传输线254a的一个线部分可与第二方向Y平行地设置并且可电连接至第三起始信号焊盘。

起始信号传输线254a的另一个线部分可与第一方向X平行地与第三焊盘部230相邻设置并且可电连接至起始信号连线253a。例如,起始信号传输线254a的另一个线部分可通过连线接触孔电连接至起始信号连线253a。因此,提供至第三起始信号焊盘的起始信号可通过起始信号传输线254a、起始信号连线253a、第二起始信号焊盘、起始信号布线和第一起始信号焊盘提供至栅极控制线组GCL中包括的起始信号线。

起始信号传输线254a的中间线部分可包括第一中间线和第二中间线,第一中间线与第一方向X平行地从一个线部分延伸,第二中间线从第一中间线延伸并与第三焊盘部230的一端(或左端)分隔开并且电连接至另一个线部分。例如,中间线部分可具有绕过第三焊盘部230的“┏”形状。

根据一实施方式的起始信号连线253a可穿过第三焊盘部230并且可电连接至起始信号传输线254a的另一个线部分。例如,起始信号连线253a可设置成穿过两个相邻第三焊盘之间的区域且不与设置在第三焊盘部230中的第三焊盘交叠。在这种情况下,提供至起始信号连线253a的起始信号不会基于提供至第三焊盘的信号而改变(或变化)并且可保持在原始电压电平。

多条移位时钟传输线254b的每一条可选择性地将多个移位时钟焊盘中的相应移位时钟焊盘连接至多条移位时钟连线253b中的相应第三移位时钟连线。例如,当栅极控制信号传输部分254包括第一至第四移位时钟传输线254b并且连线部分250包括多条第一至第四移位时钟连线253b时,多条第一移位时钟连线253b的每一条可共同地连接至第一移位时钟传输线254b,多条第二移位时钟连线253b的每一条可共同地连接至第二移位时钟传输线254b,多条第三移位时钟连线253b的每一条可共同地连接至第三移位时钟传输线254b,并且多条第四移位时钟连线253b的每一条可共同地连接至第四移位时钟传输线254b。

多条移位时钟传输线254b的每一条可具有围绕起始信号传输线254a的形状并且可与起始信号传输线254a平行地设置而绕过第三焊盘部230。根据一实施方式的多条移位时钟传输线254b的每一条可包括与相应第三移位时钟焊盘电连接的一个线部分、与相应移位时钟连线253b电连接的另一个线部分、以及电连接在其一个线部分与其另一个线部分之间以绕过第三焊盘部230的中间线部分。例如,多条移位时钟传输线254b的每一条的另一个线部分可通过连线接触孔电连接至相应移位时钟连线253b。因此,提供至多个第三移位时钟焊盘的每一个的栅极移位时钟可通过相应移位时钟传输线254b、相应移位时钟连线253b、相应第二移位时钟焊盘、相应栅极移位时钟布线和相应第一移位时钟焊盘提供至栅极控制线组GCL中包括的移位时钟线。

根据一实施方式的多条移位时钟连线253b的每一条可穿过第三焊盘部230并且可电连接至相应移位时钟传输线254b的另一个线部分。例如,多条移位时钟连线253b的每一条可设置成穿过两个相邻第三焊盘之间的区域而不与设置在第三焊盘部230中的第三焊盘交叠。在这种情况下,提供至多条移位时钟连线253b的每一条的栅极移位时钟不会基于提供至第三焊盘的信号而改变(或变化)并且可保持在原始电压电平。

至少一条栅极驱动电源传输线254c可将至少一个栅极驱动电源焊盘电连接到至少一条栅极驱动电源连线253c。

至少一条栅极驱动电源传输线254c可具有围绕最外侧的移位时钟传输线254b的形状并且可与移位时钟传输线254b平行地设置而绕过第三焊盘部230。根据一实施方式的至少一条栅极驱动电源传输线254c可包括与第三栅极驱动电源焊盘电连接的一个线部分、与栅极驱动电源连线253c电连接的另一个线部分、以及电连接在其一个线部分与其另一个线部分之间以绕过第三焊盘部230的中间线部分。例如,至少一条栅极驱动电源传输线254c的另一个线部分可通过连线接触孔电连接至栅极驱动电源连线253c。因此,提供到至少一个栅极驱动电源焊盘的栅极驱动电源可通过栅极驱动电源传输线254c、栅极驱动电源连线253c、第二栅极驱动电源焊盘、栅极驱动电源布线和第一栅极驱动电源焊盘提供至栅极控制线组GCL中包括的栅极驱动电源线。

根据一实施方式的至少一条栅极驱动电源连线253c可穿过第三焊盘部230并且可电连接至栅极驱动电源传输线254c的另一个线部分。例如,至少一条栅极驱动电源连线253c可设置成穿过两个相邻第三焊盘之间的区域而不与设置在第三焊盘部230中的第三焊盘交叠。在这种情况下,提供至栅极驱动电源连线253c的栅极驱动电源不会基于提供至第三焊盘的信号而改变(或变化)并且可保持在原始电压电平。

至少一条栅极公共电源传输线254d可将至少一个栅极公共电源焊盘电连接到至少一条栅极公共电源连线253d。

至少一条栅极公共电源传输线254d可具有围绕栅极驱动电源传输线254c的形状并且可与栅极驱动电源传输线254c平行地设置而绕过第三焊盘部230。根据一实施方式的至少一条栅极公共电源传输线254d可包括与第三栅极公共电源焊盘电连接的一个线部分、与栅极公共电源连线253d电连接的另一个线部分、以及电连接在其一个线部分与其另一个线部分之间以绕过第三焊盘部230的中间线部分。例如,至少一条栅极公共电源传输线254d的另一个线部分可通过连线接触孔电连接至栅极公共电源连线253d。因此,提供到至少一个栅极公共电源焊盘的栅极公共电源可通过栅极公共电源传输线254d、栅极公共电源连线253d、第二栅极公共电源焊盘、栅极公共电源布线和第一栅极公共电源焊盘提供至栅极控制线组GCL中包括的栅极公共电源线。根据一实施方式的至少一条栅极公共电源连线253d可穿过第三焊盘部230并且可电连接至栅极公共电源传输线254d的另一个线部分。例如,至少一条栅极公共电源连线253d可设置成穿过两个相邻第三焊盘之间的区域而不与设置在第三焊盘部230中的第三焊盘交叠。在这种情况下,提供至栅极公共电源连线253d的栅极公共电源不会基于提供至第三焊盘的信号而改变(或变化)并且可保持在原始电压电平。

图10是图解图6中所示的第i级电路单元的电路图。

参照图5至图7和图10,根据本发明的第i级电路单元150i可响应于从设置在第一基板100上的栅极控制线组GCL提供的栅极控制信号输出两个扫描信号SSi和SSi+1以及进位信号CSi。

根据一实施方式的栅极控制信号可包括:起始信号Vst;包括多个扫描时钟sCLK和多个进位时钟cCLK的多个移位时钟;第一至第三栅极驱动电源GVdd1、GVdd2和GVdd3;以及第一和第二栅极公共电源GVss1和GVss2。在这种情况下,栅极控制线组GCL可包括起始信号线、多条扫描时钟线、多条进位时钟线、第一至第三栅极驱动电源线、以及第一和第二栅极公共电源线。

根据一实施方式的栅极控制信号可包括第一至第j进位时钟和第一至第j扫描时钟。例如,j可以是4,但不限于此,可以是6、8或10或者更大的偶数。

当栅极控制信号包括第一至第四进位时钟时,第一进位时钟可施加至第4k-3(其中k是自然数)级电路单元,第二进位时钟可施加至第4k-2级电路单元,第三进位时钟可施加至第4k-1级电路单元,并且第四进位时钟可施加至第4k级电路单元。当栅极控制信号包括第一至第四扫描时钟时,第一和第二扫描时钟可施加至奇数级电路单元,并且第三和第四扫描时钟可施加至偶数级电路单元。

此外,根据一实施方式的栅极控制信号可进一步包括正向驱动信号FWS和反向驱动信号BWS。在这种情况下,栅极控制线组GCL可进一步包括正向驱动信号线和反向驱动信号线。

根据一实施方式的栅极控制信号可进一步包括用于外部感测模式的外部感测线选择信号Slss、外部感测复位信号Srst和外部感测控制信号Scs。在这种情况下,栅极控制线组GCL可进一步包括外部感测选择信号线、外部感测复位信号线和外部感测控制信号线。

根据本发明的第i级电路单元150i可包括分支网153、节点控制电路NCC、第一反相器电路IC1、第二反相器电路IC2、节点复位信号NRC和输出缓存器电路OBC。

分支网153可实现为在节点控制电路NCC、第一反相器电路IC1、第二反相器电路IC2、节点复位信号NRC和输出缓存器电路OBC之间形成电路连接并且可选择性地连接至栅极控制线组GCL的线。

分支网153可选择性地连接至栅极控制线组GCL的线。根据一实施方式的分支网153可包括第一至第三控制节点Q、QBo和QBe以及网线NL。

第一至第三控制节点Q、QBo和QBe的每一个可设置在布置于第一基板100的第i水平行中的每个像素区域的上边缘区域(或下边缘区域)中。第一至第三控制节点Q、QBo和QBe的每一个可与第一方向X或栅极线平行地设置。例如,第一至第三控制节点Q、QBo和QBe的每一个可与栅极线相邻设置。

网线NL可选择性地连接至栅极控制线组GCL的线并且可选择性地连接至第一至第三控制节点Q、QBo和QBe。此外,网线NL可选择性地连接在构成级电路单元150i的电路之间。

节点控制电路NCC可实现为控制第一至第三控制节点Q、QBo和QBe的每一个的电压。

根据一实施方式的节点控制电路NCC可通过网线NL连接至第一至第三控制节点Q、QBo和QBe的每一个,并且可实现为响应于通过网线NL提供的起始信号Vst、复位信号Vrst和第一栅极驱动电源GVdd1控制第一至第三控制节点Q、QBo和QBe的每一个的电压。例如,起始信号Vst可以是从第i-2级电路单元150i-2输出的第i-2进位信号CSi-2。复位信号Vrst可以是从第i+2级电路单元150i+2输出的第i+2进位信号CSi+2。

根据另一实施方式,节点控制电路NCC可通过网线NL连接至第一至第三控制节点Q、QBo和QBe的每一个,并且可响应于通过网线NL提供的起始信号Vst、复位信号Vrst、正向驱动信号FWS、反向驱动信号BWS和第一栅极驱动电源GVdd1控制第一至第三控制节点Q、QBo和QBe的每一个的电压。例如,当正向驱动信号FWS具有高电压电平(或高电位电压电平)时,反向驱动信号BWS可具有低电压电平(或低电位电压电平);当正向驱动信号FWS具有低电压电平(或低电位电压电平)时,反向驱动信号BWS可具有高电压电平(或高电位电压电平)。例如,当正向驱动信号FWS具有高电压电平时,栅极驱动电路150可基于正向扫描驱动向从第一条栅极线起一直到最后一条栅极线提供扫描信号;当反向驱动信号BWS具有高电压电平时,栅极驱动电路150可基于反向扫描驱动向从最后一条栅极线起一直到第一条栅极线提供扫描信号。本文中,高电压电平可称为第一电压电平、高电位电压电平、栅极导通电压电平或晶体管导通电压电平,低电压电平可称为第二电压电平、低电位电压电平、栅极截止电压电平或晶体管截止电压电平。

第一反相器电路IC1可基于通过网线NL提供的第一控制节点Q的电压控制或放电第二控制节点QBo的电压。根据一实施方式的第一反相器电路IC1可通过网线NL连接至第二栅极驱动电源GVdd2、第一控制节点Q、第二控制节点QBo、第一栅极公共电源GVss1和第二栅极公共电源GVss2。第一反相器电路IC1可响应于第二栅极公共电源GVss2和第一控制节点Q的电压将第一栅极公共电源GVss1提供至第二控制节点QBo,以将第二控制节点QBo的电压放电。

第二反相器电路IC2可基于通过网线NL提供的第一控制节点Q的电压控制或放电第三控制节点QBe的电压。根据一实施方式的第二反相器电路IC2可通过网线NL连接至第三栅极驱动电源GVdd3、第一控制节点Q、第三控制节点QBe、第一栅极公共电源GVss1和第二栅极公共电源GVss2。第二反相器电路IC2可响应于第三栅极公共电源GVss3和第一控制节点Q的电压将第一栅极公共电源GVss1提供至第三控制节点QBe,以将第三控制节点QBe的电压放电。

第二栅极驱动电源GVdd2和第三栅极驱动电源GVdd3可具有在它们之间反相(或彼此相反)的电压电平。例如,当第二栅极驱动电源GVdd2具有高电压电平时,第三栅极驱动电源GVdd3可具有低电压电平;当第二栅极驱动电源GVdd2具有低电压电平时,第三栅极驱动电源GVdd3可具有高电压电平。

第二栅极公共电源GVss2和第一栅极公共电源GVss1可具有相同的电压电平或不同的电压电平。

节点复位电路NRC可在第一控制节点Q的电压具有高电压电平的同时保持第二控制节点QBo和第三控制节点QBe的每一个的电压电平。

根据一实施方式的节点复位电路NRC可响应于通过网线NL提供的起始信号Vst和复位信号Vrst同时将第二控制节点QBo的电压和第三控制节点QBe的电压复位。例如,节点复位电路NRC可响应于起始信号Vst和复位信号Vrst将第一栅极公共电源GVss1提供至第二控制节点QBo和第三控制节点QBe,因而可将第二控制节点QBo和第三控制节点QBe保持在第一栅极公共电源GVss1的电压电平。

根据另一实施方式,节点复位电路NRC可响应于通过网线NL提供的起始信号Vst、复位信号Vrst、正向驱动信号FWS和反向驱动信号BWS同时将第二控制节点QBo的电压和第三控制节点QBe的电压复位。例如,节点复位电路NRC可响应于起始信号Vst、复位信号Vrst、正向驱动信号FWS和反向驱动信号BWS将第一栅极公共电源GVss1提供至第二控制节点QBo和第三控制节点QBe,因而可将第二控制节点QBo和第三控制节点QBe的每一个保持在第一栅极公共电源GVss1的电压电平。

输出缓存器电路OBC可实现为基于通过网线NL提供的进位时钟cCLK、扫描时钟sCLK、第一栅极公共电源GVss1和第三栅极公共电源GVss3,响应于第一至第三控制节点Q、QBo和QBe的每一个的电压依次地输出具有栅极导通电压电平的两个扫描信号或者依次地输出具有栅极截止电压电平的两个扫描信号。

当第一控制节点Q的电压具有高电压电平时,根据一实施方式的输出缓存器电路OBC可输出对应于进位时钟cCLK的第i进位信号CSi、对应于奇数扫描时钟sCLKo的第i扫描信号SSi和对应于偶数扫描时钟sCLKe的第i+1扫描信号SSi+1的每一个。例如,第i进位信号CSi可作为起始信号Vst提供至第i+2级电路单元,第i扫描信号SSi可提供至奇数栅极线GLo(或第i栅极线GLi),第i+1扫描信号SSi+1可提供至偶数栅极线GLe(或第i+1栅极线GLi+1)。

当第一控制节点Q和第三控制节点QBe的每一个的电压具有低电压电平并且第二控制节点QBo的电压具有高电压电平时,根据一实施方式的输出缓存器电路OBC可输出每一个都具有与第三栅极公共电源GVss3的电压电平对应的栅极截止电压电平的第i扫描信号SSi和第i+1扫描信号SSi+1的每一个,并且可输出具有与第一栅极公共电源GVss1的电压电平对应的栅极截止电压电平的第i进位信号CSi。

当第一控制节点Q和第二控制节点QBo的每一个的电压具有低电压电平并且第三控制节点QBe的电压具有高电压电平时,根据一实施方式的输出缓存器电路OBC可输出每一个都具有与第三栅极公共电源GVss3的电压电平对应的栅极截止电压电平的第i扫描信号SSi和第i+1扫描信号SSi+1的每一个,并且可输出具有与第一栅极公共电源GVss1的电压电平对应的栅极截止电压电平的第i进位信号CSi。

根据一实施方式的输出缓存器电路OBC可设置在与第一方向X平行的第i水平行的中心区域中。例如,当输出缓存器电路OBC与水平行的一端(或另一端)相邻设置时,由于水平行的线电阻,扫描信号的电压电平可沿从栅极线的一端到其另一端的方向降低,因而,为了防止这种问题,输出缓存器电路OBC应当设置在与第一方向X平行的第i水平行的中心区域中,但不限于此;当栅极线的总长度相对较短时,输出缓存器电路OBC可设置在第i水平行的一侧或另一侧。

第一至第三栅极公共电源GVss1、GVss2和GVss3可具有相同的电压电平或不同的电压电平。

根据本发明的第i级电路单元150i可进一步包括第四控制节点Qm、第一感测控制电路SCC1和第二感测控制电路SCC2。

第四控制节点Qm可实现为电连接在第一感测控制电路SCC1与第二感测控制电路SCC2之间。第四控制节点Qm可包括在分支网153中并且可通过网线NL电连接在第一感测控制电路SCC1与第二感测控制电路SCC2之间。

第一感测控制电路SCC1可实现为响应于通过分支网153提供的第i进位信号CSi、外部感测线选择信号Slss、外部感测控制信号Scs、外部感测复位信号Srst和第一栅极驱动电源GVdd1控制第一控制节点Q和第四控制节点Qm的每一个的电压。例如,第一感测控制电路SCC1可响应于具有高电压电平的第i进位信号CSi和具有高电压电平的外部感测线选择信号Slss将第一栅极驱动电源GVdd1充入到第四控制节点Qm中,然后可响应于充入到第四控制节点Qm中的电压、在垂直消隐时段的前期提供的具有高电压电平的外部感测控制信号Scs、以及第一栅极驱动电源GVdd1来控制第一控制节点Q的电压。因此,输出缓存器电路OBC可基于第一控制节点Q的电压在垂直消隐时段期间输出对应于进位时钟cCLK的第i进位信号CSi、对应于奇数扫描时钟sCLKo的第i扫描信号SSi和对应于偶数扫描时钟sCLKe的第i+1扫描信号SSi+1的每一个。

此外,第一感测控制电路SCC1可响应于通过分支网153提供的外部感测复位信号Srst将第一控制节点Q的电压放电。例如,第一感测控制电路SCC1可响应于在垂直消隐时段的后期提供的具有高电压电平的外部感测复位信号Srst将第一栅极公共电源GVss1提供至第一控制节点Q,以将第一控制节点Q的电压复位或初始化。

第二感测控制电路SCC2可实现为响应于第四控制节点Qm的电压和通过分支网153提供的外部感测控制信号Scs将第二控制节点QBo和第三控制节点QBe的每一个的电压放电。例如,第二感测控制电路SCC2可响应于具有高电压电平的第四控制节点Qm的电压和具有高电压电平的外部感测控制信号Scs,将第一栅极公共电源GVss1提供至第二控制节点QBo和第三控制节点QBe的每一个,以同时将第二控制节点QBo和第三控制节点QBe放电。

第i级电路单元150i可像韩国专利申请公开No.10-2019-0021881中描述的第n级一样配置,或者可像韩国专利申请公开No.10-2019-0037860中描述的第k GIP一样配置。因此,省略对图10中所示的第i级电路单元150i的描述。构成第n级或第k GIP的多个薄膜晶体管(TFT)可与驱动TFT Tdr一起形成并且可实现设置在第一基板100的每个水平行中的多个分支电路1511至151n,并且构成级电路单元1501至150m的每一个的分支网153的第一至第三控制节点的每一个可与栅极线GL一起形成。因此,多个分支电路1511至151n的每一个可包括至少一个TFT(或分支TFT)并且可设置在沿第一方向X的一个水平行内的一个或多个像素P(或像素区域PA)之间。

图11是沿图3中所示的线I-I’截取的剖面图,图12是图11中所示的区域“D”的放大图。图11和图12是用于描述根据本发明的显示设备的第一基板和第二基板的每一个的剖面结构的示图。在描述图11和图12时,与图3的元件相同或对应的元件由相似的参考标记表示,并且在下面省略或将简要给出它们的重复描述。

参照图3、图5、图7、图11和图12,根据本发明的显示设备10可包括通过使用接合构件300彼此接合(或耦接)的第一基板100和第二基板200。

根据一实施方式的第一基板100可包括电路层101、平坦化层102、发光器件层103、堤部104、堰图案105、阻挡图案部分BPP和封装层106。

电路层101可设置在第一基板100的第一表面100a上。电路层101可称为像素阵列层或TFT阵列层。

根据一实施方式的电路层101可包括缓冲层101a和电路阵列层101b。

缓冲层101a可防止在制造TFT的工艺的高温工艺中第一基板100中包括的材料扩散到电路阵列层101b。此外,缓冲层101a可防止外部水分或湿气渗透到发光器件层103中。根据一实施方式的缓冲层101a可包括硅氧化物(SiOx)、硅氮化物(SiNx)、硅氮氧化物(SiON)或其多层,但不限于此。例如,缓冲层101a可包括设置在第一基板100上并且具有SiNx的第一缓冲层BL1和设置在第一缓冲层BL1上并且包括SiOx的第二缓冲层BL2。

电路阵列层101b可包括设置在缓冲层101a上的多条像素驱动线GL、DL、PL、RL、CPL、PSL、RDL和LCP;以及像素电路PC,像素电路PC包括设置在缓冲层101a上的多个像素区域PA的每一个中的驱动TFT Tdr。

设置在每个像素区域PA中的驱动TFT Tdr可包括有源层ACT、栅极绝缘层GI、栅极电极GE、层间绝缘层101c、第一源极/漏极电极SD1、第二源极/漏极电极SD2、和钝化层101d。

有源层ACT可设置在每个像素区域PA中的缓冲层101a上。有源层ACT可包括与栅极电极GE交叠的沟道区域、以及在相邻的沟道区域之间的彼此平行的第一源极/漏极区域和第二源极/漏极区域。有源层ACT可在导电化工艺中具有导电性,因而可用作将显示区域AA中的线直接连接或者将设置在不同层上的线电连接的跳接结构(jumping structure)的桥接线(bridge line)。

栅极绝缘层GI可设置在有源层ACT的沟道区域中。栅极绝缘层GI可将有源层ACT与栅极电极GE绝缘。例如,栅极绝缘层GI可包括SiOx、SiNx、SiON或其多层,但不限于此。

栅极电极GE可设置在栅极绝缘层GI上。栅极电极GE与有源层ACT的沟道区域可在其间具有栅极绝缘层GI的情况下交叠。

栅极电极GE可具有包括钼(Mo)、钛(Ti)、Mo-Ti合金(MoTi)和铜(Cu)中至少之一的单层结构或多层结构。根据一实施方式的栅极电极GE可包括设置在栅极绝缘层GI上的第一栅极金属层和设置在第一栅极金属层上的第二栅极金属层。例如,第一栅极金属层可包括Ti或MoTi。第二栅极金属层可包括Cu。在这种情况下,栅极电极GE可具有Cu/MoTi或Cu/Ti的两层结构。

像素驱动线GL、DL、PL、RL、CPL、PSL、RDL和LCP之中的栅极线GL、电源共用线PSL、线连接图案LCP和基准分支线RDL均可具有与栅极电极GE相同的材料,但不限于此。

层间绝缘层101c可设置在第一基板100上以覆盖栅极电极GE和有源层ACT。层间绝缘层101c可将栅极电极GE与源极/漏极电极SD1和SD2电性绝缘(或隔离)。例如,层间绝缘层101c可包括SiOx、SiNx、SiON或其多层,但不限于此。

第一源极/漏极电极SD1可设置在与有源层ACT的第一源极/漏极区域交叠的层间绝缘层101c上并且可通过设置在层间绝缘层101c中的第一源极/漏极接触孔电连接至有源层ACT的第一源极/漏极区域。例如,第一源极/漏极电极SD1可以是驱动TFT Tdr的源极电极,并且有源层ACT的第一源极/漏极区域可以是源极区域。

第二源极/漏极电极SD2可设置在与有源层ACT的第二源极/漏极区域交叠的层间绝缘层101c上并且可通过设置在层间绝缘层101c中的第二源极/漏极接触孔电连接至有源层ACT的第二源极/漏极区域。例如,第二源极/漏极电极SD2可以是驱动TFT Tdr的漏极电极,并且有源层ACT的第二源极/漏极区域可以是漏极区域。

根据一实施方式的源极/漏极电极SD1/SD2可具有包括与栅极电极GE相同材料的单层结构或多层结构。例如,源极/漏极电极SD1/SD2可包括设置在层间绝缘层110c上的第一源极/漏极金属层和设置在第一源极/漏极金属层上的第二源极/漏极金属层。例如,第一源极/漏极金属层可包括钛(Ti)或钼-钛合金(MoTi)。第二源极/漏极金属层可包括铜(Cu)。在这种情况下,源极/漏极电极SD1/SD2可形成为Cu/MoTi或Cu/Ti的两层结构。

像素驱动线GL、DL、PL、RL、CPL、PSL、RDL和LCP之中的数据线DL、像素驱动电源线PL和基准电源线RL均可包括与源极/漏极电极SD1和SD2相同的材料,但不限于此。栅极控制线组GCL的每条线可包括与源极/漏极电极SD1和SD2相同的材料,但不限于此。

钝化层101d可设置在第一基板100的第一表面100a上以覆盖包括驱动TFT Tdr的像素电路PC。根据一实施方式的钝化层101d可包括SiOx、SiNx、SiON或其多层,但不限于此。

构成像素电路PC的第一开关TFT Tsw1和第二开关TFT Tsw2的每一个可与驱动TFTTdr一起形成,因而省略其详细描述。

根据一实施方式的电路层101可进一步包括遮光层101e,遮光层101e设置在构成像素电路PC的TFT Tdr、Tsw1和Tsw2的每一个的有源层ACT的下方。

遮光层(或遮光图案)101e可以以岛形状设置在第一基板100与有源层ACT之间。遮光层101e可被缓冲层101a覆盖。遮光层101e可阻挡通过第一基板100入射到有源层ACT上的光,由此防止或最小化由外部光导致的每个TFT的阈值电压变化。可选择地,遮光层101e可电连接至相应TFT的第一源极/漏极电极SD1,因而可用作相应TFT的下栅极电极,在这种情况下,可最小化或防止由光导致的每个TFT的特征变化和由偏置电压导致的每个TFT的阈值电压变化。

此外,遮光层101e可用作像素驱动线GL、DL、PL、RL、CPL、PSL、RDL和LCP之中的电源共用线PSL、线连接图案LCP和基准分支线RDL中的至少之一。

图3、图5和图6中所示的栅极驱动电路150可与像素电路PC的驱动TFT Tdr一起形成。例如,构成栅极驱动电路150的级电路单元1501至150m的每一个的多个TFT可与驱动TFTTdr一起形成,因而可实现设置在第一基板100上的每个水平行中的多个分支电路1511至151n。构成级电路单元1501至150m的每一个的分支网153的第一至第四控制节点Q、QBo、QBe和Qm可与栅极线GL一起形成。此外,基于要连接的分支电路1511至151n的每一个的连接部分的位置,构成级电路单元1501至150m的每一个的分支网153的网线可与遮光层101e、栅极线GL和数据线DL中的至少之一一起形成,但不限于此。

平坦化层102可设置在第一基板100的第一表面100a上并且可在电路层101上提供平坦表面。平坦化层102可覆盖包括设置在多个像素区域PA的每一个中的驱动TFT Tdr的电路层101。根据一实施方式的平坦化层102可包括丙烯酸树脂、环氧树脂、酚醛树脂、聚酰胺树脂或聚酰亚胺树脂,但不限于此。

根据一实施方式的平坦化层102可形成为覆盖除了第一基板100的第一表面100a的边缘部分之外的电路层101。因此,设置在第一基板100的第一表面100a的边缘部分处的电路层101的钝化层101d可暴露而未被平坦化层102覆盖。

发光器件层103可设置在平坦化层102上并且可基于顶部发光型朝向第一基板100的第一表面100a发射光。

根据一实施方式的发光器件层103可包括像素电极PE、发光器件ED和公共电极CE。

像素电极PE可称为发光器件ED的阳极电极、反射电极、下电极、或第一电极。

像素电极PE可设置在与多个像素区域PA的每一个的发光区域EA交叠的平坦化层102上。像素电极PE可被图案化并以岛形状设置在每个像素区域PA中并且可电连接至相应像素电路PC的驱动TFT Tdr的第一源极/漏极电极SD1。像素电极PE的一侧可从像素区域PA的发光区域EA延伸至设置在电路区域CA中的驱动TFT Tdr的第一源极/漏极电极SD1,并且可通过设置在平坦化层102中的接触孔CH电连接至驱动TFT Tdr的第一源极/漏极电极SD1。

根据一实施方式的像素电极PE可包括功函数较低并且反射效率优良的金属材料。

例如,像素电极PE可具有包括第一至第三像素电极层的三层结构。第一像素电极层可用作对应于平坦化层102的粘合层并且可用作发光器件ED的辅助电极,而且第一像素电极层可包括氧化铟锡(ITO)或氧化铟锌(IZO)。第二像素电极层可用作反射器并且可执行降低像素电极PE的电阻的功能,而且第二像素电极层可包括铝(Al)、银(Ag)、Mo、Ti和MoTi中的一种材料。第三像素电极层可用作发光器件ED的电极并且可包括ITO或IZO。例如,根据一实施方式的像素电极PE可形成为IZO/MoTi/ITO或ITO/MoTi/ITO的三层结构。

作为另一示例,像素电极PE可具有包括第一至第四像素电极层的四层结构。第一像素电极层可用作对应于平坦化层102的粘合层并且可用作发光器件ED的辅助电极,而且第一像素电极层可包括ITO、Mo和MoTi中的一种材料。第二像素电极层可执行降低像素电极PE的电阻的功能并且可包括Cu。第三像素电极层可用作反射器并且可包括Al、Ag、Mo、Ti和MoTi中的一种材料。第四像素电极层可用作发光器件ED的电极并且可包括ITO或IZO。例如,根据另一实施方式的像素电极PE可形成为ITO/Cu/MoTi/ITO的四层结构。

可选择地,像素驱动线GL、DL、PL、RL、CPL、PSL、RDL和LCP之中的线连接图案LCP可与像素电极PE一起由相同材料形成,但不限于此。此外,设置在第一基板100上的第一焊盘部110的第一焊盘可与像素电极PE一起由相同材料形成,但不限于此。

发光器件ED可形成在像素电极PE上并且可直接接触像素电极PE。发光器件ED可以是共同地形成在多个子像素SP的每一个中而不以子像素SP为单位进行区分的公共层。发光器件ED可对在像素电极PE与公共电极CE之间流动的电流做出响应,从而发射白色光。根据一实施方式的发光器件ED可包括有机发光器件或无机发光器件,或者可包括有机发光器件(或无机发光器件)和量子点发光器件的堆叠或组合结构。

根据一实施方式的有机发光器件可包括用于发射白色光的两个或更多个发光材料层(或发光部分)。例如,有机发光器件可包括基于第一光和第二光的组合发射白色光的第一发光材料层和第二发光材料层。在此,第一发光材料层可包括蓝色发光材料、绿色发光材料、红色发光材料、黄色发光材料和黄绿色发光材料中的至少之一。第二发光材料层可包括用于发射与第一光组合而产生白色光的第二光的蓝色发光材料、绿色发光材料、红色发光材料、黄色发光材料和黄绿色发光材料中的至少之一。

根据一实施方式的有机发光器件可进一步包括用于提高发光效率和/或寿命的一个或多个功能层。例如,功能层可设置在发光材料层上方和/或下方。

根据一实施方式的无机发光器件可包括半导体发光二极管、微型发光二极管或量子点发光二极管。例如,当发光器件ED是无机发光器件时,发光器件ED可具有1μm至100μm的大小,但不限于此。

公共电极CE可称为发光器件ED的阴极电极、透明电极、上电极或第二电极。公共电极CE可形成在发光器件ED上并且可直接接触发光器件ED或者可电性地直接接触发光器件ED。公共电极CE可包括透射从发光器件ED发射的光的透明导电材料。

根据一实施方式的公共电极CE可形成为包括功函数相对较高的石墨烯或透明导电材料中的至少一种材料的单层结构或多层结构。例如,公共电极CE可包括诸如ITO或IZO之类的金属氧化物,或者可包括氧化物和金属的组合,比如ZnO:Al或SnO

另外,可在公共电极CE上进一步设置通过调节从发光器件ED发射的光的折射率来提高光的发射效率的覆盖层(capping layer)。

堤部104可设置在平坦化层102上,以覆盖像素电极PE的边缘部分。堤部104可限定多个子像素SP的每一个的发光区域EA(或开口部分)并且可将设置在相邻子像素SP中的像素电极PE电性隔离。堤部104可形成为覆盖设置在多个像素区域PA的每一个中的接触孔CH。堤部104可被发光器件ED覆盖。

例如,堤部104可包括透明材料(例如,丙烯酸树脂、环氧树脂、酚醛树脂、聚酰胺树脂或聚酰亚胺树脂),在这种情况下,堤部104可以是透明堤部。

作为另一示例,堤部104可包括包含诸如炭黑之类的黑色颜料的吸光材料或不透明材料,并且例如可包括聚酰亚胺树脂、丙烯酸树脂或苯并环丁烯(BCB),在这种情况下,堤部104可以是防止或最小化相邻子像素SP之间的颜色混合的黑色堤部。

堰图案105可设置在第一基板100的边缘部分处的电路层101上,以具有闭环形状或闭环线形状。例如,堰图案105可设置在电路层101的钝化层101d上。堰图案105可防止封装层106的扩散或溢出。堰图案105可包括在多个像素P(或多个像素区域PA)之中的设置在第一基板100的边缘部分处的最外侧像素Po(或最外侧像素区域PAo)内。在这种情况下,堰图案105的一部分可设置(或实现)在设置于第一基板100中的第一焊盘部110与每个最外侧像素Po(或最外侧像素区域PAo)的发光区域EA之间。

根据一实施方式的堰图案105可与平坦化层102一起包括相同的材料。堰图案105可具有与平坦化层102相同的高度(或厚度),或者可具有比平坦化层102高的高度。例如,堰图案105的高度(或厚度)可以是平坦化层102的高度(或厚度)的两倍。

根据另一实施方式,堰图案105可包括与平坦化层102一起由相同材料形成的下部堰图案、和堆叠在下部堰图案上并且包括与堤部104相同材料的上部堰图案。下部堰图案可具有与平坦化层102相同的高度(或厚度),或者可具有比平坦化层102高的高度。例如,下部堰图案的高度(或厚度)可以是平坦化层102的高度(或厚度)的两倍。

包括有机发光器件的发光器件ED可仅实现在被堰图案105围绕的内部区域(或内侧区域)中。就是说,包括有机发光器件的发光器件ED可设置在第一基板100的第一表面100a中的、除了第一基板100的外表面OS与堰图案105之间的部分以外的部分处,可不设置在第一基板100的外表面OS与堰图案105之间以及不形成在堰图案105的顶表面上。此外,发光器件层103的公共电极CE可实现为覆盖发光器件ED和堰图案105。

根据一实施方式的第一基板100可进一步包括第一裕度区域(margin area)MA1、第二裕度区域MA2和堰图案区域DPA。

第一裕度区域MA1可设置在最外侧像素Po的发光区域EA与堰图案105之间。基于在形成发光器件ED的工艺中不可避免出现的发光器件ED的荫罩区域(shadow area)(或发光器件的尾部),第一裕度区域MA1可在最外侧像素Po的发光区域EA(或堤部104)的端部与堰图案105之间具有第一宽度。因此,堰图案105可实现为相对于第一方向X,与发光区域EA的端部分隔开第一裕度区域MA1的第一宽度。

第二裕度区域MA2可设置在第一基板100的外表面OS与堰图案105之间。基于发光器件ED抵抗水分的可靠性裕度,第二裕度区域MA2可在第一基板100的外表面OS与堰图案105之间具有第二宽度。因此,堰图案105可实现为相对于第一方向X,与第一基板100的外表面OS分隔开第二裕度区域MA2的第二宽度。

根据一实施方式的第二裕度区域MA2可包括与设置在第一基板100的第一表面100a的第一边缘部分处的第一焊盘部110交叠的焊盘裕度区域。

堰图案区域DPA可设置在第一裕度区域MA1与第二裕度区域MA2之间。堰图案区域DPA可具有与最下底表面(或底表面)的宽度对应的第三宽度。

第一裕度区域MA1、第二裕度区域MA2和堰图案区域DPA的每一个的宽度可实现为使得相对于第一方向X,最外侧像素的中心部分与第一基板100的外表面OS之间的第二间隔D2是两个相邻像素区域PA之间的第一间隔(或像素间距)D1的一半或更小。

例如,当在加工误差范围内,两个相邻像素区域PA之间的第一间隔(或像素间距)D1的一半是700μm时,根据基于发光器件ED的荫罩区域而设置的荫罩裕度和基于确保发光器件ED抵抗水分的可靠性而设置的封装裕度,第一裕度区域MA1、第二裕度区域MA2和堰图案区域DPA的总宽度可实现为大约670μm。在这种情况下,在加工误差范围内,第一基板100的最外侧外表面VL与包括第一焊盘部110的最外侧像素的中心部分之间的第二间隔D2可实现为700μm。在此,第一基板100的最外侧外表面VL可以是显示设备(或显示面板)的最外部外侧壁或外侧壁。

第一裕度区域MA1和第二裕度区域MA2可具有相同的宽度或不同的宽度。堰图案区域DPA可具有比第一裕度区域MA1和第二裕度区域MA2的每一个相对较窄的宽度。例如,相对于第一方向X,第一裕度区域MA1可实现为具有300μm或更小的宽度,第二裕度区域MA2可实现为具有300μm或更小的宽度,并且堰图案区域DPA可实现为具有70μm的宽度。此外,相对于第一方向X,第二裕度区域MA2中包括的焊盘裕度区域(或侧向布线区域)可实现为具有100μm或更小的宽度。

阻挡图案部分BPP可实现在第一基板100的边缘部分处。阻挡图案部分BPP可防止侧向方向的水分渗透,由此防止由侧向的水分渗透导致的发光器件ED的劣化。阻挡图案部分BPP可隔离(或断开)发光器件层103,以防止侧向的水分渗透并且提高封装层106的封装可靠性。

根据本发明的发光器件ED可由于经由第一基板100的侧表面的水分渗透而劣化或可靠性降低。为了防止这种问题,阻挡图案部分BPP可实现为在堰图案105的外围处隔离(或断开)发光器件层103的发光器件ED,由此防止或最小化由侧向的水分渗透导致的发光器件ED的可靠性降低。因此,阻挡图案部分BPP可被定义为凹槽图案部分、沟槽图案部分、隔离部分、或水分渗透防止部分。

此外,根据本发明的TFT可由于从外围材料层流入的氢而发生特征变化。为了防止这种问题,阻挡图案部分BPP可实现为包括用于收集氢的材料,由此防止TFT的特征因氢渗透而变化。

阻挡图案部分BPP可实现在第一基板100的外表面OS与堰图案105之间的电路层101中。例如,阻挡图案部分BPP可实现在电路层101的钝化层101d中。作为另一示例,阻挡图案部分BPP可实现在电路层101的钝化层101d和层间绝缘层101c中。将在下面描述阻挡图案部分BPP。

封装层106可设置在第一基板100的第一表面100a的除了最外侧边缘部分以外的部分上,以覆盖发光器件层103。例如,封装层106可实现为围绕发光器件层103的前表面和侧表面的全部。

根据一实施方式的封装层106可包括第一至第三封装层106a至106c。

第一封装层106a可实现为防止氧气或水分渗透到发光器件层103中。第一封装层106a可设置在公共电极CE上,以围绕发光器件层103。因此,发光器件层103的前表面和侧表面的全部可被第一封装层106a围绕。例如,第一封装层106a的端部可设置在与堰图案105相邻的第二裕度区域MA2中。第一封装层106a可直接接触堰图案105的外围处的钝化层101d的顶表面并且可覆盖公共电极CE与钝化层101d之间的边界部分(或界面),由此防止或最小化侧向的水分渗透。

根据一实施方式的第一封装层106a可包括无机材料。例如,第一封装层106a可称为第一无机封装层。例如,第一封装层106a可包括包含硅氧化物(SiOx)、硅氮化物(SiNx)、氮硅氧化物(SiONx)、钛氧化物(TiOx)和铝氧化物(AlOx)之一的单层结构或其堆叠结构。

第二封装层106b可实现在第一封装层106a上,以具有比第一封装层106a相对更厚的厚度。第二封装层106b可具有足以覆盖第一封装层106a上存在或不存在的颗粒(或不希望的材料或不希望的结构)的厚度。由于相对较厚的厚度,第二封装层106b可能扩散至第一基板100的第一表面100a的边缘部分,但是第二封装层106b的扩散可被堰图案105阻挡。例如,第二封装层106b的端部可直接接触堰图案105上的第一封装层106a。因此,第二封装层106b可仅设置在被堰图案105围绕的内部区域(或内侧区域)中的第一封装层106a上。第二封装层106b可称为颗粒覆盖层。

根据一实施方式的第二封装层106b可包括诸如SiOCz丙烯酸或环氧基树脂之类的有机材料。

第三封装层106c可实现为主要防止氧气或水分渗透到发光器件层103中。第三封装层106c可实现为围绕第二封装层106b和未被第二封装层106b覆盖的第一封装层106a的全部。例如,第三封装层106c的端部可设置在第一封装层106a的端部与第一基板100的外表面OS之间并且可直接接触钝化层101d。第三封装层106c可直接接触钝化层101d的顶表面并且可覆盖第一封装层106a与钝化层101d之间的边界部分(或界面),由此附加地防止或最小化侧向的水分渗透。

根据一实施方式的第三封装层106c可包括无机材料。例如,第三封装层106c可称为第二无机封装层。例如,第三封装层106c可包括包含SiOx、SiNx、SiONx、TiOx和AlOx之一的单层结构或其堆叠结构。

根据一实施方式的第一基板100可进一步包括波长转换层107。

波长转换层107可转换从多个像素区域PA的每一个的发光区域EA入射的光的波长。例如,波长转换层107可将从发光区域EA入射的白色光转换为与相应像素P对应的彩色光。

根据一实施方式的波长转换层107可包括多个波长转换图案107a和保护层107b。

多个波长转换图案107a可设置在位于多个像素区域PA的每一个的发光区域EA中的封装层106上。多个波长转换图案107a可划分(或分类)为将白色光转换为红色光的红色滤光器、将白色光转换为绿色光的绿色滤光器、和将白色光转换为蓝色光的蓝色滤光器。例如,多个波长转换图案107a可划分(或分类)为设置在第一子像素SP1中的红色滤光器(或第一滤光器)、设置在第二子像素SP2中的绿色滤光器(或第二滤光器)、和设置在第四子像素SP4中的蓝色滤光器(或第三滤光器)。

根据一实施方式的多个波长转换图案107a的每一个可实现为具有比多个像素区域PA的每一个的发光区域EA宽的尺寸。就是说,为了防止相邻子像素SP之间的颜色混合,多个波长转换图案107a的每一个可具有与像素电极PE相同的尺寸或者可具有比像素电极PE宽的尺寸,因而可与覆盖像素电极PE的边缘部分的堤部104的一部分交叠。例如,多个波长转换图案107a的每一个可设置成与多个像素区域PA的每一个的整个发光区域EA交叠并且与和发光区域EA相邻的电路区域CA的一部分交叠。在这种情况下,为了防止通过多个像素区域PA的每一个中的不与波长转换图案107a交叠的区域入射的外部光被像素驱动线反射或者最小化外部光的反射,堤部104可包括吸光材料或黑色颜料。

根据另一实施方式,多个波长转换图案107a的每一个可实现为具有与多个像素区域PA的每一个相同的尺寸。就是说,多个波长转换图案107a的每一个可设置成与多个像素区域PA的每一个整个交叠,用来防止或最小化由像素驱动线导致的外部光的反射。例如,多个波长转换图案107a的每一个可设置成覆盖多个像素区域PA的每一个的发光区域EA和电路区域CA。在这种情况下,堤部104可以是黑色堤部或透明堤部。

另外,多个波长转换图案107a的每一个可包括量子点,量子点用于基于从发光器件层103入射的白色光或蓝色光重新发射光,以附加地照射与相应像素对应的彩色光。在此,量子点可选自CdS、CdSe、CdZnSeS、CdTe、ZnS、ZnSe、GaAs、Gap、GaAs-P、Ga-Sb、InAs、InP、InSb、AlAs、AlP和AlSb之中。例如,设置在第一子像素SP1中的红色滤光器可包括诸如发射红色光的CdSe或InP之类的红色量子点,设置在第二子像素SP2中的绿色滤光器可包括诸如发射绿色光的CdZnSeS之类的绿色量子点,设置在第四子像素SP4中的蓝色滤光器可包括诸如发射蓝色光的ZnSe之类的蓝色量子点。如上所述,当多个波长转换图案107a的每一个包括量子点时,发光显示设备的颜色再现性可增强。

根据另一实施方式,多个波长转换图案107a可实现为在多个像素区域PA的每一个的电路区域CA中彼此交叠。在这种情况下,多个像素区域PA的每一个的电路区域CA可被彼此交叠的至少两个波长转换图案107a覆盖。例如,多个像素区域PA的每一个的电路区域CA可被包括红色滤光器和绿色滤光器的两层堆叠部分覆盖。作为另一示例,多个像素区域PA的每一个的电路区域CA可被包括红色滤光器、绿色滤光器和蓝色滤光器的三层堆叠部分覆盖。包括两个滤光器的两层堆叠部分或包括三个滤光器的三层堆叠部分可执行用于防止相邻子像素SP之间的颜色混合或防止或最小化外部光的反射的黑矩阵的功能。

保护层107b可实现为覆盖波长转换图案107a并且在波长转换图案107a上提供平坦表面。保护层107b可设置成覆盖波长转换图案107a和其中未设置波长转换图案107a的封装层106。根据一实施方式的保护层107b可包括有机材料。例如,保护层107b可包括丙烯酸树脂、环氧树脂、酚醛树脂、聚酰胺树脂或聚酰亚胺树脂,但不限于此。可选择地,保护层107b可进一步包括用于吸收水分和/或氧气的吸气材料。

可选择地,波长转换层107可变为具有片形式的波长转换片并且可设置在封装层106上。在这种情况下,波长转换片(或量子点片)可包括设置在一对膜之间的波长转换图案107a。例如,当波长转换层107包括用于重新发射子像素中设定的彩色光的量子点时,子像素的发光器件层103可实现为发射白色光或蓝色光。

根据一实施方式的第一基板100可进一步包括功能膜108。

功能膜108可设置在波长转换层107上。例如,功能膜108可通过透明粘合构件接合至波长转换层107。透明粘合构件可包括压敏粘合剂(PSA)、光学透明粘合剂(OCA)或光学透明树脂(OCR)。

根据一实施方式的功能膜108可包括用于防止外部光的反射的抗反射层(或抗反射膜),以提高关于由显示设备10显示的图像的户外可视性和对比度。例如,抗反射层可包括用于防止被设置在第一基板100上的TFT和/或像素驱动线反射的外部光传播到外部的圆偏振层(或圆偏振膜)。

根据一实施方式的功能膜108可进一步包括用于主要防止水分或氧气的渗透的阻挡层(或阻挡膜),阻挡层可包括水分透过率较低的材料(例如,聚合物材料)。

根据一实施方式的功能膜108可进一步包括用于控制从每个像素P输出到外部的光的路径的光路控制层(或光路控制膜)。光路控制层可包括其中高折射率层和低折射率层交替堆叠的堆叠结构并且可改变从每个像素P入射的光的路径,以将基于视角的色偏(color shift)最小化。

根据一实施方式的第一基板100可进一步包括侧面密封构件109。

侧面密封构件(或边缘密封构件)109可形成在第一基板100与功能膜108之间并且可覆盖电路层101、平坦化层102和波长转换层107的每一个的所有侧(或侧向)表面。就是说,侧面密封构件109可覆盖在功能膜108与第一基板100之间的、暴露在显示设备10外部的电路层101、平坦化层102和波长转换层107的每一个的侧表面的全部。此外,侧面密封构件109可覆盖通过倒角工艺形成(或设置)在第一基板100的第一表面100a和外表面OS之间的拐角部分处的第一倒角(chamfer)100c。例如,第一基板100的最外侧外表面、侧面密封构件109的外表面、和功能膜108的外表面的每一个可设置(或对齐)在同一垂直线VL上。

根据一实施方式的侧面密封构件109可包括硅基或紫外(UV)可固化密封剂(或树脂),但考虑到节拍工时(tack process time),侧面密封构件109可包括UV可固化密封剂。此外,侧面密封构件109可具有颜色(例如,蓝色、红色、蓝绿色或黑色),但不限于此,并且侧面密封构件109可包括用于防止侧向的光泄漏的彩色树脂或阻光树脂。侧面密封构件109可通过使用从每个子像素SP的发光器件ED发射的光之中的、从波长转换层107的内部传播到其外表面的光,来防止侧向的光泄漏。特别是,与第一基板100的第一焊盘部交叠的侧面密封构件109可防止或最小化由第一焊盘部中的焊盘导致的外部光的反射。

可选择地,侧面密封构件109可进一步包括用于吸收水分和/或氧气的吸气材料。

根据一实施方式的第一基板100可进一步包括前涂层。

前涂层可设置在波长转换层107与功能膜108之间,以覆盖波长转换层107的顶表面并且覆盖电路层101、平坦化层102和波长转换层107的每一个的侧表面的全部。就是说,前涂层可实现为覆盖在功能膜108与第一基板100之间的、暴露在显示设备10外部的电路层101、平坦化层102和波长转换层107的每一个的侧表面的全部,并且可实现为覆盖与第一基板100的第一焊盘部连接的布线部分400的顶表面和侧表面的每一个的一部分。根据一实施方式的前涂层可通过原子层沉积工艺实现。例如,前涂层可实现为具有几μm的厚度。

在本实施方式中,侧面密封构件109可实现为覆盖第一基板100的第一表面100a的边缘部分处的前涂层,或者可省略侧面密封构件109。

根据一实施方式的第二基板200可包括与布线部分400连接的金属图案层和将金属图案层绝缘的绝缘层。

金属图案层(或导电图案层)可包括多个金属层。根据一实施方式的金属图案层可包括第一金属层201、第二金属层203和第三金属层205。绝缘层可包括多个绝缘层。例如,绝缘层可包括第一绝缘层202、第二绝缘层204和第三绝缘层206。绝缘层可称为后绝缘层或图案绝缘层。

第一金属层201可实现在第二基板200的后表面200b上。根据一实施方式的第一金属层201可包括第一金属图案。例如,第一金属层201可称为第一连接层或连线层。

根据一实施方式的第一金属图案可具有Cu和MoTi的两层结构(Cu/MoTi)。第一金属图案可用作图8中所示的连线部分250的连线。例如,第一金属图案可用作多条数据连线251、多条像素驱动电源连线255、多条栅极控制信号传输线、和像素公共电源连线257中的第一公共连线257a的每一条,但不限于此。

第一绝缘层202可实现在第二基板200的后表面200b上,以覆盖第一金属层201。根据一实施方式的第一绝缘层202可包括无机材料。例如,第一绝缘层202可包括SiOx、SiNx和SiONx中的一种材料,但不限于此。

第二金属层203可实现在第一绝缘层202上。根据一实施方式的第二金属层203可包括第二金属图案。例如,第二金属层203可称为第二连接层、跳接线层或桥接线层。

根据一实施方式的第二金属图案可具有Cu和MoTi的两层结构(Cu/MoTi)。第二金属图案可用作图9中所示的连线部分250的多条连线中的多条栅极连线253,但不限于此。例如,第二金属层203可用作用于将连线部分250中的由不同金属材料形成在不同层上的连线电连接的跳接线(或桥接线)。

可选择地,设置在第二金属层203上的连线(例如,多条第一连线)可改型为设置在第一金属层201上,并且设置在第一金属层201上的连线(例如,多条第二连线)可改型为设置在第二金属层203上。

第二绝缘层204可实现在第二基板200的后表面200b上,以覆盖第二金属层203。根据一实施方式的第二绝缘层204可包括无机材料。例如,第二绝缘层204可包括SiOx、SiNx和SiONx中的一种材料。

第三金属层205可实现在第二绝缘层204上。根据一实施方式的第三金属层205可包括第三金属图案。例如,第三金属层205可称为第三连接层或焊盘电极层。

根据一实施方式的第三金属图案可具有ITO(或IZO)、Mo、Ti和MoTi中的至少两种材料的堆叠结构。例如,第三金属图案可具有ITO/Mo/ITO、ITO/MoTi/ITO、IZO/Mo/ITO或IZO/MoTi/ITO的三层结构。第三金属图案可用作图8中所示的第二焊盘部210的第二焊盘、第三焊盘部230的第三焊盘、以及像素公共电源连线257中的第二公共连线257b和多条第三公共连线257c的每一种。

第三绝缘层206可实现在第二基板200的后表面200b上,以覆盖第三金属层205。根据一实施方式的第三绝缘层206可包括有机材料。例如,第三绝缘层206可包括诸如光学丙烯酸之类的绝缘材料。第三绝缘层206可覆盖第三金属层205,以防止第三金属层205暴露在外部。第三绝缘层206可称为有机绝缘层、保护层、后保护层、有机保护层、后涂层或后覆盖层。

第三绝缘层206可进一步包括焊盘暴露孔,焊盘暴露孔暴露包括第三金属层205的第二焊盘部210的第二焊盘和第三焊盘部230的第三焊盘的每一个的一部分。

接合构件300可设置在第一基板100与第二基板200之间。因此,第一基板100和第二基板200可通过接合构件300彼此相对地接合。根据一实施方式的接合构件300可以是包括OCA或OCR的透明粘合构件或双面胶带。根据另一实施方式,接合构件300可包括玻璃纤维。

根据一实施方式的接合构件300可设置在第一基板100与第二基板200之间的整个空间中。例如,第一基板100的整个第二表面100b可接合至接合构件300的整个一个表面,并且第二基板200的整个前表面200a可接合至接合构件300的整个另一个表面。

根据另一实施方式,接合构件300可以以图案结构设置在第一基板100与第二基板200之间。例如,接合构件300可具有线图案结构或网图案结构。网图案结构可进一步包括用于在第一基板100接合至第二基板200的工艺中将在第一基板100与第二基板200之间出现的气泡排放到外部的弯折部分。

可选择地,接合构件300可进一步包括传热元件。在这种情况下,接合构件300可通过传热元件将第一基板100中产生的热量传输至第二基板200,以防止或最小化第一基板100的温度升高。第二基板200可用作防止或最小化第一基板100的温度升高的降温构件。例如,传热元件可包括包含金属材料的多个传热颗粒或传热层。当传热元件包括包含金属材料的传热层时,传热层可电性接地或浮置,因而可用作噪声阻挡层,用于防止设置在第二基板200的后表面200b上的驱动电路中产生的频率噪声或静电流入设置在第一基板100上的像素、像素驱动线和栅极驱动电路150中。

图13是沿图3中所示的线II-II’截取的剖面图,其是描述根据本发明的显示设备的第一焊盘部、第二焊盘部和布线部分的剖面结构的示图。在描述图13时,与图3的元件相同或对应的元件由相同的参考标记表示,并且在下面省略或将简要给出其重复描述。

参照图3、图4和图11至图13,在根据本发明的显示设备10中,第一焊盘部110可包括设置在第一基板100的第一表面100a的第一边缘部分处的多个第一焊盘111。多个第一焊盘111可划分(或分类)为多个第一数据焊盘、多个第一像素驱动电源焊盘、和多个第一像素公共电源焊盘。此外,多个第一焊盘111可进一步划分(或分类)为多个第一基准电源焊盘。

多个第一焊盘111的每一个可通过设置在平坦化层102中的第一焊盘接触孔电连接至多条像素驱动线中的相应线。例如,第一数据焊盘可通过设置在平坦化层102中的第一焊盘接触孔电连接至数据线DL的一端。

在根据本发明的显示设备10中,第二焊盘部210可包括设置在第二基板200的后表面200b中的、与第一焊盘部110交叠的第一边缘部分处的多个第二焊盘211。多个第二焊盘211可划分(或分类)为多个第二数据焊盘、多个第二像素驱动电源焊盘、和多个第二像素公共电源焊盘。此外,多个第二焊盘211可进一步划分(或分类)为多个第二基准电源焊盘。

多个第二焊盘211的每一个可通过设置在第一绝缘层202和第二绝缘层204的每一个中的第二焊盘接触孔电连接至连线部分250中的、包括设置在第二基板200的后表面200b上的第一金属层201或第二金属层203的连线。例如,第二数据焊盘可通过设置在第一绝缘层202和第二绝缘层204的每一个中的第二焊盘接触孔电连接至数据连线251的一端。

布线部分400可设置成围绕第一基板100的外表面OS和第二基板200的外表面OS。例如,布线部分400可设置在第一基板100的外表面OS中的第一外表面(或一个表面)OS1a和第二基板200的外表面OS中的第一外表面(或一个表面)OS1b的每一个上。

根据一实施方式的布线部分400可包括设置在第一基板100的外表面OS中的第一外表面(或一个表面)OS1a和第二基板200的外表面OS中的第一外表面(或一个表面)OS1b的每一个上的多条布线401。多条布线401可划分(或分类)为多条数据布线、多条栅极布线、多条像素驱动电源布线、和多条像素公共电源布线。此外,多条布线401可进一步划分(或分类)为多条基准电源布线。

多条布线401的每一条可形成为围绕第一基板100的第一外表面OS1a和第二基板200的第一外表面OS1b的每一个。例如,多条布线401的每一条可通过使用导电胶的印刷工艺形成。例如,多条布线401的每一条可通过使用Ag胶的印刷工艺形成,但不限于此。

在多条布线401的每一条中,其一个端部可围绕设置在第一基板100的第一边缘部分处的第一焊盘部110的第一焊盘111和第一倒角100c,其另一个端部可围绕设置在第二基板200的第一边缘部分处的第二焊盘部210的第二焊盘211和第二倒角200c,并且在一个端部与另一个端部之间的中心部分可围绕第一基板100的第一外表面OS1a和第二基板200的第一外表面OS1b的每一个。例如,在数据布线410中,其一个端部可实现为围绕设置在第一基板100的第一边缘部分处的第一焊盘部110的第一数据焊盘和第一倒角100c,其另一个端部可实现为围绕设置在第二基板200的第一边缘部分处的第二焊盘部210的第二数据焊盘和第二倒角200c,并且在一个端部与另一个端部之间的中心部分可实现为围绕第一基板100的第一外表面OS1a和第二基板200的第一外表面OS1b的每一个。

可选择地,当接合构件300包括传热元件时,接合构件300的与第一基板100的第一外表面OS1a最靠近的端部301可与第一基板100的第一外表面OS1a和/或第二基板200的第一外表面OS1b分隔开以便不电连接至多条布线401的每一条,因而可不电连接至多条布线401的每一条或者可与多条布线401的每一条电性隔离。在这种情况下,多条布线401的每一条的一部分可进入第一基板100与第二基板200之间的区域,因而可基于进入第一基板100与第二基板200之间的区域的布线401的中心部分的进入长度(或距离),设定包括传热元件的接合构件300与第一基板100的第一外表面OS1a之间的分离距离。

根据本发明一实施方式的布线部分400可进一步包括边缘涂层403。

边缘涂层403可实现为覆盖多条布线401。根据一实施方式的边缘涂层403可实现为除了多条布线401以外还覆盖第一基板100的第一外表面OS1a和第一边缘部分以及第二基板200的第一外表面OS1b和第一边缘部分的全部。边缘涂层403可防止包括金属材料的多条布线401的每一条的腐蚀或多条布线401之间的电性短路。此外,边缘涂层403可防止或最小化由多条布线401和第一焊盘部110的第一焊盘111导致的外部光的反射。根据一实施方式的边缘涂层403可包括包含黑色油墨的遮光材料。

覆盖第一基板100的第一倒角100c的边缘涂层403的顶表面可被侧面密封构件109覆盖。

边缘涂层的外表面可以是第一基板100的最外侧外表面,因而第一基板100的最外侧外表面、侧面密封构件109的外表面和功能膜108的外表面的每一个可设置在同一垂直线VL上。

图14是图13中所示的区域“E”的放大图,其是用于描述根据本发明的阻挡图案部分的示图。

参照图11、图13和图14,根据本发明一实施方式的阻挡图案部分BPP可实现为围绕堰图案105。阻挡图案部分BPP可实现为围绕堰图案105的闭环形状(或闭环线形状)。阻挡图案部分BPP可设置在位于第一基板100的多个像素区域PA之中的最外侧像素区域PAo内。例如,阻挡图案部分BPP可设置在第一基板100的外表面OS与堰图案105之间的第二裕度区域MA2中。

根据一实施方式的阻挡图案部分BPP可包括阻挡金属图案BMP。阻挡金属图案BMP可设置在电路层101中。阻挡金属图案BMP可包括用于收集氢的材料。例如,阻挡金属图案BMP可形成为包括Ti和MoTi中至少之一的单层结构或多层结构。阻挡金属图案BMP可与栅极线或数据线设置在相同层上。

根据一实施方式的阻挡图案部分BPP可包括实现在电路层101的钝化层101d中的底切区域UCA。底切区域UCA可称为用于隔离(或断开)发光器件ED的屋檐部分、夹子(clip)结构、或隔离结构。在不使用单独切割(或隔离)工艺的情况下,底切区域UCA可实现为用来隔离(或断开)发光器件层103。例如,底切区域UCA可实现为隔离(或断开)发光器件层103的公共电极CE和发光器件ED的每一个。

根据一实施方式的底切区域UCA可实现在阻挡金属图案BMP上。例如,底切区域UCA可实现在阻挡金属图案BMP与钝化层101d之间。例如,底切区域UCA可实现在阻挡金属图案BMP与钝化层101d之间的边界部分处。

根据一实施方式的阻挡图案部分BPP可包括第一阻挡图案部分BPP1和第二阻挡图案部分BPP2。

第一阻挡图案部分BPP1可实现为围绕堰图案105。例如,第一阻挡图案部分BPP1可实现为在第一基板100的外表面OS与堰图案105之间围绕堰图案105的闭环形状(或闭环线形状)。

第二阻挡图案部分BPP2可实现为围绕第一阻挡图案部分BPP1。例如,第二阻挡图案部分BPP2可实现为在第一基板100的外表面OS与第一阻挡图案部分BPP1之间围绕第一阻挡图案部分BPP1的闭环形状(或闭环线形状)。

根据一实施方式的第一阻挡图案部分BPP1和第二阻挡图案部分BPP2的每一个可包括阻挡金属图案BMP、空隙部分(void portion)VP、空隙开口部分VOP和底切区域UCA。

阻挡金属图案BMP可实现在电路层101中。根据一实施方式的阻挡金属图案BMP可设置在电路层101的层间绝缘层110c上。阻挡金属图案BMP可直接接触层间绝缘层110c的顶表面。阻挡金属图案BMP可与TFT的源极/漏极电极SD1/SD2(或数据线DL)设置在相同层上。例如,阻挡金属图案BMP可包括与具有两层结构的源极/漏极电极SD1/SD2的第一源极/漏极金属层相同的Ti或MoTi。阻挡金属图案BMP可包括用于吸收并存储氢的Ti,因而可收集氢,以防止TFT的特征因氢渗透而变化。

空隙部分VP可实现在阻挡金属图案BMP上。例如,空隙部分VP可设置在阻挡金属图案BMP与钝化层101d之间。

根据一实施方式的空隙部分VP的高度可与具有两层结构的源极/漏极电极SD1/SD2的第二源极/漏极金属层的高度相同。例如,可通过去除堆叠在阻挡金属图案BMP上的第二源极/漏极金属层的蚀刻工艺来形成空隙部分VP。因此,根据一实施方式的空隙部分VP可实现在钝化层101d中,以具有与在堆叠在阻挡金属图案BMP上之后通过蚀刻工艺被去除的第二源极/漏极金属层相同的洞穴(或隧道)形状。例如,在阻挡图案部分BPP中,设置在阻挡金属图案BMP上的第二源极/漏极金属层可在制造显示设备的工艺中用作用于形成空隙部分VP的牺牲层。

空隙开口部分VOP可实现为暴露空隙部分VP的上部。例如,在去除堆叠在阻挡金属图案BMP上的第二源极/漏极金属层的工艺中,空隙开口部分VOP可实现为用来提供路径,其中蚀刻剂通过此路径进入第二源极/漏极金属层中。

根据一实施方式的空隙开口部分VOP可实现为沿垂直方向Z穿过钝化层101d的与阻挡金属图案BMP交叠的部分,因而可与空隙部分VP连通,以暴露空隙部分VP的一部分。例如,可通过经由蚀刻工艺去除堆叠在阻挡金属图案BMP上的第二源极/漏极金属层来实现根据一实施方式的空隙部分VP。因此,空隙开口部分VOP可暴露被钝化层101d覆盖的第二源极/漏极金属层的一部分,由此能够通过蚀刻工艺去除第二源极/漏极金属层。

底切区域UCA可实现在阻挡金属图案BMP的两个边缘部分与钝化层101d之间。例如,底切区域UCA可实现在阻挡金属图案BMP的两个边缘部分与设置在空隙开口部分VOP附近的钝化层101d之间,从而底切区域UCA在其间具有空隙部分VP的情况下彼此面对。底切区域UCA可被定义为空隙部分VP的两个边缘部分。

在不使用单独切割(或隔离)工艺的情况下,底切区域UCA可实现为用来隔离(或断开)发光器件层103。例如,底切区域UCA可实现为隔离(或断开)发光器件层103的公共电极CE和发光器件ED的每一个。

可选择地,根据另一实施方式,阻挡金属图案BMP可设置在电路层101的栅极绝缘层GI上。阻挡金属图案BMP可直接接触栅极绝缘层GI的顶表面。阻挡金属图案BMP可与TFT的栅极电极(或栅极线GL)设置在相同层上。例如,阻挡金属图案BMP可包括与具有两层结构的栅极电极GE的第一栅极金属层相同的Ti或MoTi,因而可收集氢,由此防止TFT的特征因氢渗透而变化。

此外,根据另一实施方式,空隙部分VP可具有与具有两层结构的栅极电极GE的第二栅极金属层的高度相同的高度。例如,可通过去除堆叠在阻挡金属图案BMP上的第二栅极金属层的蚀刻工艺来形成空隙部分VP。因此,根据另一实施方式的空隙部分VP可实现在层间绝缘层101c中,以具有与在堆叠在阻挡金属图案BMP上之后通过蚀刻工艺被去除的第二栅极金属层相同的洞穴(或隧道)形状。例如,在阻挡图案部分BPP中,设置在阻挡金属图案BMP上的第二栅极金属层可在制造显示设备的工艺中用作用于形成空隙部分VP的牺牲层。

此外,根据另一实施方式,空隙开口部分VOP可实现为沿垂直方向Z穿过钝化层101d和层间绝缘层101c的与阻挡金属图案BMP交叠的部分,因而可与空隙部分VP连通,以暴露空隙部分VP。例如,可通过经由蚀刻工艺去除堆叠在阻挡金属图案BMP上的第二栅极金属层来实现根据另一实施方式的空隙部分VP。因此,根据另一实施方式的空隙开口部分VOP可暴露被层间绝缘层101c和钝化层101d覆盖的第二栅极金属层的一部分,由此能够通过蚀刻工艺去除第二栅极金属层。

根据另一实施方式,底切区域UCA可实现在阻挡金属图案BMP的两个边缘部分与层间绝缘层101c之间。例如,底切区域UCA可实现在阻挡金属图案BMP的两个边缘部分与设置在空隙开口部分VOP附近的层间绝缘层101c之间,从而底切区域UCA在其间具有空隙部分VP的情况下彼此面对。

阻挡图案部分BPP可隔离(或断开)设置在第一基板100上的发光器件层103的发光器件ED。例如,沉积在阻挡图案部分BPP上的发光器件ED可在第一阻挡图案部分BPP1的空隙部分VP或底切区域UCA中被隔离(或断开)。因此,发光器件ED可在沉积工艺中被第一阻挡图案部分BPP1自动隔离(或断开),因而,在根据本实施方式的显示设备中,即使在没有将发光器件ED隔离(或断开)的单独图案化工艺的情况下,也可仅通过对发光器件ED执行的沉积工艺来隔离(或断开)发光器件ED,从而防止侧向的水分渗透。

此外,阻挡图案部分BPP可隔离(或断开)设置在第一基板100上的发光器件层103的公共电极CE。例如,沉积在阻挡图案部分BPP上的公共电极CE可在第一阻挡图案部分BPP1和第二阻挡图案部分BPP2的每一个的空隙部分VP或底切区域UCA中被隔离(或断开)。因此,公共电极CE可在沉积工艺中被第一阻挡图案部分BPP1和第二阻挡图案部分BPP2自动隔离(或断开)。此外,设置在第一裕度区域MA1和第二裕度区域MA2中的公共电极CE可围绕阻挡图案部分BPP处的发光器件ED的隔离表面,因而可防止经由钝化层101d与发光器件ED之间的边界部分的侧向水分渗透,由此防止发光器件ED的可靠性因侧向的水分渗透而降低。

根据一实施方式的阻挡图案部分BPP可包括第一岛图案EDi和第二岛图案CEi。

第一岛图案EDi可与设置在第一基板100上的发光器件ED一起由相同的材料形成。根据一实施方式的第一岛图案EDi可设置在第一阻挡图案部分BPP1的阻挡金属图案BMP上。

第一岛图案EDi可包括以岛形状与设置在第一基板100上的发光器件ED隔离(或断开)的发光器件材料层(或发光器件图案)。例如,在形成阻挡图案部分BPP的工艺之后,可在第一基板100的第一表面100a中的除了边缘部分以外的部分上沉积发光器件ED。因为发光器件ED的材料直线性较强,所以沉积在第一阻挡图案部分BPP1上的发光器件ED的材料可设置在除了底切区域UCA之外的钝化层101d和阻挡金属图案BMP上。

在第一阻挡图案部分BPP1中,由于底切区域UCA,沉积在阻挡金属图案BMP上的发光器件ED的材料可以以岛形状与沉积在钝化层101d上的发光器件ED的材料分隔(或断开),由此实现第一岛图案EDi。

第二岛图案CEi可与设置在第一基板100上的公共电极CE一起由相同的材料形成。根据一实施方式的第二岛图案CEi可设置在第一阻挡图案部分BPP1的第一岛图案EDi上并且可设置在第二阻挡图案部分BPP2的阻挡金属图案BMP上。

第二岛图案CEi可包括以岛形状与设置在第一基板100上的公共电极CE隔离(或断开)的公共电极材料层(或公共电极图案)。例如,在形成发光器件ED的工艺之后,可在第一基板100的第一表面100a中的除了边缘部分以外的部分上沉积公共电极CE。沉积在第一阻挡图案部分BPP1上的公共电极CE的材料可设置在除了底切区域UCA之外的第一岛图案EDi和发光器件ED上。

在第一阻挡图案部分BPP1中,由于底切区域UCA,沉积在第一岛图案EDi上的公共电极CE的材料可以以岛形状与沉积在发光器件ED上的公共电极CE的材料隔离(或断开),由此实现第二岛图案CEi。

此外,沉积在第二阻挡图案部分BPP2上的公共电极CE的材料可设置在除了底切区域UCA之外的钝化层101d和阻挡金属图案BMP上。因此,在第二阻挡图案部分BPP2中,由于底切区域UCA,沉积在阻挡金属图案BMP上的公共电极CE的材料可以以岛形状与沉积在钝化层101d上的公共电极CE的材料隔离(或断开),由此实现第二岛图案CEi。

阻挡图案部分BPP可被上述封装层106围绕。

封装层106可围绕被阻挡图案部分BPP隔离(或断开)的发光器件ED和公共电极CE的每一个的侧表面(或隔离表面)。根据一实施方式的封装层106可填充到阻挡图案部分BPP的空隙开口部分VOP和空隙部分VP中,以密封或完全围绕阻挡图案部分BPP,因而可完全围绕或覆盖被隔离的发光器件ED和公共电极CE的每一个的侧表面(或隔离表面),由此在根本上(或完全)防止侧向的水分渗透。例如,阻挡图案部分BPP可被封装层106的第一封装层106a和第三封装层106c围绕。

设置在阻挡图案部分BPP上的封装层106的第一封装层106a可设置成围绕(或完全围绕)设置在阻挡图案部分BPP中的第二岛图案CEi和公共电极CE的隔离图案的每一个。例如,由于第一阻挡图案部分BPP1和第二阻挡图案部分BPP2的每一个的底切区域UCA,设置在第二岛图案CEi上的第一封装层106a可以以岛形状与设置在公共电极CE的隔离图案上的第一封装层106a隔离(或断开),由此实现第三岛图案106ai。

设置在阻挡图案部分BPP上的封装层106的第三封装层106c可实现为完全围绕设置在阻挡图案部分BPP上的第一封装层106a。在这种情况下,第三封装层106c可设置在阻挡图案部分BPP上从而连续地连接在一起而没有被第一阻挡图案部分BPP1和第二阻挡图案部分BPP2的每一个的底切区域UCA隔离(或断开)。在这种情况下,基于第一阻挡图案部分BPP1和第二阻挡图案部分BPP2的每一个中实现的空隙部分VP的尺寸,第三封装层106c可填满空隙部分VP或仅填充空隙部分VP的一部分。

图15是图解图3中所示的第二基板的后表面的示图,其图解了在图1至图14中所示的显示设备的第二基板上进一步设置面板支撑构件的实施方式。在描述图15时,与图1至图14的元件相同或对应的元件由相似的参考标记表示,并且在下面省略或将简要给出其重复描述。

参照图3和图15,根据本发明一实施方式的显示设备10可进一步包括设置在第二基板200的后表面200b上的面板支撑构件600。

面板支撑构件600可实现为支撑包括通过接合构件300彼此相对地接合(或耦接)的第一基板100和第二基板200的显示面板的后表面。面板支撑构件600可称为后盖、背盖或后方构件。

根据一实施方式的面板支撑构件600可包括支撑板610和多个紧固构件630。

支撑板610可连接至第二基板200的后表面200b,以支撑显示面板的后表面。支撑板610可设置成覆盖第二基板200的后表面200b中的除了第二焊盘部210和第三焊盘部230以外的部分,并且可支撑驱动电路单元500的印刷电路板(PCB)550。例如,支撑板610可通过诸如双面胶带之类的板接合构件接合至第二基板200的后表面200b。

支撑板610可包括金属材料。例如,支撑板610可包括Al、Al合金、Mg合金、Fe-Ni合金和不锈钢中的一种材料、其合金或接合结构,但不限于此。

根据一实施方式的支撑板610可包括其一侧的一部分被去除的用于暴露第三焊盘部230的凹部611。例如,当从上向下看时,支撑板610可具有“凹”或“┗┛”形状。在这种情况下,第二基板200的第三焊盘部230可通过支撑板610的凹部611在第二基板的向后方向上暴露。此外,附接在第二基板200的第三焊盘部230上的柔性电路膜510的另一边缘部分可覆盖支撑板610的凹部611与第二基板200之间的台阶部分并且可电连接至被支撑板610支撑的PCB 550。

根据另一实施方式,支撑板610可包括用于暴露第三焊盘部230的开口孔。例如,支撑板610可包括具有四边形形状并且具有比第三焊盘部230相对较大的尺寸的四边形开口孔,此四边形形状覆盖第二基板200的后表面200b中的除了第二焊盘部210以外的部分。例如,当从上向下看时,支撑板610可具有“回”形状。在这种情况下,第二基板200的第三焊盘部230可通过支撑板610的开口孔在第二基板的向后方向上暴露出来。此外,附接在第二基板200的第三焊盘部230上的柔性电路膜510的另一边缘部分可穿过支撑板610的开口孔并且可电连接至被支撑板610支撑的PCB 550。

多个紧固构件630可设置在支撑板610的后表面上。例如,多个紧固构件630可设置成接触支撑板610的每个拐角部分并且可从支撑板610的后表面突出一定长度。

根据一实施方式的多个紧固构件630的每一个可包括从其前表面凹进凹入地实现的紧固槽631。

多个紧固构件630的每一个可通过诸如螺丝或螺栓之类的固定构件固定至支撑板610的后表面。例如,固定构件可穿过紧固构件630的紧固槽631并且可紧固至支撑板610的后表面,因而可将紧固构件630的后部固定至支撑板610的后表面。

根据一实施方式的多个紧固构件630的每一个可包括可被磁铁磁化的材料。根据另一实施方式,多个紧固构件630的每一个可与支撑板610的后表面利用其间的磁铁块接合。例如,磁铁块可以是钕磁铁。

多个紧固构件630可分别紧固至设置在支撑显示设备的后框架单元中的多个紧固销。例如,紧固构件630可基于磁力接合至设置在后框架单元中的紧固销。因此,根据本发明的显示设备10可安装在后框架单元上。此外,安装在后框架单元上的多个显示设备10可沿第一方向X和第二方向Y中的至少一个方向连续铺设,因而可实现多屏显示设备或可无限延伸的显示设备。在此,后框架单元可称为后方结构、显示器支撑单元、铺设单元(tilingunit)、铺设结构、柜(cabinet)单元、模块柜单元或柜结构。此外,多屏显示设备可称为多面板显示设备、多屏幕显示设备或铺设显示设备。

另外,根据本发明一实施方式的显示设备10可进一步包括电路盖。电路盖可接合至面板支撑构件600的后表面,以覆盖暴露在面板支撑构件600的后表面处的驱动电路单元500,因而可保护驱动电路单元500免受外部冲击并且可保护驱动电路单元500免受静电。根据一实施方式的电路盖可包括具有用于覆盖暴露在面板支撑构件600的后表面处的驱动电路单元500的形状的金属材料。例如,电路盖可称为屏蔽盖(cover shield)。

图16是图解根据本发明一实施方式的多屏显示设备的示图,图17是图解图16中所示的显示设备的铺设工艺的示图,图18是沿图16中所示的线III-III’截取的剖面图。

参照图16至图18,根据本发明一实施方式的多屏显示设备可包括多个显示模块10-1至10-4和多个后框架单元30-1至30-4。