具有内埋电子元件的电路板及其制造方法

文献发布时间:2023-06-19 11:54:11

技术领域

本发明涉及一种具有内埋电子元件的电路板及其制造方法。

背景技术

內埋式电路板将电子元件(如电阻、电容等)嵌埋在电路基板的内部以减少电路板的整体尺寸,从而满足用户对电子产品轻、薄、小的追求。

现有技术中,內埋式电路板的制作过程通常包括捞型、压合等制程。其中,捞型尺寸及精度对电路板有重要的影响,捞型尺寸太大,空旷区域加大,会影响后续产品的可靠性,捞型的尺寸太小,会出现压合偏位,导致电子元件破损。其次电子元件是在埋入后再通过形成导电盲孔进行线路连接,导电盲孔和电子元件之间容易造成精度不佳,导致连接不良。

发明内容

有鉴于此,本发明提供一种具有内埋电子元件的电路板的制造方法。

另外,本发明还提供一种由以上制造方法制得的电路板。

一种电路板的制造方法,包括步骤:

提供一第一电路基板,所述第一电路基板包括一第一基材层及形成于所述第一基材层表面的第一线路层。

在所述第一线路层上安装一电子元件。

提供一第二电路基板,所述第二电路基板包括一第二基材层、形成于所述第二基材层表面的第二线路层及形成于所述第二线路层的第一导电柱。

在所述第二线路层上形成一与所述第二线路层电性连接的第一导电柱,所述第一导电柱的高度大于所述电子元件的高度。

提供一绝缘层,将具有所述第一导电柱的所述第二电路基板和具有所述电子元件的所述第一电路基板分别层叠于所述绝缘层相对的两侧,使得所述第一导电柱和所述电子元件均朝向所述绝缘层且所述第一导电柱与所述电子元件错开,从而得到一中间体。以及压合所述中间体,使得所述第一导电柱穿过所述绝缘层并电连接于所述第一线路层,并使得电子元件内埋于所述绝缘层,从而获得所述电路板。

进一步地,所述第一电路基板的制造步骤包括:

提供一覆铜基板,所述覆铜基板包括所述第一基材层和形成于所述单元基材层相对两侧的铜箔层;

在所述覆铜基板中开设贯穿的开孔,蚀刻每一所述铜箔层以形成所述第一线路层;以及

在所述开孔内进行镀铜以获得电性连接两个所述第一线路层的第二导电柱。

进一步地,形成所述第一导电柱具体包括:

在所述第二线路层上设置一干膜层,所述干膜层与所述第二导电柱对应的区域以形成一开槽;

于所述开槽内进行电镀以形成所述第一导电柱;以及

移除所述干膜层。

进一步地,所述绝缘层选自半固化片、油墨、聚酰亚胺、纯胶、背胶铜箔以及ABF材料中的一种。

进一步地,所述电子元件通过一导电胶层安装并电连接于所述第一线路层。

进一步地,所述导电胶层包含胶体和填充于所述胶体中的金属粉体,所述金属粉体选自铜、银以及金中的一种或多种。

进一步地,所述第二电路基板的结构与所述第一电路基板相同。

进一步地,所述电子元件包括电阻、电容以及电子芯片中的一种或多种。

进一步地,所述第一导电柱与所述第一线路层电性连接。

一种电路板,包括:

一第一电路基板,包括一第一基材层及形成于所述第一基材层表面的第一线路层。

一电子元件,安装于所述第一线路层上。

一第二电路基板,包括一第二基材层及形成于所述第二基材层表面的第二线路层,其中,所述第二线路层上形成有一与所述第二线路层电性连接的第一导电柱,所述第一导电柱的高度大于所述电子元件的高度。以及

一绝缘层,连接于所述第一电路基板与所述第二电路基板之间。

其中,所述第一导电柱穿过所述绝缘层并电连接于所述第一线路层,所述第一导电柱与所述电子元件错开,所述电子元件内埋于所述绝缘层。

本发明提供的电路板的制造方法具有以下优点:

1.可大幅的降低成本并且能够准确地将电子元件固定在所述电路板内部。且电子元件是在压合之前通过导电胶层粘接到第一电路基板上,使得电子元件安装位置有所偏差时能进行重工作业。

2.压合之前不需要对电路板进行捞型,有利于提高对位精度。

3.一次压合即可完成,比起现有技术中需要两次压合,能够简化制程并降低成本。

可以理解的是,以上实施例仅用来说明本发明,并非用作对本发明的限定。对于本领域的普通技术人员来说,根据本发明的技术构思做出的其它各种相应的改变与变形,都落在本发明权利要求的保护范围之内。

附图说明

图1是本发明实施例提供的覆铜基板的剖视图。

图2是本发明实施例提供的第一电路基板的剖视图。

图3是图2所示第一电路基板刷一导电胶层后的剖视图。

图4是图3所示第一电路基板粘接电子元件后的剖视图。

图5是图2所示第一电路基板设置干膜层后开槽的剖视图。

图6是图5所示第一电路基板在开槽内镀铜后的剖视图。

图7是本发明实施例提供的第二电路基板的剖视图。

图8是压合图4中所示第一电路基板、图7中所示第二电路基板及所述增层体前的剖视图。

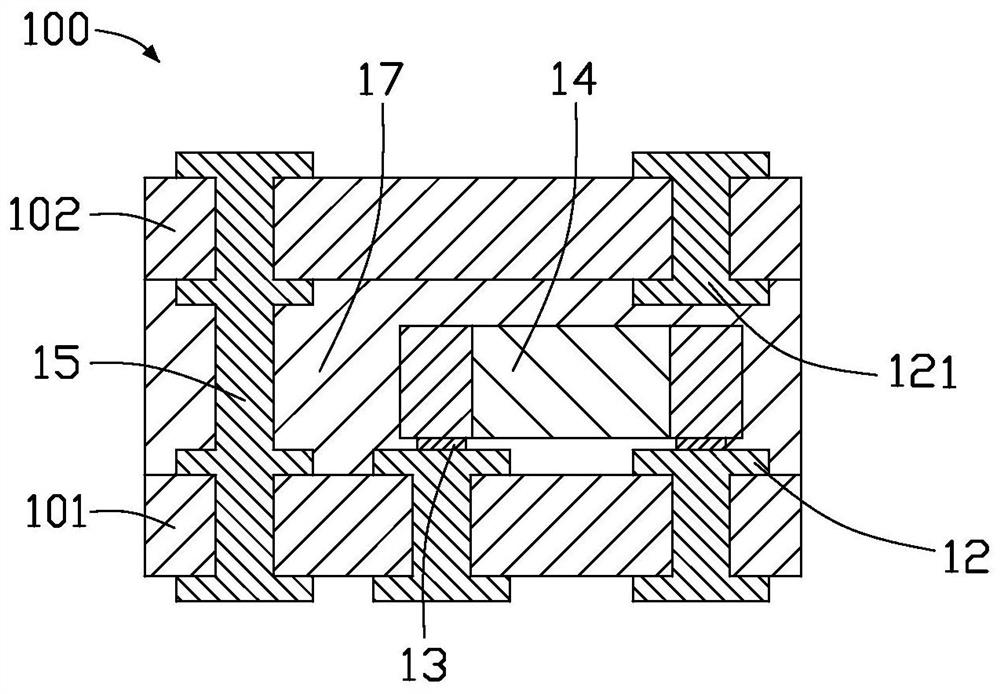

图9是本发明提供的电路板的剖视图。

主要元件符号说明

电路板 100

第一电路基板 101

第二电路基板 102

覆铜基板 10

基材层 11

第一线路层 12

第二线路层 121

导电胶层 13

电子元件 14

第一导电柱 15

干膜层 16

绝缘层 17

铜箔层 111

铜箔层 112

开孔 20

第二导电柱 21

如下具体实施方式将结合上述附图进一步说明本发明。

具体实施方式

下面将结合附图及实施例,对本技术方案提供的电路板100及其制造方法作进一步的详细说明。

请参阅图1至图9,本发明实施例提供一种内埋电子元件的电路板100的制造方法,包括如下步骤:

S1:请参见图2,提供一第一电路基板101,所述第一电路基板101包括一基材层11及形成于所述基材层11表面的至少一第一线路层12。

在本实施例中,步骤S1中所述第一电路基板101的制造具体步骤包括:

S10:请参见图1,提供一覆铜基板10,所述覆铜基板10包括一基材层11、形成于所述基材层11相对两侧的铜箔层111。

在本实施例中,所述基材层11为树脂层,如聚酰亚胺(Polyimide,PI)、聚对苯二甲酸乙二醇酯(Polyethylene Terephthalate,PET)或聚萘二甲酸乙二醇酯(PolyethyleneNaphthalate,PEN)。

S11:请一并参照图2,先于所述覆铜基板10中开设至少一贯穿的开孔20,在所述开孔20内进行镀铜以获得电性连接两个所述铜箔层111的多个第二导电柱21,对每一所述铜箔层111进行蚀刻以形成所述第一线路层12,并获得所述第一电路基板101。

在本实施例中,所述第一线路层12凸出形成于所述基材层11,在本发明的其他实施例中,可以通过内埋线路制程使得所述第一线路层12所述基材层11平齐。

S2:请参见图3,于一所述第一线路层12上形成一导电胶层13。

在本实施例中,所述导电胶层13包含胶体和填充于所述胶体中的金属粉体,所述金属粉体选自铜、银、金中的一种或多种。

S3:请参见图4,提供一电子元件14,将所述电子元件14设置在所述导电胶层13上以使得所述电子元件14与所述第一线路层12电性连接。

由于所述导电胶层13可低温硬化,同时导电胶层13具有粘性,通过导电胶层13电性连接所述电子元件14及所述第一线路层12不会出现立碑或回流等问题。

在本实施例中,步骤S3中,所述电子元件14通过所述导电胶层13设置在所述第二导电柱21对应的所述第一线路层12之上。

在本实施例中,步骤S3中,所述电子元件14包括电阻、电容、电子芯片等。

S4:请参见图7,提供一第二电路基板102,所述第二电路基板102包括一基材层11、形成于所述基材层11相对两表面的一第二线路层121,然后,在其中一所述第二线路层121上形成一第一导电柱15。

其中,所述第二电路基板102的结构可与所述第一电路基板101大致相同。

在本实施例中,步骤S4的形成所述第一导电柱15具体包括:

S41:请参见图5,于所述第一线路层12上设置一干膜层16。

其中,所述干膜层16于其中一所述第二导电柱21对应的区域开设有一开槽161,所述开槽161贯穿所述干膜层16。

S42:请参见图6,于所述开槽161内进行电镀以形成所述第一柱15。

在本实施例中,所述第一导电柱15的高度H1(参图7)与所述开槽161的深度D相同,且所述第一导电柱15的高度H1大于所述电子元件14的高度H2。

S42:请参见图7,移除所述干膜层16。

S5:请参见图8,提供一绝缘层17,将具有所述第一导电柱15的所述第二电路基板102和具有所述电子元件14的所述第一电路基板101分别层叠于所述绝缘层17相对的两侧,使得所述第一导电柱15和所述电子元件14均朝向所述绝缘层17且所述第一导电柱15与所述电子元件14错开,从而得到一中间体(图未标)。

在本实施例中,步骤S5中所述第一导电柱15朝向所述第一电路基板101的另一所述第二导电柱21。

在本实施例中,步骤S5中所述绝缘层17选自半固化片、油墨、聚酰亚胺、纯胶、背胶铜箔、ABF材料(Ajinomoto Build-up Film)或其他可以用于印刷电路板的介质材料。

S6:请参见图9,压合所述中间体以获得所述电路板100。由于所述第一导电柱15的高度H1大于所述电子元件14的高度H2,从而避免所述电子元件14在压合过程中被压坏。

在本实施例中,压合后,所述第一导电柱15与所述第一线路层12电性连接。

在本实施例中,步骤S6中,所述绝缘层17为半固化状态,压合后所述第一导电柱15穿过所述绝缘层17并与所述第一线路层12电性导通,从而使得所述第一电路基板101与所述第二电路基板102电性导通。

压合后,所述电子元件14和所述第二电路基板102朝向所述绝缘层17的一所述第二线路层121均内埋于所述绝缘层17。

请参阅图9,本发明还提供一种电路板100,包括一第一电路基板101、一第二电路基板102、设置于所述第一电路基板101及所述第二电路基板102之间的一电子元件14、填充于所述第一电路基板101及所述第二电路基板102之间除所述电子元件14以外的间隙的绝缘层17,所述第一电路基板101包括至少一第一线路层12,所述第二电路基板102包括至少一第二线路层121及凸出形成于所述第二线路层121的一个第一导电柱15,所述电子元件14通过一导电胶层13与所述第一电路基板101的所述第一线路层12电连接,所述第一导电柱15的高度大于所述电子元件14的高度且所述第一导电柱15与所述电子元件14错开。

本发明提供的电路板的制造方法具有以下优点:

1.可大幅的降低成本并且能够准确地将电子元件固定在所述电路板内部。且电子元件是在压合之前通过导电胶层粘接到第一电路基板上,使得电子元件安装位置有所偏差时能进行重工作业。

2.压合之前不需要对电路板进行捞型,有利于提高对位精度。

3.一次压合即可完成,比起现有技术中需要两次压合,能够简化制程并降低成本。

可以理解的是,以上实施例仅用来说明本发明,并非用作对本发明的限定。对于本领域的普通技术人员来说,根据本发明的技术构思做出的其它各种相应的改变与变形,都落在本发明权利要求的保护范围之内。

- 具有内埋电子元件的电路板及其制造方法

- 具有内埋电子元件的电路板及其制作方法