多模式电压泵和控制

文献发布时间:2023-06-19 11:55:48

背景技术

高数据可靠性、高速存储器存取、低功耗和减小的芯片尺寸是半导体存储器所要求的特征。在一些应用中,电路可以使用电势大于由外部电压源提供的电势的电源电压。举例来说,一些存储器电路可在存储器存取操作期间使用较高内部电压来激活存取线。可包括电压泵电路以生成较高的内部电压。在操作期间使用的外部电压供应量值与较高内部电压量值之间的差可随应用而变化。此外,电压泵电路的效率可基于工艺和温度差而变化。因此,电压泵电路可以被设计成提供足够的余量来考虑工艺、电压和温度变化,以便满足工作电压需求。然而,设计电压泵电路以在假设最坏情况的情况下操作可能在一些应用中导致浪费的功耗。

附图说明

图1是根据本公开的实施例的半导体装置的示意性框图。

图2是根据本公开的实施例的多模式电压泵的框图。

图3A-3C是根据本公开的实施例的模式控制电路的框图。

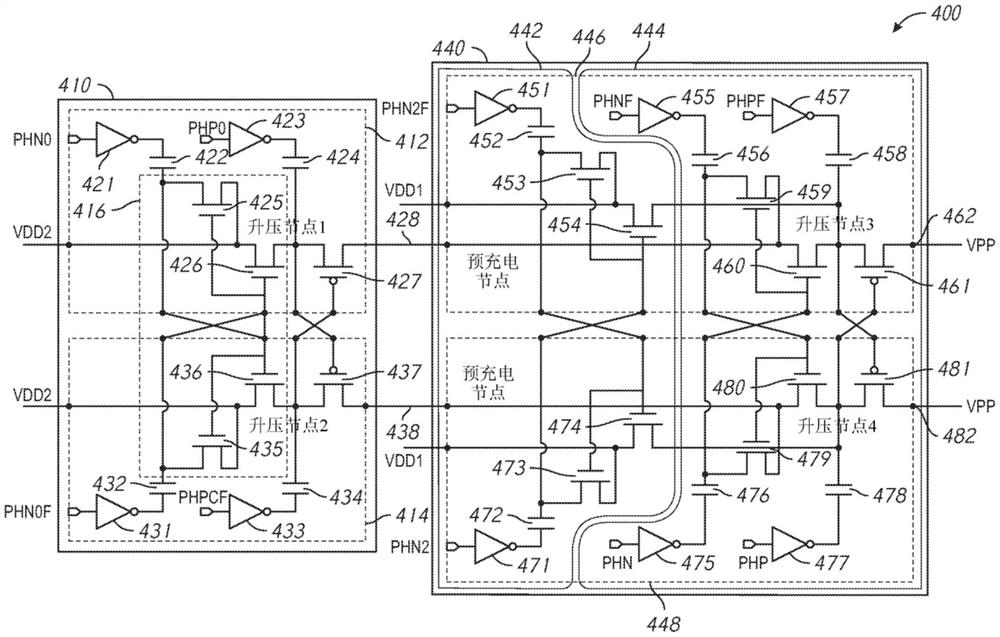

图4是根据本公开的实施例的多模式泵电路400的示意图。

图5A-5C是示范性时序图的图解,描绘了在根据本公开的实施例的多模式泵电路的各种操作模式下控制电压泵的控制信号转变。

具体实施方式

下面将参照附图详细解释本公开的各种实施例。以下详细描述参考附图,所述附图以说明的方式展示本公开的特定方面和实施例。详细描述包括足够的细节以使本领域技术人员能够实践本公开的实施例。可利用其它实施例,且可在不脱离本公开的范围的情况下作出结构、逻辑和电改变。本文所公开的各种实施例不必相互排斥,因为一些所公开的实施例可与一个或一个以上其它所公开的实施例组合以形成新实施例。

图1是根据本公开的实施例的作为存储器装置的半导体装置100的示意性框图。半导体装置100可包括时钟输入电路105、内部时钟生成器107、地址命令输入电路115、地址解码器120、命令解码器125、多个行(例如,第一存取线)解码器130,包括读出放大器150及转移栅极195的存储器单元阵列145、多个列(例如,第二存取线)解码器140、多个读取/写入放大器165、输入/输出(I/O)电路170及电压生成器电路190。半导体装置100可以包括多个外部端子,包括耦合到命令/地址总线(C/A)110的地址和命令端子、时钟端子CK和/CK、数据端子DQ、DQS和DM,以及电源端子VDD、VSS、VDDQ和VSSQ。在一些实例中,与命令/地址总线110相关联的端子和信号线可包括被配置为接收命令信号的第一组端子和信号线以及被配置为接收地址信号的单独的第二组端子和信号线。在其它实例中,与命令和地址总线110相关联的端子和信号线可包括被配置为接收命令信号和地址信号两者的共用端子和信号线。半导体装置可安装在衬底上,例如,存储器模块衬底、母板等。

存储器单元阵列145包括多个存储体BANK0-N,其中N是正整数,例如3、7、15、31等。每个存储体BANK0-N可以包括多个字线WL,多个位线BL和布置在多个字线WL和多个位线BL的交叉点处的多个存储器单元MC。每个存储体BANK0-N的字线WL的选择由相应的行解码器130执行,而位线BL的选择由相应的列解码器140执行。所述多个读出放大器150可针对其对应位线BL而定位且经由充当开关的转移栅极TG195而耦合到进一步耦合到相应主I/O线对(MIOT/B)的相应局部I/O线对(LIOT/B)。读出放大器150及转移栅极TG 195可基于来自解码器电路的控制信号而操作,所述解码器电路可包括命令解码器125、行解码器130、列解码器140、存储体BANK0-N的存储器单元阵列145的任何控制电路或其任何组合。

地址/命令输入电路115可经由命令/地址总线110在命令/地址端子处从外部接收地址信号和存储体地址信号,且将地址信号和存储体地址信号传输到地址解码器120。地址解码器120可以对从地址/命令输入电路115接收到的地址信号进行解码,并且向行解码器130提供行地址信号XADD,并且向列解码器140提供列地址信号YADD。地址解码器120还可接收存储体地址信号并将存储体地址信号BADD提供到行解码器130和列解码器140。

地址/命令输入电路115可经由命令/地址总线110在命令/地址端子处从外部(例如,存储器控制器)接收命令信号且将命令信号提供到命令解码器125。命令解码器125可解码命令信号且生成各种内部命令信号。举例来说,内部命令信号可包括用以选择字线的行命令信号,或用以选择位线的列命令信号(例如,读取命令或写入命令)。

因此,当发出读命令并且行地址和列地址被及时供给读命令时,从由行地址和列地址指定的存储器单元阵列145中的存储器单元读取读数据。读取/写入放大器165可以接收读取数据DQ,并将读取数据DQ提供给IO电路170。IO电路170可经由数据端子DQ将读取数据DQ与DQS处的读取数据选通信号一起提供到外部。类似地,当发出写入命令且及时与写入命令一起提供行地址和列地址时,输入/输出电路170可在数据端子DQ处接收写入数据,并且在DQS处一起接收写入数据选通信号,且在DM处接收数据掩码信号,且经由读取/写入放大器165将写入数据提供到存储器单元阵列145。因此,可以将写数据写入由行地址和列地址指定的存储器单元中。

转向对包括在半导体装置100中的外部端子的说明,时钟端子CK和/CK可以分别接收外部时钟信号和互补的外部时钟信号。外部时钟信号(包括互补的外部时钟信号)可以被提供给时钟输入电路105。时钟输入电路105可以接收外部时钟信号并生成内部时钟信号ICLK。时钟输入电路105可以向内部时钟生成器107提供内部时钟信号ICLK。内部时钟生成器107可以基于从地址/命令输入电路115接收到的内部时钟信号ICLK和时钟使能信号CKE来生成相位控制的内部时钟信号LCLK。尽管不限于此,但是DLL电路可以用作内部时钟生成器107。内部时钟生成器107可以向IO电路170提供相位控制的内部时钟信号LCLK。IO电路170可以使用相位控制器内部时钟信号LCLK作为用于确定读取数据的输出定时的定时信号。除了相位控制器内部时钟信号LCLK之外,内部时钟生成器可以生成用于存储器操作的各种内部时钟信号。

电源端子可以接收电源电压VDD和VSS。这些电源电压VDD和VSS可以提供给电压生成器电路190。电压生成器电路190可以基于电源电压VDD和VSS生成各种内部电压VPP、VOD、VARY、VPERI等。内部电压VPP主要用于行解码器130中,内部电压VOD和VARY主要用于包括在存储器单元阵列145中的读出放大器150中,内部电压VPERI用于许多其它电路块中。IO电路170可以接收电源电压VDDQ和VSSQ。例如,电源电压VDDQ和VSSQ可以分别是与电源电压VDD和VSS相同的电压。然而,专用电源电压VDDQ和VSSQ可用于IO电路170。

在一些实例中,电压生成器电路190包括被配置为提供VPP电压的多模式电压泵192。VPP可以是大于外部电源电压VDD的泵升电压。多模式电压泵192可以是被配置为基于温度以不同模式操作的多级电压泵电路。在一些实例中,多模式电压泵192能够以至少三种不同模式之一操作,包括单级模式、两级模式和混合级模式。多模式电压泵192可被配置为基于经由温度信号Temp接收的半导体装置的温度来选择操作模式。在一些实施例中,温度信号可以指示温度测量。在其它实例中,温度信号可以指示温度范围(例如,高、中、低等)。可在生产期间确定温度值范围的选定模式,因为每一半导体装置可经历VDD电压量值和VPP电压要求的差异,以及制造期间的工艺变化和由温度变化引起的操作差异。因此,可在半导体装置的生产测试期间确定选定模式编程的温度范围。在一些实例中,可在可编程元件组(例如,熔丝或反熔丝组电路)中对选定模式编程的温度范围进行编程。在一些实例中,可以针对每个温度范围对模式进行编程。举例来说,第一选定模式可经编程以用于第一温度范围(例如,低),第二选定模式可经编程以用于第二温度范围(例如,中等),第三选定模式可经编程以用于第三温度范围(例如,高)。在不脱离本公开的范围的情况下,可以限定另外的温度范围。在一些实例中,可针对一个以上温度范围或针对所有温度范围编程相同模式。多模式电压泵192的不同选定操作模式可提供具有不同电压量值的VPP电压。举例来说,多模式电压泵192可在使用两级的第一模式下操作,以提供第一VPP电压,多模式电压泵192可在使用单级的第二模式下操作,以提供第二VPP电压,且多模式电压泵192可在使用单级与两级的混合的第三模式下操作,以提供第三VPP电压。第三VPP电压可以在第一和第二VPP电压之间,第一VPP电压具有最大量值。多模式电压泵192的电路的控制信号定时可以基于振荡器信号OSC(例如,从诸如包括在时钟输入电路105中的振荡器电路之类的振荡器电路提供)。

图2是根据本公开的实施例的多模式电压泵292的框图。多模式电压泵292可以包括模式控制电路202,多模式控制电路204和多模式泵电路206。在一些实例中,多模式电压泵292可以包括在图1的多模式电压泵192中。

模式控制电路202可以被配置为接收温度信号Temp,并向多模式控制电路204提供模式控制信号Mode。在一些实施例中,温度信号可以指示温度测量。在该实例中,模式控制电路202可以包括将温度信号值转换为指示预定温度范围集(例如,低、中、高)之一的范围值的逻辑。例如,如果温度小于或等于第一(例如,低)温度阈值,则模式控制电路202将范围值设置为“低”。如果温度大于第一(例如,低)温度阈值并且小于或等于第二(例如,高)温度阈值,则模式控制电路202将范围值设置为“中”。如果温度大于第二(例如,高)温度阈值,则模式控制电路202将范围值设置为“高”。在不脱离本公开的范围的情况下,可实施多于或少于三个预定义范围。在其它实例中,温度信号可以直接提供范围值(例如,低、中、高等等)。模式控制电路202可以包括提供具有基于范围值的值的模式选择信号的逻辑。举例来说,模式控制电路202的逻辑可以基于范围值查找所选择的模式。在一些实例中,模式控制电路202可包括向选定模式编程提供温度范围的可编程元件(例如,熔丝或反熔丝)。例如,基于从可编程元件读取的值,模式控制电路202可以读取可编程元件以响应具有第一值的范围值选择第一模式,响应具有第二值的范围值选择第二模式,以及响应具有第三值的范围值选择第三模式。在其它实例中,基于从可编程元件读取的值,模式控制电路202可针对一个以上或所有范围值选择相同模式。编程到可编程元件中的值可基于VDD电压量值、VPP电压要求、包括多模式电压泵292的半导体装置(例如,图1的半导体装置100)的工艺变化和由温度变化引起的操作差异。

多模式控制电路204可以通过模式信号和振荡器信号OSC从模式控制电路202接收所选择的模式。多模式控制电路204可包括响应OSC信号的定时并基于所选模式向多模式泵电路206提供控制信号的逻辑。控制信号转换可以使多模式泵电路206的电路根据选择模式操作。多模式泵电路206可以包括多个级,并且可以被设计成以多种模式之一操作。可以基于来自多模式控制电路204的控制信号来控制所选择的模式。在一些实例中,模式可以包括两级,单级和混合级模式(例如,两级和单级的组合)。

图3A-3C是根据本公开的实施例的模式控制电路的框图。在一些实例中,图3A-3C的模式控制电路可以包括在图1的多模式电压泵192和/或图2的多模式控制电路204中。图3A包括时钟信号逻辑电路300,其被配置为接收振荡器信号(例如OSC、OSCF、OSC90和OSC90F)并提供时钟信号(例如PU、PUF、PU2和PU2F)。OSCF信号的值与OSC信号的值互补。OSC90F信号的值与OSC90信号的值互补。OSC90信号的值与OSC信号的值相位相差90度。时钟信号逻辑电路300包括NAND门301,其被配置为使用NAND逻辑,基于OSC和OSC90F信号的值来提供PU2信号。时钟信号逻辑电路300还包括NAND门302,其被配置为使用NAND逻辑,基于OSCF和OSC90信号的值来提供PU2F信号。时钟信号逻辑电路300还包括NAND门303,其被配置为使用NAND逻辑,基于OSC和OSC90信号的值来提供PU信号。时钟信号逻辑电路300还包括NAND门304,其被配置为使用NAND逻辑,基于OSCF和OSC90F信号的值来提供PUF信号。

图3B包括第一级控制逻辑电路1 310,第一级控制逻辑电路2 330和锁存电路305。锁存电路305可以是具有基于从第一级控制逻辑电路1 310和第一级控制逻辑电路2 330接收的输入信号控制的输出的锁存电路。图3B的电路被配置为基于从图3A的时钟信号逻辑电路300提供的PU2和PU2F信号的值来提供控制信号PHN0、PHN0F、PHP0和PHP0F。PHN0、PHN0F、PHP0和PHP0F控制信号可以被提供给多模式泵电路,例如图2的多模式泵电路206。第一级控制逻辑电路1 310包括第一串联的逻辑电路(例如,NAND门311,反相器312,反相器313,NOR门314和反相器315),第二串联的逻辑电路(例如,反相器316,反相器317和反相器318)和第三串联的逻辑电路(例如,反相器319和反相器320)。第一串联的逻辑电路可被配置为基于在NAND门311的输入端处接收的PU2信号及第一驱动信号DRVNAF(例如,来自第一级控制逻辑电路2 330的反相器333的输出端)及在NOR门314处从反相器317的输出端接收的信号而从反相器315提供PHN0F信号。第二串联的逻辑电路可被配置为基于在反相器316处接收的锁存电路305的第一输出而从反相器318提供PHP0信号。第三串联的逻辑电路可被配置为基于在反相器319处接收的PU2信号来控制锁存电路305的第一输入。第一串联的逻辑电路可进一步被配置为在反相器313的输出端处提供第二驱动信号DRVNBF。

第一级控制逻辑电路2 330包括第四串联的逻辑电路(例如,NAND门331,反相器332,反相器333,NOR门334和反相器335),第五串联的逻辑电路(例如,反相器336,反相器337和反相器338)和第六串联的逻辑电路(例如,反相器339和反相器340)。第四串联的逻辑电路可被配置为基于在NAND门331的输入端处接收的PU2F信号及DRVNBF信号(例如,来自第一级控制逻辑电路1 310的反相器313的输出端)及在NOR门334处从反相器337的输出端接收的信号而从反相器335提供PHN0信号。第五串联的逻辑电路可被配置为基于在反相器336处接收的锁存电路305的第二输出而从反相器338提供PHP0F信号。第六串联的逻辑电路可被配置为基于在329处接收的PU2F信号来控制锁存电路305的第二输入。第四串联的逻辑电路还可以被配置为在反相器333的输出端处提供DRVNAF信号。

图3C包括第二级控制逻辑电路1 350,第二级控制逻辑电路2 370和锁存电路306。锁存电路306可以是具有基于从第二级控制逻辑电路1 350和第二级控制逻辑电路2 370接收的输入信号控制的输出的锁存电路。图3C的电路被配置为基于从图3A的时钟信号逻辑电路300提供的PU和PUF信号的值来提供控制信号PHP、PHPF、PHN、PHNF、PHP2、PHP2F、PHN2和PHN2F。PHP、PHPF、PHN、PHNF、PHP2、PHP2F、PHN2和PHN2F控制信号可以被提供给多模式泵电路,例如图2的多模式泵电路206。第二级控制逻辑电路1 350包括第一串联的逻辑电路(例如,NAND门351,反相器352,反相器353,NOR门354和反相器355),第二串联的逻辑电路(例如,NAND门356,反相器357,反相器358,NOR门359和反相器360),第三串联的逻辑电路(例如,反相器363,反相器364和反相器365)和第四串联的逻辑电路(例如,反相器361和反相器362)。第一串联的逻辑电路可被配置为基于经由反相器366反相的PU2信号和在NAND门351的输入端处接收的VDD1电压以及在NOR门354处从反相器364的输出端处接收的信号,将来自反相器355的输出信号提供到XOR门390和多路复用器391。第二串联的逻辑电路可被配置为基于在NAND门356处接收的锁存电路306信号的PU、PUF和第二输出LOUT2以及在NOR门359处从NOR门354的输出端接收的信号而将来自反相器360的输出信号提供到XOR门390和多路复用器392。XOR门390的输出可以被提供给多路复用器391和多路复用器392,该输出具有基于来自反相器355的输出信号和来自反相器360的输出信号的值。响应于MODE信号的值,多路复用器391可被配置为在输出端处提供来自反相器355的输出信号(例如,混合级模式),XOR门390的输出(例如,单级模式)或浮动信号(例如,两级模式)中的一种作为PHN2F信号。响应于MODE信号的值,多路复用器392可被配置为在输出端处提供来自反相器360的输出信号(例如,混合级模式),XOR门390的输出(例如,两级模式)或浮动信号(例如,单级模式)中的一种作为PHNF信号。第三串联的逻辑电路可被配置为基于在反相器363处接收的锁存电路306的第一输出信号LOUT1来提供PHP信号。第四串联的逻辑电路可被配置为基于在反相器361处接收的PUF信号来控制锁存电路306的第一输入。

第二级控制逻辑电路2 370包括第五串联的逻辑电路(例如,NAND门371,反相器372,反相器373,NOR门374和反相器375),第六串联的逻辑电路(例如,NAND门376,反相器377,反相器378,NOR门379和反相器380),第七串联的逻辑电路(例如,反相器383,反相器384和反相器385)和第八串联的逻辑电路(例如,反相器381和反相器382)。第五串联的逻辑电路可被配置为基于经由反相器386反相的PUF信号和在NAND门371的输入端处接收的VDD1电压以及在NOR门374处从反相器384的输出端接收的信号,将来自反相器375的输出信号提供到XOR门393和多路复用器396。第六串联的逻辑电路可被配置为基于在NAND门376处接收的PU、PUF和LOUT1信号以及在NOR门379处从NOR门374的输出端接收的信号,将来自反相器380的输出信号提供到XOR门393和多路复用器395。XOR门393的反相(例如,经由反相器394)输出可被提供给多路复用器395和多路复用器396,该输出具有基于来自反相器375的输出信号和来自反相器380的输出信号的值。响应于MODE信号的值,多路复用器395可被配置为在输出端处提供来自反相器380的输出信号(例如,混合级模式),XOR门393的反相输出(例如,两级模式)或浮动信号(例如,单级模式)中的一种作为PHN信号。响应于MODE信号的值,多路复用器396可被配置为在输出端处提供来自反相器375的输出信号(例如,混合级模式),XOR门393的反相输出(例如,单级模式)或浮动信号(例如,两级模式)中的一种作为PHN2信号。第七串联的逻辑电路可被配置为基于在反相器383处接收的LOUT2信号提供PHPF信号。第八串联的逻辑电路可被配置为基于在反相器381处接收的PU信号来控制锁存电路306的第二输入。

图4是根据本公开的实施例的多模式泵电路400的示意图。在一些实例中,多模式泵电路400可以包括在图1的多模式电压泵192和/或图2的多模式泵电路206中。多模式泵电路400可被配置为从图3B和3C的逻辑电路接收PHP0、PHP0F、PHN0、PHN0F、PHP、PHPF、PHN、PHNF、PHP2、PHP2F、PHN2和PHN2F控制信号。

多模式泵电路400可以包括多级,包括第一级410和第二级440。第一级410可包括上部412和下部414。基于VDD2电压,上部412和下部414可被配置为响应于PHN0和PHP0信号以及PHN0F和PHP0F信号,分别交替地从输出节点428提供第一预充电电压和从输出节点438提供第二预充电电压。上部412可包括第一预充电电路(例如,反相器421、电容器422、n型晶体管425及n型晶体管426),其被配置为响应于PHN0信号而控制第一升压节点的预充电。上部412可进一步包括:第一升压电路(例如,反相器423及电容器424),其被配置为响应于PHP0信号而控制提供到第一升压节点的泵电压;及p型晶体管427,其被配置为将第一升压节点耦合到输出节点428。下部414可包括第二预充电电路(例如,反相器431、电容器432、n型晶体管435及n型晶体管436),其被配置为响应于PHN0F信号而控制第二升压节点的预充电。下部414可进一步包括:第二升压电路(例如,反相器433,电容器434),其被配置为响应于PHP0F信号而控制提供到第二升压节点的泵电压;及p型晶体管437,其被配置为将第二升压节点耦合到输出节点438。

第二级440可以包括第一电路442和第二电路444。上部446可以包括第一电路442的第一部分和第二电路444的第一部分。下部448可以包括第一电路442的第二部分和第二电路444的第二部分。在使用第一电路442和第二电路444的一部分的第一模式下(例如,经由PHN2、PHN2F、PHP和PHPF信号),基于VDD1电压,上部446和下部448可以被配置为响应于PHN2F和PHPF信号以及PHN2和PHP信号,分别交替地提供来自输出节点462的第一泵升电压和来自输出节点482的第二泵升电压,其具有等于VDD1电压两倍的值。在使用第一级410和第二电路444的第二模式下(例如,经由PHN0、PHN0F、PHP0、PHP0F、PHN、PHNF、PHP和PHPF信号),基于来自输出节点428和438的预充电电压,上部446和下部448可被配置为响应于PHN0、PHP0、PHNF和PHPF信号以及PHN0F、PHP0F、PHN和PHP信号,分别交替地提供来自输出节点462的第一泵升电压和来自输出节点482的第二泵升电压,其具有等于VDD1电压的两倍加上VDD2电压的值。

在上部446内,第一电路442可包括反相器451、电容器452、n型晶体管453及n型晶体管454,其被配置为响应于PHN2F信号,基于VDD1电压而控制第三升压节点的预充电。在上部446内,第二电路444可以包括第一预充电电路(例如,反相器455,电容器456、n型晶体管459和n型晶体管460),其被配置为响应于PHNF信号,基于来自输出节点428的预充电电压来控制第三升压节点的预充电。在上部446内,第二电路444可进一步包括:第一升压电路(例如,反相器457及电容器458),其被配置为响应于PHPF信号而控制提供到第三升压节点的泵电压;及p型晶体管461,其被配置为将第三升压节点耦合到输出节点462。下部414可包括反相器431、电容器432、n型晶体管435及n型晶体管436,其被配置为响应于PHN0F信号而控制第二升压节点的预充电。

在下部448内,第一电路442可包括反相器471、电容器472、n型晶体管473和n型晶体管474,其被配置为响应于PHN2信号,基于VDD1电压而控制第四升压节点的预充电。在下部448内,第二电路444可包括第二预充电电路(例如,反相器475,电容器476,n型晶体管479及n型晶体管480),其被配置为响应于PHN信号,基于来自输出节点438的预充电电压而控制第四升压节点的预充电。在下部448内,第二电路444可进一步包括:第二升压电路(例如,反相器477及电容器478),其被配置为响应于PHP信号而控制提供到第四升压节点的泵电压;及p型晶体管481,其被配置为将第四升压节点耦合到输出节点482。

在操作中,图3A-3C的电路可根据多模式泵电路400的选定操作模式提供控制信号(例如,PHN0、PHN0F、PHP0、PHP0F、PHN、PHNF、PHN2、PHN2F、PHP和PHPF信号)。多模式泵电路400可被配置为响应于控制信号而在选定操作模式下操作。在第一(例如,单级)模式下,可以使用第一电路442来控制来自输出节点462的第一泵升电压和来自输出节点482的第二泵升电压,以对第三和第四升压节点进行预充电,并且使用第二电路444的第一和第二升压电路来对第三和第四升压节点(例如,不包括第一级410和第二电路444的第一和第二预充电电路)进行升压。当在第一模式下操作时,来自输出节点462的第一泵升电压和来自输出节点482的第二泵升电压可具有为VDD1+VDD1电压的量值。在一些实例中,VDD1电压是1.8伏。

在第二(例如,两级)模式下,可以使用第一级410和第二电路444的第一和第二预充电电路来控制来自输出节点462的第一泵升电压和来自输出节点482的第二泵升电压,以对第三和第四升压节点进行预充电,并且使用第二电路444的第一和第二升压电路来对第三和第四升压节点(例如,不包括第一电路442)进行升压。在输出节点428和438处从第一级410提供的预充电电压可以具有与VDD2电压相加的VDD1电压的量值。当在第一模式下操作时,来自输出节点462的第一泵升电压和来自输出节点482的第二泵升电压可具有为VDD1+VDD1电压加上VDD2电压的量值。在一些实例中,VDD2电压是1伏。

在第三(例如,混合级)模式下,可以使用1)第一电路442和2)第一级410以及第二电路444的第一和第二预充电电路的组合来控制来自输出节点462的第一泵升电压和来自输出节点482的第二泵升电压,以对第三和第四升压节点进行预充电,并且使用第二电路444的第一和第二升压电路,以分别对第三和第四升压节点进行升压。举例来说,在在第二级440预充电阶段,第三和第四升压节点最初可以基于VDD1电压经由第一电路442预充电(例如,四分之一时钟周期),然后可以随后基于来自第一级410的预充电电压(例如,VDD1+VDD2)经由第二电路444的第一和第二预充电电路预充电(例如,四分之一时钟周期)。来自输出节点462的第一泵升电压和来自输出节点482的第二泵升电压可具有在第一模式下提供的电压与在第二模式下提供的电压之间的量值。

图5A-5C分别是示范性时序图500、501和502的图解,其描绘了在根据本公开的实施例的多模式泵电路的各种操作模式下控制电压泵的控制信号转变。时序图500、501和502可分别说明多模式控制器和多模式电压泵(例如图1的多模式电压泵192,图2的多模式控制电路204和多模式泵电路206,图3A-3B的电路和图4的多模式泵电路400)或其组合的操作。OSC和OSC90信号可分别对应于图3A的OSC和OSC90信号。PU、PUF、PU2和PU2F信号可以分别对应于图3A-3C的PU、PUF、PU2和PU2F信号。PHN0、PHP0、PHN2、PHN和PHP信号可以分别对应于图3B、3C和4的PHN0、PHP0、PHN2、PHN和PHP信号。Stg1升压节点和Stg升压节点信号可以分别对应于图4的升压节点1或升压节点2和升压节点3或升压节点4的电压。为了清楚起见,以下对时序图500、501和502的讨论可参考图3A-3B和图4的电路。具体地,在时序图500中描绘的PU、PUF、PU2和PU2F信号可以经由图3A的时钟信号逻辑电路300,基于OSC和OSC90(例如和互补)信号来生成。可经由图3B的第一级控制逻辑电路1 310,锁存电路305和第一级控制逻辑电路2 330生成时序图500、501和502中所描绘的PHN0和PHP0信号。可经由图3C的第二级控制逻辑电路1 350,锁存电路306和第二级控制逻辑电路2 370生成时序图500、501和502中所描绘的PHN2、PHN和PHP信号。

图5A的时序图500描绘在多模式泵电路的混合级操作模式下控制电压泵的控制信号转变。在时间T1处,多模式泵电路(例如,多模式泵电路400)的第一级(例如,第一级410)可响应于转变到低逻辑电平的PHN0信号(例如,分别控制反相器421和电容器422)而开始预充电操作。PHN0信号的转变可以基于图3的时钟信号逻辑电路300。预充电操作可包括经由电容器424将(例如,第一级410的)Stg1升压节点的电压预充电到VDD2电压。

在时间T2处,多模式泵电路的第一级可响应于PHP0信号转变到高逻辑电平而开始升压操作。升压操作可以包括经由电容器424将Stg1升压节点的电压充电到VDD1+VDD2电压。

在时间T3处,多模式泵电路(例如,多模式泵电路400)的第二级(例如,第二级440)可响应于PHN2信号(例如,控制反相器471)转变到低逻辑电平而开始预充电操作的第一部分。预充电操作的第一部分可以包括经由电容器478将Stg2升压节点的电压预充电到VDD1电压。

在时间T4处,多模式泵电路的第二级可响应于PHN2信号转变到高逻辑电平且PHN信号(例如,控制反相器475)转变到低逻辑电平而开始预充电操作的第二部分。预充电操作的第二部分可以包括经由电容器478将Stg2升压节点的电压预充电到Stg 1升压节点电压(例如,来自输出节点428或438的VDD1+VDD2电压)。第二级预充电操作的第一和第二部分的每一个可以具有OSC信号的时钟周期的四分之一的持续时间。最终预充电电压可以在VDD1电压和来自第一级的VDD1+VDD2电压之间。

在时间T5处,多模式泵电路的第二级可响应于PHP信号(例如,控制反相器477)转变到高逻辑电平而开始升压操作。升压操作可以包括经由电容器478将Stg2升压节点的电压充电到VDD1+VDD1电压和VDD1+VDD1+VDD2电压之间的电压。

图5B的时序图501描绘在多模式泵电路(例如,多模式泵电路400)的两级操作模式下控制电压泵的控制信号转变。当处于两级模式时,可以通过禁用PHN2信号来禁用第二级(例如,第二级440)的第一预充电电路(例如,第一电路442)。在时间T1处,多模式泵电路的第一级(例如,第一级410)可响应于PHN0信号(例如,控制反相器421)转变到低逻辑电平而开始预充电操作。预充电操作可以包括经由电容器424将Stg1升压节点预充电到VDD2电压。

在时间T2处,多模式泵电路的第一级可响应于PHP0信号转变到高逻辑电平而开始升压操作。升压操作可以包括经由电容器424将Stg1升压节点的电压充电到VDD1+VDD2电压。

在时间T3处,多模式泵电路的第二级(例如,第二级440)可响应于PHN信号(例如,控制反相器475)转变到低逻辑电平而开始预充电操作。预充电操作可包括经由电容器478预充电Stg 1升压节点电压(例如,来自输出节点428或438的VDD1+VDD2电压)。

在时间T4处,多模式泵电路的第二级可响应于PHP信号(例如,控制反相器477)转变到高逻辑电平而开始升压操作。升压操作可以包括经由电容器478将Stg2升压节点的电压充电到VDD1+VDD1+VDD2电压。

图5C的时序图502描绘在多模式泵电路(例如,多模式泵电路400)的单级操作模式下控制电压泵的控制信号转变。当处于单级模式时,可以通过禁用PHN信号来禁用第二级(例如,第二级440)的第二预充电电路(例如,第二电路444)的第一和第二预充电电路。在单级模式下,也不使用第一级(例如,第一级410)。在一些实例中,PHN0和PHP0信号也可以在处于单级模式时被禁用,以降低多模式泵电路内的功耗。

在时间T1处,多模式泵电路的第二级(例如,第二级440)可响应于PHN2信号(例如,控制反相器471)转变到低逻辑电平而开始预充电操作。预充电操作的第一部分可以包括经由电容器478将Stg2升压节点的电压预充电到VDD1电压。

在时间T2处,多模式泵电路的第二级可响应于PHP信号(例如,控制反相器477)转变到高逻辑电平而开始升压操作。升压操作可以包括经由电容器478将Stg2升压节点的电压充电到VDD1+VDD1电压。

图5A-5C的时序图500、501和502是用于说明各种所描述的实施例的操作的实例。虽然时序图500、501和502描绘了所包括的信号的信号转变的特定布置,但是本领域技术人员将理解,在不脱离本公开的范围的情况下,可以在不同场景中包括附加的或不同的转变。此外,在时序图500、501和502中表示的信号的量值的描述不旨在按比例绘制,并且代表性时序是时序特性的说明性实例。

尽管已经在某些优选实施例和实例的上下文中公开了本发明,但是本领域技术人员将理解,本发明超出具体公开的实施例扩展到其它替代实施例和/或本发明的用途及其明显的修改和等同物。此外,基于本公开,在本发明范围内的其它修改对于本领域技术人员将是显而易见的。也经审慎考虑,可以进行实施例的具体特征和方面的各种组合或子组合,并且仍然落入本发明的范围内。应当理解,所公开的实施例的各种特征和方面可以彼此组合或替换,以形成所公开的发明的各种模式。因此,本文公开的本发明的至少一些的范围不应限于上述具体公开的实施例。

- 多模式电压泵和控制

- 具有电荷泵模式和升压转换器模式的电压供应电路装置