逻辑电路系统

文献发布时间:2023-06-19 11:55:48

背景技术

设备的子部件可以通过多种方式彼此通信。例如,可以使用串行外围接口(SerialPeripheral Interface,SPI)协议、蓝牙低功耗(Bluetooth Low Energy,BLE)、近场通信(Near Field Communication,NFC)或其他类型的数字或模拟通信。

一些2D和3D打印系统包括一个或多个可更换打印设备部件,诸如打印材料容器(例如,喷墨盒、墨粉盒、油墨供应件、3D打印剂供应件、构建材料供应件等)、喷墨打印头组件等等。在一些示例中,与(多个)可更换打印设备部件相关联的逻辑电路系统与其中安装有这些可更换打印设备部件的打印设备的逻辑电路系统进行通信,例如,传送诸如其标识、能力、状态等的信息。在进一步示例中,打印材料容器可以包括用于执行一个或多个监控功能(如,打印材料水平感测)的电路系统。

附图说明

现在将参考附图来描述非限制性示例,在附图中:

图1是打印系统的示例;

图2是可更换打印设备部件的示例;

图3示出打印设备的示例;

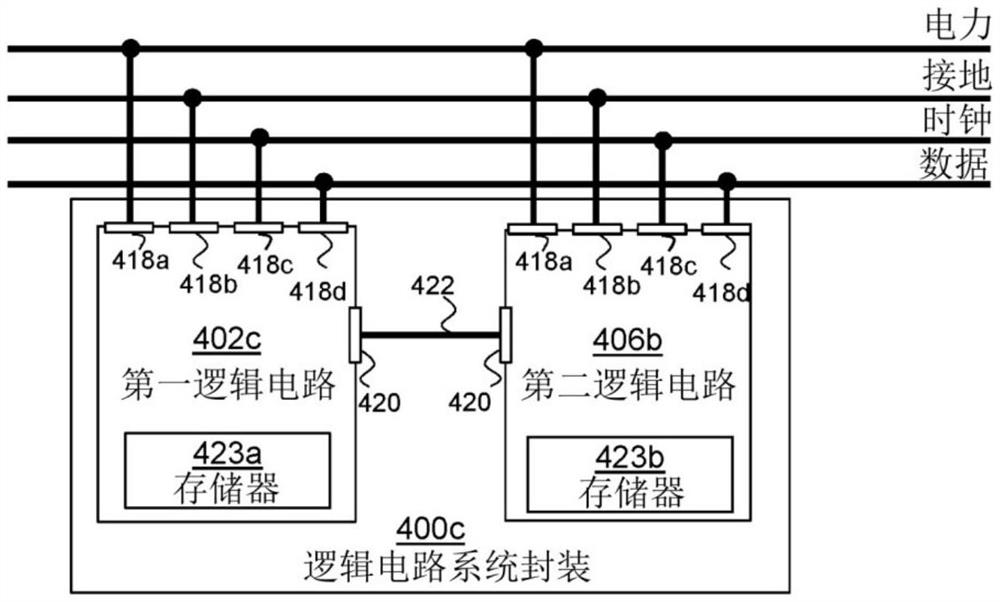

图4A、图4B、图4C、图4D和图4E示出逻辑电路系统封装和处理电路系统的示例;

图5是可以由逻辑电路系统封装实施的方法的示例;

图6是可以由逻辑电路系统封装实施的方法的进一步示例;

图7示出可以例如由处理电路系统实施的方法的示例;

图8示出打印设备中的可更换打印设备部件的示例布置;

图9是可更换打印设备部件的示例;

图10是校验打印设备部件的方法的示例;

图11是校验打印设备部件的方法的进一步示例;

图12示出校验方法的另一个示例;

图13A示出流体水平传感器的示例布置;

图13B示出打印盒的透视图的示例;

图14示出逻辑电路系统封装的示例;以及

图15示出逻辑电路系统封装的进一步示例。

具体实施方式

本文中在打印设备的背景下描述应用的一些示例。然而,并非所有示例都限于这些应用,并且在其他背景下可以使用本文中阐述的至少一些原理。

本公开中引用的其他申请和专利的内容通过引用并入本文中。

在某些示例中,内部集成电路(I

某些示例打印材料容器具有利用I2C通信的从逻辑,但在其他示例中,也可以使用其他形式的数字或模拟通信。在I2C通信的示例中,主IC通常可以被提供为打印设备(其可以称为‘主机’)的一部分,并且可更换打印设备部件将包括‘从’IC,但不必在所有示例中都如此。可以存在连接到I2C通信链路或总线的多个从IC(例如,不同颜色的打印剂的容器)。(多个)从IC可以包括处理器,用于在对来自打印系统的逻辑电路系统的请求作出响应之前执行数据操作。

打印设备和安装在该设备中的可更换打印设备部件(和/或其相应的逻辑电路系统)之间的通信可以促进各种功能。

打印设备内的逻辑电路系统可以经由通信接口从与可更换打印设备部件相关联的逻辑电路系统接收信息,和/或可以向该可更换打印设备部件逻辑电路系统发送命令,这些命令可以包括用于将数据写入到与其相关联的存储器或从该存储器读取数据的命令。

本公开可以涉及打印设备部件,其可以包括可更换打印设备部件。某些打印设备部件可以包括保持打印剂或打印材料的储器。在本公开中,打印材料和打印剂意思相同,并且旨在涵盖不同示例打印材料,包括油墨、墨粉颗粒、液体墨粉、三维打印剂(包括刺激剂和抑制剂)、三维打印构建材料、三维打印粉末。

例如,可以经由通信接口将可更换打印设备部件和/或与其相关联的逻辑电路系统的标识、功能性和/或状态传送到打印设备的逻辑电路系统。例如,打印剂容器逻辑电路可以被配置为传送标识。例如,可以将标识存储在逻辑电路上以促进由兼容的打印设备逻辑电路对其进行检查,其中,在不同示例中,标识的形式可以是产品序号、另一个盒编号、品牌名称、指示真实性的签名或比特等。在本公开的某些示例中,多个功能或逻辑电路可以与单个打印设备部件的单个逻辑电路封装相关联,由此可以将多个对应标识存储在逻辑电路封装上和/或从逻辑电路封装读取。例如,打印设备部件的逻辑电路系统可以存储打印设备部件的特性数据,例如包括表示打印材料容器的至少一个特性的数据,例如,打印材料识别特性,诸如总体积、初始填充体积和/或填充比例(参见例如欧洲专利公开号0941856,其通过引用并入本文中);颜色,诸如青色、品红色、黄色或黑色;颜色数据,包括经压缩或未经压缩的颜色图或其部分(参见例如国际专利申请公开号WO2015/016860,其通过引用并入本文中);用于重建颜色图的数据,诸如配方(参见例如国际专利申请公开号WO2016/028272,其通过引用并入本文中);等等。例如,打印材料特性可以被配置为关于其中安装有打印材料的打印设备来增强功能性或输出。在进一步示例中,可以经由通信接口提供状态,诸如与打印材料水平有关的数据(例如,填充水平)或其他感测的(例如,动态)性质,例如使得打印设备可以向用户生成该填充水平的指示。在一些示例中,校验过程可以由打印设备实施。在美国专利公开9619663(其通过引用并入本文中)中解释了以密码方式认证的通信方案的示例。例如,打印设备可以验证打印剂容器源自于已授权来源,以便确保其质量(例如,执行其认证)。被配置为对认证请求作出响应的可更换部件的逻辑电路的示例是美国专利公开号9619663(其通过引用并入本文中)、美国专利公开号9561662(其通过引用并入本文中)和/或美国专利公开号9893893(其通过引用并入本文中)。

在本公开的在某些示例中,校验过程可以包括完整性检查,以确保可更换打印设备部件和/或与其相关联的逻辑电路系统如预期的那样起作用,例如确保传送的一个或多个标识、打印材料特性和状态是如预期的那样的。校验过程可以进一步包括请求传感器信息,使得打印设备部件的逻辑电路系统可以检查该传感器数据是否遵从预期的参数。

在先前的国际专利申请公开WO2017/074342(其通过引用并入本文中)、WO2017/184147(其通过引用并入本文中)和WO2018/022038(其通过引用并入本文中)中公开了传感器和传感器阵列的示例。可以根据本公开使用这些或其他传感器类型、或类似于这些传感器阵列的对信号输出进行模拟的其他布置。

进而,可以经由通信接口从与打印设备相关联的逻辑电路系统向打印设备部件的逻辑电路系统发送用于执行任务的指令。

在下文描述的至少一些示例中,描述了逻辑电路系统封装。该逻辑电路系统封装可以与可更换打印设备部件相关联(例如,在内部或外部贴附到可更换打印设备部件,例如至少部分地在壳体内),并且适于经由作为打印设备的一部分提供的总线与打印设备控制器传送数据。

如本文中使用的术语‘逻辑电路系统封装’指代可以彼此互连或通信地链接的一个或多个逻辑电路。在提供多于一个逻辑电路的情况下,这些逻辑电路可以被封装为单个单元,或者可以被单独地封装,或者不被封装,或者其某种组合。封装可以被布置或设置在单个基板或多个基板上。在一些示例中,封装可以直接贴附到盒壁。在一些示例中,封装可以包括接口,例如包括垫或引脚。封装接口可以旨在连接到打印设备部件的通信接口,该通信接口进而连接到打印设备逻辑电路,或者封装接口可以直接连接到打印设备逻辑电路。示例封装可以被配置为经由串行总线接口进行通信。

在一些示例中,每个逻辑电路系统封装设置有至少一个处理器和存储器。在一个示例中,逻辑电路系统封装可以是或者可以用作微控制器或安全微控制器。在使用时,逻辑电路系统封装可以粘附到可更换打印设备部件或与其集成。逻辑电路系统封装可以可替代地称为逻辑电路系统组件,或者简单地称为逻辑电路系统或处理电路系统。

在一些示例中,逻辑电路系统封装可以对来自主机(例如,打印设备)的各种类型的请求(或命令)作出响应。第一类型的请求可以包括对数据(例如,标识和/或认证信息)的请求。来自主机的第二类型的请求可以是用于执行实体动作的请求,如执行至少一次测量。第三类型的请求可以是对数据处理动作的请求。可以存在另外的类型或请求。

在一些示例中,可以存在与特定逻辑电路系统封装相关联的多于一个地址,其用于对通过总线发送的通信进行寻址,以识别作为通信的目标(并且因此在一些示例中,具有可更换打印设备部件)的逻辑电路系统封装。在一些示例中,不同请求由封装的不同逻辑电路处置。在一些示例中,不同逻辑电路可以与不同地址相关联。

在至少一些示例中,多个这样的逻辑电路系统封装(其中每一个可以与不同的可更换打印设备部件相关联)可以连接到I2C总线。在一些示例中,逻辑电路系统封装的至少一个地址可以是例如根据I2C协议的I2C兼容的地址(下文中称为I2C地址),以促进根据I2C协议在主到从之间的直接通信。在其他示例中,可以使用其他形式的数字和/或模拟通信。

图1是打印系统100的示例。打印系统100包括经由通信链路106与逻辑电路系统(该逻辑电路系统与可更换打印设备部件104相关联)通信的打印设备102。尽管为了清楚起见,可更换打印设备部件104被示出为位于打印设备102外部,但在一些示例中,可更换打印设备部件104可以容纳在打印设备内。虽然示出了特定类型的2D打印设备102,但是可以替代地提供不同类型的2D打印设备或3D打印设备。

可更换打印设备部件104可以包括例如打印材料容器或盒(再一次地,其可以是用于3D打印的构建材料容器、用于2D打印的液体或干墨粉容器、或用于2D或3D打印的液体打印剂容器),其可以在一些示例中包括打印头或其他分配或转移部件。可更换打印设备部件104可以例如包含打印设备102的消耗性资源、或寿命可能比打印设备102更短(在一些示例中,显著更短)的部件。此外,虽然该示例中示出了单个可更换打印设备部件104,但是在其他示例中,可以存在多个可更换打印设备部件,例如包括不同颜色的打印剂容器、打印头(其可以与容器成一体)等等。在其他示例中,打印设备部件104可以包括例如要由维修人员更换的服务部件,这些服务部件的示例可以包括打印头、墨粉处理盒或逻辑电路封装本身,以粘附到对应的打印设备部件并与兼容的打印设备逻辑电路通信。

在一些示例中,通信链路106可以包括具有I2C能力的总线或I2C兼容的总线(下文中称为I2C总线)。

图2示出了可更换打印设备部件200的示例,其可以提供图1的可更换打印设备部件104。可更换打印设备部件200包括数据接口202和逻辑电路系统封装204。在使用可更换打印设备部件200时,逻辑电路系统封装204对经由数据接口202接收到的数据进行解码。该逻辑电路系统可以执行如下文阐述的其他功能。数据接口202可以包括I2C或其他接口。在某些示例中,数据接口202可以是与逻辑电路系统封装204相同的封装的一部分。

在一些示例中,逻辑电路系统封装204可以进一步被配置为对数据进行编码以经由数据接口202进行传输。在一些示例中,可以存在所提供的多于一个数据接口202。

在一些示例中,逻辑电路系统封装204可以被布置为在I2C通信中用作‘从’。

图3示出打印设备300的示例。打印设备300可以提供图1的打印设备102。打印设备300可以用作可更换部件的主机。打印设备300包括用于与可更换打印设备部件通信的接口302、以及控制器304。控制器304包括逻辑电路系统。在一些示例中,接口302是I2C接口。

在一些示例中,控制器304可以被配置为在I2C通信中用作主机或主。控制器304可以生成命令并向至少一个可更换打印设备部件200发送这些命令,并且可以接收并解码从可更换打印设备部件接收到的响应。在其他示例中,控制器304可以使用任何形式的数字或模拟通信与逻辑电路系统封装204通信。

可以单独地制造和/或出售打印设备102、300以及可更换打印设备部件104、200和/或其逻辑电路系统。在示例中,用户可以获取打印设备102、300并保留设备102、300多年,而在这些年中可以购买多个可更换打印设备部件104、200,例如随着在产生打印输出时使用打印剂。因此,打印设备102、300与可更换打印设备部件104、200之间可以存在至少一定程度的向前和/或向后兼容性。在许多情况下,这种兼容性可以由打印设备102、300提供,因为可更换打印设备部件104、200在其处理和/或存储器容量方面可能是相对资源受约束的。

图4A示出了逻辑电路系统封装400a的示例,其可以例如提供关于图2描述的逻辑电路系统封装204。逻辑电路系统封装400a可以与可更换打印设备部件200相关联,或者在一些示例中,可以贴附到该可更换打印设备部件和/或至少部分地并入该可更换打印设备部件内。

在一些示例中,逻辑电路系统封装400a可经由第一地址寻址,并且包括第一逻辑电路402a,其中,第一地址是用于第一逻辑电路402a的I2C地址。在一些示例中,第一地址可以是可配置的。在其他示例中,第一地址是固定地址,例如“硬连线的”,其旨在在第一逻辑电路402a的使用寿命期间保持相同的地址。在与第二地址相关联的时间段之外,第一地址可以在与打印设备逻辑电路连接时以及在与打印设备逻辑电路连接期间与逻辑电路系统封装400a相关联,如下文将阐述的。在要将多个可更换打印设备部件连接到单个打印设备的示例系统中,可以存在对应的多个不同的第一地址。在某些示例中,第一地址可以被视为用于逻辑电路系统封装400a或可更换打印部件的标准I2C地址。

在一些示例中,逻辑电路系统封装400a也可经由第二地址寻址。例如,第二地址可以与不同逻辑功能相关联,或至少部分地与不同于第一地址的数据相关联。在一些示例中,第二地址可以与不同硬件逻辑电路相关联,或与不同于第一地址的虚拟装置相关联。

在一些示例中,第二地址可以是可配置的。在开始经由第二地址进行通信会话时,第二地址可以是初始和/或默认第二地址,并且在开始该会话之后可以被重新配置为不同地址。在一些示例中,可以在通信会话的持续时间内使用第二地址,逻辑电路系统封装400a可以被配置为在该会话结束时、或在开始新会话时或之前将该地址设置为默认或初始地址。这种通信会话中的通信可以指向第二地址,并且在通信会话之间的通信可以指向第一地址,由此打印设备逻辑电路304可以例如经由不同地址通过这些不同的通信会话来验证不同的标识、特性和/或状态。在如下文进一步阐述的经由第二地址进行的通信会话的结束与逻辑电路的至少一部分的电力损失相关联的示例中,该电力损失可能造成第二‘临时’地址被丢弃(例如,第二地址可以保存在易失性存储器中,而初始或默认地址可以保存在持久性存储器中)。因此,每次在对应的通信会话开始之后均可以设置‘新’的或‘临时’的第二地址(但是在一些情况下,可能先前已关于逻辑电路系统使用了该‘新’的或‘临时’的第二地址)。

在其他示例中,逻辑电路封装400a可以不将其本身设置回用于开始每个对应的通信会话的初始第二地址。相反,其可以允许在每个对应的通信会话中配置第二地址,而不用切换到初始或默认第二地址。

换句话说,在期间要发生通信会话的时间段开始时,第二地址可以被配置为初始第二地址。逻辑电路系统封装400a可以被配置为响应于在该时间段期间向初始第二地址发送的且包括临时地址的命令,将其第二地址重新配置为该临时地址。然后,可以有效地重置逻辑电路系统封装400a,使得在接收到向第一地址发送的指示任务和时间段的后续命令之后,逻辑电路系统封装400a被配置为具有相同的初始第二地址。

在一些示例中,例如与不同打印材料类型(诸如,不同颜色或剂)相关联并且与相同打印设备逻辑电路304兼容的不同逻辑电路系统封装204、400a的初始和/或默认第二地址可以是相同的。然而,对于具有第二地址的每个通信会话,每个逻辑电路系统封装400a可以临时地与不同临时地址相关联,可以将该不同临时地址设置为用于每个通信会话的第二地址。在某些示例中,每次可以使用随机的临时第二地址,在一些示例中的条件为,在特定时刻在公共I2C总线上的每个已启用第二地址均不同于其他已启用地址。在一些示例中,‘随机’的第二地址可以是从可能的第二地址的预定池选择的第二地址,这些可能的第二地址在一些示例中可以存储在打印设备上。临时地址可以由打印设备逻辑电路304为每个连接的逻辑电路系统封装400a生成,并且通过所述命令进行传送。

在一些示例中,逻辑电路系统封装400a可以包括用于存储第二地址的存储器(在一些示例中,以易失性方式)。在一些示例中,为此目的,存储器可以包括可编程地址存储器寄存器。

在一些示例中,封装400a被配置为使得响应于向第一地址发送的指示第一时间段(以及在一些示例中的任务)的第一命令,封装400a可以通过各种方式作出响应。在一些示例中,封装400a被配置为使得其可在该时间段的持续时间内经由至少一个第二地址访问。可替代地或另外,在一些示例中,封装可以执行任务,该任务可以是第一命令中指定的任务。在其他示例中,封装可以执行不同的任务。

第一命令可以例如由主机(如其中安装有逻辑电路系统封装400a(或相关联的可更换打印设备部件)的打印设备)来发送。如下文更详细地阐述的,任务可以包括监控任务,例如监控计时器(以及在一些示例中,监控时间段)。在其他示例中,任务可以包括计算任务,诸如执行数学挑战。在一些示例中,任务可以包括为通信目的而激活第二地址和/或有效地停用第一地址(或者可以包括执行导致激活或启用第二地址和/或有效地停用或禁用第一地址的动作)。在一些示例中,激活或启用第二地址可以包括例如通过将第二地址写入存储器中的指示逻辑电路系统封装400a的地址的部分中来设置(例如,写入、重写或改变)第二地址(例如,临时第二地址)或触发该第二地址的设置。

在任务被指定的情况下,任务和/或时间段可以在第一命令中进行明确地指定,或者可以由逻辑电路系统封装400a通过参考查找表等来推断。在一个示例中,第一命令可以例如包括模式数据和时间数据。例如,可以作为串行数据封装的一部分发送的第一数据字段可以包括模式字段。这可以例如约为一个或若干位或字节的大小。在一些示例中可以作为第一数据字段的串行数据分组的一部分发送的第二数据字段可以包括‘停留时间(dwelltime)’数据字段。例如,这可以约为两个或若干位或字节的大小,并且可以指定时间段(例如,以毫秒为单位)。

在一些示例中,封装400a被配置为在第一时间段之前(在一些示例中,紧接在第一时间段之前)的第二时间段内、和/或在第一时间段之后(在一些示例中,紧接在第一时间段之后)的第三时间段内不可经由第二地址(默认或临时第二地址,或除第一地址外的任何地址)访问。在一些示例中,第一逻辑电路402a在该时间段的持续时间内忽略向第一地址(或除当前有效的第二地址之外的任何地址)发送的I2C流量。换句话说,封装400a可以在第一时间段之外对指向第一地址的命令作出响应而不对指向第二地址的命令作出响应;并且可以在第一时间段期间对指向第二地址的命令作出响应而不对指向第一地址的命令作出响应。如本文中关于在总线上发送的数据使用的术语‘忽略’可以包括以下各项中的任一项或任何组合:不接收(在一些示例中,不将数据读取到存储器中)、不动作(例如,不遵循命令或指令)和/或不作出响应(即,不提供确认、和/或不以请求的数据作出响应)。例如,可以将‘忽略’向第一地址发送的I2C流量定义为逻辑电路系统封装400a不对指向第一地址(或除如可由打印设备逻辑电路304感知的当前有效的第二地址之外的任何地址)的通信作出响应。

使得第一逻辑电路402a在第二地址被激活或在使用中的时间段的持续时间内‘忽略’(或以其他方式不作出响应)向第一地址发送的I2C流量允许第一地址和第二地址彼此完全独立。例如,第一地址可以是I2C兼容的,而第二地址可以呈任何格式,在一些示例中包括非I2C兼容格式。另外,如果在该时间段的持续时间内有效地禁用第一地址,则无需考虑对封装400a可能认为是寻址到第一地址的命令作出的任何响应。例如,第一地址可以由特定位序列来表示,并且如果有可能可以在不使用第一地址寻址该封装时辨识出第一地址,则可以采取预防措施,使得在不使用第一地址寻址该封装时避免这种识别出位序列。在通过相同串行总线在单个时间段内经由相应的不同逻辑电路系统封装的不同临时第二地址建立通信的实例中,该事件的可能性可能增加。如果未正确管理这些情况,则可能看到不确定或非预期行为。然而,如果在该时间段期间有效地禁用第一地址,则不需要这种考虑或预防措施,并且当第一地址被有效停用时,可能以其他方式由封装400a非故意地接收并解译为已通过第一地址接收到的命令将不会被接收。反之也可以成立(即,如果在该时间段之外有效地禁用任何第二地址,则在该时间段之外,封装400a将不接收可能非故意地被认为寻址到该地址的命令)。

在一些示例中,第一地址和第二地址可以具有不同长度。例如,第一地址可以是10位地址,并且第二地址可以是7位地址。在其他示例中,第一地址和第二地址可以具有相同长度,例如,两者都包括7位或10位地址。在某些示例中,第一地址和默认第二地址是硬连线的,而第二地址允许重新配置为临时地址,如上文解释的。在其他示例中,可以对第一地址和第二地址进行编程。

在一些示例中,第一逻辑电路402a在该时间段的持续时间内执行任务,该任务可以是接收到的命令中指定的任务。然而,在其他示例中,例如为了允许提高兼容性,第一逻辑电路402a可以不执行指定的任务(例如,如果无法这样做、或不必要这样做以使第一逻辑电路402a保持‘忙碌’,如下文描述的)。

在一些示例中,作为执行任务(该任务可以是第一命令中指定的任务)的结果,第一逻辑电路402a实际上可以不对向第一地址发送的请求作出响应(即,忽略)。在一些示例中,该任务可以至少基本上消耗第一逻辑电路402a的处理能力。例如,该任务可以包括以使第一逻辑电路402a的处理能力基本上专用于监控计时器的方式来执行该任务监控。在其他示例中,处理能力可以基本上专用于执行计算任务,诸如算术任务。在简单示例中,第一逻辑电路402a可以负责计算诸如pi的值。根据本发明的理解,从处理器可以在无限量的时间内继续将pi计算到进一步的小数位的意义上说,该任务可以是无限制的。因此,将该任务执行到完成会超出第一命令中指定的任何可能时间段。例如,在一些示例中,这种时间段可以是大约数秒或数十秒的量级。如果第一逻辑电路专用于计算pi/监控计时器的任务,直到该时间段过去为止,则其可能不会同时监控经由通信总线等向其发送的流量。因此,即使通信是向第一地址发送,这些通信也将被忽略。可以注意到,某些I2C从装置在执行任何种类的处理的同时通常会忽略总线。然而,本文中指定的处理与时间段相关联。注意到,考虑到逻辑电路封装在第二地址被激活的时间内不响应到其第一地址的通信,在一些示例中,(临时)第二地址可以与第一地址相同,由此仍然可以实现对应于该第二地址的期望功能。然而,如前面解释的,在其他示例中,第二地址不同于第一地址。

将理解的是,计算pi的任务仅仅是通常可能超出第一命令中指定的时间段的任务的一个示例。可以例如基于所考虑的时间段的长度来选择具有可能超出该时间段的完成时间的计算任务的其他示例。例如,如果该时间段将持续不长于3秒,则可以执行持续时间将超出3秒的处理任务(并且在一些示例中,在第一命令中指示)。此外,在其他示例中,如上所述,任务可以包括监控时间段。

在其他示例中,逻辑电路系统封装400a可以被配置为响应于包括任务和时间段的这种第一命令而不对指向其第一地址的通信作出响应,不一定是通过执行处理任务而是有效地通过被编程为不作出响应。

在一些示例中,封装400a被配置为响应于向第一地址发送的指令而提供第一组响应或以第一模式操作、并且响应于向第二地址发送的指令而提供第二组响应或以第二模式操作。换句话说,该地址可以触发由封装400a提供的不同功能。在一些示例中,响应于向第一地址发送的命令且不响应于向第二地址发送的命令而输出第一组响应中的至少一个响应,并且响应于向第二地址发送的命令且不响应于向第一地址发送的命令而输出第二组响应中的至少一个响应。在一些示例中,可以以密码方式认证第一组响应(即,伴有使用基础密钥生成或另外以密码方式‘签名’和/或加密的消息认证码,参见例如美国专利公开号9619663,其通过引用并入本文中),并且不以密码方式认证第二组响应。在一些示例中,第二组响应可以与传感器数据有关,并且第一组响应可以不与传感器数据有关。在一些示例中,消息可以伴有会话密钥标识符。例如,可以在第一组响应和第二组响应中传送封装400a的逻辑电路的标识,由此在第一组中而不是在第二组中以密码方式对其进行认证。这可以允许封装400a提供两种不同功能。可以从封装400a的输出数据缓冲器输出数据。

在一些示例中,封装400a可以被配置为使用向第一地址发送的I2C通信来参与第一校验过程、以及使用向第二地址发送的通信来参与第二校验过程。如上所述,第二地址可以是可重新配置的地址,并且在一些示例中,可以在已实施第一校验过程之后进行重新配置。在一些示例中,第一校验过程可以包括交换已加密或可认证的消息,其中,这些消息基于存储在封装中的基础密钥来加密和/或签名,该基础密钥可以是与在打印设备中存储或保存的秘密密钥相对应的秘密密钥(或基于秘密基础密钥)。在一些示例中,第二校验过程可以包括完整性检查,其中封装400a可以返回请求的数据值,使得主机设备可以验证这些数据值是否满足预定标准。

在上文阐述的示例中,已描述了用于与电路系统封装400a通信的地址。进一步通信可以涉及存储器地址,其用于请求与这些存储器地址相关联的信息。这些存储器地址可以具有与逻辑电路系统封装400a的第一地址和第二地址不同的配置。例如,主机设备可以通过将存储器地址包括在读取命令中来请求将特定存储器寄存器读出到总线上。换句话说,主机设备可以了解和/或控制存储器的布置。例如,可以存在与第二地址相关联的多个存储器寄存器和对应的存储器地址。特定寄存器可以与某个值相关联,该值可以是静态的或可重新配置的。主机设备可以通过使用存储器地址识别寄存器来请求将该寄存器读出到总线上。在一些示例中,寄存器可以包括以下各项中的任一项或任何组合:(多个)地址寄存器、(多个)参数寄存器(例如,用于存储增益和/或补偿参数)、(多个)传感器标识寄存器(其可以存储传感器类型的指示)、(多个)传感器读数寄存器(其可以存储使用传感器读取或确定的值)、(多个)传感器数量寄存器(其可以存储传感器的数量或计数)、(多个)版本标识寄存器、用于存储时钟周期的计数的(多个)存储器寄存器、用于存储指示逻辑电路系统的读/写历史的值的(多个)存储器寄存器、或其他寄存器。

图4B示出逻辑电路系统封装400b的另一个示例。在该示例中,封装400b包括第一逻辑电路402b(在该示例中,包括第一计时器404a)和第二逻辑电路406a(在该示例中,包括第二计时器404b)。虽然在该示例中,第一逻辑电路402b和第二逻辑电路406a中的每一者包括其自己的计时器404,但是在其他示例中,它们可以共享计时器或参考至少一个外部计时器。在进一步示例中,第一逻辑电路402b和第二逻辑电路406a由专用信号路径408链接。

在一个示例中,逻辑电路系统封装400b可以接收包括两个数据字段的第一命令。第一数据字段是设置请求的操作模式的一字节数据字段。例如,可以存在多种预定义模式,如:第一模式,其中逻辑电路系统封装400b要忽略向第一地址发送的数据流量(例如,在执行任务时);以及第二模式,其中逻辑电路系统封装400b要忽略向第一地址发送的数据流量并将使能信号传输到第二逻辑电路406a,如下文进一步阐述的。

第一命令可以包括附加字段,诸如地址字段和/或对确认的请求。

逻辑电路系统封装400b被配置为处理第一命令。如果无法遵从第一命令(例如,命令参数具有无效的长度或值,或者不可能启用第二逻辑电路406a),则逻辑电路系统封装400b可以生成错误代码并将该错误代码输出到通信链路,以返回到例如打印设备中的主机逻辑电路系统。

然而,如果有效接收并且可以遵从第一命令,则逻辑电路系统封装400b例如利用计时器404a来测量在第一命令中包括的时间段的持续时间。在一些示例中,计时器404a可以包括数字“时钟树”。在其他示例中,计时器404a可以包括RC电路、环形振荡器或某种其他形式的振荡器或计时器。在该示例中,响应于接收到有效的第一命令,第一逻辑电路402b启用第二逻辑电路406a并有效地禁用第一地址,例如如上所述通过对第一逻辑电路402b委以处理任务。在一些示例中,启用第二逻辑电路406a包括由第一逻辑电路402b向第二逻辑电路406a发送激活信号。换句话说,在该示例中,逻辑电路系统封装400b被配置为使得第二逻辑电路406a由第一逻辑电路402b选择性地启用。

在该示例中,第二逻辑电路406a通过第一逻辑电路402b经由信号路径408发送信号来启用,该信号路径可以是或可以不是专用信号路径408,即,专用于启用第二逻辑电路406a的专用信号路径408。在一个示例中,第一逻辑电路402b可以具有连接到信号路径408的专用接触引脚或垫,该信号路径链接第一逻辑电路402b和第二逻辑电路406a。在特定示例中,专用接触引脚或垫可以是第一逻辑电路402b的通用输入/输出(General PurposeInput/Output,GPIO)引脚。接触引脚/垫可以用作第二逻辑电路406a的使能触点。

可以将信号路径408的电压驱动为高以启用第二逻辑电路406a。在一些示例中,这种信号可以在基本上第一时间段的持续时间(例如,在接收到第一命令之后开始)内存在,并且可以在第一时间段结束时停止。如上所述,该启用可以由命令中的数据字段来触发。在其他示例中,可以例如在该时间段的持续时间内以另一种方式来选择性地启用/禁用第二逻辑电路。

在一些示例中,这种接触垫或引脚是以某种方式提供以便通常不可从可更换打印设备部件的外部访问。例如,其可以是相对远离接口的,和/或可以被壳体完全围封。这对于确保其仅经由第一逻辑电路402b来触发可以是有用的。

在该示例中,第二逻辑电路406a可经由至少一个第二地址寻址。在一些示例中,当第二逻辑电路406a被激活或启用时,其可以具有初始或默认的第二地址,该初始或默认的第二地址可以是I2C地址或具有某种其他地址格式。第二逻辑电路406a可以从主或主机的逻辑电路系统接收指令,以将初始地址改变为临时第二地址。在一些示例中,临时第二地址可以是由主或主机的逻辑电路系统选择的地址。这可以允许第二逻辑电路406a被提供在同一I2C总线上的多个封装400之一中,该多个封装至少最初共享相同的初始第二地址。稍后可以由打印设备逻辑电路将此共享的默认地址设置为特定临时地址,由此允许该多个封装在其临时使用期间具有不同的第二地址,从而促进向每个单独封装的通信。同时,提供相同的初始第二地址可以具有制造或测试优点。

在一些示例中,第二逻辑电路406a可以包括存储器。存储器可以包括用于存储初始和/或临时第二地址的可编程地址寄存器(在一些示例中,以易失性方式)。在一些示例中,可以在I2C写入命令之后和/或通过执行I2C写入命令来设置第二地址。在一些示例中,第二地址在使能信号存在或为高时可以是可设置的,但是在使能信号不存在或为低时可以是不可设置的。当使能信号被移除时和/或在恢复对第二逻辑电路406a的启用时,可以将第二地址设置为默认地址。例如,每当信号路径408上的使能信号为低时,便可以重置第二逻辑电路406a或其(多个)相关部分。当第二逻辑电路406a或其(多个)相关部分切换为非重置(out-of-reset)时,可以设置默认地址。在一些示例中,默认地址是7位或10位标识值。在一些示例中,可以将默认地址和临时第二地址轮流写入到单个公共地址寄存器。

在一些示例中,第二逻辑电路406a的地址可以在其被启用的任何时候进行重写。在一些示例中,当连接到总线时,第二逻辑电路406a可以处于低电流状态,除非其处于已启用状态时。

在一些示例中,第二逻辑电路406a可以包括上电重置(power-on reset,POR)装置。这可以包括电子装置,该电子装置检测施加到第二逻辑电路406a的电力并生成重置脉冲,该重置脉冲转到整个第二逻辑电路406a从而将其置于已知状态。这种POR装置可能对于在安装之前测试封装400b有特别效用。

在一些示例中,多个另外的逻辑电路可以与另外的引脚(其可以是GPIO引脚)等等‘链接(chained)’在一起。在一些示例中,一旦第二地址已被写入(即,逻辑电路具有不同于其默认地址的地址),其便可以激活‘输出’引脚或垫,并且因此链(如果存在链的话)中的下一个逻辑电路的‘输入’引脚或垫被驱动为高,并且逻辑电路可以被启用。这种(多个)另外的逻辑电路可以如关于第二逻辑电路406a描述的那样起作用。在一些示例中,这种另外的逻辑电路可以与第二逻辑电路406a具有相同的默认地址。关于以这种方式可以串行地链接和访问多少个逻辑电路不存在绝对限制,然而,在给定的实施方式中,基于总线线路上的串联电阻、从ID的数量等等可能存在实际限制。

在一个示例中,第一逻辑电路402b被配置为生成使能信号,该使能信号可以是低态有效(active low)非同步重置信号。在一些示例中,当该信号被移除(或被驱动为逻辑0)时,第二逻辑电路406a可以立即停止操作。例如,数据传输可以立即停止,并且第二逻辑电路406a可以呈现为默认状态(其可以是睡眠状态和/或低电流状态)。在一些示例中,存储器(诸如,寄存器)可以恢复到初始化状态(例如,默认地址可以包括地址寄存器的初始化状态)。

在I2C总线用于与封装400b通信的示例中,第一逻辑电路402b和第二逻辑电路406a可以连接到相同I2C总线。如上所述,在接收到专用命令之后,可以选择性地启用例如在第一逻辑电路402b和第二逻辑电路406a的GPIO引脚之间提供的附加连接。例如,第一逻辑电路402b可以在命令中指定的时间段内将专用GPIO引脚驱动为高(而默认情况下该引脚可以处于低状态)。在该时间段的持续时间内,第一逻辑电路402b可以不确认(‘NAK’)使用第一地址进行通信的任何尝试。在指定的时间段结束时,专用接触引脚可以返回到‘低’状态,并且第一逻辑电路402b可以再一次接收在I2C总线上向第一地址发送的通信。然而,当接触引脚被驱动为高时,第二逻辑电路406a可以被启用,并且接收在I2C总线上的通信。

可以注意到,通过在第一逻辑电路402b和第二逻辑电路406a之间共享I2C触点,电互连成本很小。另外,如果仅在该时间段的持续时间内选择性地给第二逻辑电路供电,则第二逻辑电路可能不太容易受电化学损耗的影响。另外,这可以允许将包括相应的第一逻辑电路402b和第二逻辑电路406a的多个封装设置在相同的串行I2C总线上,其中,第二逻辑电路406a可以(至少最初)共享地址,这可以进而降低制造和部署的复杂性。

在一些示例中,如上文概述的,逻辑电路系统封装400b包括:第一操作模式,其中该逻辑电路系统封装对向第一地址而非任何第二地址发送的通信作出响应;以及第二操作模式,其中该逻辑电路系统封装对向第二地址(例如,当前在使用中、并且在一些示例中当前存储在第二逻辑电路406a的专用寄存器中的第二地址)而非第一地址发送的通信作出响应。

在图4b中图示的示例中,第二逻辑电路406a包括单元(cell)的第一阵列410、以及至少一个第二单元412或第二单元的第二阵列。第一单元416a至416f、414a至414f和至少一个第二单元412可以包括电阻器。第一单元416a至416f、414a至414f和至少一个第二单元412可以包括传感器。在一个示例中,第一单元阵列410包括打印材料水平传感器,并且至少一个第二单元412包括另一个传感器和/或其他传感器阵列。

在该示例中,第一单元阵列410包括被配置为检测打印供应件的打印材料水平的传感器,该打印材料在一些示例中可以是固体,但在本文中描述的示例中是液体,例如油墨或其他液体打印剂。第一单元阵列410可以包括一系列温度传感器(例如,单元414a至414f)和一系列加热元件(例如,单元416a至416f),这些温度传感器和加热元件例如与WO2017/074342(其通过引用并入本文中)、WO2017/184147(其通过引用并入本文中)、以及WO2018/022038(其通过引用并入本文中)中描述的水平传感器阵列相比较在结构和功能方面类似。在该示例中,电阻器单元414的电阻与其温度相关。加热器单元416可以用于直接或间接地使用介质来加热传感器单元414。传感器单元414的后续行为取决于其浸没于内的介质,例如其处于液体中(或在一些示例中,被包裹在固体介质中)还是处于空气中。浸没于液体中/被包裹的那些传感器单元可以比处于空气中的那些传感器单元通常更快失热,因为液体或固体可以比空气更好地将热从电阻器单元414传导出去。因此,液位可以基于哪些电阻器单元414暴露于空气来确定,并且这可以基于在由相关联的加热器单元416提供热脉冲之后(至少在该热脉冲开始时)其电阻的读数来确定。

在一些示例中,每个传感器单元414和加热器单元416以一个直接在另一个顶部上的方式堆叠。由每个加热器单元416生成的热可以基本上在空间上被包含在加热器元件布局的周边内,使得热传递基本上局限于堆叠在加热器单元416正上方的传感器单元414。在一些示例中,每个传感器单元414可以被布置在相关联的加热器单元416与流体/空气接口之间。

在该示例中,第二单元阵列412包括可以具有不同功能(如(多个)不同的感测功能)的多个不同的单元。例如,第一单元阵列410和第二单元阵列412可以包括不同的电阻器类型。可以在第二逻辑电路406a中提供用于不同功能的不同单元阵列410、412。

图4C示出了逻辑电路系统封装400c的第一逻辑电路402c和第二逻辑电路406b(其可以具有上文描述的电路/封装的任何属性)可以如何连接到I2C总线以及如何彼此连接的示例。如该图中示出的,电路402c、406b中的每一者具有连接到I2C总线的电力线、接地线、时钟钱和数据线的四个垫(或引脚)418a至418d。在另一个示例中,四个公共连接垫用于将这两个逻辑电路402c、406b连接到打印设备控制器接口的四个对应连接垫。注意到,在一些示例中,代替四个连接垫,可以存在更少的连接垫。例如,可以从时钟垫收集电力;可以提供内部时钟;或者可以通过另一个接地电路将封装接地;使得可以省略一个或多个垫或使其变为冗余。因此,在不同示例中,封装可以仅使用两个或三个接口垫和/或可以包括“虚设(dummy)”垫。

电路402c、406b中的每一者具有接触引脚420,这些接触引脚由公共信号线422连接。第二电路的接触引脚420用作其使能触点。

在该示例中,第一逻辑电路402c和第二逻辑电路406b中的每一者包括存储器423a、423b。

第一逻辑电路402c的存储器423a存储信息,该信息包括密码值(例如,密码密钥和/或可以从中得到密钥的种子值)以及相关联的可更换打印设备部件的标识数据和/或状态数据。在一些示例中,存储器423a可以存储表示打印材料的特性的数据,例如其类型、颜色、颜色图、配方、批次号、年限等中的任一者、任何部分、或任何组合。

第二逻辑电路406b的存储器423b包括可编程地址寄存器,用于在第二逻辑电路406b首先被启用时包含第二逻辑电路406b的初始地址并且随后包含另外的(临时)第二地址(在一些示例中,以易失性方式)。在第二逻辑电路406b被启用之后,该另外的(例如,临时)第二地址可以被编程到第二地址寄存器中,并且可以在启用时段结束时被有效地擦除或替换。在一些示例中,存储器423b可以进一步包括可编程寄存器,用于以易失性或非易失性方式存储读/写历史数据、单元(例如,电阻器或传感器)计数数据、模数转换器数据(ADC和/或DAC)、以及时钟计数中的任一项、或任何组合。下文更详细地描述了这种数据的使用。某些特性(诸如,单元计数或者ADC或DAC特性)可以从第二逻辑电路得到,而不是作为单独数据存储在存储器上。

在一个示例中,第二逻辑电路406b的存储器423b存储以下各项中的任一项或任何组合:地址,例如第二I2C地址;呈修订ID形式的标识;以及例如,每个不同的单元阵列或者多个不同的单元阵列(如果这些单元阵列具有相同单元数)的最后一个单元的索引号(其可以是单元数减去一,因为索引可以从0开始)。

在使用第二逻辑电路406b时,在一些操作状态下,第二逻辑电路406的存储器423b可以存储以下各项中的任一项或任何组合:计时器控制数据,其可以启用第二电路的计时器和/或在一些计时器(诸如,环形振荡器)的情况下启用其中的频率抖动;抖动控制数据值(用于指示抖动方向和/或值);以及计时器样本测试触发值(用于通过相对于可由第二逻辑电路406b测量的时钟周期对计时器采样来触发计时器的测试)。

虽然此处将存储器423a、423b示出为单独的存储器,但是它们可以组合为共享的存储器资源或以某种其他方式进行划分。存储器423a、423b可以包括单个或多个存储器装置,并且可以包括易失性存储器(例如,DRAM、SRAM、寄存器等)和非易失性存储器(例如,ROM、EEPROM、闪速存储器、EPROM、忆阻器等)中的任一项或任何组合。

虽然图4C中示出一个封装400c,但是可以存在以类似或不同配置附接到总线的多个封装。

图4D示出了与打印材料容器一起使用的处理电路系统424的示例。例如,处理电路系统424可以贴附到打印材料容器或与其成一体。如已经提到的,处理电路系统424可以包括本公开的任何其他逻辑电路系统封装的任何特征,或者可与本公开的任何其他逻辑电路系统封装相同。

在该示例中,处理电路系统424包括存储器426和第一逻辑电路402d,该第一逻辑电路启用从存储器426进行的读取操作。处理电路系统424可经由其中安装有打印材料容器的打印设备的接口总线访问,并且与第一地址和至少一个第二地址相关联。总线可以是I2C总线。第一地址可以是第一逻辑电路402d的I2C地址。第一逻辑电路402d可以具有本公开中描述的其他示例电路/封装的任何属性。

第一逻辑电路402d适于参与由其中安装有容器的打印设备对打印材料容器的认证。例如,这可以包括密码过程,诸如任何种类的以密码方式认证的通信或消息交换,例如基于存储在存储器426中并且可以与存储在打印机中的信息结合使用的加密密钥。在一些示例中,打印机可以存储与多个不同打印材料容器兼容的密钥版本,以提供‘共享秘密’的基础。在一些示例中,可以基于这种共享秘密来实施打印材料容器的认证。在一些示例中,第一逻辑电路402d可以参与消息以利用打印设备得到会话密钥,并且可以基于这种会话密钥使用消息认证码来对消息进行签名。在早前提到的美国专利公开号9619663(其通过引用并入本文中)中描述了根据本段落的被配置为以密码方式认证消息的逻辑电路的示例。

在一些示例中,存储器426可以存储包括以下各项的数据:标识数据和读/写历史数据。在一些示例中,存储器426进一步包括单元计数数据(例如,传感器计数数据)和时钟计数数据。时钟计数数据可以指示第一计时器404a和/或第二计时器404b(即,与第一逻辑电路或第二逻辑电路相关联的计时器)的时钟速度。在一些示例中,存储器426的至少一部分与第二逻辑电路(诸如,如上文关于图4B描述的第二逻辑电路406a)的功能相关联。在一些示例中,在存储器426上存储的数据的至少一部分将响应于经由第二地址接收到的命令进行传送。在一些示例中,存储器426包括可编程地址寄存器或存储器字段,用于存储处理电路系统的第二地址(在一些示例中,以易失性方式)。第一逻辑电路402d可以启用从存储器426进行的读取操作和/或可以执行处理任务。

本文中描述的第一逻辑电路402的其他示例可以适于以类似方式参与认证过程。

存储器426可以例如包括表示打印材料的特性的数据,例如其类型、颜色、批次号、年限等中的任一者或任何组合。存储器426可以例如包括要响应于经由第一地址接收到的命令而进行传送的数据。处理电路系统可以包括第一逻辑电路,用于启用从存储器进行的读取操作并执行处理任务。

在一些示例中,处理电路系统424被配置为使得在接收到经由第一地址向第一逻辑电路402d发送的指示任务和第一时间段的第一命令之后,处理电路系统424可在该第一时间段的持续时间内由至少一个第二地址访问。可替代地或另外,处理电路系统424可以被配置为使得响应于向使用第一地址寻址的第一逻辑电路402d发送的指示任务和第一时间段的第一命令,处理电路系统424在基本上如由处理电路系统424的计时器(例如,如上文描述的计时器404a、404b)测量的时间段的持续时间内忽视(例如,‘忽略’或‘不作出响应’)向第一地址发送的I2C流量。在一些示例中,处理电路系统可以另外执行任务,该任务可以是第一命令中指定的任务。如本文中关于在总线上发送的数据使用的术语‘忽视’或‘忽略’可以包括以下各项中的任一项或任何组合:不接收(在一些示例中,不将数据读取到存储器中)、不动作(例如,不遵循命令或指令)和/或不作出响应(即,不提供确认、和/或不以请求的数据作出响应)。

处理电路系统424可以具有本文中描述的逻辑电路系统封装400的任何属性。具体地,处理电路系统424可以进一步包括第二逻辑电路,其中,该第二逻辑电路可经由第二地址访问。在一些示例中,第二逻辑电路可以包括至少一个传感器,该至少一个传感器可由其中安装有打印材料容器的打印设备经由第二地址读取。在一些示例中,这种传感器可以包括打印材料水平传感器。

处理电路系统424可以具有:第一校验功能,其由在I2C总线上向第一地址发送的消息来触发;以及第二校验功能,其由在该I2C总线上向第二地址发送的消息来触发。

图4E示出了逻辑电路系统封装400d的第一逻辑电路402e和第二逻辑电路406c的另一个示例,该第一逻辑电路和第二逻辑电路可以具有本文中描述的相同名称的电路/封装的任何属性,第一逻辑电路和第二逻辑电路可以经由相应接口428a、428b连接到I2C总线以及彼此连接。在一个示例中,相应接口428a、428b连接到相同接触垫阵列,其中仅一个数据垫用于连接到相同串行I2C总线的两个逻辑电路402e、406c,参见例如图13A和图13B。换句话说,在一些示例中,被寻址到第一地址和第二地址的通信经由相同数据垫来接收。

在该示例中,第一逻辑电路402e包括微控制器430、存储器432和计时器434。微控制器430可以是安全微控制器或适于用作安全或非安全的微控制器的定制的集成电路系统。

在该示例中,第二逻辑电路406c包括:发射/接收模块436,其从连接有封装400d的总线接收时钟信号和数据信号;数据寄存器438;多路复用器440;数字控制器442;模拟偏压(analogue bias)和模数转换器444;至少一个传感器或单元阵列446(其在一些示例中可以包括具有一个或多个电阻器元件阵列的水平传感器);以及上电重置(power-on reset,POR)装置448。POR装置448可以用于在不使用接触引脚420的情况下允许第二逻辑电路406c的操作。

模拟偏压和模数转换器444从(多个)传感器阵列446和从外部传感器接收读数。例如,可以向感测电阻器提供电流,并且可以将所得电压转换为数字值。该数字值可以存储在寄存器中并通过I2C总线读出(即,作为串行数据位或作为‘比特流’传输)。模数转换器444可以利用可以存储在寄存器中的参数,例如增益参数和/或补偿参数。

在该示例中,存在不同的附加单个传感器,包括例如环境温度传感器450、裂纹检测器452和/或流体温度传感器454中的至少一个。这些传感器可以分别感测环境温度、其上设置有逻辑电路系统的裸片的结构完整性、以及流体温度。

图5示出一种方法的示例,该方法可以由处理电路系统实施,例如由逻辑电路系统封装(诸如,上文描述的逻辑电路系统封装400a至400d)、或由关于图4D描述的处理电路系统424、和/或由设置在可更换打印设备部件(例如,消耗性打印材料容器)上的处理电路系统实施。

框502包括:接收向处理电路系统的第一地址发送的指示任务和第一时间段的第一命令。框504包括:由处理电路系统在该时间段的持续时间内启用通过处理电路系统的至少一个第二地址对处理电路系统的访问。

图6更详细地示出框504的方法的一个示例。在该示例中,提供了第一逻辑电路和第二逻辑电路,每个逻辑电路分别与第一地址和至少一个第二地址相关联,如上文参考图4B描述的。

框602包括:激活第二逻辑电路。如上文描述的,这可以包括:第一逻辑电路例如经由专用信号路径向第二逻辑电路发送或传输激活信号以激活第二逻辑电路。在该示例中,激活第二逻辑电路允许使用至少一个第二地址(例如,使用初始或默认第二地址)来访问处理电路系统。在一些示例中,在激活之后,可能造成第二逻辑电路设置新的或临时的第二地址,例如,以替换第二逻辑电路的初始或默认地址。在一些示例中,可以在通信会话的持续时间内设置临时地址。

框604包括:通过使第一逻辑电路在该时间段的持续时间内执行处理任务(在一些示例中,在框502中接收到的命令中指定的处理任务),在该时间段的持续时间内禁用经由第一地址(即,使用被寻址到第一地址的通信)对处理电路系统的访问。在其他示例中,可以通过防止传输对向第一地址发送的消息的响应来有效地禁用第一地址。框606包括:由处理电路系统使用处理电路系统的计时器来监控该时间段的持续时间。在一些示例中,使用计时器来监控该时间段的持续时间本身可以包括该处理任务。

在该时间段到期之后,该方法继续进行框608,该框包括:停用第二逻辑电路。例如,这可以包括由第一逻辑电路移除激活信号。因此,在该时间段的持续时间之后,可以禁用经由第二地址对处理电路系统的访问。例如,可以通过移除该信号来将第二逻辑电路断电或置于睡眠模式。

在通信会话的结束与逻辑电路的至少一部分的电力损失相关联的示例中,该电力损失可能造成第二地址被丢弃(例如,第二地址可以保存在易失性存储器中,而初始或默认地址可以硬连线或保存在持久性存储器中)。在重置之后,在新会话开始之前,可以再次将第二地址设置为默认或初始地址。在一些示例中,初始或默认地址可以保存在持久性存储器中并且可以在第二逻辑电路被启用时恢复到第二逻辑电路的寄存器。因此,每当通信会话开始时均可以设置‘新’的第二地址(但是在一些情况下,可能先前已关于逻辑电路系统使用该‘新’的第二地址)。

如本文中其他地方更详细地阐述,在激活时段期间,第二逻辑电路可以提供服务,例如单元或传感器读数等等。然而,在其他示例中,第二逻辑电路可以例如提供输出(诸如,激活光或声音(例如,第二逻辑电路可以控制光源或扬声器或某种其他设备)),可以接收数据(例如,可以包括用于存储数据文件的存储器),和/或可以提供某种其他类型的输出或服务。

图7示出可以例如由处理电路系统424或由如上文描述的封装400a至400d实施的方法的示例。该方法包括:在框702中,接收经由通信总线(例如,I2C总线)向处理电路系统的第一地址发送的指示处理任务和第一时间段的第一命令。

框704包括:开始处理电路系统的计时器。在其他示例中,可以监控而非开始计时器。例如,可以记录计时器的初始计数,并且可以监控该计数的增加。

框706包括:由处理电路系统执行处理任务,并且框708包括:忽视向第一地址发送的流量。在一些示例中,忽视I2C流量可以作为执行命令中指定的任务或执行另一项任务的结果。任务可以包括监控计时器。在其他示例中,任务可以包括计算任务,诸如进行工作以对数学挑战求解。

框708可以继续直到该时间段到期为止,如使用计时器监控的。

该方法可以包括上文关于任务和/或忽视(例如,‘忽略’或简单地‘不作出响应’)流量所描述的任何特征。该方法可以使用处理电路系统来实施,该处理电路系统与打印材料容器和/或可更换打印设备部件相关联或设置在其上。

在一些示例中,如上文描述的,该方法可以包括:在该时间段的持续时间内,由处理电路系统对向处理电路系统的第二地址发送的I2C流量作出响应。在一些示例中,第一地址与处理电路系统的第一逻辑电路相关联,并且第二地址与处理电路系统的第二逻辑电路相关联。在一些示例中,在提供第一逻辑电路和第二逻辑电路的情况下,第一逻辑电路可以在该时间段的持续时间内执行处理任务和/或可以例如经由专用信号路径向第二逻辑电路发送激活信号。在一些示例中,可以通过停止激活信号来停用第二逻辑电路。

图8示意性示出一种布置,其中在打印设备804中提供了多个可更换打印设备部件802a至802d。

可更换打印设备部件802a至802d中的每一者与逻辑电路系统封装806a至806d相关联,该逻辑电路系统封装可以是如上文描述的逻辑电路系统封装400a至400d。打印设备804包括主机逻辑电路系统808。主机逻辑电路系统808和逻辑电路系统封装806经由公共I2C总线810进行通信。在一种操作模式中,逻辑电路系统封装806中的每一者具有不同的第一地址。因此,逻辑电路系统封装806中的每一者(并且引申开来,可更换打印设备部件中的每一者)可以由主机打印设备804唯一地寻址。

在示例中,可以向可更换打印设备部件逻辑电路系统封装806中的特定一者发送第一命令(即,针对该逻辑电路系统封装使用唯一的第一地址来进行寻址),该第一命令指示该逻辑电路系统封装在对应的‘第一命令’时间段内启用其(至少一个)第二地址。因此,该可更换打印设备部件802可以例如启用至少一个第二地址和/或在一些示例中启用其相关联的功能。在一些示例中,这导致如上文描述的启用第二逻辑电路。例如,已寻址的逻辑电路系统封装806可以例如响应于相同命令或单独命令而在第一命令时间段的持续时间内忽略(例如,不确认和/或不作出响应)向逻辑电路系统封装806的第一地址发送的I2C流量。也可以向其他打印设备部件802发送第二命令,从而导致这些其他打印设备部件在‘第二命令’时间段的持续时间内忽略向其第一地址发送的I2C流量。如上所述,当不存在其他从装置‘监听’I2C总线时,可以减少关于通过I2C总线发送的消息的形式和内容的限制。因此,以这种方式,可以有效地禁用所有第一地址,而仅一个第二地址与I2C总线810进行通信。在其他示例中,可以同时通过相应的不同地址来寻址多于一个封装。在一些示例中,第一命令也可以导致已寻址的部件/封装在第一命令时间段的持续时间内忽略向其第一地址发送的I2C流量,和/或第二命令也可以导致已寻址的部件/封装可经由至少一个第二地址访问。

在一些示例中,(多个)逻辑电路系统封装806可以执行处理任务,该处理任务可以是如命令中指定的处理任务,以‘保持忙碌’并在指定的时间段的持续时间内忽略向第一地址发送的I2C流量。如上所述,这可以包括计算任务或监控任务,例如监控计时器。

因此,逻辑电路系统封装806可以被配置为:对第一命令具有第一响应,该第一响应导致该封装的第二地址在第一命令时间段的持续时间内被启用;对第二命令具有第二响应,该第二响应导致该封装在第二命令时间段的持续时间内忽略向第一地址发送的I2C流量(例如,通过执行处理任务,诸如监控计时器和/或实施吸收处理能力的计算任务)。换句话说,取决于接收到的命令的性质,可以启用逻辑电路系统封装806中的每一者以实施图5和/或图7的方法中的任一者。

为了考虑特定示例,主机装置(诸如,在该示例中为打印设备804,其希望经由逻辑电路系统封装806(在该示例中为逻辑电路系统封装806a)的第二地址来与其通信)可以发出命令,以便指示其他逻辑电路系统封装806b至806d以导致它们忽略总线810上的流量的方式进行动作。这可以包括逻辑电路系统808串行地发送被寻址到其他逻辑电路系统封装806b至806d中的每一者的唯一地址的三个命令,每个命令指定第一操作模式和时间段。第一操作模式可以导致总线上的流量被忽略。接下来,逻辑电路系统808可以经由目标逻辑电路系统封装806a的第一地址向其发送专用命令,该命令指定第二操作模式和时间段。第二操作模式可以包括导致总线810上的向第一地址发送的流量被忽略并且启用第二地址的指令。可以将第一命令时间段和第二命令时间段(在这些时间段内流量被不同逻辑电路分组806忽略)指定为彼此重叠,在一些示例中,要考虑到指令将被接收的延迟。

主机逻辑电路系统然后可以在该时间段的持续时间内经由所选择的逻辑电路系统封装806a的第二地址来与其通信。在该时间段期间,由于在一些示例中没有其他装置‘监听’I2C总线,因此任何通信协议(在一些示例中包括非I2C兼容协议)均可以用于经由所选择的逻辑电路系统封装806a的第二地址来与其通信。

当然,这仅是一个示例。在其他示例中,一些或所有封装可以同时经由第二地址访问,或者相应封装的第一地址和第二地址的混合体可以是可访问的。

图9示出包括I2C兼容的逻辑电路系统封装900的可更换打印设备部件802的示例,该I2C兼容的逻辑电路系统封装可以包括封装400a至400d或关于图4A至图4E描述的电路系统424的任何属性,并且可以在一些示例中被配置为实施本文中描述的任何方法。该示例中的封装包括I2C接口902,该I2C接口包括用于经由主机打印机的I2C总线进行通信的数据触点904。

该示例中的封装包括存储器,该存储器包括表示打印液体特性的数据,并且该数据是经由数据触点904可取得的和可更新的。封装900被配置为:响应于经由第一I2C地址从主机设备接收到的读取请求(即,该读取请求使用第一地址来寻址),通过总线并经由数据触点904来传输包括表示打印液体特性的所述数据的数据。不同的可更换打印设备部件802可以与可以存储不同打印液体特性的存储器相关联。

封装900进一步被配置为使得响应于经由第一地址接收到的指示任务和第一时间段的命令,该封装响应于(并且在一些示例中,仅响应于)接收到的寻址到不同于第一地址的至少一个第二地址的命令而通过相同总线和数据触点在该时间段的持续时间内传输数据、以及在该时间段结束之后响应于(并且在一些示例中,仅响应于)接收到的寻址到第一地址的命令而再次通过相同总线和数据触点来传输数据。

在一些示例中,该至少一个不同地址包括默认第二地址和另外的或临时第二地址,其中,封装900被配置为响应于接收到的寻址到默认第二地址的命令而将该地址重新配置为临时第二地址和/或对向临时第二地址发送的后续命令作出响应(并且在一些示例中,仅响应于),直到该时间段结束为止。这种响应可以通过相同总线和单个数据触点904发送。

可更换打印设备部件802可以被提供作为其存储器存储不同打印材料特性的多个打印设备部件之一。该多个可更换打印设备部件中的每一者的封装可以被配置为:响应于经由相应的第一地址接收到的指示任务和第一时间段的命令,传输对接收到的寻址到相同的相应默认地址的命令的数据响应。

在一些示例中,封装900被配置为:响应于所指示的在该时间段之外接收到的寻址到第一地址的命令,传输被认证(例如,以密码方式认证,例如使用秘密密钥且伴有消息认证码)的数据。然而,在该时间段期间,可以响应于接收到的寻址到该至少一个不同地址的命令来传输未认证的数据。

图10描述了一种使用与打印设备部件相关联的逻辑电路系统来校验该打印设备部件的方法。在一些示例中,逻辑电路系统可以是如上文描述的逻辑电路系统封装404a至404d、900和/或处理设备424。

例如,在校验打印设备部件时,可以旨在验证打印剂容器源自于已授权来源,以便确保其质量(例如,通过执行其认证)。在一些示例中,校验过程可以包括完整性检查,以确保可更换打印设备部件和/或与其相关联的逻辑电路系统如预期的那样起作用。这可以包括请求传感器信息,使得打印设备部件的逻辑电路系统可以检查该传感器数据是否遵从预期的参数。

该方法包括:在框1002中,以第一校验响应对经由I2C总线向与逻辑电路系统相关联的第一地址发送的第一校验请求作出响应。框1004包括:以第二校验响应对经由I2C总线向与逻辑电路系统相关联的第二地址发送的第二校验请求作出响应。

在一些示例中,第一校验响应是以密码方式认证的响应。例如,这可以使用共享秘密和/或使用密码密钥。在一些示例中,密码响应可以包括至少一个‘签名’消息,例如伴有消息认证码的消息,或者可以包括加密响应。在一些示例中,第二校验响应包括(多个)未加密响应或(多个)未签名响应。在一些示例中,对向第一地址发送的校验请求的大部分或全部响应是使用存储在逻辑电路上的密钥以密码方式签名的,而对向第二地址发送的校验请求的响应不是以密码方式签名的。这可以允许减少用于提供对向第二地址发送的命令的响应的处理资源。

图11更详细地描述了框1004的一个示例。在该示例中,第二校验请求包括对逻辑电路系统的计时器的时钟速度的指示的请求(在一些示例中,对第二计时器404b(或更一般地,与第二逻辑电路相关联的计时器)的时钟速度的请求)。该方法包括:在框1102中,相对于可由逻辑电路系统测量的另一个系统时钟或周期信号的频率,确定逻辑电路系统的时钟速度。框1104包括:基于相对时钟速度来确定第二校验响应。这可以例如允许由主机设备在设置有逻辑电路系统的计时器的背景下设置时间段。在一些示例中,可以测量逻辑电路系统本身的计时器的时钟速度,以便确定校验响应。例如,可以确定在预定数量的其他时钟信号/可测量周期内计时器的时钟周期数量,并且在一些示例中,可以提供该结果的指示作为校验响应。在一些示例中,可以通过将逻辑电路系统的计时器的已知时钟速度与该时钟速度进行比较来有效地确定时钟速度。在一些示例中,校验响应可以包括对在存储器中保存的值(例如,时钟计数)的选择,其指示相对于系统时钟/可测量周期的逻辑电路系统的时钟速度。如上已述,在一个示例中,该响应可以基于第二逻辑电路的内部计时器的时钟速度,该内部计时器可以是除了第一逻辑电路的第一计时器之外的第二计时器。

为了考虑这种方法的一个示例,逻辑电路系统可以包括多个寄存器。在一个示例中,寄存器可以在可由逻辑电路系统检测的设置数量的周期内记录逻辑电路系统封装的计时器(在一些示例中,与第二逻辑电路相关联的计时器)的输出数量。例如,在8个可检测周期内,可以存在使用逻辑电路系统封装的内部计时器记录的大约120个周期。这可以记录在一个或多个寄存器中。在这种示例中,可以将值“120”记录在寄存器或存储器上,该值可以由打印设备逻辑电路读取和验证,其中,验证可以例如包括将该值与预期值进行比较。在一个示例中,该相对时钟速度值可以由在本公开的示例中提到的时钟计数来表示。在另一个示例中,时钟计数可以与绝对时钟速度有关。可以测量时钟速度,并将其与所存储的时钟计数进行比较。在本公开中,所存储的时钟计数可以包括表示相对时钟速度或时钟计数的任何值,包括参考值或范围。

在一些示例中,可以设置系统时钟以考虑计时器的速度。在一些示例中,如上文描述的,系统时钟可以由第二逻辑电路的环形振荡器来驱动。第二逻辑电路可以包括多个计时器,诸如SAR时钟(用于模数转换器)和系统时钟两者。

图12示出了校验方法的另一个示例,该校验方法可以是使用与打印设备部件相关联的逻辑电路系统来校验该打印设备部件的方法。在一些示例中,逻辑电路系统可以是如上文描述的逻辑电路系统封装404a至404d、900和/或处理设备424。

在该示例中,在框1200中,逻辑电路封装以密码方式认证的响应对指向其第一地址的第一校验请求作出响应。作为第一校验的一部分,可以包括以下各项中的任一项或任何组合:封装(其至少一部分)的版本标识(即,修订(revision)ID);每类别的单元的数量;打印材料水平;时钟计数;读/写历史数据以及与第二地址有关的其他标识和特性数据。在一些示例中,可以将与第二逻辑电路相关联的标识数据(诸如,版本标识,如上文描述的)存储在第一逻辑电路中。在一些示例中,可以将标识数据存储在第一逻辑电路和第二逻辑电路两者中。在一些示例中,如上文描述的,在第二逻辑电路已被启用之后,该方法包括:在框1202中,接收地址设置信号,该地址设置信号经由I2C总线被发送到与逻辑电路系统相关联的初始第二地址。在一些示例中,地址设置信号可以指示临时第二地址。例如,主机逻辑电路系统(例如,打印设备的逻辑电路系统)可以选择和/或生成临时第二地址,并且将该临时第二地址传输到与可更换打印设备部件相关联的逻辑电路系统。在其他示例中,可以以某种其他方式(例如基于在逻辑电路系统的存储器中保存的数据)来选择临时第二地址。框1204包括:将第二地址设置为逻辑电路系统的地址。如上所述,在一些示例中,这可以包括用临时地址替换默认地址,在一些示例中,该临时地址可以由打印设备来选择。

在一些示例中,可以在通信时段的持续时间内保持临时第二地址,并且然后可以将该地址恢复到初始地址(因此其可以提供默认地址)。在一些示例中,初始地址在第二逻辑电路被启用的下一个时机复原。

该方法在框1206中继续:通过读取逻辑电路系统的存储器以提供版本标识的指示来确定第二校验响应。这可以是逻辑电路系统封装中(例如,该封装的第二逻辑电路中)使用的硬件、软件和/或固件的版本的指示。在一些示例中,这可以是可以被提供作为逻辑电路系统的一部分的至少一个传感器的版本的指示。第二校验的版本标识(即,修订ID)可以与第一校验的版本标识相匹配。

例如,这可以包括提供一个或多个‘修订值’,该一个或多个‘修订值’可以是一个或多个寄存器的内容。可以是这样的情况:逻辑电路系统的至少一个(并且在一些示例中,每一个)裸片和/或子部件与指示硬件的类型或版本的修订值相关联,并且可以允许主I2C电路提供更适当的通信。

假设返回的值满足预定标准(例如,返回预期数量的修订值和/或修订值被主机打印设备辨识,或具有有效格式等等),则该方法在框1208中继续:通过测试逻辑电路系统的至少一个部件以返回测试结果来确定另外的第二校验响应。虽然传感器可能不是与所有逻辑电路系统相关联地提供的(和/或可以不执行其测试),但是在一些示例中,第二校验响应可以包括实际测试在通过第二地址进行的通信中涉及的任何被提供的传感器或单元。例如,这可以包括用于指示单元和/或电阻器如预期的那样作出响应的测试。例如,该测试可以包括例如通过将测量的时钟速度与所存储的时钟速度进行比较来验证绝对或相对时钟速度,如上文描述的。在一些示例中,可以基于版本标识(例如,‘修订值’)的指示来确定时钟速度的预期值。例如,可以确定预期硬件的特定版本具有特定响应值。

在框1210中,该方法包括:通过读取逻辑电路系统的存储器以提供至少一种传感器类别中的单元或传感器的数量的指示,来确定另外的第二校验响应。在一些示例中,返回的该第二校验的数量应当与第一校验中所提供的传感器计数相匹配。例如,这可以提供流体水平传感器中电阻器的数量的指示。在一些示例中,可以提供与例如不同传感器类型有关的多个值。该校验特征可以允许打印设备配置参数以稍后读取传感器。另外,如果该值不是预期值(该预期值可以通过匹配在第一校验和第二校验中所提供的值来确定),则可能导致逻辑电路系统未能通过校验测试。在一些示例中,可以基于第二校验响应来确定该预期值。例如,可以确定预期硬件的特定版本具有特定数量的传感器。

在该示例中,持续地(例如,在与图12的每个框相关联的动作之间)将逻辑电路系统的至少一部分的读取和/或写入状态(在一些示例中,第二逻辑电路的读/写历史)记录在其存储器中。具体地,在该示例中,将读/写状态的多个指示存储在存储器中,每个指示使用不同的预定算法函数来确定。可以应用这种算法函数(其可以是秘密算法函数,或基于秘密数据,其中,解还基于由其中要布置有可更换打印设备部件的打印设备已知的秘密得到),使得不同的读/写操作导致存储不同值。算法函数可以包括加扰,例如对读/写历史值进行签名,这可以通过在逻辑电路系统封装上的硬连线或已写入指令来执行。在一些示例中,算法可以考虑读取和/或写入的内容,使得如果读/写操作的内容不同,则相同数量的读/写操作可能导致与历史相关联的不同值。在一些示例中,读/写操作的顺序也可能影响所存储的值。可以在逻辑电路系统封装中(例如,在第二逻辑电路中)存储或硬连线算法。在一些示例中,读/写历史状态值可以用于数据通信错误检查。在一些示例中,逻辑电路系统封装被配置为在读/写事件之后更新读/写历史。例如,第二逻辑电路可以被配置(例如,硬连线)为在第二逻辑电路上进行每个相应读取或写入动作之后重写读/写历史数据部分,其中,可以在每个读取或写入周期之后或在每个读取或写入周期时重写该读/写历史数据部分。可以在来自打印设备的读取请求、来自打印设备的写入请求、或这两者之后更新读/写历史数据部分。例如,该更新可以基于内部输出缓冲器刷新,或其可以基于接收到的打印设备电路的指令。第二逻辑电路可以是硬连线的,以基于第二逻辑电路的动作来更新读/写历史数据部分。在示例中,逻辑电路系统封装被配置为当将第二地址重新配置为临时地址时不更新读/写历史。在示例中,逻辑电路系统封装被配置为在将第二地址配置为临时地址之后在测量的时间段期间更新读/写历史。在又另一示例中,打印设备重写读/写历史数据字段。

因此,在该示例中,该方法进一步包括:存储逻辑电路系统的读/写历史状态的多个指示;以及利用逻辑电路系统的每个读/写请求来更新所存储的指示。

在框1212中,该方法包括:确定包括逻辑电路系统的读取和/或写入历史的指示的另外的第二校验响应。可以基于请求中所提供的指示来选择该响应,使得选择并返回与特定算法函数相关联的预期值。算法函数可以存储或硬连线在逻辑电路系统封装(例如,第二逻辑电路)中。算法函数可以包括对读/写历史数据进行签名。提供多种不同算法函数可以辅助提高校验过程的安全性。

在一个示例中,逻辑电路系统包括至少一个寄存器(例如,只读),该至少一个寄存器创建表示签名的值,即,其允许由存储用于解码该签名的数据的打印设备来进行解码和检查。指示读/写历史的值可以存储在其中,并且可以在逻辑电路系统内发生操作(读/写)时进行更新,并且因此提供逻辑电路系统的读取和/或写入历史的指示。可能并非所有动作都导致寄存器被更新,并且可以存在不导致值被更新的至少一个寄存器访问事件。读/写的顺序可能对这些值有影响。由于主机设备可以保持它对逻辑电路系统请求的其自己的读取和写入历史,因此可以参照(against)其自己的记录来验证该值,以确定是否正在执行读/写和/或用于确定该值的功能是否如预期的那样操作。

在该示例中,虽然由于这些方法可以基于共享秘密,这种方法可以被看作伪密码方法,但是第二校验响应可以在没有数字签名或消息认证码或会话密钥或会话密钥标识符的情况下提供,也不可以将其称为以密码方式认证的通信,而第一校验响应可以在具有数字签名、消息认证码或会话密钥和/或会话密钥标识符的情况下提供,并且可以称为以密码方式认证的通信。在一个示例中,不同校验可以与可以在不损害系统完整性的情况下以相对具有成本效益的方式被集成在封装中的不同逻辑电路相关联。

在一些示例中,可以关于其中传感器可能接触打印流体的可更换打印设备部件来实施图10至图12中的任一者的方法。这种接触可能意味着传感器易于损坏,并且因此验证传感器如预期的那样作用可以是特别有益的。然而,也可以关于其他类型的可更换打印设备部件来实施这些方法。

在一些示例中,如果任何校验响应均不符合预期(或者,在一些示例中,如果未接收到请求的响应和/或确认),则打印设备可以确定可更换打印设备部件未能通过检查,并且在一些示例中可以拒绝该可更换打印设备部件。在一些示例中,作为可更换打印设备部件未能通过检查的结果,可以防止或更改打印设备的至少一种操作。

在一些示例中,校验响应可以按时间切片提供,其中每个测试是以串行方式实施的。

图13A示出了由与电路系统封装1302相关联的传感器组件1300实施的第二逻辑电路的可能实际布置的示例。传感器组件1300可以包括薄膜堆叠,并且包括至少一个传感器阵列,诸如流体水平传感器阵列。该布置具有高的长宽比(例如,如沿着基板表面测量),例如,宽度约为0.2mm(例如,小于1mm、0.5mm或0.3mm),并且长度约为20mm(例如,大于10mm),从而导致长宽比等于或高于大约20:1、40:1、60:1、80:1或100:1。在已安装条件下,可以沿着高度来测量长度。在该示例中,如在(例如,硅)基板的底部和相对的外表面之间所测量的,逻辑电路可以具有小于1mm、小于0.5mm或小于0.3mm的厚度。这些尺寸意味着,各个单元或传感器很小。传感器组件1300可以被提供在相对刚性的载体1304上,在该示例中,该载体也承载接地、时钟、电力和数据I2C总线触点。

图13B示出了打印盒1312的透视图。打印盒1312具有壳体1314,该壳体的宽度W小于其高度H并且长度L或深度大于高度H。打印液体输出1316(在该示例中,被提供在盒1312的底面上的打印剂出口)、空气输入1318和凹部1320被提供在盒1312的前表面中。凹部1320跨盒1312的顶部延伸,并且逻辑电路系统封装1302(例如,如上文描述的逻辑电路系统封装400a至400d、900)的I2C总线触点(即,垫)1322抵靠壳体1314的侧壁内壁、邻近壳体1314的顶部和前部被提供在凹部1320的的一侧处。在该示例中,数据触点是触点1322中的最低触点。在该示例中,逻辑电路系统封装1302被设置为抵靠侧壁的内侧。

在一些示例中,逻辑电路系统封装1302包括如图13A中所示的传感器组件。

将了解的是,由于在装运和用户处置期间或在产品的寿命内逻辑电路系统可能发生电短路或损坏的风险,将逻辑电路系统放置在打印材料盒内可能对盒的可靠性造成挑战。

受损传感器可能提供不准确的测量结果,并且在评估这些测量结果时导致打印设备做出不适当的决策。因此,可以使用如关于图10至图12阐述的方法来验证基于特定通信序列与逻辑电路系统进行的通信提供了预期结果。这可以校验逻辑电路系统的操作健康状态。

在其他示例中,可更换打印设备部件包括本文中描述的任何示例的逻辑电路系统封装,其中,该部件进一步包括一定体积的液体。该部件的高度H可以大于宽度W并且长度L大于高度,宽度在两侧之间延伸。封装的接口垫可以设置在面向用于要插入数据互连的切口的一侧的内侧,这些接口垫沿高度方向在部件的顶部和前部附近延伸,并且数据垫是这些接口垫中的最底部垫,部件的液体和空气接口关于平行于高度H方向的相同竖直参考轴被设置在前部处,其中,该竖直轴平行于与这些接口垫相交的轴线并与其有一定距离(即,这些垫从该边缘部分地内缩距离d)。逻辑电路系统封装的其余部分也可以被设置为抵靠内侧。

在一些示例中,打印盒包括打印材料容器,该打印材料容器包括校验电路系统封装,该校验电路系统封装包括:存储器;触点阵列,其用于与打印设备的I2C总线连接;至少一个计时器;以及电路系统,其用于提供:第一校验功能,其由在I2C总线上向第一地址发送的消息来触发;以及第二校验功能,其由在该I2C总线上向第二地址发送的消息来触发。

在预先存在的打印设备部件(诸如,打印盒)中,逻辑电路系统封装可以由有时称为微控制器或安全微控制器的集成电路构成。这些集成电路被配置为(有时以安全方式)存储、传送和更新对应的打印设备部件的状态和特性。所述状态可以包括例如由打印设备在每次打印工作之后并基于墨滴计数和/或页计数来更新的打印材料的水平。使状态基于墨滴计数或页计数意味着测量剩余打印材料水平的间接方式,因为其可以基于例如全域打印统计学而非单独打印设备部件的内容。因此,打印设备部件的状态或特性(如由其相关联的逻辑电路系统封装所存储和反映的)可能是错误的或不可靠的。

本公开说明了第一示例逻辑电路系统封装,其适于实现将另外的感测装置连接到打印设备部件、或包括那些感测装置。本公开还说明了逻辑电路系统封装的其他示例,其被配置为与打印设备逻辑电路兼容,该打印设备逻辑电路被设计为与第一示例逻辑电路系统封装兼容(例如,读取、写入和/或命令)。

如所述的,例如,作为上述基于微控制器的集成电路(其通常未被配置为直接测量某些部件的状态)的补充或替代,本公开的不同示例促进可更换打印部件的电路封装中的不同子装置与打印机控制器通信。

在一个示例中,逻辑电路封装允许在控制成本和/或制造的同时进行相对安全且可靠的通信。本公开的某些示例促进将能力添加到打印机中的(部分)现有通信协议,诸如与打印设备部件上的集成电路通信的现有I2C总线。

在一个示例中,本公开探索将例如芯片实验室型(lab-on-chip type)的单元阵列(例如,作为“第二逻辑电路”的一部分)包括在打印设备部件逻辑电路系统封装中,在一个示例中,这些打印设备部件逻辑电路系统封装可以与现有打印设备接口总线结合实施,例如以努力控制成本和可靠性。如先前所解释的,第二逻辑电路的示例包括薄型、基于硅的传感器阵列。在一个示例中,这些传感器不使用已建立或标准的数字数据通信协议,诸如I2C。相反,这些传感器可以依赖于定制的模拟信号通信。本公开的一些示例涉及将这种存储器阵列集成在打印设备部件的逻辑电路系统封装中。

图14表示包括这种传感器阵列的逻辑电路系统封装的不同特定示例。

在某些示例中,将相对未开发(有时相对复杂)的感测装置集成到打印设备部件可能导致本领域中的意料之外的问题。例如,制造商可能能够确切地预测本创新在不同气候条件下放在架子上若干年之后并且然后在不同打印条件期间和之间的连接状态下可能产生的效果。另外,可能出现意料之外的成本和制造问题。出于其他原因,可能还期望提供用于连接到相同打印设备的替代部件。为了减轻这些潜在挑战或其他挑战中的任一者,某些打印设备部件(诸如,打印服务盒)可能未配备有传感器阵列。因此,本公开也涵盖其他示例逻辑电路系统封装,其与最初适于与具有传感器的第二逻辑电路通信的主机打印设备逻辑电路兼容,在某些实例中,该主机打印设备在设计这些其他兼容封装之前可能已经在全球各地的许多不同客户所在处操作。这些其他兼容封装适于不依赖于具有传感器的相同的第二逻辑电路来与最初的主机打印设备逻辑电路通信。在这些示例中,取决于接收到的打印机命令,某些实体硬件部件(诸如,传感器装置)可以至少部分地被表示不同性质或状态的不同虚拟或硬连线的部件或数据取代,这可以允许打印设备将这些逻辑电路系统封装接受为包括最初的传感器阵列。除了可操作之外,这些兼容封装还可能需要通过某些完整性检查,诸如所提到的第一校验和第二校验。

在一个示例中,这些兼容封装可以相对便宜或相对容易制造。在其他示例中,这些兼容封装可以比本公开的传感器阵列逻辑电路系统封装更可靠。在另外的其他示例中,这些兼容封装提供基于传感器阵列的第二逻辑电路的替代方案。在另外的其他示例中,这些兼容封装可以促进测试或维修打印设备或打印设备的其他部件。兼容封装可以被设计为输出对打印设备逻辑电路命令的类似响应,使得打印设备逻辑电路接受这些响应,就像安装了最初的第二逻辑电路。在某些示例中,在以下各情况下,可以提供兼容集成电路:当本领域中的某些基于传感器阵列的逻辑电路系统封装未能取代这些故障的集成电路时;为了节省成本;因为它们更容易制造;作为替代方案;或出于其他原因。图15公开了这种其他兼容逻辑电路封装的示例。先前提到的示例也涵盖这种替代封装,诸如例如图4B。

图14图示了逻辑电路系统封装1401,其用于可更换打印部件通过单个接口封装与打印设备逻辑电路进行接口连接并且具有带有单元或传感器阵列的第二逻辑电路1405。逻辑电路系统封装1401可以包括第一逻辑电路1403和第二逻辑电路1405,但是下文将描述的子特征可以被提供在单个封装中而在第一逻辑电路1403与第二逻辑电路1405之间没有明确区分。事实上,所图示的逻辑电路系统封装1401可以包括所图示的子部件中的一些而非全部。在本公开的其他示例中已说明了所图示的子部件。关于第一校验和第二校验来解释一些特征。为了更好地理解图14的某些特征,参考本公开中引用的所有公开,所有这些公开都属于本申请人。

第一逻辑电路1403包括第一地址(由框1402指示),该第一地址可以是第一I2C地址,并且可以不同于要同时连接到相同主机设备的其他部件的其他封装。第二逻辑电路1405可以包括第二地址(由框1404指示),该第二地址至少在启用第二逻辑电路1405之前或启用第二逻辑电路时可以与要同时连接到相同主机设备的其他部件的其他封装相同。在启用第二逻辑电路1405时或之后,第二地址可以被重新配置为例如不同于其他连接的封装1401。

第一逻辑电路1403包括存储器1407和CPU(中央处理单元)1409。存储器1407可以包括已签名和未签名部分,例如,这取决于特定数据特征的期望安全性,如由OEM和/或部分地由每个已签名或未签名部分的可用空间所期望的。存储器1407可以存储与可更换打印部件相关联的特性、状态和标识数据1415、1419/1437中的至少一者。特性可以包括颜色、打印材料类型、颜色图1411、颜色转换配方1413、以及其他特性。标识1415可以包括产品编号、品牌和/或要与可更换打印设备部件的标识相关联的任何代码,例如用于与OEM的保修相关联(若有必要或出于其他原因)。在某些示例中,例如,当除OEM之外的第三方供应封装1401时,一个或多个标识1419/1437、1415可以有意地留空。状态可以包括例如基于页计数、墨滴计数中的至少一者、和/或基于第二逻辑电路1403、1405的单元1451、1453、1457、1455的状态而与相对或绝对打印材料水平1427相关联的数据。第一逻辑电路1403可以进一步包括用于以密码方式认证消息的密码密钥1441,这些消息可以包括所述状态、特性和/或标识中的任一者。

逻辑电路系统封装1401包括用于将包括第一逻辑电路1403和第二逻辑电路1405的封装子部件互连到打印设备接口总线的接口1423,例如,包括三个或四个I2C兼容的互连垫。逻辑电路系统封装1401可以包括单独的专用认证逻辑1417。该专用认证逻辑可以包括其自己的与CPU 1409分离的专用处理器,例如,尤其被设计为在短时间窗1421内执行特定计算周期很多次。可以将时间窗1421存储在存储器1407中。逻辑电路系统封装1401可以包括第一计时器1429,用于测量如命令中所指示的计时器时段,例如以执行特定任务(诸如,启用第二逻辑电路)。第一逻辑电路1403可以包括、或连接到信号路径和/或开关,以启用第二逻辑电路1405和/或确定这样的时间,即,逻辑电路系统封装1401从该时间起要对指向第二可重新配置的地址(由框1404指示)的命令作出响应。

存储器1407可以存储与第二逻辑电路1405有关的特性。存储器1407可以存储至少一种类别的单元1451、1453、1457、1455中的每一者的单元计数1431,该单元计数将与该(这些)相应类别的单元的数量相关联。存储器1407可以存储可以与第二计时器1435的相对或绝对时钟速度相关联的时钟计数1433。存储器1407可以存储将与第二逻辑电路1405的修订ID 1437相关联的修订ID 1419。

先前提到的数据中的一些数据可以被包括作为数字签名的数据,诸如例如时间窗1421、修订ID 1419、颜色转换配方1413、颜色图1411、单元计数1433中的至少一者。在一个示例中,密码密钥1441存储在单独的安全硬件存储器中,该硬件存储器应当被理解为由第一存储器1407所涵盖。

此外,存储器1407可以存储以下至少一项:指令1443,用于使用密钥1441以密码方式认证消息;指令1443,用于在时间窗1421内提供经认证的挑战响应;以及指令1445,用于基于包括计时器时段和/或任务的相应命令来启用/激活第二逻辑电路1405,包括例如用第一计时器1429来测量时间段;以及其他认证或非认证指令。逻辑电路系统封装1401可以被配置为使得响应于指向第一地址的命令而进行的通信可以使用密码密钥1441(例如,伴有消息认证码和/或会话密钥标识符)以密码方式认证,而对指向第二地址的命令的响应可以不是使用密钥1441(例如,不伴有消息认证码和/或会话密钥标识符)以密码方式认证。

第二逻辑电路1405包括不同类别的多个单元1451、1453或单元阵列1455、1457,其数量可以对应于单元计数1431、1463。所图示的示例包括四个不同单元类别,但可以存在不同单元的更多或更少类别。例如,每种类别的单元可以具有类似的电阻、大小、材料或其他性质。单元阵列可以包括至少50或至少100个单元。这些单元可以适于加热或感测某种性质,诸如邻近单元的打印材料是否存在。这些单元可以包括具有或没有感测或加热性质的电阻器、或仅用于接收信号而不影响读取或写入动作的虚设单元。取决于单元的类型,可以使用至少一个ADC和/或DAC 1467来在数字和模拟之间转换信号,例如以经由接口1423促进信号转换。

第二逻辑电路1405可以包括可以确定内部时钟速度的第二计时器1435,所述时钟速度可以对应于所存储的时钟计数1433。

第二逻辑电路1405可以存储修订ID 1437,该修订ID可以通过打印设备与某些性质相关联。打印设备可以比较存储在相应的第一逻辑电路1403和第二逻辑电路1405上的第一修订ID和第二修订ID,如关于第一校验响应和第二校验响应解释的。

第二逻辑电路1405可以被配置为传送属于每个相应单元类别的至少一个单元计数1463,该至少一个单元计数可以对应于第一逻辑电路1403的单元计数1431。在另一个示例中,可以由打印设备逻辑电路或逻辑电路系统封装(当安装在打印设备中时)来探测每种类别的单元。例如,第二逻辑电路1405的单元计数可以通过测量最后一个传感器或最后一个传感器性质来确定。可以将所读取或测试的单元计数与在第一逻辑电路1403中存储的单元计数进行比较。

逻辑电路系统封装1401可以包括存储与读取和写入动作相关联的读/写历史的字段或数据部分1465,这些读取和写入动作与第二地址1404(例如,临时第二地址1404)相关联。逻辑电路系统封装可以被配置为在每个相应的读/写会话之后使用可以部分地基于读/写会话的内容和/或基于其他变量的算法函数来更新该字段,该功能可以为某种形式的位加扰。

第二逻辑电路1405可以包括第二存储器布置1461,该第二存储器布置存储这些第二逻辑电路特性中的至少一者,诸如单元计数1463、R/W历史1465和/或修订ID 1437。

如先前关于第一校验和第二校验所提到的,在一个示例中,不使用与来自第一逻辑电路1403的通信相同的密码密钥以密码方式认证来自第二逻辑电路1405的通信,和/或根本不以密码方式认证这些通信。在一个示例中,第二逻辑电路1405的信号输出可以是硬连线的,以对其输出信号进行加扰,这些输出信号进而可以由打印设备逻辑电路来解码。

图15图示了兼容的逻辑电路系统封装1501,其被配置为具有与图14的逻辑电路系统封装1401类似的对相应打印设备命令的响应。逻辑电路系统封装1501包括用于连接到打印设备接口总线的接口1523,例如,包括三个或四个I2C兼容的互连垫。第一逻辑电路系统封装1501包括存储器1507和CPU(中央处理单元)1509。封装1501可以存储用于对指向以下各项的对应命令作出响应的指令1545:(i)第一地址;以及在包括时间段的使能命令下,(ii)初始第二地址;以及当接收到重新配置的地址时,(iii)重新配置的第二地址(如由框1502、1504指示)。存储器1507可以存储特性1515、1519、1537中的至少一者,包括与可更换打印部件相关联的标识数据和状态1527。

该示例封装1501可以包括某些LUT、算法1505和/或被配置为生成响应的硬连线1551、1553、1555、1557,,打印设备逻辑电路将这些响应与这些单元相关联。在一个示例中,逻辑电路系统封装1501的硬连线具有与图14的单元阵列和单元类似的性质,以辅助生成兼容的输出信号或接收输入信号。在一个示例中,硬连线用于接收输入信号和/或模仿单元(诸如,电阻器和寄存器)。在一个示例中,硬连线可以包括对应于时钟计数1533的第二计时器或时钟。在另一个示例中,图14的第二逻辑电路可以被完全虚拟仿真取代,例如,使用所述LUT和/或算法1505,而没有附加的硬连线。输出LUT1505可以被配置为例如至少部分地基于已更新状态1527将某些接收到的命令和信号与某些可接受输出相关联。作为输出LUT1505的补充或替代,可以提供算法以生成兼容输出。因此,输出LUT、算法1505、以及硬连线1551、1553、1555、1557可以被配置为表示传感器阵列1451、1453、1455、1457或完整的第二逻辑电路1405(图14),其在图15的该示例中是至少部分地虚拟的并且不需要以打印设备将进行解译的方式来表示打印部件的实际状态。相反,LUT、算法1505和/或硬连线1551、1553、1555、1557可以促进工作中的兼容逻辑电路系统封装1501能够利用打印设备进行打印。

兼容封装1501将修订ID 1519、1537存储在例如一个字段中或两个字段中,或者至少被配置为基于对应的读取请求将其提供给打印设备。修订ID 1519、1537是打印设备逻辑电路可以与第二逻辑电路相关联的另一个ID,如该示例中所解释的,其可以非实体地存在,而是在某种程度上可以虚拟地表示。类似地,封装1501可以存储单元计数1531、1563、时钟计数1533,该时钟计数可以与或可以不与计时器1529、1535的相对或绝对时钟速度相关联。逻辑电路系统封装1501可以被配置为将与命令相关联的读/写历史1565存储和/或输出到重新配置的第二地址1504。修订ID、单元计数、时钟计数和读/写历史可以响应于经由第二地址(例如,重新配置的第二地址)的读取请求来可读取地提供,并且在进一步示例中,可以不使用密码密钥1541以密码方式认证。

该逻辑电路系统封装1501的某些特征可以与图14的第一逻辑电路1403类似或相同。例如,特性可以包括颜色、打印材料类型、颜色图1511、颜色转换配方1513、以及其他特性。一个或多个标识1515可以包括产品编号、品牌和/或要与可更换打印设备部件的标识相关联的任何代码。状态1527可以包括打印设备与打印材料水平相关联的数据。逻辑电路系统封装1501可以包括用于以密码方式认证消息的密码密钥1541,这些消息可以包括所述状态、特性和/或标识中的任一者。逻辑电路系统封装1501可以包括单独的专用认证逻辑1517并存储对应的时间窗1521。逻辑电路系统封装1501可以包括第一计时器1529、1535,用于测量如相应命令中所指示的计时器时段。在一个示例中,单个计时器装置1529、1535可以用于表示第一计时器和第二计时器。

此外,封装1501可以存储以下至少一项:指令1543,用于使用密钥1541以密码方式认证消息;指令1543,用于在时间窗1421内提供已认证的挑战响应;以及指令1545,用于基于包括计时器时段和/或任务的相应命令来设置地址1502、1504,包括例如用计时器1529、1535来测量时间段;以及其他认证或非认证指令。逻辑电路系统封装1401可以被配置为使得响应于指向第一地址的命令而进行的通信使用密码密钥1541(例如,伴有消息认证码和/或会话密钥标识符)以密码方式认证,而对指向第二地址的命令的响应可以不使用密钥1541(例如,不伴有消息认证码和/或会话密钥标识符)以密码方式认证。

先前提到的数据部分中的一些可以存储为数字签名的数据,诸如例如时间窗1521、修订ID 1519、1537、颜色转换配方1513、颜色图1511、单元计数1533和其他数据中的至少一者,以允许打印机相应地对该数据进行解码/解除签名。

在图14和图15的示例中,逻辑电路系统封装1401、1501的接口1423、1523的接口连接垫可以对应于图13A和图13B中所图示的接口触点。图15的示例可以完全地或主要地被提供在图13B的打印设备部件外部,而图14的示例可以部分地或主要地被提供在图13B的打印设备部件内部(例如,抵靠打印材料储器的内壁),但接口连接垫除外。

本文中描述的逻辑电路系统封装400a至400d、806a至806d、900、1401、1501中的每一者可以具有本文中描述的任何其他逻辑电路系统封装400a至400d、806a至806d、900、1401、1501或者处理电路系统424的任何特征。本文中描述的处理电路系统424可以具有逻辑电路系统封装400a至400d、806a至806d、900、1401、1501的任何特征。任何逻辑电路系统封装400a至400d、806a至806d、900、1401、1501或处理电路系统424均可以被配置为实施本文中描述的方法的至少一个方法框。任何第一逻辑电路均可以具有任何第二逻辑电路的任何属性,反之亦然。

本公开中的示例可以作为方法、系统或机器可读指令(诸如软件、硬件、固件等的任何组合)来提供。这种机器可读指令可以包括在其中或其上具有机器可读程序代码的机器可读存储介质(包括但不限于磁盘存储设备、CD-ROM、光学存储设备等)上。

参考根据本公开的示例的方法、装置和系统的流程图和框图来描述本公开。尽管上文描述的流程图示出了特定的执行顺序,但是执行顺序可以与所描绘的顺序不同。关于一个流程图描述的框可以与另一个流程图的框组合。应当理解,流程图和框图中的至少一些框以及其组合可以通过机器可读指令来实现。

机器可读指令可以例如由通用计算机、专用计算机、嵌入式处理器或其他可编程数据处理装置的处理器来执行,以实现说明书和图中描述的功能。具体地,处理器或处理电路系统可以执行机器可读指令。因此,可以通过执行存储在存储器中的机器可读指令的处理器或根据嵌入在逻辑电路系统中的指令操作的处理器来实施设备和装置的功能模块(例如,逻辑电路系统和/或控制器)。术语‘处理器’应当广义地解释为包括CPU、处理单元、ASIC、逻辑单元或可编程门阵列等。方法和功能模块可以全部由单个处理器执行,或者在若干处理器之间划分。

这种机器可读指令还可以存储在机器可读存储设备(例如,有形机器可读介质)中,该机器可读存储设备可以引导计算机或其他可编程数据处理装置以特定模式操作。

这种机器可读指令还可以被加载到计算机或其他可编程数据处理装置上,使得计算机或其他可编程数据处理装置执行一系列操作以产生计算机实施的处理,因此,在计算机或其他可编程装置上执行的指令实现了由流程图中和/或框图中的(多个)框所指定的功能。

进一步地,本文中的教导可以以计算机软件产品的形式来实施,该计算机软件产品存储在存储介质中并且包括用于使计算机装置实施本公开的示例中记载的方法的多个指令。

虽然已经参考某些示例描述了方法、设备和相关方面,但是可以在不脱离本公开的主旨的情况下进行各种修改、改变、省略和替代。因此,方法、设备和相关方面旨在仅受以下权利要求及其等效物的范围限制。应当注意,上文提到的示例图示而非限制本文中描述的内容,并且本领域技术人员将能够在不脱离所附权利要求的范围的情况下设计出许多替代实施方式。关于一个示例描述的特征可以与另一个示例的特征组合。

词语“包括(comprising)”不排除权利要求中列出的元素之外的元素的存在,“一个/种(a/an)”不排除多个,并且单个处理器或其他单元可以实现权利要求中记载的几个单元的功能。

任何从属权利要求的特征可以与任何独立权利要求或其他从属权利要求的特征组合。

在一些示例中,本公开包括以下陈述中的任一者。

陈述

1.一种逻辑电路系统封装,所述逻辑电路系统封装被配置为与打印设备逻辑电路通信,

其中,所述逻辑电路系统封装被配置为对向第一地址和至少一个第二地址发送的通信作出响应,并且

所述逻辑电路系统封装包括第一逻辑电路,其中,所述第一地址是用于所述第一逻辑电路的地址,并且

所述封装被配置为使得响应于向所述第一地址发送的指示任务和第一时间段的第一命令,所述封装在所述时间段的持续时间内可经由至少一个第二地址访问。

2.根据陈述1所述的逻辑电路系统封装,其中,所述封装用于与打印材料容器相关联。

3.根据陈述2所述的逻辑电路系统封装,进一步包括存储器,所述存储器存储代表所述打印材料容器的至少一个特性的数据。

4.根据任一前述陈述所述的逻辑电路系统封装,所述逻辑电路系统封装被配置为是I2C兼容的,并且其中,所述第一地址和第二地址中的至少一者是I2C兼容的地址。

5.根据任一前述陈述所述的逻辑电路系统封装,其中,所述封装在所述第一时间段之前的第二时间段内和/或在所述第一时间段之后的第三时间段内不可经由所述第二地址访问。

6.根据任一前述陈述所述的逻辑电路系统封装,所述逻辑电路系统封装被配置为:

在所述第一时间段之外,对向所述第一地址发送的通信作出响应并且不对向所述(多个)第二地址发送的通信作出响应;以及

在所述第一时间段期间,对向所述(多个)第二地址发送的通信作出响应并且不对向所述第一地址发送的通信作出响应。

7.根据任一前述陈述所述的逻辑电路系统封装,被配置为在每次开始所述第一时间段时将所述第二地址设置为初始第二地址。

8.根据陈述7所述的逻辑电路系统封装,其中,所述封装被配置为响应于向所述初始第二地址发送的命令将其第二地址设置为临时地址,所述命令包括所述临时地址。

9.根据陈述7或8所述的逻辑电路系统封装,其中,在接收到向所述第一地址发送的指示所述任务和所述第一时间段的后续命令时,所述逻辑电路系统封装被配置为具有相同的初始第二地址。

10.根据任一前述陈述所述的逻辑电路系统封装,其中,所述第一逻辑电路在所述时间段的持续时间内执行所述任务。

11.根据陈述10所述的逻辑电路系统封装,其中,所述任务包括以下至少一项:

激活所述第二地址、停用所述第一地址、将信号传输到所述封装的另一个逻辑电路、将所述初始第二地址重新配置为不同的临时第二地址、执行计算任务、以及监控所述第一逻辑电路的计时器。

12.根据任一前述陈述所述的逻辑电路系统封装,其中,所述第一逻辑电路包括用于测量所述时间段的持续时间的计时器。

13.根据任一前述陈述所述的逻辑电路系统封装,其中,所述第一逻辑电路被配置为在所述时间段的持续时间内不对向所述第一地址发送的命令作出响应。

14.根据任一前述陈述所述的逻辑电路系统封装,其中,所述封装被配置为:响应于向所述第一地址发送的通信而以第一模式操作;以及响应于向所述第二地址发送的通信而以第二模式操作。

15.根据任一前述陈述所述的逻辑电路系统封装,其中,所述封装被配置为:响应于向所述第一地址发送的以密码方式认证的通信,提供以密码方式认证的一组响应;以及响应于向所述至少一个第二地址发送的通信,提供不以密码方式认证的第二组响应。

16.根据任一前述陈述所述的逻辑电路系统封装,进一步包括第二逻辑电路,其中,所述第二地址是所述第二逻辑电路的地址。

17.根据陈述16所述的逻辑电路系统封装,其中,所述第二逻辑电路包括非易失性存储器、多个寄存器、计时器、以及读取和/或写入缓冲器中的至少一者。

18.根据陈述16或17所述的逻辑电路系统封装,其中,所述第二逻辑电路包括至少一个传感器或传感器阵列。

19.根据陈述16至18中任一项所述的逻辑电路系统封装,其中,所述封装包括在所述第一逻辑电路与所述第二逻辑电路之间的专用信号路径,并且所述至少一个第二地址通过所述第一逻辑电路经由所述专用信号路径发送信号来启用,并且其中,所述封装被配置为响应于所述第一命令来激活所述第二逻辑电路。

20.根据陈述19所述的逻辑电路系统封装,其中,所述信号在所述时间段的持续时间内存在。

21.根据任一前述陈述所述的逻辑电路系统封装,所述逻辑电路系统封装包括至少一个传感器或传感器阵列。

22.根据陈述20所述的逻辑电路系统封装,其中,所述至少一个传感器或传感器阵列包括打印材料水平传感器和另一传感器类型中的至少一者。

23.根据任一前述陈述所述的逻辑电路系统封装,所述逻辑电路系统封装被配置为在所述时间段之外并且响应于向所述第一地址发送的通信来传输使用密钥认证的通信,并且所述逻辑电路系统封装进一步被配置为在所述时间段期间并且响应于向所述第二地址发送的通信来传输不使用该密钥认证的通信。

24.根据任一前述陈述所述的逻辑电路系统封装,所述逻辑电路系统封装被配置为在所述时间段之外并且响应于向所述第一地址发送的通信来传输使用密钥认证的与打印材料水平有关的数据,并且所述逻辑电路系统封装进一步被配置为在所述时间段期间并且响应于向所述第二地址发送的通信来传输不使用所述密钥认证的与打印材料水平有关的数据,其中,与打印材料水平有关的数据是所述打印设备逻辑电路解释的且表示为所述逻辑电路系统封装所属的打印部件的打印材料水平的数据。

25.根据陈述23或24所述的逻辑电路系统封装,其中,所述密钥是加密密钥和/或秘密基础密钥。

26.一种可更换打印设备部件,包括任一前述陈述所述的逻辑电路系统封装,所述部件进一步包括一定体积的液体,

所述部件的高度大于宽度并且长度大于所述高度,所述宽度在两侧之间延伸,并且其中:

所述封装包括用于与所述打印设备逻辑电路通信的接口垫,并且这些接口垫设置在面向供插入数据互连件的切口的一侧的内侧,这些接口垫沿着高度方向在所述部件的顶部和前部附近延伸,并且这些接口垫包括数据垫,所述数据垫是这些接口垫中的最底部垫,

并且所述部件的液体和空气接口以平行于所述高度方向的相同竖直参考轴设置在前部处,其中,所述竖直轴平行于与这些接口垫相交的轴线并与其有一定距离。

27.根据陈述26所述的可更换打印设备部件,其中,所述逻辑电路系统封装的其余部分也被设置为抵靠所述内侧。

28.根据陈述1至25中任一项所述的多个封装,所述多个封装具有不同的第一地址和相同的第二地址。

29.一种可更换打印设备部件,包括I2C兼容的逻辑电路系统封装,其中,所述I2C兼容的逻辑电路系统封装包括:

I2C接口,所述I2C接口包括用于经由主机打印设备的I2C总线进行通信的数据触点;

存储器,所述存储器包括表示打印液体特性的数据,所述数据可经由所述数据触点取得和更新;

其中,所述封装被配置为通过所述数据触点将包括表示打印液体特性的所述数据的数据传输到所述总线;以及

其中,所述封装进一步被配置为:响应于向第一地址发送的指示第一时间段的命令,随后对在所述时间段的持续时间内通过相同总线和数据触点向至少一个第二地址发送的命令作出响应;以及

在所述时间段结束之后,再次对通过相同总线和数据触点向所述第一地址传输的命令作出响应。

30.根据陈述29所述的可更换打印设备部件,其中,所述命令还指示任务。

31.根据陈述29所述的可更换打印设备部件,其中,

所述第二地址包括初始第二地址,并且

所述封装被配置为:响应于到所述初始第二地址的包括临时地址的命令,对在所述时间段结束之前通过相同总线和数据触点向所述临时地址发送的数据作出响应。

32.一种打印盒,包括根据陈述1至25中任一项所述的I2C兼容的逻辑电路系统封装并且具有壳体,所述壳体的宽度小于高度,其中,在前表面中,从底部到顶部,分别设置打印液体输出、空气输入和凹部,所述凹部在所述顶部处延伸,其中,所述封装的I2C总线触点抵靠所述壳体的侧壁内侧、邻近所述壳体的顶部和前部被提供在所述凹部的一侧处,所述数据触点是所述触点中的最低触点。

33.根据陈述32所述的打印盒,其中,所述封装的第一逻辑电路同样被设置为抵靠所述侧壁的内侧。

34.一种方法,包括:

响应于经由通信总线向处理电路系统的第一地址发送的指示任务和第一时间段的第一命令,由所述处理电路系统在所述时间段的持续时间内启用经由至少一个第二地址对所述处理电路系统的访问。

35.根据陈述34所述的方法,其中,所述方法在设置在可更换打印设备部件上的处理电路系统上实施。

36.根据陈述34或35所述的方法,进一步包括:在所述时间段的持续时间内禁用经由所述第一地址对所述处理电路系统的访问。

37.根据陈述34至36所述的方法,进一步包括:在所述时间段的持续时间之后,禁用经由任何第二地址对所述处理电路系统的访问。

38.根据陈述34至37所述的方法,进一步包括:使用所述处理电路系统的计时器来监控所述时间段的持续时间。

39.根据陈述34至38中任一项所述的方法,其中,所述第一地址与第一逻辑电路相关联,并且所述第二地址与第二逻辑电路相关联,并且所述方法包括:由所述第一逻辑电路在所述时间段的持续时间内执行所述任务。

40.根据陈述33至38中任一项所述的方法,其中,所述第一地址与第一逻辑电路相关联,并且所述至少一个第二地址与第二逻辑电路相关联,并且其中,启用经由所述第二地址对所述处理电路系统的访问包括激活所述第二逻辑电路。

41.根据陈述40所述的方法,其中,所述方法包括所述第一逻辑电路向所述第二逻辑电路发送激活信号以激活所述电路系统。

42.根据陈述41所述的方法,其中,所述方法进一步包括:通过停止所述激活信号来停用所述第二逻辑电路。

43.根据陈述40至42所述的方法,所述方法包括经由专用信号路径发送所述激活信号。

44.根据陈述34至43中任一项所述的方法,其中,在所述第一时间段开始时,所述第二地址被配置为初始第二地址。

45.根据陈述44所述的方法,所述方法包括由所述处理电路系统响应于在所述第一时间段期间向所述初始第二地址发送且包括临时地址的命令而将所述初始第二地址重新配置为所述临时地址。

46.根据陈述44或陈述45所述的方法,其中,在接收到向所述第一地址发送的指示所述任务和所述第一时间段的后续命令时,所述处理电路系统被配置为具有相同的初始第二地址。

47.一种供与可更换打印设备部件一起使用的处理电路系统,所述处理电路系统包括:

存储器和第一逻辑电路,所述第一逻辑电路用于启用从所述存储器进行的读取操作,

其中,所述处理电路系统可经由其中安装有所述可更换打印设备部件的打印设备的I2C总线访问,并且与第一地址和至少一个第二地址相关联,并且所述第一地址是用于所述第一逻辑电路的I2C地址,并且

其中,所述第一逻辑电路参与由其中安装有所述可更换打印设备部件的打印设备对所述可更换打印设备部件的认证;以及

所述处理电路系统被配置为使得在接收到经由所述第一地址向所述第一逻辑电路发送的指示第一时间段的第一命令之后,所述处理电路系统在所述时间段的持续时间内可经由至少一个第二地址访问。

48.根据陈述47所述的处理电路系统,其中,所述处理电路系统进一步包括第二逻辑电路,其中,所述第二逻辑电路可经由所述至少一个第二地址访问,并且其中,所述第二逻辑电路包括至少一个传感器,所述至少一个传感器可由其中安装有所述可更换打印设备部件的打印设备经由所述至少一个第二地址读取。

49.根据陈述47或48所述的处理电路系统,其中,可由其中安装有所述可更换打印设备部件的打印设备经由所述至少一个第二地址读取的所述至少一个传感器不可经由所述第一地址读取。

50.根据陈述47至49中任一项所述的处理电路系统,其中,所述传感器包括耗材水平传感器。

在一些示例中,本公开包括以下段落中的任一者

段落

1.一种逻辑电路系统封装,具有第一地址并且包括第一逻辑电路,

其中,所述第一地址是用于所述第一逻辑电路的I2C地址,并且其中,所述封装被配置为使得:响应于向所述第一地址发送的指示任务和第一时间段的第一命令,所述第一逻辑电路在所述时间段的持续时间内进行以下操作:

(i)执行任务,以及

(ii)忽视向所述第一地址发送的I2C流量。

2.根据段落1所述的逻辑电路系统封装,其中,所述第一逻辑电路进一步包括用于测量所述时间段的计时器。

3.根据段落2所述的逻辑电路系统封装,其中,由所述逻辑电路系统封装执行的所述任务包括以下至少一项:监控所述计时器以及执行计算任务,所述计算任务具有超出所述时间段的完成时间。

4.根据任一前述段落所述的逻辑电路系统封装,其中,所述封装用于与打印材料容器相关联。

5.根据段落4所述的逻辑电路系统封装,进一步包括存储器,所述存储器存储代表所述打印材料容器的至少一个特性的数据。

6.根据任一前述段落所述的逻辑电路系统封装,其中,所述封装包括第二逻辑电路,并且所述封装被配置为使所述第二逻辑电路在所述时间段期间可访问。

7.根据段落6所述的逻辑电路系统封装,其中,所述封装包括在所述第一逻辑电路与第二逻辑电路之间的专用信号路径,并且通过所述第一逻辑电路经由所述专用信号路径发送信号使所述第二逻辑电路可访问。

8.根据段落7所述的逻辑电路系统封装,其中,所述信号在所述时间段的持续时间内存在。

9.根据任一前述段落所述的逻辑电路系统封装,所述封装包括至少一个传感器或传感器阵列。

10.根据段落9所述的逻辑电路系统封装,其中,所述至少一个传感器包括至少一个打印材料水平传感器。

11.根据任一前述段落所述的逻辑电路系统封装,其中,所述封装具有至少一个第二地址,并且被配置为使得响应于所述第一命令,所述封装在所述时间段的持续时间内可经由第二地址访问。

12.根据段落11所述的逻辑电路系统封装,其中,所述封装被配置为:响应于向所述第一地址发送的指令而提供第一组响应;以及响应于向第二地址发送的指令而提供第二组响应。

13.根据段落11或段落12所述的逻辑电路系统封装,其中,所述封装被配置为:响应于向所述第一地址发送的指令而以第一模式操作;以及响应于向所述第二地址发送的指令而以第二模式操作。

14.根据段落11至13中任一项所述的逻辑电路系统封装,其中,所述封装被配置为:响应于向所述第一地址发送的以密码方式认证的通信,提供以密码方式认证的一组响应;以及响应于向所述第二地址发送的通信,提供不以密码方式认证的第二组响应。

15.根据段落11至14中任一项所述的逻辑电路系统封装,所述封装被配置为在所述时间段之外并且响应于向所述第一地址发送的通信来传输使用加密密钥认证的与打印材料水平有关的数据,并且所述封装进一步被配置为在所述时间段期间并且响应于向所述第二地址发送的通信来传输不使用所述密钥认证的与打印材料水平有关的数据。

16.根据段落11至15中任一项所述的逻辑电路系统封装,其中,所述至少一个第二地址是第二逻辑电路的地址。

17.根据段落11至16中任一项所述的逻辑电路系统封装,其中,所述封装在所述第一时间段之前的第二时间段内和/或在所述第一时间段之后的第三时间段内不可经由所述第二地址访问。

18.根据段落11至17中任一项所述的逻辑电路系统封装,被配置为在每次开始所述第一时间段时将所述第二地址设置为初始第二地址。

19.根据段落18所述的逻辑电路系统封装,其中,所述封装被配置为响应于向所述初始第二地址发送的命令将所述封装的第二地址设置为临时地址,所述命令包括所述临时地址。

20.根据段落18或19所述的逻辑电路系统封装,其中,在接收到向所述第一地址发送的指示任务和所述第一时间段的后续命令时,所述逻辑电路系统封装被配置为具有相同的初始第二地址。

21.根据段落11至20中任一项所述的逻辑电路系统封装,被配置为:

在所述第一时间段之外,对指向所述第一地址的命令作出响应而不对指向所述第二地址的命令作出响应;以及

在所述第一时间段期间,对指向所述第二地址的命令作出响应而不对指向所述第一地址的命令作出响应。

22.根据段落11至21中任一项所述的多个逻辑电路系统封装,所述多个逻辑电路系统封装具有不同的第一地址和相同的第二地址。

23.一种方法,包括:

响应于经由I2C总线向处理电路系统的第一地址发送的指示任务和第一时间段的第一命令,在所述时间段的持续时间内进行以下操作:

(i)由所述处理电路系统执行任务,以及

(ii)忽视向所述第一地址发送的I2C流量

所述方法包括:在所述时间段的持续时间内,使用所述处理电路系统的计时器来监控所述时间段。

24.根据段落23所述的方法,其中,所述方法是在设置在可更换打印设备部件上的处理电路系统上实施的。

25.根据段落23至24中任一项所述的方法,进一步包括:在所述时间段的持续时间内,由所述处理电路系统对向所述处理电路系统的至少一个第二地址发送的I2C流量作出响应。

26.根据段落25所述的方法,其中,所述第一地址与所述处理电路系统的第一逻辑电路相关联,并且所述至少一个第二地址与所述处理电路系统的第二逻辑电路相关联。

27.根据段落25或26所述的方法,进一步包括:在所述时间段的持续时间之后,禁用经由所述至少一个第二地址对所述处理电路系统的访问。

28.根据段落25至27中任一项所述的方法,其中,在所述第一时间段开始时,所述第二地址被配置为初始第二地址。

29.根据段落28所述的方法,其中,所述处理电路系统被配置为:响应于在所述第一时间段期间向所述初始第二地址发送的且包括临时第二地址的命令,将其第二地址重新配置为该临时地址。

30.根据段落29所述的方法,其中,在接收到向所述第一地址发送的指示所述任务和所述第一时间段的后续命令时,所述逻辑电路系统被配置为具有相同的初始第二地址。

31.根据段落23至30中任一项所述的方法,其中,所述处理电路系统包括所述处理电路系统的第一逻辑电路和第二逻辑电路,其中,所述第一逻辑电路在所述时间段的持续时间内执行所述任务并向所述第二逻辑电路发送激活信号。

32.根据段落31所述的方法,其中,所述方法进一步包括:通过停止所述激活信号来停用所述第二逻辑电路。

33.根据段落31或32所述的方法,其中,所述激活信号是经由专用信号路径来发送的。

34.根据段落23至33中任一项所述的方法,其中,由所述处理电路系统执行的任务是所述第一命令中所指示的任务。

35.一种处理电路系统,所述处理电路系统供与可更换打印设备部件一起使用以连接到打印设备逻辑电路,所述处理电路系统包括:

存储器和第一逻辑电路,所述第一逻辑电路用于启用从所述存储器进行的读取操作并执行处理任务,所述第一逻辑电路包括计时器,

其中,所述处理电路系统能够经由其中安装有所述可更换打印设备部件的打印设备的I2C总线访问,并且与第一地址和至少一个第二地址相关联,并且所述第一地址是用于所述第一逻辑电路的I2C地址,并且

其中,所述第一逻辑电路参与由其中安装有所述可更换打印设备部件的打印设备对所述可更换打印设备部件的认证;以及

所述处理电路系统被配置为使得响应于经由所述第一地址向所述第一逻辑电路发送的指示任务和第一时间段的第一命令,所述处理电路在如由所述计时器测量的所述时间段的持续时间内进行以下操作:

(i)执行任务,以及

(ii)不向所述第一地址发送的I2C流量作出响应。

36.根据段落35所述的处理电路系统,其中,所述处理电路系统进一步包括第二逻辑电路,其中,所述第二逻辑电路能够经由所述I2C总线和第二地址访问,并且所述第一逻辑电路用于生成激活信号以在所述时间段的持续时间内激活所述第二逻辑电路。

37.根据段落36所述的处理电路系统,其中,所述处理电路系统包括在所述第一逻辑电路与第二逻辑电路之间的专用信号路径以用于传输所述激活信号。

38.根据段落36或37所述的处理电路系统,其中,所述第二逻辑电路包括至少一个传感器,所述至少一个传感器可由其中安装有所述可更换打印设备部件的打印设备经由所述第二地址读取。

39.根据段落36至38中任一项所述的处理电路系统,所述处理电路系统包括至少一个传感器,所述至少一个传感器可由其中安装有所述可更换打印设备部件的打印设备经由所述第二地址读取并且不能经由所述第一地址读取。

40.根据段落38或39所述的处理电路系统,其中,所述传感器包括耗材水平传感器。

41.多个打印部件,每个打印部件包括存储器,其中,不同打印部件的存储器存储不同打印液体特性,并且每个打印部件包括根据段落1至21中任一项所述的逻辑电路系统封装或根据段落35至40所述的处理电路系统。

42.一种打印盒,包括根据段落1至21中任一项所述的逻辑电路系统封装并且具有壳体,所述壳体的宽度小于高度,其中,在前面中,从底部到顶部,分别设置打印液体输出部、空气输入和凹部,所述凹部在所述顶部处延伸,其中,所述封装的I2C总线触点抵靠所述壳体的侧壁内侧、邻近所述壳体的顶部和前部被提供在所述凹部的一侧处,并且包括数据触点,所述数据触点是这些I2C总线触点中的最低触点。

43.根据段落42所述的打印盒,其中,所述封装的第一逻辑电路同样被设置为抵靠所述侧壁的内侧。

44.一种可更换打印设备部件,包括段落1至21中任一项所述的逻辑电路系统封装,所述部件进一步包括一定体积的液体,所述部件的高度大于宽度并且长度大于所述高度,所述宽度在两侧之间延伸,其中,所述封装包括接口垫,并且所述接口垫设置在面向供插入数据互连件的切口的一侧的内侧,所述接口垫沿着高度方向在所述部件的顶部和前部附近延伸,并且数据垫是所述接口垫中的最底部的垫,所述部件的液体和空气接口以平行于所述高度方向的相同竖直参考轴设置在前部,其中,所述竖直轴平行于与所述接口垫相交的轴线并与其有一定距离。

45.根据段落44所述的可更换打印设备部件,其中,所述逻辑电路系统封装的其余部分也被设置为抵靠所述内侧。

在一些示例中,本公开包括以下条款中的任一者:

条款

1.一种逻辑电路系统封装,

被配置为可经由第一地址和至少一个第二地址寻址并且包括第一逻辑电路,

其中,所述第一地址是用于所述第一逻辑电路的地址,其中,所述封装被配置为使得:

响应于向所述第一地址发送的指示第一命令时间段的第一命令,所述封装可在所述第一命令时间段的持续时间内经由至少一个第二地址访问;以及

响应于向所述第一地址发送的指示第二命令时间段的第二命令,所述第一逻辑电路在所述第二命令时间段的持续时间内忽视向所述第一地址发送的流量。

2.根据条款1所述的逻辑电路系统封装,其中,所述第一逻辑电路包括计时器,其中,所述第一命令时间段和/或第二命令时间段由所述计时器测量。

3.根据条款1或条款2所述的逻辑电路系统封装,其中,响应于所述第二命令,所述逻辑电路被配置为在至少所述第一或第二命令时间段期间执行处理任务。

4.根据条款3所述的逻辑电路系统封装,其中,所述处理任务包括以下至少一项:监控计时器并执行计算任务,所述计算任务具有超出所述第一命令时间段和/或第二命令时间段的完成时间。

5.根据任一前述条款所述的逻辑电路系统封装,其中,所述第二命令时间段长于所述第一命令时间段,并且所述第一逻辑电路响应于所述第二命令要在所述第二命令时间段的持续时间内不对向所述第一地址发送的流量作出响应。

6.根据任一前述条款所述的逻辑电路系统封装,其中,所述封装用于与打印材料容器相关联。

7.根据条款6所述的逻辑电路系统封装,进一步包括存储器,所述存储器存储代表所述打印材料容器的至少一个特性的数据。

8.根据任一前述条款所述的逻辑电路系统封装,其中,所述封装包括第二逻辑电路,并且所述封装被配置为使所述第二逻辑电路在所述第一命令时间段期间可访问。

9.根据条款8所述的逻辑电路系统封装,其中,所述封装包括所述第一和第二逻辑电路之间的专用信号路径,并且通过所述第一逻辑电路经由所述专用信号路径发送信号使所述第二逻辑电路可访问。

10.根据条款9所述的逻辑电路系统封装,其中,所述信号在所述第一命令时间段的持续时间内存在。

11.根据任一前述条款所述的逻辑电路系统封装,所述封装包括至少一个传感器或至少一个传感器阵列。

12.根据条款11所述的逻辑电路系统封装,其中,所述至少一个传感器或至少一个传感器阵列包括至少一个打印材料水平传感器。

13.根据任一前述条款所述的逻辑电路系统封装,其中,所述封装被配置为使得响应于所述第二命令,所述封装可在所述第二命令时间段的持续时间内经由第二地址访问。

14.根据条款13所述的逻辑电路系统封装,其中,所述封装被配置为:响应于向所述第一地址发送的指令而提供第一组响应;以及响应于向第二地址发送的指令而提供第二组响应。

15.根据条款13或14所述的逻辑电路系统封装,其中,所述封装被配置为:响应于向所述第一地址发送的指令而以第一模式操作;以及响应于向所述第一地址发送的指令而以第二模式操作。

16.根据条款13至15中任一项所述的逻辑电路系统封装,其中,所述封装被配置为:响应于向所述第一地址发送的以密码方式认证的指令,提供以密码方式认证的一组响应;以及响应于向所述第二地址发送的指令,提供不以密码方式认证的第二组响应。

17.根据条款13至16中任一项所述的逻辑电路系统封装,其中,所述第二地址是所述第二逻辑电路的地址。

18.根据条款13至17中任一项所述的逻辑电路系统封装,其中,所述封装在所述第一命令时间段之前的时间段内和/或在所述第一命令时间段之后的时间段内不可经由所述第二地址访问。

19.根据条款13至18中任一项所述的逻辑电路系统封装,其中,所述第二地址在所述第一命令时间段开始时被配置为初始第二地址。

20.根据条款19所述的逻辑电路系统封装,其中,所述封装被配置为:在所述第一命令时间段期间响应于向所述初始第二地址发送的且包括临时地址的命令而将其第二地址重新配置为所述临时地址。

21.根据条款19或20所述的逻辑电路系统封装,其中,在接收到向所述第一地址发送的指示所述第一命令时间段的后续命令时,所述逻辑电路系统封装被配置为具有相同的初始第二地址。

22.根据任一前述条款所述的逻辑电路系统封装,所述封装被配置为:

在所述第一命令时间段之外对指向所述第一地址的命令作出响应而不对指向第二地址的命令作出响应;以及

在所述第一命令时间段期间对指向第二地址的命令作出响应而不对指向所述第一地址的命令作出响应。

23.多个根据条款13至22中任一项所述的逻辑电路系统封装,其具有不同的第一地址和相同的第二地址。

24.根据条款23所述的多个逻辑电路系统封装,其存储代表不同打印材料容器的至少一个特性的不同数据。

25.一种方法,包括:

响应于经由I2C总线向处理电路系统的第一地址发送的指示第一命令时间段的第一命令,由所述处理电路系统在所述第一命令时间段的持续时间内启用经由至少一个第二地址对所述处理电路系统的访问;以及

响应于经由所述I2C总线向所述第一地址发送的指示第二命令时间段的第二命令并且在所述第二命令时间段的持续时间内,忽略向所述第一地址发送的I2C流量;

所述方法进一步包括:使用所述处理电路系统的计时器来监控所述第一和第二命令时间段中的至少一者。

26.根据条款25所述的方法,其中,所述方法是在被设置在可更换打印设备部件上的处理电路系统上实施的。

27.根据条款25或26所述的方法,其中,响应于所述第二命令,所述处理电路系统执行任务。

28.根据条款27所述的方法,其中,所述任务是所述第二命令中所指示的任务。

29.根据条款25至28中任一项所述的方法,进一步包括:在所述第一命令时间段的持续时间内,由所述处理电路系统对向所述处理电路系统的所述至少一个第二地址发送的I2C流量作出响应。

30.根据条款29所述的方法,其中,所述第一地址与所述处理电路系统的第一逻辑电路相关联,并且所述至少一个第二地址与所述处理电路系统的第二逻辑电路相关联。

31.根据条款30所述的方法,进一步包括:在所述第一命令时间段的持续时间之后,将经由所述至少一个第二地址对所述处理电路系统的访问禁用。

32.根据条款25至31中任一项所述的方法,其中,所述第二地址在所述第一命令时间段开始时被配置为初始第二地址。

33.根据条款32所述的方法,其中,所述处理电路系统被配置为:在所述第一命令时间段期间响应于向所述初始第二地址发送的且包括临时地址的命令而将其第二地址重新配置为所述临时地址。

34.根据条款33所述的方法,其中,在接收到向所述第一地址发送的指示所述第一命令时间段的后续命令时,所述处理电路系统被配置为具有相同的初始第二地址。

35.根据条款25至34中任一项所述的方法,其中,所述处理电路系统包括所述处理电路系统的第一逻辑电路和第二逻辑电路,其中,所述方法包括:由所述第一逻辑电路在所述第一命令时间段的持续时间内向所述第二逻辑电路发送激活信号。

36.根据条款35所述的方法,其中,所述方法进一步包括:通过停止所述激活信号来停用所述第二逻辑电路。

37.根据条款35或36所述的方法,其包括经由专用信号路径发送所述激活信号。

38.一种用于与可更换打印设备部件一起使用的处理电路系统,所述处理电路系统包括:

存储器和第一逻辑电路,所述第一逻辑电路用于启用从所述存储器进行的读取操作并执行处理任务,所述第一逻辑电路包括计时器,

其中,所述处理电路系统可经由其中安装有所述可更换打印设备部件的打印设备的I2C总线访问,并且与第一地址和至少一个第二地址相关联,并且所述第一地址是用于所述第一逻辑电路的I2C地址,并且

其中,所述第一逻辑电路参与由其中安装有所述可更换打印设备部件的打印设备对所述可更换打印设备部件的认证;以及

其中,所述电路系统被配置为使得:

响应于向所述第一地址发送的指示第一命令时间段的第一命令,所述处理电路可在所述第一命令时间段的持续时间内经由至少一个第二地址访问;以及

响应于向所述第一地址发送的指示第二命令时间段的第二命令,所述第一逻辑电路在如由所述计时器测量的所述第二命令时间段的持续时间内忽略向所述第一地址发送的I2C流量。

39.根据条款38所述的处理电路系统,其中,所述第一逻辑电路被配置为可在所述第一命令时间段的持续时间内经由所述至少一个第二地址访问。

40.根据条款39所述的处理电路系统,其中,所述处理电路系统进一步包括第二逻辑电路,其中,所述第二逻辑电路可经由所述I2C总线和第二地址访问,并且所述第一逻辑电路用于生成激活信号以在所述第一命令时间段的持续时间内激活所述第二逻辑电路。

41.根据条款40所述的处理电路系统,其中,所述处理电路系统包括所述第一和第二逻辑电路之间的专用信号路径以用于传输所述激活信号。

42.根据条款39或41所述的处理电路系统,其中,所述第二逻辑电路包括至少一个传感器或传感器阵列,所述至少一个传感器或传感器阵列可由其中安装有所述可更换打印设备部件的打印设备经由所述至少一个第二地址读取。

43.根据条款42所述的处理电路系统,其中,可由其中安装有所述可更换打印设备部件的打印设备经由所述至少一个第二地址读取的所述至少一个传感器或传感器阵列不可经由所述第一地址读取。。

44.根据条款42或43中任一项所述的处理电路系统,其中,所述传感器包括耗材水平传感器。

45.根据条款42至44中任一项所述的处理电路系统,其中响应于所述第一命令,所述处理电路系统在如由所述计时器测量的所述第一命令时间段的持续时间内忽略向所述第一地址发送的I2C流量;和/或响应于所述第二命令,所述处理电路可在所述第一命令时间段的持续时间内经由至少一个第二地址访问。

46.多个打印部件,每个打印部件包括存储器,其中,不同打印部件的这些存储器存储不同打印液体特性,并且每个打印部件包括根据条款1至22中任一项所述的逻辑电路系统封装。

47.一种打印盒,包括根据条款1至22中任一项所述的逻辑电路系统封装并且具有壳体,所述壳体的宽度小于高度,其中,在前表面中,从底部到顶部,分别提供打印液体输出端、空气输入端和凹部,所述凹部在所述顶部处延伸,其中,所述封装的I2C总线触点抵靠所述壳体的侧壁内侧、邻近所述壳体的顶部和前部被提供在所述凹部的一侧处,这些I2C总线触点包括数据触点,所述数据触点是这些触点中的最低触点。

48.根据条款47所述的打印盒,其中,所述封装的第一逻辑电路同样被设置为抵靠所述侧壁的内侧。

49.一种可更换打印设备部件,包括条款1至22中任一项所述的逻辑电路系统封装,所述部件进一步包括一定体积的液体,所述部件的高度大于宽度并且长度大于所述高度,所述宽度在两侧之间延伸,所述封装包括接口垫,其中,这些接口垫设置在面向供插入数据互连件的切口的一侧的内侧处,这些接口垫沿着高度方向在所述部件的顶部和前部附近延伸,并且包括数据垫,所述数据垫是这些接口垫中的最底部垫,所述部件的液体和空气接口以平行于所述高度方向的相同竖直参考轴上被提供在前部处,其中,所述竖直轴平行于与这些接口垫相交的轴线并与其有一定距离。

50.根据条款49所述的可更换打印设备部件,其中,所述逻辑电路系统封装的其余部分也被设置为抵靠所述内侧。

在一些示例中,本公开包括以下描述中的任一者:

描述

1.一种方法,包括:由与可更换打印设备部件相关联的逻辑电路系统进行以下操作:

以第一校验响应对经由I2C总线向与所述逻辑电路系统相关联的第一地址发送的第一校验请求作出响应;以及

以第二校验响应对经由所述I2C总线向与所述逻辑电路系统相关联的第二地址发送的第二校验请求作出响应。

2.根据描述1所述的方法,其中,所述第一校验响应包括以密码方式认证的响应。

3.根据描述2所述的方法,其中,

所述逻辑电路系统存储打印设备部件特性数据和用于以密码方式认证所传送的数据的第一密钥,其中,所述第一密钥与存储在所述打印设备上的用于以密码方式认证的第二密钥有关,并且

所述以密码方式认证的响应包括使用所述第一密钥进行加密的所述特性数据、以及从所述第一密钥和所述第二密钥中的所述至少一者得到的消息认证码和会话密钥标识符中的至少一者。

4.根据描述3所述的方法,其中,所述第二校验响应包括比特流,所述比特流不使用所述第一密钥进行加密并且不伴有消息认证码和/或会话密钥标识符。

5.根据描述2至4中任一项所述的方法,其中,

响应于经由所述第一地址的以密码方式认证的命令而使用密钥来认证的所述第一以密码方式认证的响应包括:在解码之后将由接收打印设备逻辑电路表示为或用作打印材料水平数据的数据,以及

响应于经由所述第二地址接收到的命令而不使用所述密钥认证的另一个响应也包括:在解码之后将由所述接收打印设备逻辑电路表示为或用作打印材料水平数据的数据。

6.根据任一前述描述所述的方法,其中,所述第二校验响应包括未加密响应。

7.根据任一前述描述所述的方法,其中,所述第二校验请求包括对于所述逻辑电路系统的计时器的时钟速度的指示的请求,并且所述方法包括相对于另一个可测量时钟信号或周期来确定所述逻辑电路系统的时钟速度。

8.根据任一前述描述所述的方法,进一步包括:在接收到所述第一校验请求之后,接收经由所述I2C总线向与所述逻辑电路系统相关联的初始第二地址发送的地址设置信号,其中,所述地址设置信号指示临时第二地址;以及将所述临时第二地址设置为所述逻辑电路系统的地址。

9.根据描述8所述的方法,其中,所述初始地址是在设置临时地址的每个时机之前要使用的默认地址。

10.根据任一前述描述所述的方法,其包括:通过读取所述逻辑电路系统的存储器以提供版本标识的指示,来确定所述第二校验响应。

11.根据任一前述描述所述的方法,包括:通过测试所述逻辑电路系统的至少一个部件以返回测试结果,来确定所述第二校验响应。

12.根据任一前述描述所述的方法,包括:通过读取所述逻辑电路系统的存储器以提供至少一种传感器类别中的传感器的数量的指示,来确定所述第二校验响应。

13.根据任一前述描述所述的方法,包括:确定所述第二校验响应,所述第二校验响应包括所述逻辑电路系统的读/写历史的指示。

14.根据描述13所述的方法,进一步包括:存储所述逻辑电路系统的读/写状态的指示;以及用所述逻辑电路系统的读/写请求来更新所存储的指示。

15.根据描述14所述的方法,当其从属于描述8时,其中,当将所述逻辑电路系统的地址重写为所述临时第二地址时,不更新所述指示。

16.根据描述14至15中任一项所述的方法,其中,更新所述指示包括:将预定算法函数应用于读/写请求和/或响应以确定经更新的指示。

17.根据描述13至16中任一项所述的方法,其中,读/写状态的多个指示存储在存储器中,每个指示使用不同的预定算法函数来确定,并且其中,所述第二校验请求包括对于这些所存储指示中的一者的请求,并且所述方法包括为所述指示提供响应。

18.一种用于可更换打印设备部件的逻辑电路系统封装,所述逻辑电路系统封装可经由第一地址和第二可重新配置地址寻址;

其中,所述封装被配置为:基于向所述第一地址发送的通信来参与第一校验过程;

以及基于向所述第二地址发送的通信来参与第二校验过程。

19.根据描述18所述的逻辑电路系统封装,其中,所述逻辑电路系统封装是使用I2C兼容的地址而与I2C兼容的。

20.根据描述18或19所述的逻辑电路系统封装,其中,所述第二可重新配置地址在默认地址和至少一个不同地址之间是可重新配置的。

21.根据描述18至20中任一项所述的逻辑电路系统封装,其中,所述封装包括存储器,所述存储器包括被配置为经由所述第二地址读取的标识数据。

22.根据描述21所述的逻辑电路系统封装,其中,相同的标识数据存储在所述封装中,以便经由所述第一地址通过以密码方式认证的通信来读取。

23.根据描述18至22中任一项所述的逻辑电路系统封装,其中,所述封装包括存储器,所述存储器包括被配置为经由所述第二地址读取的读/写历史数据部分。

24.根据描述23所述的逻辑电路系统封装,其中,所述存储器进一步包括至少一个单元计数。

25.根据描述24所述的逻辑电路系统封装,其中,所述至少一个单元计数被配置为经由所述第二地址读取。

26.根据描述25所述的逻辑电路系统封装,其中,相同的至少一个单元计数数据被配置为经由所述第一地址通过以密码方式认证的通信来读取。

27.根据描述24至26中任一项所述的逻辑电路系统封装,包括至少一个单元或单元阵列,所述至少一个单元或单元阵列的数量对应于所存储的单元计数。

28.根据描述18至27中任一项所述的逻辑电路系统封装,其中,所述存储器进一步存储时钟计数。

29.根据描述28所述的逻辑电路系统封装,其中,所述时钟计数表示所述封装的计时器的相对或绝对时钟速度。

30.根据描述18至29中任一项所述的逻辑电路系统封装,其中,

所述逻辑电路系统存储打印设备部件特性数据和用于以密码方式认证所传送的数据的第一密钥,其中,所述第一密钥与存储在所述打印设备上的用于以密码方式认证的第二密钥有关,并且

参与所述第一校验过程包括发送以密码方式认证的响应,所述以密码方式认证的响应包括使用所述第一密钥进行加密的所述特性数据、以及从所述第一密钥和所述第二密钥中的所述至少一者得到的消息认证码和会话密钥标识符中的至少一者。

31.根据描述30所述的逻辑电路系统封装,被配置为通过发送包括比特流的校验响应来参与所述第二校验过程,所述比特流不使用所述第一密钥进行加密并且不伴有消息认证码和/或会话密钥标识符。

32.根据描述31所述的逻辑电路系统封装,其中,所述逻辑电路系统封装被配置为:

响应于对所述第一地址的第一以密码方式认证的校验请求,使用所述第一密钥来提供以密码方式认证的响应,

响应于包括时间段的命令,对指向默认第二地址的命令作出响应,

响应于指向默认第二地址的命令,所述命令包括新地址,将所述默认第二地址重新配置为临时第二地址,

响应于对所述经重新配置的临时第二地址的第二校验请求,提供不使用所述第一密钥以密码方式认证的响应,

在所述时间段结束之后,再次对指向所述第一地址的命令作出响应。

33.根据描述32所述的逻辑电路系统封装,其中,在接收到向所述第一地址发送的指示时段的后续命令时,所述逻辑电路系统封装被配置为具有相同的默认第二地址。

34.根据描述32或描述33所述的逻辑电路系统封装,被配置为在包括所述时间段的每个命令之前或之时将所述第二地址重置为相同的默认地址。

35.根据描述34所述的逻辑电路系统封装,其包括分别与所述第一和第二地址相关联的第一和第二逻辑电路,所述封装被配置为:响应于包括所述时间段的所述命令来启用所述第二逻辑电路;以及在设置的启用时设置所述初始第二地址。

36.根据描述32至34中任一项所述的逻辑电路系统封装,其中,所述封装包括:第一操作模式,其中所述封装对向所述第一地址而非所述第二地址发送的通信作出响应;以及第二操作模式,其中所述封装对向所述可重新配置地址而非所述第一地址发送的通信作出响应。

37.根据描述24至36中任一项所述的逻辑电路系统封装,其中,所述封装包括与所述第一地址相关联的第一逻辑电路、以及与所述可重新配置地址相关联的第二逻辑电路。

38.根据描述37所述的逻辑电路系统封装,被配置为使得所述第二逻辑电路由所述第一逻辑电路选择性地启用。

39.根据描述18至32中任一项所述的逻辑电路系统封装,其中,所述第一校验响应包括标识数据,所述封装包括第二逻辑电路,并且所述标识数据与所述第二逻辑电路相关。

40.根据描述18至39中任一项所述的逻辑电路系统封装,其中,所述第一校验响应包括标识数据,并且所述第二校验响应包括相同的标识数据。

41.根据描述18至40中任一项所述的逻辑电路系统封装,其中,所述封装被配置为使得响应于向所述第一地址发送的指示任务和第一时间段的第一命令,所述封装可在所述时间段的持续时间内经由至少一个第二地址访问。

42.根据描述41所述的逻辑电路系统封装,包括用于测量所述时间段的计时器。

43.根据描述42所述的逻辑电路系统封装,包括用于在所述时间段期间指示所述逻辑电路系统的时钟速度的第二计时器。

44.一种打印材料容器校验封装,包括:存储器;触点阵列,其用于与I2C总线连接;至少一个计时器;以及电路系统,用于提供:

第一校验功能,其由在I2C总线上向第一地址发送的消息来触发,

第二校验功能,其由在所述I2C总线上向第二地址发送的消息来触发。

45.一种打印盒,包括根据描述18至43中任一项所述的逻辑电路系统封装并且具有壳体,所述壳体的宽度小于高度,其中,在前表面中,从底部到顶部,分别提供打印液体输出端、空气输入端和凹部,所述凹部在所述顶部处延伸,所述封装包括I2C总线触点,其中,这些I2C总线触点抵靠所述壳体的侧壁内侧、邻近所述壳体的顶部和前部被提供在所述凹部的的一侧处,并且所述I2C总线触点包括数据触点,所述数据触点是这些I2C总线触点中的最低触点。

46.根据描述45所述的打印盒,其中,所述封装的逻辑电路同样被设置为抵靠所述侧壁的内侧。

- 具有集成的功率电子电路系统和逻辑电路系统的模块

- 低电平逻辑转高电平逻辑的高频levelshift电路与电路系统