一种半导体器件及其制作方法、显示面板

文献发布时间:2023-06-19 12:02:28

技术领域

本申请涉及显示技术领域,尤其涉及一种半导体器件及其制作方法、显示面板。

背景技术

从成本、易用性和准确性等方面上来看,指纹识别已经成为用于验证身份的领先方法,以替代常规密码和密钥。传统的指纹识别光学传感器存在成本高,体积大和图像失真等问题。基于硅芯片的传感器因为它们可以做得非常小而且便宜,受到了人们的青睐,然而,它们容易发生静电击穿,可能会受环境条件破坏,这限制了其进一步应用。

相比于硅基PN结传感器,采用非晶硅晶体管(a-Si TFT)的指纹掌纹光传感器,具有高量子效率、高可靠性、低成本等优势。然而由于实际应用中的指纹掌纹的反射光极弱,且指纹间距较小,需要传感器同时具备小占比面积以及高光响应。指纹传感器等弱光传感为应用的传感器器件需要在50lx的光强下,产生10

图1为传统的非晶硅晶体管在不同白光光强下的转移特性曲线,在图1中的曲线从下至上依次为0lx(图1中用dark表示)、47.5lx、115lx、250lx。如图1所示,在负压小于-30V时,0lx、47.5lx、115lx、250lx的转移特性曲线相互接近无法区分,从而降低了传感器的明暗电流比以及可靠性,出现难以满足指纹传感的应用需求。因此,传统的非晶硅晶体管(a-Si TFT)的性能难以满足指纹传感的应用需求,其在高负压下容易出现Poole-Frenkel(普尔)效应,降低了传感器的明暗电流比以及可靠性,难以满足弱光传感快速响应的应用。

发明内容

本申请的目的在于,提供一种半导体器件及其制作方法、显示面板,用以解决现有的非晶硅晶体管的传感器在高负压下容易出现Poole-Frenkel(普尔)效应,降低了传感器的明暗电流比以及可靠性的技术问题。

为了实现上述目的,本申请提供一种半导体器件,包括衬底基板、第一栅极、栅极绝缘层、第一有源构件、第一源极以及第一漏极;所述第一栅极设于所述衬底基板上;所述栅极绝缘层设于所述第一栅极上并覆盖所述第一栅极;所述第一有源构件设于所述栅极绝缘层上并与所述第一栅极对应设置,其中,所述第一有源构件具有沟道区和位于所述沟道区两侧的掺杂区;所述第一源极设于所述第一有源构件上,并电连接至所述第一有源构件的其中一个掺杂区;所述第一漏极设于所述第一有源构件上,并电连接至所述第一有源构件的另一个掺杂区。其中,所述第一有源构件包括第一半导体层以及接触层;所述接触层设于所述第一半导体层上且位于所述掺杂区;所述接触层包括从下至上依次层叠设置的第一掺杂层、第二半导体层及第二掺杂层;具体的,所述第一掺杂层设于所述第一半导体层上;所述第二半导体层设于所述第一掺杂层上;所述第二掺杂层设于所述第二半导体层上。

进一步地,所述第一半导体层为非晶硅层;所述第一掺杂层为N型掺杂的非晶硅层;所述第二半导体层为非晶硅层;所述第二掺杂层为N型掺杂的非晶硅层。

进一步地,所述第一掺杂层的厚度为5-10nm,所述第二半导体层的厚度为10-12nm,所述第二掺杂层的厚度为5-10nm。

基于前文所述的半导体器件,本申请还提供一种半导体器件的制作方法,其包括以下步骤:

制作第一栅极步骤:在衬底基板上沉积一层金属并图案化处理形成第一栅极;

制作栅极绝缘层步骤:在所述第一栅极上制作栅极绝缘层,其中,所述栅极绝缘层覆盖所述第一栅极;

制作第一有源构件步骤:在所述栅极绝缘层上与所述第一栅极对应的位置制作第一有源构件,其中,所述第一有源构件具有沟道区和位于所述沟道区两侧的掺杂区;以及

制作第一源极和第一漏极步骤;在所述第一有源构件上与所述掺杂区对应的位置沉积一层金属并图案化处理形成第一源极和第一漏极,其中,所述第一源极和所述第一漏极分别电连接至所述第一有源构件与两所述掺杂区对应的部分。

进一步地,所述制作第一有源构件步骤具体包括:

制作第一半导体层步骤:在所述栅极绝缘层上采用化学气相沉积方式沉积一层非晶硅并图案化处理形成与所述第一栅极对应设置的第一半导体层;

制作第一掺杂层步骤:在所述第一半导体层的掺杂区上采用化学气相沉积方式制作第一掺杂层;

制作第二半导体层步骤:在所述第一掺杂层上采用化学气相沉积方式制作第二半导体层;以及

制作第二掺杂层步骤:在所述第二半导体层上采用化学气相沉积方式制作第二掺杂层;其中所述第一掺杂层、所述第二半导体层及所述第二掺杂层形成接触层,所述第一半导体层及所述接触层形成所述第一有源构件。

进一步地,所述制作第一掺杂层步骤包括:使用H

基于相同的发明构思,本申请还提供一种显示面板,其包括光传感器以及开关晶体管;其中所述光传感器及所述开关晶体管均采用前文所述的半导体器件,所述光传感器和所述开关晶体管的各个膜层对应同层设置。

基于相同的发明构思,本申请还提供一种显示面板,其包括衬底基板、光传感器、开关晶体管、保护层以及走线层。其中所述光传感器包括衬底基板、第一栅极、栅极绝缘层、第一有源构件、第一源极以及第一漏极;所述第一栅极设于所述衬底基板上;所述栅极绝缘层设于所述第一栅极上并覆盖所述第一栅极;所述第一有源构件设于所述栅极绝缘层上并与所述第一栅极对应设置,其中,所述第一有源构件具有沟道区和位于所述沟道区两侧的掺杂区;所述第一源极设于所述第一有源构件上,并电连接至所述第一有源构件的其中一个掺杂区;所述第一漏极设于所述第一有源构件上,并电连接至所述第一有源构件的另一个掺杂区。其中,所述第一有源构件包括第一半导体层以及接触层;所述接触层设于所述第一半导体层上且位于所述掺杂区;所述接触层包括从下至上依次层叠设置的第一掺杂层、第二半导体层及第二掺杂层;具体的,所述第一掺杂层设于所述第一半导体层上;所述第二半导体层设于所述第一掺杂层上;所述第二掺杂层设于所述第二半导体层上。所述开关晶体管包括第二栅极、第二有源构件、第二源极、第二漏极;所述第二栅极,设于所述衬底基板和所述栅极绝缘层之间;所述第二有源构件设于所述栅极绝缘层上并与所述第二栅极对应设置;所述第二源极设于所述第二有源构件上;所述第二漏极设于所述第二有源构件上。所述保护层设于所述栅极绝缘层上并覆盖所述第一源极、所述第一漏极、所述第二源极和所述第二漏极;所述走线层设于所述保护层上,所述走线层的一部分通过所述保护层的第一过孔与所述第一源极、所述第一漏极中的一者电连接,所述走线层的另一部分通过所述保护层的第二过孔与所述第二源极、所述第二漏极中的一者电连接。

进一步地,所述第一有源构件、所述第二有源构件的材质包括非晶硅、IZO、In

进一步地,所述显示面板还包括遮光层;所述遮光层设于所述开关晶体管上方,所述第二有源构件在所述衬底基板上的投影位于所述遮光层在衬底基板上的投影的覆盖范围内。

进一步地,所述第一半导体层为非晶硅层;所述第一掺杂层为N型掺杂的非晶硅层;所述第二半导体层为非晶硅层;所述第二掺杂层为N型掺杂的非晶硅层。

进一步地,所述第一掺杂层的厚度为5-10nm,所述第二半导体层的厚度为10-12nm,所述第二掺杂层的厚度为5-10nm。

进一步地,所述第二有源构件包括第三半导体层以及第三掺杂层;所述第三半导体层设于所述栅极绝缘层上;所述第三掺杂层设于第三半导体层上。或者,所述第二有源构件与所述第一有源构件的结构相同,包括第一半导体层以及接触层;所述接触层设于所述第一半导体层上且位于所述掺杂区;所述接触层包括从下至上依次层叠设置的第一掺杂层、第二半导体层及第二掺杂层;具体的,所述第一掺杂层设于所述第一半导体层上;所述第二半导体层设于所述第一掺杂层上;所述第二掺杂层设于所述第二半导体层上。

本申请的有益效果在于,提供一种半导体器件及其制作方法、显示面板,通过将第一有源构件设置为第一半导体层及接触层,所述接触层包括从下至上依次层叠设置的第一掺杂层、第二半导体层及第二掺杂层,从而其内部具有至少两个PN结界面,用以增大所述半导体器件的明暗电流比,可以抑制晶体管结构的Poole-Frenkel(普尔)效应,优化半导体器件的明暗电流比和可靠性,提供一种高响应、小占比面积、低成本的指纹/掌纹半导体器件,实现了弱光高响应的目标。

附图说明

下面结合附图,通过对本申请的具体实施方式详细描述,对本申请的技术方案及其它有益效果进行说明。

图1为传统的非晶硅晶体管在不同白光光强下的转移特性曲线。

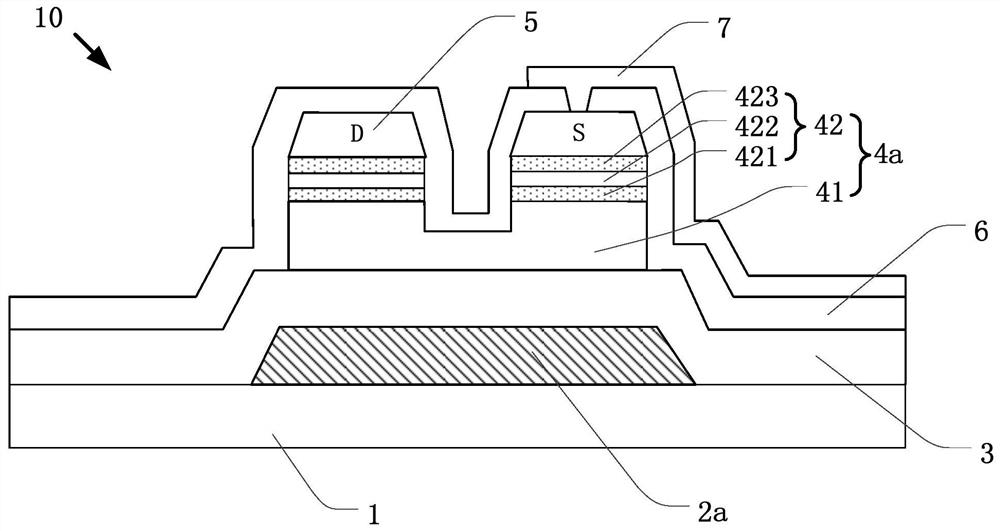

图2为本申请实施例1中的一种显示面板的结构示意图;

图3为本申请实施例中的一种半导体器件的结构示意图。

图4为本申请实施例中所述半导体器件在不同白光光强下的转移特性曲线。

图5为本申请实施例中所述半导体器件在不同白光光强下的光响应电流变化图。

图6为本申请实施例中所述接触层内具有至少两个PN结界面的能带原理分析图。

图7为本申请实施例2中的一种显示面板的结构示意图。

图8为本申请实施例中的一种半导体器件的制作方法的流程图。

图9为本申请实施例中在制作所述第一有源构件时的制作方法的流程图。

图10为本申请实施例中在制作所述接触层时的制作方法的流程图。

图11为本申请实施例中的一种显示面板的制作方法的流程图。

图中部件标识如下:

衬底基板1,第一栅极2a,第二栅极层2b,

栅极绝缘层3,第一有源构件4a,第二有源构件4b,

源漏极层5,保护层6,走线层7,

遮光层8,盖板9,半导体器件10,

光传感器11,开关晶体管12,第一半导体层41,

接触层42,第三半导体层43,第三掺杂层44,

显示面板100,第一掺杂层421,第二半导体层422,

第二掺杂层423。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

实施例1

请参阅图2所示,本申请实施例1中提供一种显示面板100,所述显示面板100包括从下至上依次层叠设置的衬底基板1、驱动电路层、保护层6以及走线层7,其中驱动电路层包括光传感器11和开关晶体管12。所述衬底基板1的材质包括玻璃、Al

如图3所示,本申请提供一种半导体器件10,该半导体器件10可作为光传感器11或开关晶体管12的结构使用。当所述半导体器件10作为光传感器11时,能够实现对弱光的快速响应。

如图2所示,所述光传感器11及所述开关晶体管12均采用前文所述的半导体器件10,所述光传感器11和所述开关晶体管12的各个膜层对应同层设置。亦即所述开关晶体管12与所述半导体器件10并列设置,所述光传感器11和所述开关晶体管12形成阵列式排布的阵列基板结构。这样可便于在不同功能区域制作相同的结构实现不同的功能,可简化制作流程。

具体的,如图3及图2所示,所述半导体器件10包括衬底基板1、第一栅极2a、栅极绝缘层3、第一有源构件4a、源漏极层5;所述源漏极层5包括第一源极S和第一漏极D。所述第一栅极2a设于所述衬底基板1上;所述第一栅极2a包括铟锡氧化物(ITO)、Mo/Cu、Al/Mo、Al、MoTi/Cu、Al/MoTi、Ni/Cu、Al/Ni、Cd/Cu、Al/Cd、Ti/Cu、Al/Ti中的至少一种结构。所述栅极绝缘层3设于所述衬底基板1上并覆盖所述第一栅极2a;所述栅极绝缘层3材料包括氧化铝、氮化硅、二氧化硅、氮化铝、氧化锆中的至少一种。所述第一有源构件4a设于所述栅极绝缘层3上并与所述第一栅极2a对应设置;所述第一有源构件4a具有沟道区和位于所述沟道区两侧的掺杂区;其中,所述第一有源构件4a包括第一半导体层41及接触层42;所述第一半导体层41设于所述栅极绝缘层3上;所述接触层42设于所述第一半导体层41上;所述接触层42包括从下至上依次层叠设置的第一掺杂层421(NP1)、第二半导体层422(AH)以及第二掺杂层423(NP2),从而其内部具有至少两个PN结界面,用以增大所述半导体器件10的明暗电流比。所述源漏极层5设于所述第一有源构件4a上,所述源漏极层5位于所述掺杂区内并电连接至所述第一有源构件4a;所述源漏极层5包括铟锡氧化物(ITO)、Mo/Cu、Mo/Al、Al、MoTi/Cu、MoTi/Al、Ni/Cu、Ni/Al、Cd/Cu、Cd/Al、Ti/Cu、Ti/Al中的至少一种结构。所述第一源极S设于所述第一有源构件4a上,并电连接至所述第一有源构件4a的其中一个掺杂区;所述第一漏极D设于所述第一有源构件4a上,并电连接至所述第一有源构件4a的另一个掺杂区。其中PN结界面即为晶体管PN结的接触面,具有载流子的跃迁势垒。将多个所述PN结界面的载流子的跃迁势垒之和大于现有的一个PN结界面的载流子的跃迁势垒,能够有效降低漏电流,实现增大所述半导体器件10的明暗电流比。可理解的是,明暗电流比即为所述半导体器件10在不同白光光强下的光响应电流变化中的明亮的光强下的光响应电流与暗淡的光强下的光响应电流的比值。

请参阅图4所示,图4为所述半导体器件10在不同白光光强下的转移特性曲线,在图4中的曲线从下至上依次为0lx(图4中用dark表示)、26lx、46.6lx、130lx、250lx、525lx。如图4可见其Poole-Frenkel(普尔)效应较小,光响应较大,且在250lx时的明暗电流比提升到120。

请参阅图5所示,图5为所述半导体器件10在不同白光光强(luminance,单位为lx)下的光响应电流变化图,当固定在栅电压Vgs=-10V,Vd=15V时,所述半导体器件10在50lx时的电流响应达到1.4*10

具体地,本实施例中,所述接触层42内的所述第一掺杂层421设于所述半导体层41上;所述第二半导体层422设于所述第一掺杂层421上;所述第二掺杂层423设于所述第二半导体层422上;其中在所述第一掺杂层421与所述半导体层41之间形成第一PN结界面,在所述第二掺杂层423与所述第二半导体层422之间形成第二PN结界面;所述第一PN结界面的载流子的跃迁势垒小于所述第二PN结界面的载流子的跃迁势垒。

请参阅图6所示,图6为所述接触层42内具有至少两个PN结界面的能带原理分析图,以所述接触层42内设有第一PN结界面和第二PN结界面为例说明,其中在图6中从左至右依次为无掺杂晶体管的能带原理图、参考掺杂晶体管的能带原理图、本实施例的所述半导体器件10的能带原理图。

其中,无掺杂晶体管的结构为在第一半导体层(图6中用AS

其中,参考掺杂晶体管的结构为在第一半导体层(图6中用AS

其中,本实施例的所述半导体器件10的结构为在第一半导体层(图6中用AS

在图6中从左至右依次表示参考掺杂晶体管与无掺杂晶体管相比,增加了PN结界面的数量;本实施例的所述半导体器件10与参考掺杂晶体管相比,增加了PN结界面的载流子的跃迁势垒值。其中无掺杂晶体管只有一个PN结界面,且其载流子的跃迁势垒值为Eb1;参考掺杂晶体管具有两个PN结界面,且其载流子的跃迁势垒值分别为Eb2、Eb2’,参考掺杂晶体管结构与无掺杂晶体管相比存在更多的PN结界面,载流子的跃迁势垒为Eb2+Eb2’>Eb1,能有效降低漏电流;本实施例的所述半导体器件10具有两个PN结界面,且其载流子的跃迁势垒值分别为Eb3、Eb3’,Eb3<Eb2,Eb3’>Eb2’,Eb3+Eb3’>Eb2+Eb2’,通过调整PH

通过对比可知,本实施例的所述半导体器件10通过在所述接触层内具有至少两个PN结界面,用以增大所述半导体器件的明暗电流比,可以抑制晶体管结构的Poole-Frenkel(普尔)效应,优化半导体器件的明暗电流比和可靠性,提供一种高响应、小占比面积、低成本的指纹/掌纹半导体器件,实现了弱光高响应的目标。

本实施例中,所述第一掺杂层421与所述第二半导体层422的厚度比为1:3至1:2,优选为0.35、0.4、0.45;所述第二半导体层422与所述第二掺杂层423的厚度比为3:2至2:1,优选为1.6、1.7、1.8、1.9。所述第一掺杂层421的厚度为5-10nm,优选为6nm、7nm、8nm、9nm;所述第二半导体层422的厚度为10-12nm,优选为11nm;所述第二掺杂层423的厚度为5-10nm,优选为6nm、7nm、8nm、9nm;更优选地,所述第一掺杂层421的厚度为5nm,所述第二半导体层422的厚度为15nm,所述第二掺杂层423的厚度为10nm。

本实施例中,所述半导体层41的材质包括非晶硅;所述第一掺杂层421由化学气相沉积非晶硅形成,并使用H

本实施例中,所述走线层7设于所述保护层6上且与所述源漏极层5电性连接。具体的,所述保护层6设有与所述源漏极层5对应设置的过孔,所述走线层7穿过所述过孔电连接至所述源漏极层5。

本实施例中,所述开关晶体管12的上方设有遮光层8,所述遮光层8用于遮挡光线进入所述开关晶体管12的沟道区,避免光线对所述开关晶体管12沟道区的影响。所述遮光层8的材质包括但不限于金属、金属氧化物、黑色矩阵树脂等有机材料。所述遮光层8可以位于所述显示面板100上,也可设于一彩膜层内,也可设于所述显示面板100上方的盖板9上。具体的,所述盖板9设于所述开关晶体管12上方;所述遮光层8设于所述盖板9的下表面且位于所述开关晶体管12上方。

实施例2

如图7所示,在实施例2中包括实施例1的大部分技术特征,其区别在于,实施例2中仅所述光传感器11采用前文所述的半导体器件10的结构,所述开关晶体管12与所述光传感器11对应设置。这样可使得所述光传感器11与所述开关晶体管12略有差异,不用设置所述遮光层8位于所述开关晶体管12上方来避免光线进入所述开关晶体管12的沟道区。

如图7所示,所述开关晶体管12包括第二栅极2b、第二有源构件4b、所述源漏极层5的第二源极S及第二漏极D;其中,所述第二栅极2b与所述第一栅极2a同层间隔设置,设于所述衬底基板1和所述栅极绝缘层3之间,即所述栅极绝缘层3设于所述第二栅极2b上并覆盖所述第二栅极2b;所述第二有源构件4b设于所述栅极绝缘层上并与所述第二栅极2b对应设置;所述第二有源构件4b具有沟道区和位于所述沟道区两侧的掺杂区;所述第二源极S设于所述第二有源构件4b上,并电连接至所述第二有源构件4b的其中一个掺杂区;所述第二漏极D设于所述第二有源构件4b上,并电连接至所述第二有源构件4b的另一个掺杂区。

同样的,本实施例中,所述显示面板100包括保护层6和走线层7;所述保护层6设于所述栅极绝缘层3上并覆盖所述第一源极S、所述第一漏极D、所述第二源极S和所述第二漏极D;所述走线层7设于所述保护层6上,所述走线层7的一部分通过所述保护层6的第一过孔与所述第一源极S、所述第一漏极D中的一者电连接,所述走线层7的另一部分通过所述保护层6的第二过孔与所述第二源极S、所述第二漏极D中的一者电连接。

所述显示面板100还包括遮光层8;所述遮光层8设于所述开关晶体管12上方,所述第二有源构件4b在所述衬底基板1上的投影位于所述遮光层8在衬底基板1上的投影的覆盖范围内。

本实施例中的所述开关晶体管12的所述第二有源构件4b的材质、结构与所述光传感器11的所述第一有源构件4a的材质、结构不同。所述第一有源构件4a、所述第二有源构件4b的材质包括非晶硅、IZO、In

当所述第二有源构件4b的结构与所述第一有源构件4a的结构相同时,请参考图2。当所述第二有源构件4b的结构与所述第一有源构件4a的结构不同时,如图7所示,所述第二有源构件4b包括第三半导体层43以及第三掺杂层44;所述第三半导体层43设于所述栅极绝缘层3上,与所述第一半导体层41同层设置,优选一起制作形成;所述第三掺杂层44设于所述第三半导体层43上,优选所述第三掺杂层44为所述第三半导体层43的上表面掺杂形成。

请参阅图8所示,基于前文所述的半导体器件10,本申请还提供一种半导体器件10的制作方法,其包括以下步骤S1-S4。

S1、制作第一栅极步骤:在衬底基板1上沉积一层金属并图案化处理形成第一栅极2a。优选在一衬底基板1上形成所述第一栅极2a,所述衬底基板1的材质包括玻璃、Al

S2、制作栅极绝缘层步骤:在所述衬底基板1上沉积一层覆盖所述第一栅极2a的绝缘层并图案化处理形成栅极绝缘层3。所述栅绝缘层3的材料包括氧化铝、氮化硅、二氧化硅、氮化铝、氧化锆中的至少一种。即在所述第一栅极2a上制作栅极绝缘层3覆盖所述第一栅极2a。

S3、制作第一有源构件步骤:在所述栅极绝缘层3上与所述第一栅极2a对应位置制作第一有源构件4a;所述第一有源构件4a具有沟道区和位于所述沟道区两侧的掺杂区;具体的,在所述栅极绝缘层3上采用化学气相沉积方式沉积一层非晶硅形成第一半导体层41,对所述第一半导体层41掺杂形成沟道区和位于所述沟道区两侧的掺杂区,再在所述第一半导体层41上从下至上依次制作第一掺杂层421、第二半导体层422及第二掺杂层423形成接触层42,所述第一半导体层41及所述接触层42形成第一有源构件4a。

其中,请参阅图9所示,在制作所述第一有源构件4a时具体包括步骤:

S31、制作第一半导体层步骤:在所述栅极绝缘层3上采用化学气相沉积方式沉积一层非晶硅形成第一半导体层41,对所述第一半导体层41掺杂形成沟道区和位于所述沟道区两侧的掺杂区;及

S32、制作接触层步骤:在所述第一半导体层41上从下至上依次制作第一掺杂层421、第二半导体层422及第二掺杂层423形成接触层42;所述接触层42内具有至少两个PN结界面,用以增大所述半导体器件10的明暗电流比。

本实施例中,请参阅图10所示,在制作所述接触层42时具体包括步骤:

S321、制作第一掺杂层步骤:使用H

S322、制作第二半导体层步骤;使用H2、SiH4作为反应气体,在所述第一掺杂层421上采用化学气相沉积方式沉积一层非晶硅,形成第二半导体层422(AH);以及

S323、制作第二掺杂层步骤:使用H

其中在所述第一掺杂层421与所述半导体层41之间形成第一PN结界面,在所述第二掺杂层423与所述第二半导体层422之间形成第二PN结界面;所述第一PN结界面的载流子的跃迁势垒小于所述第二PN结界面的载流子的跃迁势垒。本实施例的所述半导体器件10可实现降低漏电流的能带原理分析图见图6所示,具体对比分析内容详见前文,在此不做赘述。

本实施例中,在制作所述接触层42步骤中,所述第一掺杂层421与所述第二半导体层422的厚度比为1:3至1:2;所述第二半导体层422与所述第二掺杂层423的厚度比为3:2至2:1。所述第二半导体层422与所述第二掺杂层423的厚度比为3:2至2:1。所述第一掺杂层421的厚度为5-10nm,所述第二半导体层422的厚度为10-12nm,所述第二掺杂层423的厚度为5-10nm;优选地,所述第一掺杂层421的厚度为5nm,所述第二半导体层422的厚度为15nm,所述第二掺杂层423的厚度为10nm。

S4、制作第一源极和第一漏极步骤:在所述第一有源构件4a上位于所述掺杂区内沉积一层金属并图案化处理形成源漏极层5。所述源漏极层5包括第一源极S和第一漏极D,第一源极S和第一漏极D分别电连接至所述第一有源构件4a与两所述掺杂区对应的部分。所述源漏极层5包括铟锡氧化物(ITO)、Mo/Cu、Mo/Al、Al、MoTi/Cu、MoTi/Al、Ni/Cu、Ni/Al、Cd/Cu、Cd/Al、Ti/Cu、Ti/Al中的至少一种结构。

请参阅图11所示,基于前文所述的显示面板100,本申请还提供一种显示面板100的制作方法,其包括以下步骤S11-S16。

S11、制作栅极层步骤:在一衬底基板1上沉积一层金属并图案化处理形成第一栅极2a和第二栅极2b,所述衬底基板1的材质包括玻璃、Al

S12、制作栅极绝缘层步骤:在所述衬底基板1上沉积一层覆盖所述第一栅极2a的绝缘层并图案化处理形成栅极绝缘层3。所述栅绝缘层3的材料包括氧化铝、氮化硅、二氧化硅、氮化铝、氧化锆中的至少一种。即在所述第一栅极2a上制作栅极绝缘层3覆盖所述第一栅极2a。

S13、制作有源层步骤:在所述栅极绝缘层3上与所述第一栅极2a对应位置制作第一有源构件4a;所述第一有源构件4a具有沟道区和位于所述沟道区两侧的掺杂区;在所述栅极绝缘层3上与所述第二栅极2b对应位置制作第二有源构件4b;所述第一有源构件4a和所述第二有源构件4b形成所述有源层。

S14、制作源漏极层步骤:在所述有源层上位于所述掺杂区内沉积一层金属并图案化处理形成源漏极层5。所述源漏极层5包括第一源极、第二源极和第一漏极、第二漏极,分别电连接至所述掺杂区。所述源漏极层5包括铟锡氧化物(ITO)、Mo/Cu、Mo/Al、Al、MoTi/Cu、MoTi/Al、Ni/Cu、Ni/Al、Cd/Cu、Cd/Al、Ti/Cu、Ti/Al中的至少一种结构。

S15、制作保护层步骤:在所述栅极绝缘层3上沉积一层覆盖所述源漏极层5的透明绝缘层形成保护层6,所述保护层6的材质包括氧化铝、氮化硅、二氧化硅、氮化铝、氧化锆中的至少一种。

S16、制作走线层步骤:在所述保护层6上沉积一层与所述源漏极层5电性连接的金属层并图案化处理形成走线层7。具体的,所述保护层6设有与所述源漏极层5的源电极对应设置的过孔,所述走线层7穿过所述过孔电连接至所述源漏极层5的源电极。所述走线层7包括铟锡氧化物(ITO)、Mo/Cu、Mo/Al、Al、MoTi/Cu、MoTi/Al、Ni/Cu、Ni/Al、Cd/Cu、Cd/Al、Ti/Cu、Ti/Al中的至少一种结构。

请参阅图4所示,图4为所述半导体器件10在不同白光光强下的转移特性曲线,在图4中的曲线从下至上依次为0lx(图4中用dark表示)、26lx、46.6lx、130lx、250lx、525lx。如图4可见其Poole-Frenkel(普尔)效应较小,光响应较大,且在250lx时的明暗电流比提升到120。

请参阅图5所示,图5为所述半导体器件10在不同白光光强下的光响应电流变化图,当固定在栅电压Vg=-10V,Vd=15V时,所述半导体器件10在50lx时的电流响应达到1.4*10

本申请的有益效果在于,提供一种半导体器件及其制作方法、显示面板,通过将第一有源构件设置为第一半导体层及接触层,所述接触层包括从下至上依次层叠设置的第一掺杂层、第二半导体层及第二掺杂层,从而其内部具有至少两个PN结界面,用以增大所述半导体器件的明暗电流比,具体原理为通过将一个能垒值高的PN结界面分解为由多个能垒值低的PN结界面组成,从而每一个能垒值低的PN结界面能实现对弱光的识别精度,并且总的PN结界面可整体增大所述半导体器件的明暗电流比,能够抑制晶体管结构的Poole-Frenkel(普尔)效应,优化半导体器件的明暗电流比和可靠性,提供一种高响应、小占比面积、低成本的指纹/掌纹半导体器件,实现了弱光高响应的目标。

在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

以上对本申请实施例所提供的一种半导体器件及其制作方法、显示面板进行了详细介绍,本文中应用了具体个例对本申请的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本申请的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本申请各实施例的技术方案的范围。

- 一种半导体器件及其制作方法、显示面板

- 一种半导体器件制作方法、半导体结构和半导体器件