制造包括PNP双极晶体管和NPN双极晶体管的器件的方法

文献发布时间:2023-06-19 12:05:39

本申请要求于2020年1月30日提交的第2000903号法国专利申请的优先权权益,在法律允许的最大范围内其全部内容通过引用结合于此。

技术领域

本文档涉及用于制造包括至少两个双极晶体管的微电子器件的方法,该至少两个双极晶体管包括NPN晶体管和竖直PNP晶体管,并且还涉及所述微电子器件。所述微电子器件的应用特别涉及射频领域。

背景技术

对于射频(RF)应用,在BiCMOS或双极技术的微电子器件中集成PNP型双极晶体管带来了困难。

如果微电子器件包括PNP双极晶体管和NPN双极晶体管两者,则优化每个所述晶体管的性能是不可行的。

在所述微电子器件中,PNP双极晶体管和NPN双极晶体管可以如下制造。

提供P掺杂半导体衬底。

进行N掺杂剂(例如,磷)的局部注入,然后进行所述N掺杂剂的扩散退火,以便在半导体衬底中形成旨在反向极化的N阱,使得PNP双极晶体管的集电极可以与衬底电隔离。进行P掺杂剂(例如,硼)的局部注入,然后进行所述P掺杂剂的扩散退火,以在N阱内形成P+掺杂阱。

此外,进行N掺杂剂(例如砷)的局部注入,然后进行所述N掺杂剂的扩散退火,以便在半导体衬底中形成旨在将NPN双极晶体管的集电极与半导体衬底电隔离的N+阱。

在半导体衬底上经由外延形成厚度约为1μm的半导体层。在半导体衬底上生长所述半导体层允许在半导体衬底中掩埋P+阱和N+阱。

进行P掺杂剂的局部注入,然后进行所述P掺杂剂的扩散退火,以在外延半导体层中形成P掺杂区,所述区形成与P+掺杂区电接触的PNP双极晶体管的集电极。

进行N掺杂剂的局部注入,然后进行所述N掺杂剂的扩散退火,以在外延半导体层中形成N掺杂区,所述区形成与N+掺杂区电接触的NPN双极晶体管的集电极。

然后在所述晶体管的相应的集电极上形成每个双极晶体管的基极和发射极。

所述方法的一个缺点是在形成P+阱和N+阱的注入掺杂剂的扩散方面的行为差异。N型掺杂剂是重形态,如砷和锑。另一方面,P型掺杂剂是轻形态,诸如硼。考虑到它们不同的扩散系数,N型掺杂剂在衬底内几乎不扩散,而P型掺杂剂很容易扩散。结果,与NPN双极晶体管的N+阱相比,PNP双极晶体管的P+阱经由扩散进一步向衬底表面延伸。

因此,外延半导体层必须足够厚,约为1μm,以考虑到P+阱的更大扩散,并保持足够的厚度以形成PNP晶体管的集电极。然而,NPN双极晶体管受到外延半导体层的所述厚度的影响。其在晶体管速度方面的性能显著降低。

减小外延半导体层厚度的一种备选方案将是将P+阱更深地掩埋在衬底内。然而,这将需要注入具有高能量的掺杂剂,这可能在衬底中产生晶体缺陷,这将惩罚PNP晶体管的性能。

因此,在用于超高频应用的微电子器件中,本领域需要相互独立地优化PNP双极晶体管和NPN双极晶体管的性能的可行性。

发明内容

在实施例中,提出了一种用于制造包括P型掺杂半导体衬底和竖直布置在所述半导体衬底中的PNP晶体管和NPN晶体管的微电子器件的方法。该方法包括以下连续步骤:在半导体衬底中形成PNP晶体管的N+掺杂隔离阱;在N+掺杂隔离阱中形成P+掺杂区;在半导体衬底上外延生长第一半导体层;形成NPN晶体管的N+掺杂阱,所述N+掺杂阱的至少一部分延伸到第一半导体层中;在第一半导体层上外延生长第二半导体层;在第二半导体层中形成P掺杂区,该P掺杂区被配置为形成PNP晶体管的集电极,以与P+掺杂区电接触;以及在第二半导体层中形成N掺杂区,该N掺杂区被配置为形成NPN晶体管的集电极,以与N+掺杂阱电接触。

“连续”是指步骤以指示的顺序发生,这并不排除中间步骤的执行。

本文的射频(RF)是指20GHz至300GHz范围内的电磁波频率。

借助于外延生长形成的两个半导体层,在PNP晶体管的P+阱的形成与NPN晶体管的N+阱的形成之间形成第一半导体层,在N+阱的形成与所述晶体管的集电极的形成之间形成第二半导体层,可以在不施加高能量注入的情况下在衬底中埋入比N+阱更深的P+阱。

因此,防止了在进行注入的区中形成晶体缺陷。

此外,第二外延层的相对薄的厚度允许NPN晶体管的速度的增加,而不会受到PNP晶体管的P+阱的更大扩散的惩罚。

换句话说,两个外延层允许在NPN晶体管的优化与PNP晶体管的优化之间去链接。

在一些实施例中,第一半导体层具有在0.5μm至0.7μm之间的厚度。

所述第一半导体层可以是轻P掺杂的,也可以是非有意掺杂的。

在一些实施例中,第二半导体层具有在0.3μm至0.5μm之间的厚度。

所述第二半导体层可以是轻N掺杂的,也可以是非有意掺杂的。

在一些实施例中,第一半导体层和第二半导体层的厚度的总和在0.8μm至1.2μm之间。

在实施例中,微电子器件包括:半导体衬底以及竖直布置在所述衬底中的PNP晶体管和NPN晶体管,其中:PNP晶体管的集电极布置在半导体衬底的P+掺杂区上;NPN晶体管的集电极被布置在半导体衬底的N+掺杂阱上;该PNP晶体管的所述P+掺杂区至少部分地延伸到第一半导体层中,并且NPN晶体管的N+掺杂阱至少部分地延伸到被布置在第一半导体层上的第二半导体层中,PNP晶体管的P+掺杂区位于比NPN晶体管的N+掺杂阱更远离器件的表面。

在一些实施例中,第一半导体层具有在0.5μm至0.7μm之间的厚度。

所述第一半导体层可以是轻P掺杂的,也可以是非有意掺杂的。

在一些实施例中,第二半导体层具有在0.3μm至0.5μm之间的厚度。

所述第二半导体层可以是轻N掺杂的,也可以是非有意掺杂的。

在一些实施例中,第一半导体层和第二半导体层的厚度的总和在0.8μm至1.2μm之间。

附图说明

这些实施例的其它特征和优点将在以下参考附图的详细描述中变得显而易见,其中:

图1是局部注入N型掺杂剂时的P型衬底的示意性横截面图;

图2是图1中的衬底在注入的掺杂剂扩散退火以形成将PNP晶体管的集电极与衬底隔离的区之后的示意图;

图3是图2中的衬底在隔离区中局部注入P型掺杂剂时的示意性横截面图;

图4是图3中的衬底在注入的P型掺杂剂扩散退火以形成PNP晶体管的P+阱之后的示意性横截面图;

图5是图4中的衬底在衬底上形成第一外延层之后的示意性横截面图;

图6是图5中的衬底在注入N型掺杂剂时的示意性横截面图;

图7是图6中的衬底在注入的N型掺杂剂扩散退火以形成NPN晶体管的N+阱之后的示意性横截面图;

图8是图7中的衬底在第一外延层上形成第二外延层之后的示意性截面图;

图9是图8中的衬底在第二外延层中注入P型掺杂剂时的示意性横截面图;

图10是图9中的衬底在注入的P型掺杂剂扩散退火以形成PNP晶体管的集电极之后的示意性横截面图;以及

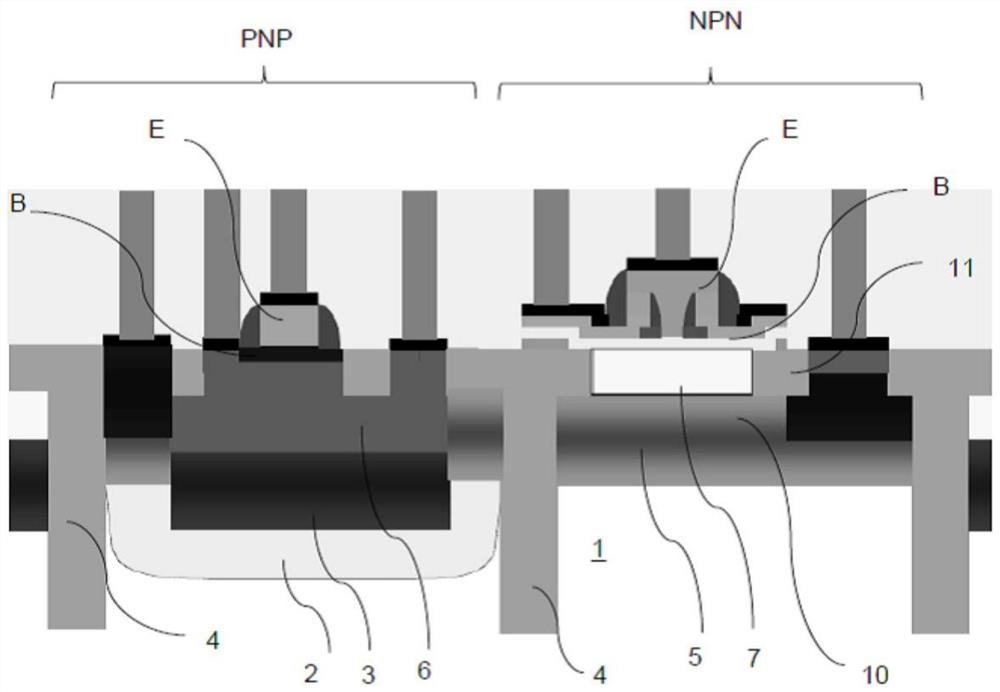

图11是利用上述方法获得的包括PNP晶体管和NPN晶体管的器件的示意性截面图。

为了便于附图辨认,这些附图没有按比例绘制。此外,附图已经被简化,以便仅示出对理解附图有用的那些元件。

具体实施方式

图1至图10示意性地示出了用于制造微电子器件的方法的连续步骤,该微电子器件包括P型掺杂半导体衬底和被竖直布置在所述半导体衬底中的PNP晶体管和NPN晶体管。

参照图1,半导体衬底1是P型掺杂半导体衬底。半导体衬底的材料例如可以是硅。

掩模M形成在衬底1的主表面上。掩模M包括至少一个开口,该开口允许暴露半导体衬底1的、与PNP晶体管位置对应的表面的确定部分。掩模M可以通过在制造微电子器件的方法中常规使用的光刻技术形成。

在掩模的开口注入掺杂剂(由箭头表示)(选择掩模M的材料和厚度以防止掺杂剂穿过掩模)。掺杂剂为N型(如磷)。

因此,包含注入的掺杂剂的区2a从由掩模M的开口暴露的那表面部分延伸到衬底1的一部分厚度中。

参照图2,对如此注入的半导体衬底施加热处理,并移除掩模M。

在允许掺杂剂在区2a中扩散和激活以形成N+掺杂阱2的条件下,进行所述热处理。如下所示,所述N+掺杂阱2旨在形成PNP晶体管的隔离阱。

参照图3,在半导体衬底1的主表面上形成新的掩模M。掩模M包括至少一个开口,该开口允许暴露半导体衬底1的、与阱2相对的表面的确定部分。所述开口的尺寸小于阱2。

在掩模的开口中注入掺杂剂(由箭头表示)(选择掩模M的材料和厚度以防止掺杂剂穿过掩模)。掺杂剂为P型(如硼)。

因此,包含注入的掺杂剂的区3a从由掩模M的开口暴露的表面部分延伸到阱2的一部分厚度中。

参照图4,对如此注入的半导体衬底施加热处理,并移除掩模M。

在允许掺杂剂在区3a中扩散和激活的条件下施加所述热处理,以在阱2中形成P+掺杂区3。

参照图5,在衬底1的主表面上进行第一半导体层10的外延生长。优选地,外延层的材料与衬底1的材料相同(同质外延)。可选地,外延层的材料可以不同于衬底1的材料(异质外延),但具有尽可能接近衬底1的晶格参数,以最小化外延层中晶体缺陷的形成。

第一外延层10可以是轻P掺杂的,或者是非有意掺杂的。

所述第一外延层10的一个功能是有助于在结构内掩埋P+掺杂区3。

第一外延层10的厚度可以在0.5μm和0.7μm之间。

在外延步骤的温度的影响下,N+掺杂区3的掺杂剂可以任选地扩散到第一外延层10的一部分中。

参照图6,在第一外延层10的主表面上形成新的掩模M。掩模M包括开口,该开口允许暴露第一外延层10的在阱2的任一侧(图中在左侧)和NPN晶体管的位置(图中在右侧)的确定部分。

在掩模的开口中执行掺杂剂的注入(由箭头表示)(选择掩模M的材料和厚度以防止掺杂剂穿过掩模)。掺杂剂为N型(如砷)。

因此,包含注入的掺杂剂的区4a和5a分别从掩模M的开口所暴露的表面部分延伸到第一外延层10的一部分厚度中,在专用于形成PNP晶体管的部分中(阱2的任一侧)和专用于形成NPN晶体管的部分中。

参照图7,对如此注入的半导体衬底施加热处理,并移除掩模M。

在允许掺杂剂在区4a和5a中扩散和激活的条件下,施加所述热处理,以在第一外延层10和半导体衬底1的一部分中形成N+掺杂区4和5。

区4旨在确保阱2与器件表面之间的电连续性,从而允许PNP晶体管的阱2的电极化。

区5旨在形成NPN晶体管的阱。

参照图8,在第一半导体层10的主表面上进行第二半导体层11的外延生长。优选地,第二外延层的材料与第一外延层的材料相同(同质外延)。任选地,第二外延层的材料可以不同于第一外延层的材料(异质外延),但具有尽可能接近第一外延层的晶格参数,以最小化第二外延层中晶体缺陷的形成。

在外延步骤的温度的影响下,N+掺杂阱5的掺杂剂可能扩散到第二外延层11的一部分中。

第二外延层11可以是轻N掺杂的,或者是非有意掺杂的。

第二外延层11的厚度可以在0.3μm至0.5μm之间。

所述第二外延层11的一个功能是在结构内掩埋NPN晶体管的N+掺杂阱5,并且与先前形成的第一外延层10一起有助于掩埋PNP晶体管的P+掺杂区3。

因此,在图8中可以看出,PNP晶体管的阱2和区3比NPN晶体管的阱5更深地埋在结构中,阱2和区3通过厚度在0.8μm至1.2μm之间的层10和层11的堆叠而与图8中的结构的表面分离,而阱5仅通过厚度在0.3μm至0.5μm之间的层11与所述表面分离。

因此,在该方法的不同步骤中形成两个外延层,这针对PNP晶体管的P+掺杂区3和NPN晶体管的N+掺杂阱5提供了注入深度的选择性,同时以中等能量施加掺杂剂注入允许与注入相关的晶体缺陷的最小化。

外延层10和外延层11的厚度可以根据在器件的整个制造过程中该结构所经受的热平衡来调节,以优化PNP晶体管和NPN晶体管的性能。第一外延层10的厚度可以由NPN晶体管的耐压(需要层10的足够大的厚度)与PNP晶体管的速度(需要层10的足够小的厚度)之间的折衷而产生。第二外延层11的厚度可以根据两个晶体管的期望耐压来选择。

参照图9,在第二外延层11的主表面上形成新的掩模M。掩模M包括至少一个开口,该开口允许暴露第二外延层的、与PNP晶体管的区3相对的表面的确定部分。

在掩模的开口中进行掺杂剂的注入(由箭头表示)(选择掩模M的材料和厚度以防止掺杂剂穿过掩模)。掺杂剂为P型(如硼)。

因此,包含注入的掺杂剂的区6a从由掩模M的开口所暴露的部分表面延伸到第二外延层11中,并且可能延伸到第一外延层10的一部分中。

参照图10,对这样注入的结构施加热处理,并移除掩模M。

在允许掺杂剂在区6a中扩散和激活的条件下施加所述热处理,以形成延伸到P+掺杂区3的P掺杂区6,以确保与区3的电连续性。区6用于形成PNP晶体管的集电极。

类似地(未示出),在第二外延层的主表面上形成新的掩模。掩模包括至少一个开口,该开口允许暴露第二外延层的、与NPN晶体管的阱5相对的表面的确定部分。

在掩模的开口中进行掺杂剂的注入(选择掩模M的材料和厚度以防止掺杂剂穿过掩模)。掺杂剂为N型(如砷)。

因此,包含注入的掺杂剂的区从由掩模M的开口所暴露的表面部分延伸到第二外延层中并且可能延伸到阱5中。

然后对这样注入的结构施加热处理,并移除掩模。

在允许掺杂剂在掺杂区中扩散和激活的条件下施加所述热处理,以形成延伸到N+掺杂阱5的N掺杂的区(参考图11中的7),以确保与阱5的电连续性。区7用于形成NPN晶体管的集电极。

图11是在形成PNP晶体管(左侧)和NPN晶体管(右侧)的发射极E和基极B之后器件的横截面图。这些部件的成形是用本身已知的方法获得的,因此本文不作描述。

如上所述,PNP晶体管的P+掺杂区3位于比NPN晶体管的N+掺杂阱5更远离器件表面。

这些区/阱的深度布置的这种差异,允许考虑在制造器件时施加的不同热处理期间PNP晶体管的P掺杂剂的更大扩散,而不牺牲NPN晶体管的快速性或不需要可能产生晶体缺陷的高能量注入。因此,它允许在微电子器件的同一半导体衬底中集成这两种类型的晶体管,而不会降低这些晶体管中任一个的性能。

- 制造包括PNP双极晶体管和NPN双极晶体管的器件的方法

- 具有npn和pnp双极晶体管的集成电路装置及相应的制造方法