半导体模块及其制造方法

文献发布时间:2023-06-19 12:14:58

技术领域

本发明涉及半导体模块及其制造方法。

背景技术

以往,作为存储装置已知有DRAM(Dynamic Random Access Memory,动态随机存取存储器)等易失性存储器(RAM)。对于DRAM要求大容量化,以能够承受运算装置(以下称为逻辑芯片)的高性能化和数据量的增大。因此,通过存储器(存储单元阵列、存储芯片)的微细化以及平面地增设单元来实现大容量化。另一方面,因为微细化导致的对噪声的脆弱性、大面积的增加等,这种大容量化已达到了极限。

因此,最近正在开发通过层叠多个平面的存储器进行三维化(3D化)来实现大容量化的技术。作为采用这样的技术的装置,提出了使用在硅基板的厚度方向上贯通的电极将所层叠的芯片电连接的方法(例如参照专利文献1)。

现有技术文献

专利文献

专利文献1:日本特开2016-46447号公报。

发明内容

发明要解决的问题

在专利文献1所记载的方法中公开了将使电极部朝向上方的多个晶圆进行位置对齐后进行层叠。此外,在专利文献1的方法中公开了以将配置在电极部的电极沿着层叠方向配置成锥状的方式层叠晶圆。接着,在专利文献1的方法中公开了形成从最上层的电极部贯通到最下层的电极部的贯通孔。

然而,在专利文献1的方法中,在形成贯通孔时,将最上层和中间层的电极用作硬掩模。因此,越是上层的电极,被蚀刻的时间越长。因此,越是上层的电极,越蓄积损伤。例如,越是上层的电极,厚度因损伤而变得越薄。特别是当晶圆的层叠片数变多时,由于损伤的蓄积可能导致电极消失。

本发明的目的在于提供一种能够抑制对电极造成的损伤的半导体模块及其制造方法。

用于解决问题的方案

本发明涉及一种层叠多个电路模块来制造半导体模块的制造方法,包括:制造具有基板和与所述基板的一个面相邻的布线层的多个电路模块的步骤,该步骤包括针对多个所述电路模块分别形成电极层的步骤;从最下层向最上层层叠多个所述电路模块的步骤,以从最下层向最上层以交替地配置所述布线层和所述基板的方式层叠电路模块;形成从最上层向最下层在所述电路模块的层叠方向上延伸且所述电路模块各自的所述电极层露出的通路孔的步骤,该步骤包括形成从最上层向最下层在所述电路模块的层叠方向延伸的通路孔的引导孔的步骤、和通过扩大所述引导孔来使所述最下层的所述电路模块的所述电极层及不是所述最下层的所述电路模块的所述电极层露出的步骤;以及通过在所述通路孔配置导体来形成将所层叠的多个所述电路模块贯通的导通孔从而将各个所述电极层电连接的步骤。此外,制造所述电路模块的步骤可以包括:针对多个所述电路模块分别在距布线层的面中的相反面的距离不同的位置形成电极层的步骤,所述相反面为与基板相向的相向面的相反面;以及从最下层向最上层按照所述电极层的距离从小到大的顺序层叠所述电路模块的步骤。

此外,制造所述电路模块的步骤可以包括:针对多个所述电路模块分别在距布线层的面中的相向面的距离不同的位置形成电极层的步骤,所述相向面为与基板相向的面;以及从最下层向最上层按照所述电极层的距离从小到大的顺序层叠所述电路模块的步骤。

此外,在形成所述通路孔的步骤中,优选形成从最上层向最下层缩径的所述通路孔。

此外,在形成所述电极层的步骤中,优选在与要层叠的所述电路模块的层叠方向交叉的方向的位置中的与所述通路孔的缩径率相匹配的位置形成所述电极层。

此外,本发明涉及一种半导体模块,其具有:层叠的多个电路模块、和在层叠方向延伸且将多个所述电路模块电连接的导通孔,所述电路模块具有:基板;布线层,将其一个面作为相向面与所述基板相向地配置;电极层,其配置在所述布线层的内部,所述电路模块以从最下层向最上层交替地配置所述布线层和所述基板的方式层叠,所述导通孔从最上层向最下层缩径,关于形成用于形成所述导通孔的通路孔时在层叠方向被去除的所述电极层的去除厚度,相对于配置在最下层侧的所述电极层的去除厚度,除此之外的所述电极层的去除厚度为2倍到5倍。

此外,本发明涉及一种半导体模块,其具有:层叠的多个电路模块、和在层叠方向延伸且将多个所述电路模块电连接的导通孔,所述电路模块具有:基板;布线层,将其一个面作为相向面与所述基板相向地配置;电极层,其配置在所述布线层的内部,所述电路模块以从最下层向最上层交替地配置布线层和基板的方式层叠,并且从最下层向最上层按照从布线层的面中的相反面到电极层的距离从小到大的顺序层叠,所述相反面为与基板相向的相向面的相反面,所述导通孔从最上层向最下层缩径。

此外,本发明涉及一种半导体模块,其具有:层叠的多个电路模块、和在层叠方向延伸且将多个所述电路模块电连接的导通孔,所述电路模块具有:基板;布线层,将其一个面作为相向面与所述基板相向配置;电极层,其配置在所述布线层的内部,所述电路模块以从最下层向最上层交替地配置布线层和基板的方式层叠,并且从最下层向最上层按照从布线层的面中的相向面到电极层的距离从小到大的顺序层叠,所述相向面为与基板相向的面,所述导通孔从最上层向最下层缩径。

此外,所述电极层优选配置在与要层叠的所述电路模块的层叠方向交叉的方向的位置中的与所述通路孔的缩径率相匹配的位置。

此外,所述电极层优选形成为俯视时呈环状或凸片状。

发明效果

根据本发明,可提供一种能够抑制对电极造成的损伤的半导体模块及其制造方法。

附图说明

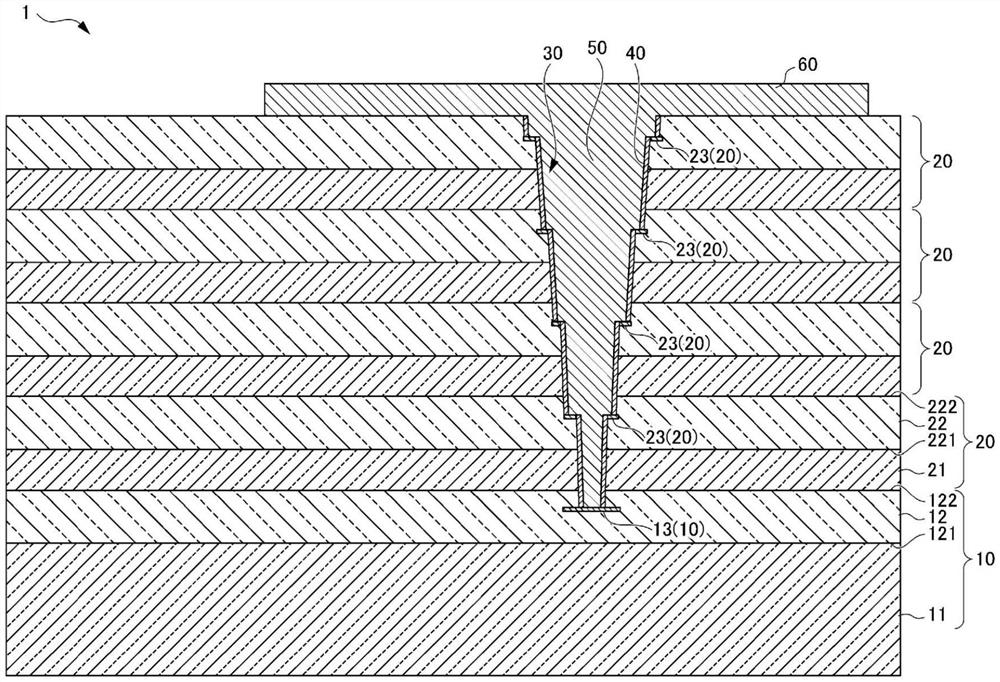

图1表示本发明的第一实施方式涉及的半导体模块的概要剖视图。

图2表示将第一实施方式涉及的半导体模块的多个电路模块进行层叠后的半导体模块的概要剖视图。

图3表示在第一实施方式涉及的半导体模块中形成了通路孔的一部分的半导体模块的概要剖视图。

图4表示在第一实施方式涉及的半导体模块中形成了通路孔的一部分的半导体模块的概要剖视图。

图5表示在第一实施方式涉及的半导体模块中形成了通路孔的一部分的半导体模块的概要剖视图。

图6表示在第一实施方式涉及的半导体模块中形成了通路孔的一部分的半导体模块的概要剖视图。

图7表示在第一实施方式涉及的半导体模块中形成了通路孔的半导体模块的概要剖视图。

图8表示在第一实施方式涉及的半导体模块的通路孔形成了氧化膜层的半导体模块的概要剖视图。

图9表示在第一实施方式涉及的半导体模块形成了导通孔的半导体模块的概要剖视图。

图10表示本发明的第二实施方式涉及的半导体模块的概要剖视图。

图11表示将第二实施方式涉及的半导体模块的多个电路模块进行层叠后的半导体模块的概要剖视图。

图12为表示在本发明的第三实施方式涉及的半导体模块的最下层的电路模块形成的电极层的俯视图。

图13为表示在第三实施方式涉及的半导体模块的最下层以外的一个电路模块形成的电极层的俯视图。

图14为表示在第三实施方式涉及的半导体模块的最下层以外的一个电路模块形成的电极层的其他例子的俯视图。

图15为表示在第三实施方式涉及的半导体模块的最下层以外的一个电路模块形成的电极层的其他例子的俯视图。

具体实施方式

以下,参照图1~图15对本发明的各实施方式涉及的半导体模块1及其制造方法进行说明。

在说明各实施方式的半导体模块1及其制造方法之前,对各实施方式的半导体模块1的概要进行说明。

各实施方式涉及的半导体模块1例如为存储器模块,其是将多个电路模块20(RAM)层叠在接口模块10(例如Active Interposer(AIP),有源中介层)上而构成的。接口模块10也是电路模块20的一个例子。不使用接口模块10的结构也是存储器模块的一个例子。此外,在各实施方式涉及的半导体模块1中,多个电路模块20通过一个贯通电极(导通孔(via)50)电连接。

各实施方式涉及的半导体模块1,优选考虑用于形成导通孔50的蚀刻造成的所层叠的电路模块20的蚀刻量,使通过蚀刻而露出的电极层23的形成位置变化。例如,对于从所层叠的电路模块20的表面起在厚度方向上缩径的通路孔30,考虑通过间歇地蚀刻所层叠的电路模块20来形成的情况。在该情况下,与深度方向顶端侧相比,表面侧的通路孔30的直径变大,电路模块20的被蚀刻的面积变大。因此,即使是进行了同样时间的蚀刻的情况下,所层叠的电路模块20的表面侧的被蚀刻的量比所层叠的电路模块20的深度方向顶端侧的被蚀刻的量更多。根据该情况,在各实施方式中,可以调整通过蚀刻而露出的电极层23的形成位置。另外,在以下的实施方式中,以半导体模块1的表面侧为上层侧,以深度方向顶端侧为下层侧进行说明。

[第一实施方式]

以下,参照图1~图10对本发明的第一实施方式涉及的半导体模块1及其制造方法进行说明。

如图1所示,半导体模块1具有接口模块10、多个电路模块20、通路孔30、氧化膜40、导通孔50以及电极端子60。半导体模块1例如为DRAM(Dynamic Random Access Memory,动态随机存取存储器)。

接口模块10为板状体,配置在半导体模块1的最下层。接口模块10具有接口基板11、接口布线层12以及接口电极层13。另外,接口模块10可以是后述的电路模块20的一个例子。因此,在以下的说明中,接口基板11有时也被记载为基板21。此外,接口布线层12有时也被记载为布线层22。此外,接口电极层13有时也被记载为电极层23。

接口基板11例如为Si基板。

接口布线层12在与层叠方向交叉的面中的一个相向面121,与接口基板11相向地配置。接口布线层12具有例如利用绝缘层(例如SiO

接口电极层13例如为Al层。接口电极层13配置在接口布线层12的内部。在本实施方式中,接口电极层13配置在如下位置:在接口布线层12的厚度方向上,从接口布线层12的面中的与相向面121相反的相反面122起离开了规定的距离的位置。此外,接口电极层13配置在与层叠方向交叉的方向上在后述的通路孔30的底部露出的位置。

多个电路模块20层叠在接口模块10。具体而言,多个电路模块20与接口模块10的接口布线层12的相反面122相邻地配置。多个电路模块20分别具有基板21、布线层22以及电极层23。

基板21例如为Si基板。基板21是例如通过研磨一个面而构成的。在本实施方式中,基板21的一个面与相邻的接口模块10的接口布线层12或电路模块20的布线层22相邻地配置。

布线层22配置在基板21的另一面侧。具体而言,布线层22将其一个面作为相向面221而与基板21相向地配置。布线层22构成为被绝缘层(未图示)覆盖电子线路(未图示)。

电极层23配置在布线层22的内部。电极层23例如为Al层。在本实施方式中,电极层23可以在每个电路模块20中形成在距布线层22的面中的相反面222的距离不同的位置(例如图2的t1到t5),所述相反面222为与基板21相向的相向面221的相反面。此外,在本实施方式中,电极层23配置成使与基板21(或相向面221)之间的布线层22的距离,成为与其他的电路模块20(以及接口模块10)中的电极层23和基板21之间的距离相同的距离(例如图2的t0)。此外,电极层23配置在与层叠方向交叉的方向上在后述的通路孔30的位置处露出的位置。

根据以上的接口模块10和电路模块20,如图2所示,从最下层向最上层,将基板21(接口基板11)作为下层侧,将布线层22(接口布线层12)作为上层侧,依次层叠。由此,接口模块10和电路模块20以从最下层向最上层交替地配置基板21和布线层22的方式被层叠。并且,最上层的电路模块20的布线层22的相反面以露出的状态配置。

在本实施方式中,四个电路模块20配置在接口模块10之上。而且,接口模块10和四个电路模块20优选从最下层向最上层,按照距布线层22(12)的面中的相反面222(122)的距离从小到大的顺序依次被层叠,所述相反面222(122)为与基板21(11)相向的相向面221(121)的相反面。例如,接口模块10和四个电路模块20可以按照图2所示的t1到t5为t1>t2>t3>t4>t5的顺序被层叠。

此外,电极层23配置在与所层叠的电路模块20的层叠方向交叉的方向上与后述的导通孔50的缩径率相匹配的位置。即,电极层23沿着沿后述的导通孔50的形成面的位置来配置。

通路孔30从多个电路模块20的最上层起配置至接口模块10。具体而言,通路孔30从多个电路模块20的最上层起配置至接口模块10的接口布线层12。通路孔30形成为从最上层向最下层缩径的锥状。此外,通路孔30在顶端处露出接口模块10的接口电极层13。而且,通路孔30形成为将电路模块20的电极层23的上表面露出的台阶状。

氧化膜40例如为SiO

导通孔50配置在通路孔30的位置。具体而言,导通孔50配置在填充通路孔30的位置。导通孔50例如为金属。导通孔50通过配置在通路孔30的位置,从而与氧化膜40相邻地配置。导通孔50将多个电路模块20电连接。更详细而言,导通孔50将多个电路模块20各自的电极层23电连接。此外,导通孔50将接口模块10的接口电极层13与多个电路模块20的电极层23电连接。在本实施方式中,导通孔50在与电路模块20的被层叠的方向相反的方向上缩径。换言之,导通孔50形成为从最上层向最下层缩径的锥状。

根据以上的通路孔30和导通孔50,在本实施方式中,在形成用于形成导通孔50的通路孔30时,接口电极层13和电极层23在层叠方向被去除。可以认为,相对于配置在最下层侧的接口电极层13在层叠方向的去除厚度,除此之外的电极层23在层叠方向的去除厚度为例如2倍到5倍。

电极端子60配置在电路模块20的布线层22之上。更详细而言,电极端子60配置在最上层的电路模块20的布线层22的相反面之上。电极端子60例如由与导通孔50相同的金属形成。电极端子60是为了经由导通孔50将各个电极层23(接口电极层13)与外部进行电连接而配置的。

接下来,参照图1至图10,对本实施方式的半导体模块1的制造方法进行说明。

半导体模块1的制造方法包括:制造电路模块20的步骤、层叠电路模块20的步骤、形成通路孔30的步骤、将电极层23(接口电极层13)电连接的步骤以及形成电极端子60的步骤。

首先,实施制造电路模块20的步骤。制造电路模块20的步骤包括准备基板21和布线层22的步骤和形成电极层23的步骤。

在准备基板21和布线层22的步骤中,准备具有基板21和与基板21的一个面相邻的布线层22的电路模块20。接下来,在形成电极层23的步骤中,针对多个电路模块20分别形成电极层23。此时,可以在距布线层22的面中的相反面222的距离不同的位置形成电极层23,所述相反面222为与基板21相向的相向面221的相反面。在形成电极层23的步骤中,在与要层叠的电路模块20的层叠方向交叉的方向的位置中的与通路孔30的缩径率相匹配的位置形成电极层23。

接下来,实施层叠电路模块20的步骤。在层叠电路模块20的步骤中,如图2所示,在接口模块10的接口布线层12的相反面上层叠多个电路模块20。电路模块20可以以从最下层向最上层交替地配置布线层22和基板21的方式层叠,并且从最下层向最上层按照电极层23的距离从小到大的顺序层叠。然后,在最上层的电路模块20的布线层22的相反面上,配置具有与蚀刻电路模块20的基板21的时间大致相同的时间内被蚀刻的厚度的硬掩模70。

接下来,实施形成通路孔30的步骤。在形成通路孔30的步骤中,形成从最上层向最下层在电路模块20的层叠方向上延伸且电路模块20的各自的电极层23(接口电极层13)露出的通路孔30。形成通路孔30的步骤包括形成通路孔30的引导孔的步骤和露出电极层23(接口电极层13)的步骤。

在形成通路孔30的引导孔的步骤中,形成从最上层向最下层在电路模块20的层叠方向上延伸的通路孔30的引导孔。例如,在形成通路孔30的引导孔的步骤中,形成即将使配置在最靠最下层的电极层23(接口电极层13)露出的通路孔30的引导孔。在本实施方式中,形成具有以下深度的通孔30的引导孔,即,其深度为直到紧邻接口模块10的上方的电路模块20(第四层的电路模块20)的相向面221为止。

首先,如图3所示,在电路模块20的最上层形成通路孔30的引导孔。具体而言,在硬掩模70的露出面中的通路孔30的引导孔的形成位置以外配置光致抗蚀剂80。然后,形成直到最上层的布线层22的相向面221的位置为止的通路孔30的引导孔。此时,以不露出最上层的电路模块20的电极层23的直径来形成通路孔30的引导孔。

接下来,如图4所示,形成直到最上层的下一层(第二层)为止的通路孔30的引导孔。具体而言,配置将已经形成的通路孔30的引导孔的形成位置的直径扩大了的光致抗蚀剂80。然后,形成直到第二层的布线层22的相向面221的位置为止的通路孔30的引导孔。此时,以不露出最上层和第二层的电路模块20的电极层23的直径来形成通路孔30的引导孔。

接下来,如图5所示,形成直到第二层的下一层(第三层)为止的通路孔30的引导孔。具体而言,配置将通路孔30的引导孔的形成位置的直径扩大了的光致抗蚀剂80。然后,形成直到第三层的布线层22的相向面221的位置为止的通路孔30的引导孔。此时,以不露出最上层到第三层的电路模块20的电极层23的直径来形成通路孔30的引导孔。

接下来,如图6所示,形成直到第三层的下一层(第四层)为止的通路孔30的引导孔。具体而言,配置将通路孔30的引导孔的形成位置的直径扩大了的光致抗蚀剂80。然后,形成直到第四层的布线层22的相向面的位置为止的通路孔30的引导孔。此时,以可以露出与最上层到第四层的电路模块20的层叠方向交叉的方向的电极层23的端面、但不露出层叠方向的一面的直径,来形成通路孔30的引导孔。由此,在本实施方式中,形成将紧邻接口模块10的上方的电路模块20的基板21作为底部的通路孔30的引导孔。此外,在本实施方式中,以在层叠方向上不露出电极层23(接口电极层13)程度的直径,来形成从最上层向最下层缩径的通路孔30的引导孔。

接下来,实施露出电极层23(接口电极层13)的步骤。在露出电极层23(接口电极层13)的步骤中,通过扩大通路孔30的引导孔,最下层的电路模块20的电极层23(接口电极层13)以及不是最下层的电路模块20的电极层23被露出。例如,如图7所示,通路孔30的引导孔在层叠方向上被扩大,直到接口模块10的接口电极层13露出为止。此外,将通路孔30的引导孔扩大到使沿通路孔30的引导孔配置的各电路模块20的电极层23露出的直径。具体而言,首先,在通路孔30的形成位置配置扩大了直径的光致抗蚀剂80。然后,形成直到接口模块10的接口电极层13的位置为止的通路孔30。通过该步骤,以最上层到第四层的电路模块20的电极层23的层叠方向的一面、和接口模块10的接口电极层13的层叠方向的一面露出的直径,来形成通路孔30。由此,以使所层叠的电路模块20各自的电极层23以及接口模块10的接口电极层13露出的方式,形成从最上层向最下层缩径的通路孔30。

接下来,实施将电极层23(接口电极层13)电连接的步骤。即,实施通过形成将所层叠的多个电路模块20贯通的导通孔50来将各个电极层23(接口电极层13)电连接的步骤。将电极层23(接口电极层13)电连接的步骤包括形成氧化膜40的步骤和形成导通孔50的步骤。

首先,实施形成氧化膜40的步骤。在形成氧化膜40的步骤中,如图8所示那样形成氧化膜40。具体而言,除去光致抗蚀剂80和硬掩模70。然后,在所形成的通路孔30的位置形成氧化膜40。之后,通过各向异性蚀刻,除去接口模块10的接口电极层13和电路模块20各自的电极层23在层叠方向上重叠的位置的氧化膜40。由此,接口模块10的接口电极层13和电路模块20各自的电极层23露出。

接下来,实施形成导通孔50步骤。在形成导通孔50步骤中,形成通过在通路孔30配置导体来将各个电极层23(接口电极层13)连接的导通孔50。在形成导通孔50的步骤中,例如图9所示,在通路孔30的形成位置形成导通孔50。导通孔50例如通过电镀处理来形成。将接口模块10的接口电极层13和电路模块20各自的电极层23电连接。

接下来,实施形成电极端子60的步骤。在形成电极端子60的步骤中,如图1所示那样形成电极端子60。电极端子60例如沿着最上层的布线层22的相反面222形成为板状。

根据如以上这样的第一实施方式的半导体模块1,能够获得以下的效果。

(1)一种半导体模块1的制造方法,层叠多个电路模块20来制造半导体模块1,所述半导体模块1的制造方法包括:制造具有基板21和与基板21的一个面相邻的布线层22的多个电路模块20的步骤,该步骤包括针对多个电路模块分别形成电极层23的步骤;从最下层向最上层层叠多个电路模块20的步骤,以从最下层向最上层交替地配置布线层22和基板21的方式层叠电路模块20;形成从最上层向最下层在电路模块20的层叠方向上延伸且电路模块20各自的电极层23露出的通路孔30的步骤,该步骤包括形成从最上层向最下层在电路模块20的层叠方向上延伸的通路孔30的引导孔的步骤、和通过扩大引导孔来使最下层的电路模块20的电极层23和不是最下层的电路模块20的电极层23露出的步骤;以及通过在通路孔30配置导体来形成将所层叠的多个电路模块20贯通的导通孔50从而将各个电极层23电连接的步骤。由此,在朝向下层侧形成了通路孔30的引导孔之后,通过扩大引导孔,露出电极层23。虽然与下层侧相比,先在上层侧的电路模块20形成引导孔,但上层侧的电极层23和下层侧的电极层23都是通过扩大引导孔而被露出。因此,能够抑制上层侧的电路模块20的电极层23被蚀刻。此外,制造多个电路模块20的步骤可以包括:针对多个电路模块20,分别在距布线层22的面中的相反面的距离不同的位置形成电极层23的步骤,所述相反面为与基板21相向的相向面的相反面;以及从最下层向最上层按照电极层23的距离从小到大的顺序层叠电路模块20的步骤。由此,能够进一步抑制上层侧的电路模块20的电极层23被蚀刻。因此,能够提高半导体模块1的品质,提高成品率。

(2)在形成通路孔30的步骤中,形成从最上层向最下层缩径的通路孔30。由此,与沿着层叠方向形成相同直径的通路孔30的情况相比,能够更容易地形成通路孔30。

(3)在形成电极层23的步骤中,在与要层叠的电路模块20的层叠方向交叉的方向的位置中,在与通路孔30的缩径率相匹配的位置形成电极层23。由此,能够使电路模块20各自的电极层23的上层侧的面露出,因此能够增加电极层23与导通孔50的接触面积。

(4)一种半导体模块1,其具有:层叠的多个电路模块20、和在层叠方向上延伸且将多个电路模块20电连接的导通孔50,电路模块20具有:基板21;布线层22,将其一个面作为相向面221与基板21相向地配置;电极层23,其配置在布线层22的内部,电路模块20以从最下层向最上层交替地配置布线层22和基板21的方式层叠,导通孔50从最上层向最下层缩径,关于形成用于形成导通孔50的通路孔30时在层叠方向被去除的所述电极层的去除厚度,相对于配置在最下层侧的电极层23(接口电极层13)的去除厚度,除此之外的电极层23的去除厚度为2倍到5倍。由此,能够得到抑制了对电极层23造成的损伤的半导体模块。

(5)一种半导体模块1,其具有:层叠的多个电路模块20、和在层叠方向上延伸且将多个电路模块20电连接的导通孔50,电路模块20具有:基板21;布线层22,将其一个面作为相向面与基板21相向地配置;电极层23,其配置在布线层22的内部,电路模块20以从最下层向最上层交替地配置布线层22和基板21的方式层叠,并且从最下层向最上层按照从布线层22的面中的相反面到电极层23的距离从小到大的顺序层叠,所述相反面为与基板21相向的相向面的相反面,导通孔50从最上层向最下层缩径。由此,能够抑制上层侧的电路模块20的电极层23被蚀刻。因此,能够提高半导体模块1的品质,提高成品率。

(6)电极层23配置在与要层叠的电路模块20的层叠方向交叉的方向的位置中的与导通孔50的缩径率相匹配的位置。由此,能够使电路模块20各自的电极层23的上层侧的面露出,因此能够增加电极层23与导通孔50的接触面积。

[第二实施方式]

接下来,参照图10和图11对本发明的第二实施方式涉及的半导体模块1及其制造方法进行说明。在说明第二实施方式时,对同一结构元件标注同一标记,省略或简化其说明。

在第二实施方式涉及的半导体模块1及其制造方法中,如图10和图11所示,接口模块10仅由接口基板11构成,这一点与第一实施方式不同。此外,在第二实施方式涉及的半导体模块1及其制造方法中,电路模块20是将布线层22配置在下层侧、将基板21配置在上层侧来层叠的,这一点也与第一实施方式不同。与此相伴地,电路模块20从最下层向最上层按照布线层22的面中的与基板21相向的相向面到电极层23的距离从小到大的顺序层叠,这一点也与第一实施方式不同。而且,在各个电路模块20之间,从电极层23到下层侧的布线层22的厚度相同,这一点也与第一实施方式不同。此外,在第二实施方式涉及的半导体模块1的制造方法中,不使用硬掩模70,这一点也与第一实施方式不同。另外,在本实施方式中,向接口基板11(10)层叠五个电路模块20。

根据如以上这样的第二实施方式的半导体模块1,能够获得以下的效果。

(7)一种层叠多个电路模块20来制造半导体模块1的制造方法,包括:制造具有基板21和与基板21的一个面相邻的布线层22的多个电路模块20的步骤,该步骤包括针对多个电路模块分别形成电极层23的步骤;从最下层向最上层层叠多个电路模块20的步骤,以从最下层向最上层交替地配置布线层22和基板21的方式层叠电路模块20;形成从最上层向最下层在电路模块20的层叠方向延伸且电路模块20各自的电极层23露出的通路孔30的步骤,该步骤包括形成从最上层向最下层在电路模块20的层叠方向延伸的通路孔30的引导孔的步骤、和通过扩大引导孔来使最下层的电路模块20的电极层23和不是最下层的电路模块20的电极层23露出的步骤;形成露出电极层23的通路孔30的步骤;通过在通路孔30配置导体来形成将所层叠的多个电路模块20贯通的导通孔50从而将各个电极层23电连接的步骤。由此,在朝向下层侧形成了通路孔30的引导孔之后,通过扩大引导孔,露出电极层23。虽然与下层侧相比,先在上层侧的电路模块20形成引导孔,但上层侧的电极层23和下层侧的电极层23都是通过扩大引导孔而被露出。因此,能够抑制上层侧的电路模块20的电极层23被蚀刻。此外,制造多个电路模块20的步骤可以包括:针对多个电路模块20分别在距布线层22的面中的相向面的距离不同的位置形成电极层23的步骤,所述相向面为与基板21相向的面;从最下层向最上层按照电极层23的距离从小到大的顺序层叠电路模块20的步骤。由此,能够进一步抑制上层侧的电路模块20的电极层23被蚀刻。因此,能够提高半导体模块1的品质,提高成品率。

(8)一种半导体模块1,其具有:层叠的多个电路模块20、和在层叠方向延伸且将多个电路模块20电连接的导通孔50,电路模块20具有:基板21;布线层22,将其一个面作为相向面而与基板21相向地配置;电极层23,其配置在布线层22的内部,电路模块20以从最下层向最上层交替地配置布线层22和基板21的方式层叠,并且从最下层向最上层按照从布线层22的面中的与基板21相向的相向面到电极层23的距离从小到大的顺序层叠,导通孔50从最上层向最下层缩径。由此,能够抑制上层侧的电路模块20的电极层23被蚀刻。因此,能够提高半导体模块1的品质,提高成品率。

[第三实施方式]

接下来,参照图12至图15对本发明的第三实施方式涉及的半导体模块1及其制造方法进行说明。在说明第三实施方式时,对同一结构元件标注同一符号,省略或简化其说明。

第三实施方式涉及的半导体模块1是改良电极层23的形状的半导体模块。在第三实施方式涉及的半导体模块1中,如图12所示,最下层的电极层23(或接口电极层13)形成为俯视时呈圆形或多边形状。而且,如图13和图14所示,最下层以外的电极层23形成为环状。此外,作为另一例,如图15所示,最下层以外的电极层23形成为凸片状。

根据如以上这样的第三实施方式的半导体模块1,能够获得以下的效果。

(9)电极层23形成为俯视时呈环状或凸片状。由此,即使在通路孔30的位置偏离的情况下,也能够在通路孔30露出电极层23。此外,在图14和图15的形状中,通路孔30和导通孔50仅与电极层23的一部分(例如在图14中为环的上边,在图15中为凸起的下方的部分)连接。其结果是,能够去除电极23所占据的面积,能够提高配置许多电极层23和导通孔50的情况下的配置密度,因此能够去除半导体模块1的面积。

以上,对本发明的半导体模块及其制造方法的优选的各实施方式进行了说明,但本发明不限于上述实施方式,能够适当进行变更。

例如,在上述实施方式中,针对多个电路模块20的每一个,在距与基板21相向的相向面221的距离、或者距与相向面221相反的相反面222的距离不同的位置,形成了电极层23,但不限于此。例如,只要能够抑制由蚀刻带来的对电极层23造成的损伤,也能够采用其他方法。例如,对于一部分的电极层23的形成位置,也可以将距与基板21相向的相向面221的距离、或者距与相向面221相反的相反面222的距离设为相同或大致相同。而且,与层叠方向交叉的方向上的电极层23的形成位置也可以根据在各个电路模块20中所预测的蚀刻量来调整。

此外,在上述实施方式中,在形成通路孔30的引导孔的步骤中,优选全部的电极层23都不露出,但不限于此。在形成通路孔30的引导孔的步骤中,也可以一部分的电极层23露出。即,在使其露出的步骤中,只要最下层的电极层23和至少一个不是最下层的电极层23露出即可。

此外,在形成通路孔30的引导孔的步骤中,例如,也可以露出所有电极层23的与层叠方向交叉的面的一区域。即,在使其露出的步骤中,只要露出最下层的电极层23和至少一个不是最下层的电极层23中的一部分区域以外的区域即可。

只要与将电极层23用作掩模层而产生的对电极层23造成的损伤相比能够减轻损伤,就实现了上述实施方式的结构和作用效果。

例如,在上述实施方式中,电极层23配置成在最下层的前一个电路模块20形成通路孔30的时点,露出与层叠方向交叉的方向的端面。与此相对,电极层23也可以配置成在最下层的电路模块20形成通路孔30的时点,露出与层叠方向交叉的方向的端面。由此,即使在与电极层23的层叠方向交叉的方向上,也能够抑制电极层23被蚀刻。

此外,在上述实施方式中,说明了形成一个通路孔30的例子,但不限于此。例如,也可以在多个位置同时形成通路孔30。

附图标记说明

1:半导体模块

10:接口模块

20:电路模块

11、21:基板

12、22:布线层

13、23:电极层

30:通路孔

50:导通孔

121、221:相向面

122、222:相反面。

- 半导体模块制造方法、电子装置制造方法、半导体模块和电子装置

- 用于制造散热板的方法、散热板、用于制造半导体模块的方法及半导体模块