半导体器件及其设计版图

文献发布时间:2023-06-19 12:14:58

技术领域

本发明涉及集成电路制造技术领域,尤其涉及一种半导体器件及其设计版图。

背景技术

只读存储器(Read-Only Memory,ROM)又称为固定存储器,是一种以非破坏性读出的方式工作的存储器件,信息一旦写入ROM后就固定下来,即使切断电源也不会丢失。ROM具有存储数据稳定、断电后数据不会改变、结构简单、使用方便等特点,用于存储各种固定程序和数据。

图1为一只读存储器的设计版图,图2为图1中有源区的分区情况示意图,图3为图1中所述只读存储器沿AA’方向的剖面结构示意图。参阅图1-图3,所述只读存储器的衬底100中形成有有源区110和隔离区120,所述有源区110包括垂直交错的第一有源分区111和第二有源分区112,所述衬底100的表面形成有栅极130,且所述栅极130平行设置在所述第一有源分区111两侧的衬底100上,所述第二有源分区112的表面还设置有电连接件140。所述第一有源分区111的宽度(即图1中CD1所表示的宽度)为所述有源区110的特征尺寸,且所述特征尺寸CD1例如为0.11μm。

图4为图1中所述只读存储器的有源区进行模拟光刻后的结构示意图,受光学邻近效应和其他因素的影响,进行模拟光刻形成的模拟有源区200的特征尺寸(即图4中CD2所表示的宽度)明显大于所述特征尺寸CD1。图5为图1中所述只读存储器的设计版图进行光刻后形成的只读存储器沿AA’方向的剖面结构示意图图,图5中CD3所表示的宽度为所述只读存储器中有源区310的特征尺寸,且CD3例如为0.216μm。综合上述情况可知,在制备所述只读存储器的过程中,实际形成的有源区的特征尺寸明显大于设计版图中有源区的特征尺寸。

然而,所述只读存储器还包括隔离区320和栅极330,所述栅极330形成于所述隔离区320上靠近所述有源区310的一侧。受半导体制造工艺的限制,在形成所述隔离区320的过程中,所述隔离区320与所述有源区310的交界处存在凹陷。参阅图3,在设计版图中有源区110和隔离区120的交界线与所述栅极130之间存在一定距离;参阅图5,当所述有源区310的特征尺寸过大时,有源区310和隔离区320的交界线出现偏移,使得栅极330搭在所述交界线上,所述交界线的凹陷内填满多晶硅(即图5中圆圈所表示的情况),从而导致所述只读存储器漏电,进而影响所述只读存储器的性能。

鉴于此,需要一种设计版图来解决进行光刻后有源区的特征尺寸过大的问题,减少或避免有源区和栅极连通,从而避免半导体器件漏电。

发明内容

本发明的目的在于提供一种半导体器件及其设计版图,第一有源分区切断的第二有源分区在光刻后会形成连续的第二有源分区,以使光刻后有源区的光刻特征尺寸更接近有源区的设计特征尺寸,减少或避免因光刻特征尺寸过大导致的所述有源区和栅极的连通,从而避免半导体器件漏电。

为了达到上述目的,本发明提供了一种半导体器件的设计版图,包括:

衬底,包括有源区和隔离区,所述有源区包括垂直交错的第一有源分区和第二有源分区,所述第一有源分区的宽度为所述有源区的设计特征尺寸,所述第一有源分区将所述第二有源分区切断,且所述第二有源分区与所述第一有源分区之间的距离为一设定值;

栅极,设置于所述第一有源分区两侧的衬底上,且所述栅极与所述第一有源分区之间存在一设定距离。

可选的,所述设定值介于所述设计特征尺寸的十分之一到二分之一之间。

可选的,所述设定值为0.01μm~0.05μm。

可选的,所述第一有源分区和所述第二有源分区的形状均包括矩形。

可选的,所述设计版图包括多个平行设置的所述第一有源分区,且每个所述第一有源分区与多个所述第二有源分区垂直交错。

可选的,与任一所述第一有源分区垂直交错的多个所述第二有源分区之间的间距相同。

可选的,所述设定距离介于所述设计特征尺寸的三分之一到三分之二。

可选的,所述设定距离为0.03μm~0.07μm。

可选的,所述第二有源分区中远离所述第一有源分区一侧的表面设置有电连接件。

相应地,本发明还提供一种半导体器件,根据所述半导体器件的设计版图制成。

可选的,所述半导体器件包括只读存储器。

综上所述,本发明提供一种半导体器件及其设计版图,所述半导体器件的设计版图包括衬底和栅极,所述衬底包括有源区和隔离区,所述有源区包括垂直交错的第一有源分区和第二有源分区,所述第一有源分区的宽度为所述有源区的设计特征尺寸,所述第一有源分区将所述第二有源分区切断,且所述第二有源分区与所述第一有源分区之间的距离为一设定值;所述栅极设置于所述第一有源分区两侧的衬底上,且所述栅极与所述第一有源分区之间存在一设定距离。本发明中,第一有源分区切断的第二有源分区在光刻后会形成连续的第二有源分区,以使光刻后有源区的光刻特征尺寸更接近有源区的设计特征尺寸,减少或避免因光刻特征尺寸过大导致的所述有源区和栅极的连通,从而避免半导体器件漏电。

附图说明

图1和图2为一只读存储器的设计版图;

图3为图1中所述的只读存储器沿AA’方向的剖面结构示意图;

图4为图1中所述只读存储器的有源区进行模拟光刻后的结构示意图;

图5为图1中所述的只读存储器进行光刻后沿AA’方向的剖面结构示意图图;

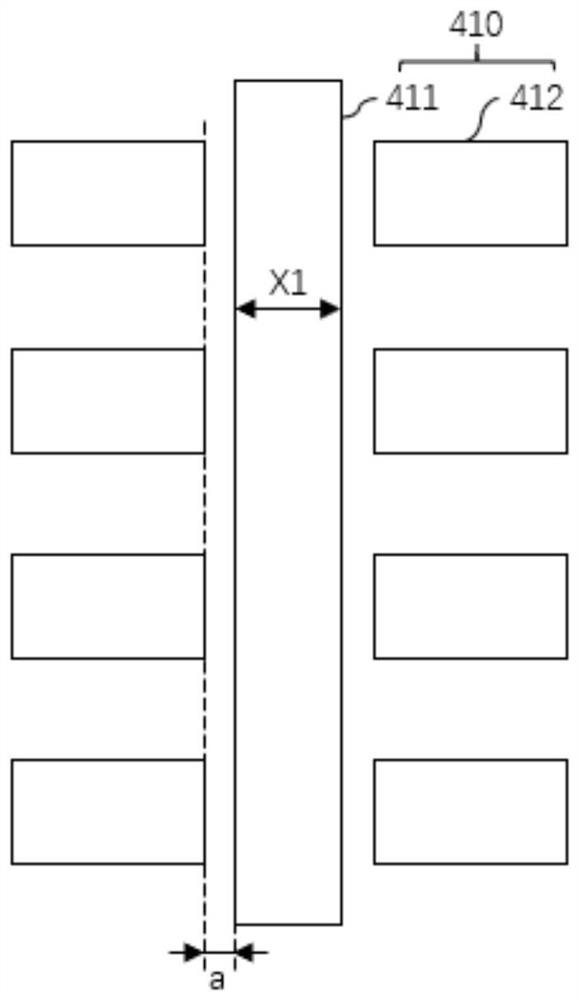

图6为本发明一实施例提供的半导体器件的设计版图;

图7为本发明一实施例提供的有源区的设计版图;

图8为本发明一实施例提供的半导体器件的设计版图光刻后的有源区结构示意图;

其中,附图标记如下:

100-衬底;110-有源区;111-第一有源分区;112-第二有源分区;120-隔离区;130-栅极;140-电连接件;

200-模拟有源区;

300-衬底;310-有源区;320-隔离区;330-栅极;

400-衬底;410-有源区;411-第一有源分区;412-第二有源分区;420-隔离区;430-栅极;440-电连接件;

510-光刻有源区;511-第一光刻有源分区;512-第二光刻有源分区;

CD1、CD2、CD3-特征尺寸;X1-设计特征尺寸;X2-光刻特征尺寸。

具体实施方式

下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下列描述,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

图6为本发明一实施例提供半导体器件的设计版图,图7为本发明一实施例提供的有源区的设计版图。参阅图6和图7,本实施例所述的半导体器件的设计版图包括衬底400,所述衬底400包括有源区410和隔离区420,所述有源区410包括垂直交错的第一有源分区411和第二有源分区412,所述第一有源分区411的宽度为所述有源区410的设计特征尺寸X1,所述第一有源分区411将所述第二有源分区412切断,且所述第二有源分区412与所述第一有源分区411之间的距离为一设定值;栅极430,设置于所述第一有源分区411两侧的衬底400上,且所述栅极430与所述第一有源分区411之间存在一设定距离。

本实施例中,所述第一有源分区411和所述第二有源分区412的形状均为矩形,在本发明的其他实施例中,所述第一有源分区411和所述第二有源分区412的形状可以根据实际需要进行调整,本发明对此不做限制。可选的,所述设计版图包括多个平行设置的所述第一有源分区411,且每个所述第一有源分区411与多个所述第二有源分区412垂直交错。参阅图7,与任一所述第一有源分区411垂直交错的多个所述第二有源分区412之间的间距相同。在本发明的其他实施例中,与一第一有源分区垂直交错的多个第二有源分区之间的间距也可以不同,本发明对此不作限制。

继续参阅图7,所述设定值(即图7中a所表示的距离)介于所述设计特征尺寸X1的十分之一到二分之一之间。可选的,所述设定值为0.01μm~0.05μm。需要说明的是,所述设定值的具体数值与所述第一有源分区411和所述第二有源分区412的尺寸有关,所述第一有源分区411和所述第二有源分区412的尺寸与技术节点有关,因此,需要通过仿真来确定所述设定值的具体数值。

继续参阅图6,所述设定距离(即图6中b所表示的距离)介于所述设计特征尺寸X1的三分之一到三分之二。可选的,所述设定距离为0.03μm~0.07μm。需要说明的是,受半导体制造工艺的限制,实际形成的半导体器件中隔离区与有源区的交界处存在凹陷,因此,所述第一有源分区411和所述栅极430存在所述设定距离可以避免栅极形成于所述凹陷上,从而减少或避免所形成的半导体器件漏电。

可选的,所述第二有源分区412中远离所述第一有源分区411一侧的表面设置有电连接件440。

图8为本实施例所述的半导体器件的设计版图进行光刻后的有源区结构示意图。参阅图7和图8,受光学邻近效应及其他因素的影响,所述有源区410在进行光刻后形成光刻有源区510,所述第一有源分区411在光刻后形成第一光刻有源分区511,所述第二有源分区412在进行光刻后形成连续的第二光刻有源分区512,此时所述光刻有源区510的特征尺寸为光刻特征尺寸X2。对比图4和图8可知,与现有技术相比,本实施例所述的半导体器件的设计版图进行光刻后得到的光刻特征尺寸X2更接近有源区的设计特征尺寸X1,减少或避免因光刻特征尺寸过大导致的所述有源区和栅极的连通,从而避免半导体器件漏电。

相应地,本发明还提供一种半导体器件,根据所述半导体器件的设计版图制成。本实施例中,所述半导体器件为只读存储器,在本发明的其他实施例中,所述半导体器件还可以为其他具有相同结构的半导体器件,本发明对此不作限制。

综上,本发明提供一种半导体器件及其设计版图,所述半导体器件的设计版图包括衬底和栅极,所述衬底包括有源区和隔离区,所述有源区包括垂直交错的第一有源分区和第二有源分区,所述第一有源分区的宽度为所述有源区的设计特征尺寸,所述第一有源分区将所述第二有源分区切断,且所述第二有源分区与所述第一有源分区之间的距离为一设定值;所述栅极设置于所述第一有源分区两侧的衬底上,且所述栅极与所述第一有源分区之间存在一设定距离。本发明中,第一有源分区切断的第二有源分区在光刻后会形成连续的第二有源分区,以使光刻后有源区的光刻特征尺寸更接近有源区的设计特征尺寸,减少或避免因光刻特征尺寸过大导致的所述有源区和栅极的连通,从而避免半导体器件漏电。

上述仅为本发明的优选实施例而已,并不对本发明起到任何限制作用。任何所属技术领域的技术人员,在不脱离本发明的技术方案的范围内,对本发明揭露的技术方案和技术内容做任何形式的等同替换或修改等变动,均属未脱离本发明的技术方案的内容,仍属于本发明的保护范围之内。

- 半导体器件及其设计版图

- 标准单元、半导体集成电路器件及其版图设计方法