一种改善底部线宽均匀性的刻蚀方法及装置

文献发布时间:2023-06-19 13:26:15

技术领域

本申请涉及半导体器件制造技术领域,尤其涉及一种改善底部线宽均匀性的刻蚀方法及装置。

背景技术

随着科技的不断发展,半导体元器件在电子行业已经得到了广泛的应用。而在半导体元器件的制造工艺中,刻蚀技术又是至关重要的一部分,通常刻蚀技术可以分为湿法刻蚀和干法刻蚀。其中,等离子刻蚀是干法刻蚀中较为常见的一种方式,原理是利用暴露在电子区域的气体形成等离子体,等离子体通过电场加速时,会释放足够的能量,促使等离子体与材料表面发生反应,从而完成对半导体材料表面的刻蚀。在等离子刻蚀的过程中,底部线宽的均匀性是重要参数之一,底部线宽均匀性对于后续工艺以及整个制程的良品率有着很大的影响,也会影响到公司的生产成本和收益,因此,如何在刻蚀的过程中改善底部线宽的均匀性,是人们一直关注的问题。

发明内容

有鉴于此,本申请提供了一种改善底部线宽均匀性的刻蚀方法及装置,以便于在刻蚀的过程中一定程度上改善底部线宽的均匀性。

为了实现上述目的,现提出的方案如下:

一种改善底部线宽均匀性的刻蚀方法,对曝光后的待刻蚀半导体基底进行刻蚀处理,所述待刻蚀半导体基底由上至下包括光阻层、抗反射层、TiN层、Al层、Ti层和氧化物层,刻蚀的过程包括:

响应用户发送的刻蚀指令,控制第一混合气体输入反应腔室,对所述待刻蚀半导体基底的抗反射层进行刻蚀;

在抗反射层刻蚀完成之后,控制第二混合气体输入反应腔室,对所述待刻蚀半导体基底的TiN层进行刻蚀;

在TiN层刻蚀完成之后,控制第三混合气体输入反应腔室,并将电流比例在0.2~0.8之间进行调节,对所述待刻蚀半导体基底的Al层进行刻蚀,所述第三混合气体中包括N

在Al层刻蚀完成之后,控制第四混合气体输入反应腔室,对所述待刻蚀半导体基底的Ti层和氧化物层进行刻蚀处理。

可选的,所述第三混合气体中还包括:BCl

可选的,所述第一混合气体包括:Cl

可选的,控制第四混合气体输入反应腔室,对所述待刻蚀半导体基底的Ti层和氧化物层进行刻蚀处理,包括:

控制第四混合气体输入反应腔室;

调节反应腔室中的电流比例和偏置电压,对所述待刻蚀半导体基底的Ti层和氧化物层进行刻蚀处理。

可选的,在响应用户发送的刻蚀指令,控制第一混合气体输入反应腔室,对所述待刻蚀半导体基底的抗反射层进行刻蚀之前,还包括:

控制Cl

可选的,在控制第四混合气体输入反应腔室,对所述待刻蚀半导体基底的Ti层和氧化物层进行刻蚀处理之后,还包括:

去除所述待刻蚀半导体基底上方的光阻层和抗反射层。

可选的,在控制第四混合气体输入反应腔室,对所述待刻蚀半导体基底的Ti层和氧化物层进行刻蚀处理之后,还包括:

控制O

一种改善底部线宽均匀性的刻蚀装置,用于对曝光后的待刻蚀半导体基底进行刻蚀处理,所述待刻蚀半导体基底由上至下包括光阻层、抗反射层、TiN层、Al层、Ti层和氧化物层,装置包括:

抗反射层刻蚀模块,用于响应用户发送的刻蚀指令,控制第一混合气体输入反应腔室,对所述待刻蚀半导体基底的抗反射层进行刻蚀;

TiN层刻蚀模块,用于在抗反射层刻蚀完成之后,控制第二混合气体输入反应腔室,对所述待刻蚀半导体基底的TiN层进行刻蚀;

Al层刻蚀模块,用于在TiN层刻蚀完成之后,控制第三混合气体输入反应腔室,并将电流比例在0.2~0.8之间进行调节,对所述待刻蚀半导体基底的Al层进行刻蚀,所述第三混合气体中包括N

Ti层和氧化物层刻蚀模块,用于在Al层刻蚀完成之后,控制第四混合气体输入反应腔室,对所述待刻蚀半导体基底的Ti层和氧化物层进行刻蚀处理。

可选的,还包括:

反应腔室清理模块,用于控制Cl

可选的,还包括:

腐蚀预防模块,用于控制O

从上述的技术方案可以看出,本申请实施例提供的一种改善底部线宽均匀性的刻蚀方法,对曝光后的待刻蚀半导体基底进行刻蚀,刻蚀的过程中,通过响应用户发送的刻蚀指令,控制第一混合气体输入反应腔室,对待刻蚀半导体基底的抗反射层进行刻蚀,在抗反射层刻蚀完成之后,控制第二混合气体输入反应腔室,对待刻蚀半导体基底的TiN层进行刻蚀,在TiN层刻蚀完成之后,控制第三混合气体中的N

由于待刻蚀半导体基底边缘处离子运动轨迹会发生偏移,这使得对边缘进行刻蚀时,容易出现侧壁被刻蚀的情况出现,从而导致与中心的底部线宽相差较大,在本申请中第三混合气体包括N

附图说明

为了更清楚地说明本申请实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据提供的附图获得其他的附图。

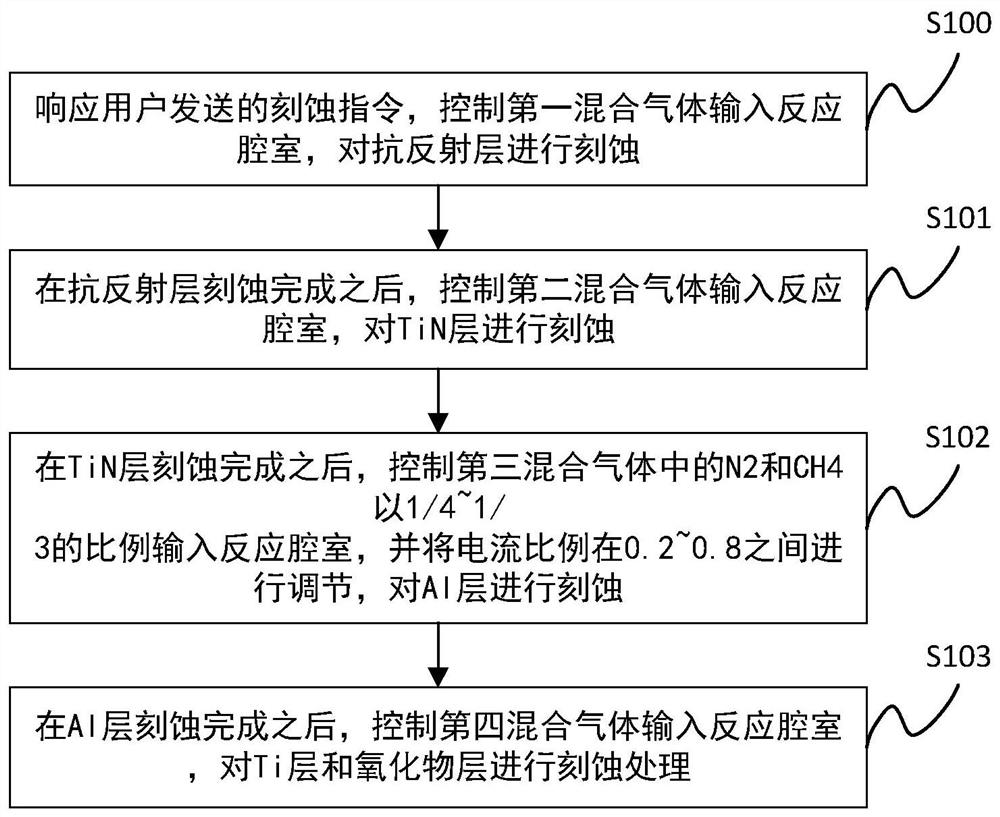

图1为本申请实施例提供的一种改善底部线宽均匀性的刻蚀方法流程图;

图2为本申请实施例提供的一种刻蚀过程示意图;

图3为本申请实施例提供的一种刻蚀前后的待刻蚀半导体基底示意图;

图4为本申请实施例提供的一种改善底部线宽均匀性的刻蚀装置结构示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

图1为本申请实施例提供的一种改善底部线宽均匀性的刻蚀方法流程图,参考图1所示,采用该方法可以对曝光后的待刻蚀半导体基底进行刻蚀处理,其中,待刻蚀半导体基底由上至下包括光阻层、抗反射层、TiN层、Al层、Ti层和氧化物层,改善底部线宽均匀性的刻蚀方法可以包括以下步骤:

步骤S100、响应用户发送的刻蚀指令,控制第一混合气体输入反应腔室,对抗反射层进行刻蚀。

具体的,对待刻蚀半导体基底的抗反射层进行刻蚀是刻蚀的第一步,可以控制第一混合气体输入反应腔室的气体流量,来控制开口的大小,开口的大小对于后续其他层的刻蚀会产生一定的影响。其中,开口的大小会影响顶部线宽的大小,顶部线宽的标准宽度可以设置为230nm,最大的顶部线宽与最小的顶部线宽的差别在13nm之内,可以视为符合顶部线宽均匀性的标准。

步骤S101、在抗反射层刻蚀完成之后,控制第二混合气体输入反应腔室,对TiN层进行刻蚀。

具体的,在上述步骤中将未被光阻所覆盖的抗反射层清除之后,可以控制第二混合气体输入反应腔室,对暴露出来的TiN层进行刻蚀。

步骤S102、在TiN层刻蚀完成之后,控制第三混合气体中的N2和CH4以1/4~1/3的比例输入反应腔室,并将电流比例在0.2~0.8之间进行调节,对Al层进行刻蚀。

其中,上述电流比例为反应腔室中的边缘电流与总电流的比值。

具体的,在待刻蚀半导体基底中Al层的占比最大,刻蚀完成后可以将Al层最下方区域视为底部,从而可以确定刻蚀后的底部线宽。

在对Al层的刻蚀过程中,第三混合气体中包括N

在本步骤中将N

其中,可以将底部线宽的标准宽度设置为245nm,最大的底部线宽与最小的底部线宽的差别在5nm之内,可以视为符合底部线宽均匀性的要求。一般情况下,中心和边缘的底部线宽不一致是影响底部线宽均匀性的原因之一,所以可以通过比较中心的底部线宽与边缘的底部线宽来判断底部线宽的均匀性。

步骤S103、在Al层刻蚀完成之后,控制第四混合气体输入反应腔室,对Ti层和氧化物层进行刻蚀处理。

具体的,通过上述步骤,可以将Al层刻蚀完成,此时可以控制第四混合气体输入反应腔室,对Ti层和氧化物层进行刻蚀。在对Ti层和氧化物层刻蚀完成之后,则完成了对待刻蚀半导体基底的刻蚀。其中,在控制第四混合气体输入反应腔室,对Ti层和氧化物层进行刻蚀的过程中,需要控制底部的形貌和改善底部深度的均匀性,还需要对氧化物层的刻蚀量进行控制,使得满足制程的要求和工艺标准。其中,氧化物层的刻蚀量的标准尺寸可以设置为大于40nm,一般标准机台要求的尺寸可以是50nm。

上述实施例中,提供的一种改善底部线宽均匀性的刻蚀方法,对曝光后的待刻蚀半导体基底进行刻蚀,刻蚀的过程中,通过响应用户发送的刻蚀指令,控制第一混合气体输入反应腔室,对待刻蚀半导体基底的抗反射层进行刻蚀,在抗反射层刻蚀完成之后,控制第二混合气体输入反应腔室,对待刻蚀半导体基底的TiN层进行刻蚀,在TiN层刻蚀完成之后,控制第三混合气体中的N

由于待刻蚀半导体基底边缘处离子运动轨迹会发生偏移,这使得对边缘进行刻蚀时,容易出现侧壁被刻蚀的情况出现,从而导致与中心的底部线宽相差较大,在本申请中第三混合气体包括N

在本申请的一些实施例中,参考图2所示,图2为本申请实施例提供的一种刻蚀过程示意图,对待刻蚀半导体基底进行刻蚀的过程可以包括以下步骤:

S1、抗反射层刻蚀。

具体的,控制第一混合气体输入反应腔室,将待刻蚀半导体基底的抗反射层清除。

其中,上述第一混合气体中可以包括:Cl

在对待刻蚀半导体基底的刻蚀过程中,对抗反射层的刻蚀属于该刻蚀过程的第一步,在对抗反射层刻蚀之后,不仅有可能会对开口产生影响,还可能会一定程度上影响底部线宽和底部线宽的均匀性。

S2、TiN层刻蚀。

具体的,控制第二混合气体输入反应腔室,将待刻蚀半导体基底的TiN层清除。

其中,本步骤中输入反应腔室的第二混合气体可以包括:BCl

在本步骤中,可以对输入反应腔室的第二混合气体中的BCl

S3、Al层主体刻蚀。

具体的,控制第三混合气体输入反应腔室,对待刻蚀半导体基底的Al层进行刻蚀,刻蚀掉大部分的Al。

在本步骤中,第三混合气体除了N

由于待刻蚀半导体基底边缘处离子运动轨迹会发生偏移,这使得对边缘进行刻蚀时,容易出现侧壁被刻蚀的情况出现,从而导致与中心的底部线宽相差较大。在本申请中第三混合气体包括N

为了改善底部线宽的均匀性,可以将N

其中,在对待刻蚀半导体基底的刻蚀过程中,对Al层主体的刻蚀是耗时最长,也是较为关键的一步。通过在Al层主体的刻蚀过程中,对电流比例以及N

S4、Al层补充刻蚀。

具体的,在上述步骤中,可以刻蚀掉大部分的Al,上述步骤的停止刻蚀的方式一般可以采用自动找终点的方式。在刻蚀掉大部分的Al之后,可以利用该步骤刻蚀掉上一步骤中未刻蚀干净的少量Al,以确保无Al残留。

在对剩余的Al层进行刻蚀的过程中,通入第三混合气体,将第三混合气体中N

在本步骤中,可以保证Al层被刻蚀完,而且还能保证Al层的正常形貌,对于第三混合气体的流量以及比例进行控制,加上电流比例的调节,可以有效的减少刻蚀产品出现缺陷或者形貌上的不足。如果工艺控制不当,很可能会出现侧壁的钻刻。

S5、Ti和氧化物层刻蚀。

具体的,控制第四混合气体输入反应腔室,对待刻蚀半导体基底的Ti层和氧化物层进行刻蚀处理。

其中,第四混合气体中可以包括:BCl

进一步的,在对Ti层和氧化物层进行刻蚀的过程中,为控制底部的形貌和改善底部深度的均匀性,可以通过反应腔室中的偏置电压大小,以及调节电流比例,从而控制底部的形貌和改善底部深度的均匀性。其中,电流比例的调节可以对刻蚀速率也带来一定的影响,一般电流比例增大,可以使得边缘的刻蚀速率加快,相反的,电流比例减小,可以使得中心的刻蚀速率加快。

在本申请的一些实施例中,反应腔室使用后,可能会残留Al或者Al

具体的,为了清理残留在反应腔室中的Al或者Al

其中,O

在本申请的一些实施例中,在控制第四混合气体输入反应腔室,对待刻蚀半导体基底的Ti层和氧化物层进行刻蚀处理之后,由于此时刻蚀已经完成,剩余的光阻层和抗反射层会影响后续的其他工艺流程,所以可以对刻蚀后的半导体基底上方的光阻层和抗反射层进行清除。

具体的,可以向反应腔室输入O

进一步的,结合图3所示,刻蚀前放入反应腔体中的待刻蚀半导体基底包含:光阻层、抗反射层、TiN层、Al层、Ti层和氧化物层,经过上述实施例对待刻蚀半导体基底进行刻蚀,并且将待刻蚀半导体基底上方剩余的光阻层和抗反射层清除之后,从反应腔室中取出的刻蚀后的半导体基底包含TiN层、Al层、Ti层和氧化物层。

在本申请的一些实施例中,对待刻蚀半导体基底的刻蚀过程中使用了Cl

具体的,为了避免出现Cl

下面对本申请实施例提供的一种改善底部线宽均匀性的刻蚀装置进行描述,下文描述的一种改善底部线宽均匀性的刻蚀装置与上文描述的一种改善底部线宽均匀性的刻蚀方法可相互对应参照。

参考图4所示,图4为本申请实施例提供的一种改善底部线宽均匀性的刻蚀装置结构示意图,改善底部线宽均匀性的刻蚀装置用于对曝光后的待刻蚀半导体基底进行刻蚀处理,所述待刻蚀半导体基底由上至下包括光阻层、抗反射层、TiN层、Al层、Ti层和氧化物层,改善底部线宽均匀性的刻蚀装置可以包括:

抗反射层刻蚀模块10,用于响应用户发送的刻蚀指令,控制第一混合气体输入反应腔室,对所述待刻蚀半导体基底的抗反射层进行刻蚀;

TiN层刻蚀模块20,用于在抗反射层刻蚀完成之后,控制第二混合气体输入反应腔室,对所述待刻蚀半导体基底的TiN层进行刻蚀;

Al层刻蚀模块30,用于在TiN层刻蚀完成之后,控制第三混合气体输入反应腔室,并将电流比例在0.2~0.8之间进行调节,对所述待刻蚀半导体基底的Al层进行刻蚀,所述第三混合气体中包括N

Ti层和氧化物层刻蚀模块40,用于在Al层刻蚀完成之后,控制第四混合气体输入反应腔室,对所述待刻蚀半导体基底的Ti层和氧化物层进行刻蚀处理。

上述实施例中,提供的一种改善底部线宽均匀性的刻蚀装置,对曝光后的待刻蚀半导体基底进行刻蚀,刻蚀的过程中,通过抗反射层刻蚀模块10响应用户发送的刻蚀指令,控制第一混合气体输入反应腔室,对待刻蚀半导体基底的抗反射层进行刻蚀,在抗反射层刻蚀完成之后,TiN层刻蚀模块20控制第二混合气体输入反应腔室,对待刻蚀半导体基底的TiN层进行刻蚀,在TiN层刻蚀完成之后,Al层刻蚀模块30控制第三混合气体中的N

由于待刻蚀半导体基底边缘处离子运动轨迹会发生偏移,这使得对边缘进行刻蚀时,容易出现侧壁被刻蚀的情况出现,从而导致与中心的底部线宽相差较大,在本申请中Al层刻蚀模块30控制输入反应腔室的第三混合气体中包括N

可选的,改善底部线宽均匀性的刻蚀装置,还可以包括:

反应腔室清理模块,用于控制Cl

可选的,改善底部线宽均匀性的刻蚀装置,还可以包括:

腐蚀预防模块,用于控制O

可选的,Ti层和氧化物层刻蚀模块40,可以包括:

气体控制模块,用于控制第四混合气体输入反应腔室;

电流电压调节模块,用于调节反应腔室中的电流比例和偏置电压,对所述待刻蚀半导体基底的Ti层和氧化物层进行刻蚀处理。

可选的,改善底部线宽均匀性的刻蚀装置,还可以包括:

清除模块,用于去除所述待刻蚀半导体基底上方的光阻层和抗反射层。

最后,还需要说明的是,在本文中,诸如第一和第二等之类的关系术语仅仅用来将一个实体或者操作与另一个实体或操作区分开来,而不一定要求或者暗示这些实体或操作之间存在任何这种实际的关系或者顺序。而且,术语“包括”、“包含”或者其任何其他变体意在涵盖非排他性的包含,从而使得包括一系列要素的过程、方法、物品或者设备不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者设备所固有的要素。在没有更多限制的情况下,由语句“包括一个……”限定的要素,并不排除在包括所述要素的过程、方法、物品或者设备中还存在另外的相同要素。

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间可以相互组合,且相同相似部分互相参见即可。

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本申请。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本申请的精神或范围的情况下,在其它实施例中实现。因此,本申请将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

- 一种改善底部线宽均匀性的刻蚀方法及装置

- 一种改善等离子体刻蚀均匀性的装置及方法