一种优化电场特性的分裂栅沟槽MOS及其制造方法

文献发布时间:2023-06-19 13:46:35

技术领域

本发明涉及分裂栅沟槽MOSFET技术领域,具体涉及一种优化电场特性的分裂栅沟槽MOS及其制造方法。

背景技术

传统N型SGT MOS的电场分布如图1所示,Pbody和N漂移区形成的PN结处和沟槽底部出现两个电场尖峰,而中间部位电场强度较弱,存在低电场区域,没有使屏蔽栅结构作为体内场板的优势完全发挥。存在这一现象的原因为:1)由于刻蚀和填充工艺能力的限制,SGT的深沟槽不是完全垂直的,存在一定的斜度;2)沟槽底部的电场为球形分布,电场曲率半径很小,电场强度太高,导致中间部位电场无法拉平。

发明内容

本发明的目的是针对现有技术存在的不足,提供一种优化电场特性的分裂栅沟槽MOS及其制造方法。

为实现上述目的,在第一方面,本发明提供了一种优化电场特性的分裂栅沟槽MOS的制造方法,包括:

提供第一导电类型的衬底,在所述衬底的上侧制作外延层,具体如下:

在所述衬底的上侧生长掺杂浓度为N3的第一外延层;调整掺杂源的浓度使掺杂浓度线性增加,并在所述第一外延层的上侧生长掺杂浓度从N3至N2线性增加的第二外延层;调整掺杂源的浓度使掺杂浓度线性降低,并在所述第二外延层的上侧生长掺杂浓度从N2至N1线性降低的第三外延层;在所述第三外延层的上侧生成掺杂浓度为N1的第四外延层;

在所述外延层上刻蚀形成若干沟槽;

在所述外延层的上侧及沟槽内生长第一氧化层;

在所述第一氧化层的内侧淀积经第一导电类型杂质掺杂的多晶硅,然后通过光刻和刻蚀形成屏蔽栅;

在所述屏蔽栅的上侧经淀积、化学机械抛光和刻蚀操作形成隔离氧化层;

在所述隔离氧化层上侧的沟槽侧壁上制作栅氧化层,然后在所述隔离氧化层上侧的沟槽淀积经第一导电类型杂质掺杂的多晶硅,通过光刻、刻蚀操作形成多晶硅栅,在所述多晶硅栅的上侧生长第二氧化层;

在所述栅氧化层四周的外延层内执行体区注入操作和体区退火操作,以制作形成第二导电类型的体区;

并在所述体区的上端执行源区光刻、源区注入操作和源区退火操作,以制作形成第一导电类型的源区;

在所述外延层的上侧淀积介质层,并在所述介质层和外延层上刻蚀形成连接孔;

在所述介质层的上侧及连接孔内沉积金属层,所述金属层经刻蚀形成源极金属和栅极金属。

进一步的,所述第一外延层的厚度为沟槽深度的三分之二,所述第二外延层的厚度为沟槽深度的六分之一,所述第三外延层的厚度为沟槽深度的四分之一,所述第四外延层的厚度为沟槽深度的二分之一。

进一步的,所述N3的取值均为2E16-3E16,且(1+10%)*N1≥N3≥N1。

进一步的,所述N2取值为7E16-1E17。

进一步的,所述沟槽的深度为2-8um,其宽度为0.2-1.5um。

在第二方面,本发明提供了一种优化电场特性的分裂栅沟槽MOS,包括第一导电类型的衬底和设置在所述衬底上侧的外延层,所述外延层包括依次设置在衬底上侧的第一外延层、第二外延层、第三外延层和第四外延层,所述第一外延层的掺杂浓度为N3,所述第二外延层的掺杂浓度从N3至N2线性增加,所述第三外延层的掺杂浓度为从N2至N1线性降低,所述第四外延层的掺杂浓度为N1,所述外延层上刻蚀形成有若干沟槽,所述沟槽内生长有第一氧化层,所述第一氧化层的内侧制作形成有屏蔽栅,所述屏蔽栅的上侧淀积形成有隔离氧化层,所述隔离氧化层的上侧制作形成有多晶硅栅,所述多晶硅栅与外延层之间设有栅氧化层,且其上侧生长有第二氧化层,所述栅氧化层四周的外延层内制作形成有第二导电类型的体区,所述体区的上端制作形成有第一导电类型的源区,所述外延层的上侧淀积有介质层,所述介质层和外延层上刻蚀形成有连接孔,所述介质层的上侧及连接孔内沉积金属层,所述金属层经刻蚀形成源极金属和栅极金属。

进一步的,所述第一外延层的厚度为沟槽深度的三分之二,所述第二外延层的厚度为沟槽深度的六分之一,所述第三外延层的厚度为沟槽深度的四分之一,所述第四外延层的厚度为沟槽深度的二分之一。

进一步的,所述N3的取值均为2E16-3E16,且(1+10%)*N1≥N3≥N1。

进一步的,所述N2取值为7E16-1E17。

进一步的,所述沟槽的深度为2-8um,其宽度为0.2-1.5um。

有益效果:1、本发明通过调节外延层的掺杂分布,使SGT MOSFET中间部位的电荷补偿能力增强,电场分布更加接近梯形分布,增加了器件的耐压能力,并且在击穿电压相同的情况下,导通电阻可以减小30%左右;

2、本发明与传统SGT工艺相同,在不显著增加加工成本的前提下可以实现。

附图说明

图1是传统N型SGT MOS的电场分布图;

图2是在衬底上制作外延层后的结构示意图;

图3是在外延层上刻蚀形成沟槽后的结构示意图;

图4是在外延层的上侧及沟槽内生长第一氧化层后的结构示意图;

图5是在沟槽内制作出屏蔽栅后的结构示意图;

图6是在屏蔽栅的上侧生长隔离氧化层后的结构示意图;

图7是在沟槽的上端生长栅氧化层后的结构示意图;

图8是在沟槽的上端制作出多晶硅栅并生长第二氧化层后的结构示意图;

图9是在外延层内制作出体区和源区后的结构示意图;

图10是在介质层上刻蚀出连接孔后的结构示意图;

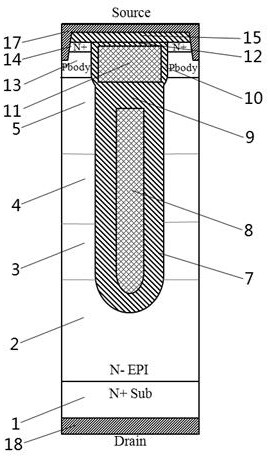

图11是制作出源极金属和背金层后的结构示意图;

图12是优化电场特性的分裂栅沟槽MOS的电场分布图;

图13是具有优化电场特性的分裂栅沟槽MOSFET与传统结构电场分布对比图;

图14是具有优化电场特性的分裂栅沟槽MOSFET与传统结构的掺杂浓度对比图。

具体实施方式

下面结合附图和具体实施例,进一步阐明本发明,本实施例在以本发明技术方案为前提下进行实施,应理解这些实施例仅用于说明本发明而不用于限制本发明的范围。

如图2至11所示,本发明实施例提供了一种优化电场特性的分裂栅沟槽MOS的制造方法,包括:

参见图2,提供第一导电类型的衬底1,在衬底1的上侧制作外延层,具体如下:在衬底1的上侧生长掺杂浓度为N3的第一外延层2,N3的取值优选为2E16-3E16。调整掺杂源的浓度使掺杂浓度线性增加,并在第一外延层2的上侧生长掺杂浓度从N3至N2线性增加的第二外延层3,N2取值优选为7E16-1E17。调整掺杂源的浓度使掺杂浓度线性降低,并在第二外延层3的上侧生长掺杂浓度从N2至N1线性降低的第三外延层4,N1与N3相同或接近,优选的,(1+10%)*N1≥N3≥N1;在第三外延层4的上侧生成掺杂浓度为N1的第四外延层5。本发明的技术方案对于N型MOSFET和P型MOSFET均适用,为了便于描述技术方案,以下以N型MOSFET为例说明。N型MOSFET的衬底1一般采用砷元素掺杂,掺杂浓度为N4,与现有技术中的掺杂浓度相同,大于外延层的掺杂浓度,电阻率通常在0.001-0.05Ω.cm。

参见图3,在外延层上刻蚀形成若干沟槽6。具体的,在沟槽刻蚀前先在外延层的上侧淀积一层SiO2/SiN/SiO2结构,总厚度为4000埃左右,SiO2/SiN/SiO2结构的厚度可根据沟槽6刻蚀形貌做微调。然后进行沟槽光刻、沟槽刻蚀形成沟槽6,沟槽6的厚度优选为2-8um,其宽度优选为0.2-1.5um,倾斜角度优选为88-89度,便于后续多晶硅和栅氧化层填充。

参见图4,在外延层的上侧及沟槽6内生长第一氧化层7。具体的,可通过干-湿-干法的氧化和CVD方法形成第一氧化层7,第一氧化层7的厚度为3500-7000埃。

参见图5,在第一氧化层7的内侧执行多晶硅淀积、光刻和刻蚀操作,以在第一氧化层7的内侧制作形成屏蔽栅8。一般沉积多晶硅的厚度为0.8-1.2um,在经过刻蚀后,只保留沟槽6内的大半部分。此处淀积的多晶硅是经过N型元素掺杂的,掺杂浓度为1E19-6E19,掺杂元素优选为磷。

参见图6,在屏蔽栅8的上侧淀积形成隔离氧化层9。在淀积时,可将沟槽6内淀积填充满,然后再通过化学机械抛光和刻蚀操作保留5000-10000埃的厚度,隔离氧化层9用于将屏蔽栅8与沟槽6的上端区域隔离。

参见图7和图8,在隔离氧化层9上侧的沟槽6侧壁上制作栅氧化层10,然后在隔离氧化层9上侧的沟槽6内执行多晶硅淀积、光刻和刻蚀操作,以在隔离氧化层的上侧制作形成多晶硅栅11,在多晶硅栅11的上侧生长第二氧化层12。栅氧化层10的厚度优选为500-1000埃,生长温度一般为950℃-1050℃,栅氧化层10的厚度越厚,则需要更高的温度生长。在生长栅氧化层10前还可对沟槽6的侧壁通过干法氧化形成一层厚度200-300埃的牺牲氧化层,氧化温度1000-1100℃,然后用湿法漂洗去500埃左右的牺牲氧化层和外延层。此处沉积多晶硅的厚度也优选为0.8-1.2um,此步骤淀积的多晶硅也是通过N型元素掺杂的,掺杂浓度为1E19-6E19,掺杂元素优选为磷。

参见图9,在栅氧化层10四周的外延层内执行体区注入操作和体区退火操作,以制作形成P型的体区13。具体的,体区注入操作注入的元素优选为硼,注入的能量优选为60KEV-120Kev,注入的剂量根据可VTH参数的需求调整,通常在5E12-1.8E13左右。体区退火操作的退火温度优选为1100℃,退火时间优选为60min。在体区退火过程中可以通入一定量的氧气,以在外延层的表面形成一层氧化层,也可以采用双注入提高体区13掺杂浓度的均匀性。

并在体区13的上端执行源区光刻、源区注入操作和源区退火操作,以制作形成N型的源区14。具体的,源区注入操作注入的元素优选为砷,注入的能量优选为60KeV。源区退火操作的退火温度优选为950℃,退火时间优选为60min。

参见图10,在外延层的上侧淀积介质层15,并在介质层15和外延层上刻蚀形成连接孔16。还可对连接孔16进行孔注入操作和孔退火操作,以降低接触电阻,孔注入操作注入的元素优选为硼和二氧化硼,注入的剂量优选为2E14-5E14,注入的能量优选为30-40KeV,孔退火操作的退火温度优选为950℃,退火时间优选为30s。还可进行Ti/TiN层淀积和钨金属填充回刻,形成欧姆接触孔。

参见图11,在介质层15的上侧及连接孔16内沉积金属层,金属层经刻蚀形成源极金属17和栅极金属。金属层优选为铝层,铝中可掺杂一定比例的SiCu防止铝硅互溶,厚度优选4um。

还可在器件的上侧沉积钝化层,钝化层优选为氮化硅钝化层,其厚度优选为7000-12000埃。然后经过钝化层光刻、腐蚀形成Gate和Source的开口区,可降低芯片表面可动离子引起的器件漏电。还可以从衬底1的下侧减薄至剩余厚度为150um左右,在衬底1的下侧蒸发形成背金层18,背金层18优选为Ti-Ni-Ag(钛-镍-银)层。

假设沟槽6的深度为d,本发明实施例的第一外延层2的厚度优选为沟槽6深度的三分之二,即2d/3。第二外延层3的厚度优选为沟槽6深度的六分之一,即1d/6。第三外延层4的厚度优选为沟槽6深度的四分之一,即1d/4。第四外延层5的厚度优选为沟槽6深度的二分之一,即1d/2。

结合图2至11,基于以上实施例,本领域技术人员可以轻易理解,本发明还提供了一种优化电场特性的分裂栅沟槽MOS,包括第一导电类型的衬底1,在衬底1上侧的外延层。具体的,外延层包括依次设置在衬底1上侧的第一外延层2、第二外延层3、第三外延层4和第四外延层5,第一外延层2的掺杂浓度为N3,N3的取值优选为2E16-3E16。第二外延层3的掺杂浓度从N3至N2线性增加,N2取值优选为7E16-1E17。第三外延层4的掺杂浓度为从N2至N1线性降低,N1与N3相同或接近,优选的,(1+10%)*N1≥N3≥N1。第四外延层的掺杂浓度为N1。在外延层上刻蚀形成有若干沟槽6,沟槽6内生长有第一氧化层7,在第一氧化层7的内侧制作形成有屏蔽栅8,屏蔽栅8的上侧淀积形成有隔离氧化层9,在隔离氧化层9的上侧制作形成有多晶硅栅11,多晶硅栅11与外延层之间设有栅氧化层10,在多晶硅栅11的上侧生长有第二氧化层12,栅氧化层10四周的外延层内制作形成有第二导电类型的体区13,体区13的上端制作形成有第一导电类型的源区14,在外延层的上侧淀积有介质层15,介质层15和外延层上刻蚀形成有连接孔16,介质层15的上侧及连接孔16内沉积金属层,金属层经刻蚀形成源极金属17和栅极金属。

还可在器件的上侧沉积钝化层,钝化层优选为氮化硅钝化层,其厚度优选为7000-12000埃。然后经过钝化层光刻、腐蚀形成Gate和Source的开口区,可降低芯片表面可动离子引起的器件漏电。还可以从衬底1的下侧减薄至剩余厚度为150um左右,在衬底1的下侧蒸发形成背金层18,背金层18优选为Ti-Ni-Ag(钛-镍-银)层。

本发明实施例的第一外延层2的厚度优选为沟槽6深度的三分之二,第二外延层3的厚度优选为沟槽6深度的六分之一,第三外延层4的厚度优选为沟槽6深度的四分之一,第四外延层5的厚度优选为沟槽6深度的二分之一。

参见图12,本发明实施例的分裂栅沟槽MOSFET结构与传统SGT MOSFET结构电力线分布对比,本发明实施例的MOSFET结构中间部位电力线较为密集,原因是中间部位的电荷补偿能力增强,电场强度提高。参见图13和图14,本发明实施例的优化电场分布的分裂栅沟槽MOSFET结构与传统SGT MOSFET结构掺杂浓度对比,传统SGT MOSFET结构在不包括衬底反扩的位置,掺杂浓度没有变化。而本发明实施例的外延层掺杂浓度存在峰值,使屏蔽栅能够拥有更好的的电荷平衡作用。

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,其它未具体描述的部分,属于现有技术或公知常识。在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

- 一种优化电场特性的分裂栅沟槽MOS及其制造方法

- 一种可提高沟槽栅MOS器件性能的沟槽栅及其制造方法