基于光电存算单元的神经网络加速系统及其方法

文献发布时间:2023-06-19 18:29:06

技术领域

本发明基于光电存算单元提供一种多功能、兼容性好、低功耗的神经网络加速系统,能够实现光电存算单元的复位、光输入、激励输入、读出和处理操作,解决了光电存算单元的系统级部署问题。

背景技术

针对感知系统的实时探测以及实时分类识别等应用中快速实时处理系统运算能力弱、体积大、功耗高的瓶颈问题,因此需要一种全新的计算架构实现运算能力高、体积小、功耗低等特点,以便于在各类终端上进行部署。存算一体技术成功克服了传统冯诺依曼架构下存储单元和计算单元分离导致的数据搬运功耗问题,光电计算单元作为一种典型的存算一体技术(如专利号ZL 201811398206.9),相对于其他存算一体技术方案具有工艺兼容性好,利于超大规模集成,单器件存储位宽高等优势,但由于其采用了模拟域计算,光电存算单元在实际应用中容易产生功能单一、读出电路复杂、配置繁琐等问题。

发明内容

鉴于现有的光电计算单元系统在神经网络加速算法中出现的上述技术问题,本发明提供一种多功能、兼容性好、低功耗的基于光电存算单元的神经网络加速系统及其方法,能够实现光电存算单元的复位、光输入、激励输入、读出和处理操作,解决了光电存算单元的系统级部署问题。

本发明系统采用的技术方案如下:

基于光电存算单元的神经网络加速系统,包括:

光电存算单元阵列模块,由多个光电存算单元组成,在计算模式下用于对输入信号进行处理,在光输入和擦除模式下用于对光电存算单元进行权值写入,并实现非易失存储;

阵列驱动模块,包括输入控制电路和高压驱动电路;所述输入控制电路,用于控制高压驱动电路的工作状态;所述高压驱动电路,与光电存算单元阵列模块的各端口相连接,用于提供不同工作模式下需要的各种高压;

光输入模块,包括发光单元阵列、辅助光学元件、感光电路和编程校准电路;所述发光单元阵列,用于提供编程模式所需的光信号;所述辅助光学元件,用于辅助实现发光单元阵列和光电存算单元阵列模块的光学耦合关系;所述感光电路,用于收集发光单元阵列的光信号;所述编程校准电路,用于对编程过的光电存算单元进行读出并与期望值编程值进行比较,完成校准功能;

读出模块,包括钳位电路和格式转换电路;所述钳位电路,用于提供计算模式中光电存算单元阵列模块需要的计算电压;所述格式转换电路,用于将光电存算单元的电流信号转换为后级电路可以识别并处理的数据形式;

处理模块,包括非理想因素矫正电路、移位累加电路、非线性激活函数电路、负数产生电路和池化电路;所述非理想因素矫正电路,用于对温漂现象和电流偏移现象进行补偿;所述移位累加电路,用于实现移位累加操作;所述非线性激活函数电路,用于实现激活操作;所述负数产生电路,用于将负数权值或者负数输入转换为光电存算单元阵列中实现的正数进行处理;所述池化电路,用于实现池化操作;

所述光电存算单元阵列模块与阵列驱动模块和读出模块相连接,所述阵列驱动模块设置在光电存算单元阵列模块之前,所述读出模块设置在光电存算单元阵列模块之后,所述处理模块设置在阵列驱动模块和光电存算单元阵列模块之间,或者设置在读出模块和光电存算单元阵列模块之间。

进一步地,所述阵列驱动模块的激励信号输入方式是按比特位进行的数字输入,或者是使用脉冲宽度调制进行时间维度上的调控或给模拟电压信号。

进一步地,所述钳位电路包括能实现负反馈的电路结构放大器。

进一步地,所述格式转换电路中,包括由放大器和电阻构成的跨阻放大器或者由放大器和电容构成的电容跨阻放大器,以实现电流电压的转换;还包括采用逐次逼近型模数转换器、单斜率模数转换器或者它们混合的拓扑结构,以实现模拟信号和数字信号的转换。

进一步地,所述非理想因素校准电路通过查表法改变加载在光电存算单元阵列模块上的计算电压实现补偿,或者通过引入参考列进行电流对减。

进一步地,所述移位累加电路通过按权值分布的不同容值的电容实现电荷共享。

进一步地,所述非线性激活函数电路通过比较器实现激活功能。

进一步地,所述负数产生电路通过在模拟域实现电流对减来实现负数到正数的转换。

进一步地,所述池化电路通过多输入比较器来实现最大池化。

本发明还提供一种利用上述神经网络加速系统的工作方法,该方法包括如下步骤:

(1)复位:通过阵列驱动模块将光电存算单元的权值复位到初始值;

(2)光输入:通过光输入模块和阵列驱动模块将光电存算单元的权值编程到期望值;

(3)激励输入:通过阵列驱动模块将待处理信号加载到光电存算单元阵列模块中,使光电存算单元产生电流响应;

(4)读出:通过读出模块将光电存算单元产生的电流信号读出并转换为后级电路可以识别并处理的数据形式;

(5)处理:通过处理模块对读出模块输出的信号进行处理,或者在激励输入之前就对激励输入信号进行处理。

本发明的神经网络加速系统在光电存算单元阵列的基础上提出了配合阵列工作的其他辅助模块,使得阵列在复杂的工作环境下能够高效工作。由于光电存算单元需要实现准确的光输入,使用光电混合控制的方式可以使得光输入更加精确。在激励输入完成后,处理模块可以配合读出模块完成高效率读出,通过非理想因素矫正、移位累加、非线性激活等操作使得神经网络加速系统兼容性更好、功耗更低。

附图说明

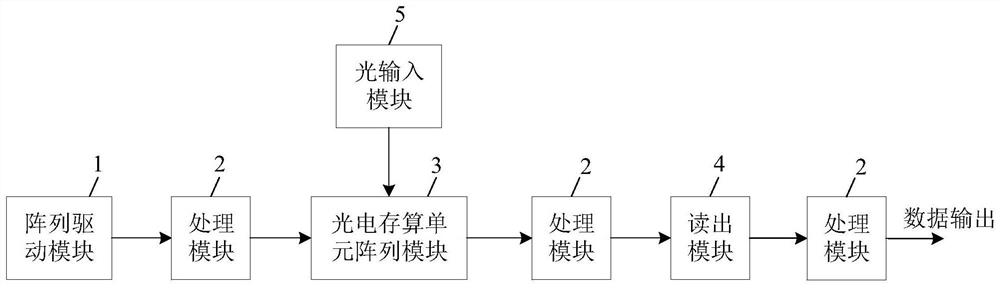

图1为本发明基于光电存算单元的神经网络加速系统的结构框图;

图2为阵列驱动模块与光电存算单元阵列模块的耦合示意图;

图3为阵列驱动模块的一种电路示意图;

图4为光输入模块与光电存算单元阵列模块的耦合示意图;

图5为读出模块与光电存算单元阵列模块的耦合示意图;

图6为读出模块的一种电路示意图。

具体实施方式

图1为本实施例一种基于光电存算单元的神经网络加速系统的结构框图,该神经网络加速系统包括:

阵列驱动模块1,包括输入控制电路和高压驱动电路,所述输入控制电路,用于控制高压驱动电路的工作状态,所述高压驱动电路,与光电存算单元阵列的各端口相连接,用于提供不同工作模式下需要的各种高压,并且可以精确控制高压持续时间;

处理模块2,包括非理想因素矫正电路、移位累加电路、非线性激活函数电路、负数产生电路和池化电路,所述非理想因素矫正电路,用于对器件温漂现象和金属线分压导致的电流偏移现象进行补偿,保证计算结果的精确性,所述移位累加电路,用于实现移位累加操作,所述非线性激活函数电路,用于实现激活操作,所述负数产生电路,用于将算法中需要的负数权值或者负数输入转换为光电存算单元阵列中容易实现的正数进行处理,所述池化电路,用于实现池化操作;

光电存算单元阵列模块3,由多个光电存算单元组成,在计算模式下可以对输入信号进行处理,在光输入和擦除模式下可以对光电存算单元进行权值写入,并实现非易失存储;

读出模块4,包括钳位电路和格式转换电路,所述钳位电路,用于提供计算模式中光电存算单元阵列需要的计算电压,所述格式转换电路,用于将光电存算单元的电流信号转换为后级电路可以识别并处理的数据形式;

光输入模块5,包括发光单元阵列、辅助光学元件、感光电路和编程校准电路,所述发光单元阵列,用于提供编程模式所需的光信号,所述辅助光学元件,用于辅助实现发光单元阵列和光电存算一体阵列的光学耦合关系,所述感光电路,用于收集发光单元阵列的光信号,便于系统对发光单元阵列进行调控,所述编程校准电路,用于对编程过的光电存算单元进行读出并与期望值编程值进行比较,完成校准功能。

其中,光电存算单元的权值可调,相当于每个光电存算单元中存储一个可变的模拟权重数据,光电存算单元阵列可以映射一个模拟权重矩阵,当光电存算单元受到激励后,就会感应出电流,电流大小等于激励乘以权值,再通过阵列间单元的耦合关系,可以实现同行或者同列电流的汇聚,进而可以利用光电存算单元阵列完成各种运算。

本发明提供的神经网络加速系统,通过阵列驱动模块1来接收外部控制信号,完成不同模式选择,在光输入模式,通过外部控制将每个光电存算单元输入到期望输入权值,在复位模式,通过外部控制将每个光电存算单元擦除到期望擦除权值,在计算模式,通过外部控制将激励信号送到阵列中。

本发明提供的神经网络加速系统,还通过光输入模块5配合阵列驱动模块完成光输入操作,权重数据可以反应在电信号上也可以反应在光信号上,或者是电信号和光信号的共同控制。

本发明提供的神经网络加速系统,还通过读出模块4配合阵列驱动模块完成计算操作,可以是阵列驱动模块提供计算电压,也可以是读出模块提供计算电压。

本发明提供的神经网络加速系统,还通过处理模块2配合读出模块和阵列驱动模块完成计算操作,处理模块2可以在阵列驱动模块1和光电存算单元阵列模块3之间,也可以在读出模块4和光电存算单元阵列模块3之间。

图2为阵列驱动模块1与光电存算单元阵列模块3的耦合示意图,包括光电存算单元阵列模块3,大小为M行N列,字线WL驱动电路201、位线BL驱动电路202和源线SL驱动电路203组成阵列驱动模块1,光电存算单元阵列的每条WL、BL和SL都配置一个独立的驱动电路,也可以通过开关实现驱动电路和阵列的复用关系,节省驱动电路面积。BL驱动电路和SL驱动电路的地位相同,其功能可以互相替换,并且BL和SL的方向不仅可以是图示的平行关系,也可以是垂直关系。激励信号可以从任意一端的驱动电路输入,激励输入方式可以是按比特位进行的数字输入,也可以是使用脉冲宽度调制进行时间维度上的调控或给模拟电压信号,下面以从WL驱动电路进行激励输入进行实施例说明。

图3为阵列驱动模块的一种电路示意图,WL驱动电路201由数字寄存器301和电平移位电路302组成,激励信号通过外部控制器输入数字寄存器,电平移位电路将数字信号的逻辑转换为操作光电存算单元阵列模块的高压信号,若需要输入多位激励信号,可以分时逐位输入,达到多位激励输入的效果。将电平移位电路302替换为PWM产生电路和DAC电路都可以实现激励信号输入。

图4为光输入模块与光电存算单元阵列模块的耦合示意图,发光阵列401提供光电存算单元阵列模块光输入需要的光信号,可以通过直接投影或者借助镜头实现光输入,根据权重配置不同位置的光强,实现光电存算单元的权值写入操作,光输入控制装置402提供发光阵列的控制信号,实现权值的自动写入与校准功能。

图5为读出模块与光电存算单元阵列模块的耦合示意图,钳位电路501和格式转换电路502组成读出模块,其中计算模式所需的计算电压由钳位电路501提供,光电存算单元阵列产生的电流激励由格式转换电路转换后送至后级模块进行处理。

图6为读出模块的一种电路示意图,钳位电路501采用运放和MOS管组成,得到光电存算单元阵列的电流后通过电流镜拷贝至电流电压(IV)转换电路601,转换成电压信号后再通过数模转换(ADC)602进行量化处理,钳位电路501也可以使用各种能够实现负反馈的结构进行实现,如果ADC602是电流输入型,IV转换电路601可以省略。钳位电路501和IV转换电路601也可以集成在同一个模块中,实现面积和功耗的最优化。

如图1所示,处理模块2可以位于阵列驱动模块1和光电存算单元阵列模块3之间,位于该位置的处理模块2是非理想因素矫正电路,在计算模式下可以通过调整计算电压来补偿温度变化和电阻分压(IR drop)导致的电流偏移,使得计算结果更加精确,温漂模型和IR drop模型均可以通过实测数据拟合得到。处理模块2也可以位于光电存算单元阵列模块3和读出模块4之间,位于该位置的处理模块2是非理想因素矫正电路,位于该位置的处理模块2是移位累加电路、非线性激活函数电路、负数产生电路、池化电路或者是其中几个的组合,移位累加电路用于实现加权累加操作,非线性激活函数电路用于实现激活函数功能,负数产生电路用于实现算法中需要的负权值或者负激励,使得算法通用性更强,池化电路用于实现池化功能。处理模块2也可以位于读出模块4之后,位于该位置的处理模块2可以是所述累加电路、非线性激活函数电路、负数产生电路、池化电路或者后续算法中所需的必要处理电路。

本实施例提供一种基于光电存算单元的神经网络加速系统的工作方法:

(1)复位:通过阵列驱动模块1将光电存算单元阵列3的权值复位到初始值,所有WL加-9V的电压,所有BL加5V的电压,所有SL加5V的电压,衬底加5V的电压,持续若干秒后,全部光电存算单元的权值复位到初始值;

(2)光输入:通过光输入模块5和阵列驱动模块1将光电存算单元阵列3的权值编程到期望值,选中的WL加5.5V的电压,非选中的WL加0V的电压,选中的BL加0V的电压,非选中的BL加-2V的电压,选中的SL加0V的电压,非选中的SL加-2V的电压,衬底加-2V的电压,同时控制发光单元阵列投射均匀光,通过控制每个光电存算单元的光输入时间来进行权值写入;

(3)激励输入:通过阵列驱动模块1将待处理信号加载到光电存算单元阵列3中,选中的WL加3.2V的电压,非选中的WL加0V的电压,光电存算单元阵列3根据激励输入信号和对应光电存算单元的权值产生电流响应,采用分时逐位数字输入的方法,完成总位宽为8bit的激励信号输入;

(4)读出:通过读出模块4将光电存算单元阵列3产生电流信号读出并转换为后级电路可以识别并处理的数据形式,钳位电压为0.2V,也采用分时逐位读出的方法;

(5)处理:通过处理模块2对读出模块4分时输出的信号进行移位累加处理,得到最后的计算结果。

- 基于忆阻器的存算一体存算单元和存算阵列

- 基于忆阻器的多比特存算一体存算单元及控制方法