脉冲产生电路及多量子比特控制系统

文献发布时间:2023-06-19 18:30:43

技术领域

本发明涉及超导电路设计技术领域,特别是涉及一种脉冲产生电路及多量子比特控制系统。

背景技术

室温微波源是目前对量子比特进行控制的主要器件,如任意波形发生器等;这些外部的微波源输入到量子比特需要大量的硬件消耗,如滤波器、混频器、衰减器、隔离器、环形器等,也正是这些硬件消耗限制了量子比特个数的扩展。

在有限的量子比特个数下,量子计算机对于传统计算机的优越性还无法完美体现。超导量子电路因其工作温度低、能耗低、噪声小、以及制备工艺与传统集成电路工艺兼容等特点,是目前最具希望实现通用量子计算的方案之一。现有的SFQ(超导单磁通量子)电路控制量子比特的方式,主要是通过产生序列脉冲实现,而这种方法还是需要通过输入相应的微波源信号将其转化为脉冲信号才可以对量子比特进行控制,本质上没有脱离对硬件消耗的依赖。

发明内容

鉴于以上所述现有技术的缺点,本发明的目的在于提供一种脉冲产生电路及多量子比特控制系统,用于解决现有量子比特控制方式存在硬件消耗大的问题。

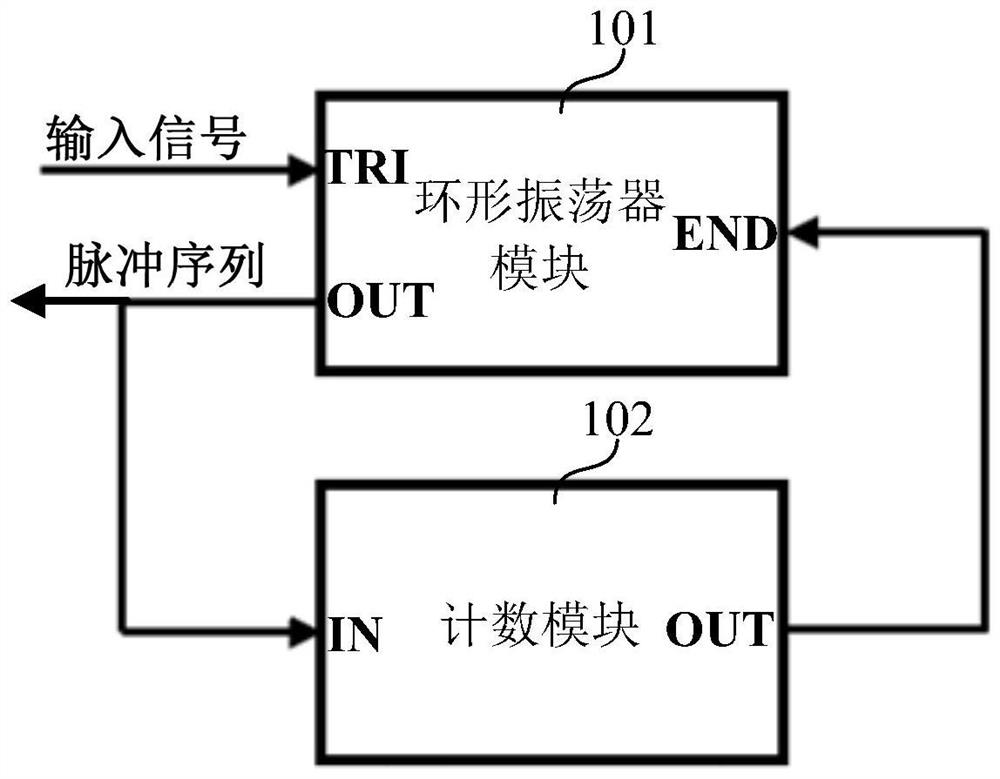

为实现上述目的及其他相关目的,本发明提供一种脉冲产生电路,所述脉冲产生电路包括:环形振荡器模块及计数模块;

所述环形振荡器模块用于在输入信号的作用下产生脉冲序列输出,并在终止信号的作用下停止所述脉冲序列输出;

所述计数模块连接所述环形振荡器模块的输出端,用于对所述脉冲序列的个数进行计数,并在计数值达到设定值时产生所述终止信号。

可选地,所述环形振荡器模块包括:非破坏性读出单元、第一汇流缓冲单元、第一分流单元及第二分流单元;

所述第一分流单元的输入端连接所述输入信号,第一输出端连接所述第一汇流缓冲单元的第一输入端,第二输出端连接所述非破坏性读出单元的置位端;所述第一汇流缓冲单元的第二输入端连接所述第二分流单元的第一输出端,输出端连接所述非破坏性读出单元的时钟端;所述非破坏性读出单元的复位端连接所述计数模块的输出端,输出端连接所述第二分流单元的输入端;所述第二分流单元的第二输出端作为所述环形振荡器模块的输出端。

可选地,所述环形振荡器模块包括:非门单元、第二汇流缓冲单元及第三分流单元;

所述第二汇流缓冲单元的第一输入端连接所述输入信号,第二输入端连接所述第三分流单元的第一输出端,输出端连接所述非门单元的时钟端;所述非门单元的输入端连接所述计数模块的输出端,输出端连接所述第三分流单元的输入端;所述第三分流单元的第二输出端作为所述环形振荡器模块的输出端。

可选地,所述环形振荡器模块包括:异或门单元、第三汇流缓冲单元、第四分流单元及第五分流单元;

所述异或门单元的第一输入端连接所述计数模块的输出端,第二输入端连接所述第四分流单元的第一输出端,时钟端连接所述第四分流单元的第二输出端,输出端连接所述第五分流单元的输入端;所述第四分流单元的输入端连接所述第三汇流缓冲单元的输出端;所述第三汇流缓冲单元的第一输入端连接所述输入信号,第二输入端连接所述第五分流单元的第一输出端;所述第五分流单元的第二输出端作为所述环形振荡器模块的输出端。

可选地,所述环形振荡器模块包括:约瑟夫森结及输出级;

所述约瑟夫森结的第一端连接所述输入信号,第二端接地,用于在所述输入信号的作用下产生脉冲序列;

所述输出级连接所述约瑟夫森结的第一端及所述计数模块的输出端,用于将所述约瑟夫森结产生的所述脉冲序列输出,并在所述终止信号的作用下停止所述脉冲序列输出。

可选地,所述计数模块包括:M个T触发器单元及M个第四汇流缓冲单元,二者间隔设置;

M个所述第四汇流缓冲单元的第一输入端对应连接M位预设码值,M个所述第四汇流缓冲单元通过第二输入端与M个所述T触发器单元级联,第一个所述第四汇流缓冲单元的第二输入端连接所述环形振荡器模块的输出端,第M个所述T触发器单元的输出端作为所述计数模块的输出端;其中,M为大于等于1的正数。

可选地,所述计数模块包括:N个D触发器单元;

N个所述D触发器单元级联,N个所述D触发器单元的时钟端均连接第一个所述D触发器单元的输入端并连接所述环形振荡器模块的输出端,第N个所述D触发器单元的输出端作为所述计数模块的输出端;其中,N为大于等于1的正数。

本发明还提供一种多量子比特控制系统,所述多量子比特控制系统包括:K个如上所述的脉冲产生电路,K个所述脉冲产生电路并行设置,其中,K为大于等于2的正数。

可选地,所述多量子比特控制系统还包括:译码器电路,用于对输入进行译码操作并产生K个输出,以对应输入至K个所述脉冲产生电路。

可选地,所述多量子比特控制系统还包括:开关控制电路,包括K个控制开关,对应连接于所述译码器电路的K个输出端和K个所述脉冲产生电路的输入端之间。

可选地,K个所述脉冲产生电路的各所述计数模块中,若至少有两个通过预设码值来调节设定值,且其中至少有两个具有相同的设定值,则所述多量子比特控制系统还包括:分流电路,用于将一组预设码值分流成至少两组输入至相应所述计数模块中。

如上所述,本发明的脉冲产生电路及多量子比特控制系统,通过环形振荡器模块和计数模块的设计,仅需输入低频信号即可输出脉冲序列以实现对量子比特的控制,无需高频信号的输入,避免了高频线缆带来的硬件消耗,使得量子位数的扩展不再受限于制冷机对于线缆空间的限制,可以很便捷地对量子位数进行扩展控制;而且,本发明电路结构相对简单,功耗低,可以和量子比特集成控制,更符合对量子比特控制的低功耗需求。

附图说明

图1显示为非破坏性读出单元的端口说明示意图。

图2显示为非破坏性读出单元的状态转换示意图。

图3显示为汇流缓冲单元的端口说明示意图。

图4显示为汇流缓冲单元的状态转换示意图。

图5显示为分流单元的端口说明示意图。

图6显示为分流单元的状态转换示意图。

图7显示为非门单元的端口说明示意图。

图8显示为非门单元的状态转换示意图。

图9显示为异或门单元的端口说明示意图。

图10显示为异或门单元的状态转换示意图。

图11显示为T触发器单元的端口说明示意图。

图12显示为T触发器单元的状态转换示意图。

图13显示为D触发器单元的端口说明示意图。

图14显示为D触发器单元的状态转换示意图。

图15显示为本发明脉冲产生电路的示意图。

图16显示为本发明环形振荡器模块的第一种电路示意图。

图17显示为图16所示环形振荡器模块输出脉冲序列的频率随偏置电流变化的示意图。

图18显示为本发明环形振荡器模块的第二种电路示意图。

图19显示为本发明环形振荡器模块的第三种电路示意图。

图20显示为本发明环形振荡器模块的第四种电路示意图。

图21显示为本发明计数模块的第一种电路示意图。

图22显示为本发明计数模块的第二种电路示意图。

图23显示为本发明多量子比特控制系统的示意图。

元件标号说明

100 脉冲产生电路

101 环形振荡器模块

101a 输出级

102 计数模块

200 译码器电路

300 开关控制电路

400 分流电路

具体实施方式

以下通过特定的具体实例说明本发明的实施方式,本领域技术人员可由本说明书所揭露的内容轻易地了解本发明的其他优点与功效。本发明还可以通过另外不同的具体实施方式加以实施或应用,本说明书中的各项细节也可以基于不同观点与应用,在没有背离本发明的精神下进行各种修饰或改变。

请参阅图1至图23。需要说明的是,本实施例中所提供的图示仅以示意方式说明本发明的基本构想,虽图示中仅显示与本发明中有关的组件而非按照实际实施时的组件数目、形状及尺寸绘制,其实际实施时各组件的形态、数量及比例可为一种随意的改变,且其组件布局形态也可能更为复杂。

实施例一

为了更好地理解技术方案,在介绍本实施例方案之前,先简单介绍下本实施例方案中涉及到的一些超导单元器件。具体如下:

如图1和图2所示,非破坏性读出单元NDRO的功能是:通过RI端和SI端的输入控制单元电路的状态,最终实现对输出的控制。无论当前单元电路处于“0”态还是“1”态,当SI端有信号输入时,单元电路的状态都会转换到“1”态,而当RI端有信号输入时,单元电路的状态都会转换到“0”态;当单元电路处于“0”态时,若TI端有信号输入,TO端不产生输出(输出逻辑“0”),当单元电路处于“1”态时,若TI端有信号输入,则TO端产生输出;其中,TO端的输出不影响单元电路的状态,所以此单元电路具有非破坏性读出的特性。

如图3和图4所示,汇流缓冲单元CB的功能是:无论AI端还是BI端有信号输入,都会使单元电路在ABO端输出一个信号,而没有状态的改变,单元电路的状态始终为“0”态,实现逻辑“或”的功能。

如图5和图6所示,分流单元SPL的功能是:将AI端的输入分流成AO1端和AO2端的两路输出,其中,AO1端和AO2端的输出与AI端的输入完全相同。

如图7和图8所示,非门单元NOT的功能是:通过TI端的输入读取单元电路状态的“非”态。当AI端无信号输入时,单元电路的初始态为“0”态,当AI端有信号输入时,单元电路的状态由“0”态翻转为“1”态;TI端有信号输入时,若单元电路的状态为“0”态,则AO端产生输出,若单元电路的状态为“1”态,则AO端不产生输出,且单元电路的状态转换为“0”态。

如图9和图10所示,异或门单元XOR的功能是:通过TI端的输入读取AI端和BI端输入的异或状态。若AI端和BI端都没有信号输入,单元电路的状态为“00”态,若AI端和BI端都有信号输入,单元电路的状态为“11”态,但该状态为不稳定状态,会马上转变为“00”态,此时若TI端有信号输入,TO端不产生输出,单元电路保持“00”态;若AI端有信号输入、BI端无信号输入,或AI端无信号输入、而BI端有信号输入,也就是单元电路的状态为“10”态或“01”态,此时若TI端有信号输入,TO端则产生输出,且单元电路的状态转换为“00”态。

如图11和图12所示,T触发器单元TFF的功能是:AI端每输入一个信号,单元电路的状态就翻转一次,输入第一个信号使单元电路的状态由“0”态翻转为“1”态,AO端无输出;输入第二个信号则使单元电路的状态由“1”态翻转为“0”态,AO端产生输出,由此实现二进制的计数。

如图13和图14所示,D触发器单元DFF的功能是:AI端有信号输入时,单元电路的状态从“0”态翻转为“1”态;当单元电路处于“0”态时,若TI端有信号输入,TO端不产生输出(输出逻辑“0”);当单元电路处于“1”态时,若TI端有信号输入,则TO端产生输出,且单元电路的状态转换为“0”,所以此单元电路具有破坏性读出的特性。

其中,非破坏性读出单元NDRO、汇流缓冲单元CB、分流单元SPL、非门单元NOT、异或门单元XOR、T触发器单元TFF及D触发器单元DFF均为超导领域现有的单元器件,以上仅简单介绍下各自的功能,对具体电路构成就不再具体介绍;但本领域技术人员应该了解,超导单元器件都是由约瑟夫森结和电感构成,约瑟夫森结和电感的数量和/或排列不同,最终构成的单元电路的功能也不同。

如图15所示,本实施例提供一种脉冲产生电路100,该脉冲产生电路100包括:环形振荡器模块101及计数模块102。

环形振荡器模块101用于在输入信号的作用下产生脉冲序列输出,并在终止信号的作用下停止脉冲序列输出。利用环形振荡器模块101产生脉冲序列时,仅需输入低频信号即可产生脉冲序列输出,无需高频信号的输入,因此,避免了高频线缆带来的诸多硬件消耗。

在一种可能的实施方式中,如图16所示,环形振荡器模块101包括:非破坏性读出单元NDRO、第一汇流缓冲单元CB1、第一分流单元SPL1及第二分流单元SPL2;第一分流单元SPL1的输入端AI连接输入信号,第一输出端AO1连接第一汇流缓冲单元CB1的第一输入端AI,第二输出端AO2连接非破坏性读出单元NDRO的置位端SI;第一汇流缓冲单元CB1的第二输入端BI连接第二分流单元SPL2的第一输出端AO1,输出端ABO连接非破坏性读出单元NDRO的时钟端TI;非破坏性读出单元NDRO的复位端RI连接计数模块102的输出端,输出端TO连接第二分流单元SPL2的输入端AI;第二分流单元SPL2的第二输出端AO2作为环形振荡器模块101的输出端。

本实施方式中,采用输入信号(如低频直流脉冲)作为非破坏性读出单元NDRO中置位端SI和时钟端TI的输入,使得非破坏性读出单元NDRO能够产生脉冲输出(即,非破坏性读出单元NDRO的SI端有信号输入,单元电路的状态为“1”态,此时,TI端有信号输入,则TO端产生输出);再经由第二分流单元SPL2和第一汇流缓冲单元CB1形成一个反馈回路,使得非破坏性读出单元NDRO能够不断地产生新的脉冲输出,由此输出脉冲序列。而采用终止信号作为非破坏性读出单元NDRO中复位端RI的输入,使得非破坏性读出单元NDRO的状态被重置,不再产生新的脉冲输出(即,非破坏性读出单元NDRO的RI端有信号输入,单元电路的状态为“0”态,此时,TI端有信号输入,则TO端不产生输出,停止输出新的脉冲)。

其中,输出脉冲序列的频率由反馈回路中第二分流单元SPL2和第一汇流缓冲单元CB1之间的传输线JTL(即第二分流单元SPL2的第一输出端AO1和第一汇流缓冲单元CB1的第二输入端BI之间的传输线JTL)的总延时决定,而该总延时则可通过调节施加至该传输线JTL上的偏置电流来调节,从而实现调节输出脉冲序列的频率;也即,通过调节第二分流单元SPL2的第一输出端AO1和第一汇流缓冲单元CB1的第二输入端BI之间传输线JTL的偏置电流,来调节环形振荡器模块101输出脉冲序列的频率。

对于超导电路而言,各单元器件之间的电连接是采用传输线JTL实现,实际上,传输线JTL是由约瑟夫森结构成,其传输功能即是通过对约瑟夫森结施加偏置电流来实现,但施加偏置电流的大小会影响传输的延时。针对本实施方式的环形振荡器模块101,施加至反馈回路中相应传输线JTL的偏置电流的大小会直接影响环形振荡器模块101输出脉冲序列的频率,具体如图17所示;横坐标XI表示的是针对偏置电流的变化倍数,纵坐标表示的是环形振荡器模块101输出脉冲序列的频率,在标准电流值下,即XI=1的情况下,环形振荡器模块101输出脉冲序列的频率约为5GHz,在电流变化为原来的1.2倍时,即XI=1.2的情况下,环形振荡器模块101输出脉冲序列的频率约为6.5GHz。

在另一种可能的实施方式中,如图18所示,环形振荡器模块101包括:非门单元NOT、第二汇流缓冲单元CB2及第三分流单元SPL3;第二汇流缓冲单元CB2的第一输入端AI连接输入信号,第二输入端BI连接第三分流单元SPL3的第一输出端AO1,输出端ABO连接非门单元NOT的时钟端TI;非门单元NOT的输入端AI连接计数模块102的输出端,输出端AO连接第三分流单元SPL3的输入端AI;第三分流单元SPL3的第二输出端AO2作为环形振荡器模块101的输出端。

本实施方式中,采用输入信号(如低频直流脉冲)作为非门单元NOT中时钟端TI的输入,使得非门单元NOT能够产生脉冲输出(即,非门单元NOT的AI端无信号输入,单元电路的状态为“0”态,此时,TI端有信号输入,则AO端产生输出);再经由第三分流单元SPL3和第二汇流缓冲单元CB2形成一个反馈回路,使得非门单元NOT能够不断地产生新的脉冲输出,由此输出脉冲序列。而采用终止信号作为非门单元NOT中输入端AI的输入,使得非门单元NOT无输出,不再产生新的脉冲输出(即,非门单元NOT的AI端有信号输入,单元电路的状态由“0”态翻转为“1”态,此时,TI端有信号输入,则AO端不产生输出,停止输出新的脉冲)。

其中,输出脉冲序列的频率由反馈回路中第三分流单元SPL3和第二汇流缓冲单元CB2之间的传输线JTL(即第三分流单元SPL3的第一输出端AO1和第二汇流缓冲单元CB2的第二输入端BI之间的传输线JTL)的总延时决定,而该总延时则可通过调节施加至该传输线JTL上的偏置电流来调节,从而实现调节输出脉冲序列的频率;也即,通过调节第三分流单元SPL3的第一输出端AO1和第二汇流缓冲单元CB2的第二输入端BI之间传输线JTL的偏置电流,来调节环形振荡器模块101输出脉冲序列的频率。

在第三种可能的实施方式中,如图19所示,环形振荡器模块101包括:异或门单元XOR、第三汇流缓冲单元CB3、第四分流单元SPL4及第五分流单元SPL5;异或门单元XOR的第一输入端AI连接计数模块102的输出端,第二输入端BI连接第四分流单元SPL4的第一输出端AO1,时钟端TI连接第四分流单元SPL4的第二输出端AO2,输出端TO连接第五分流单元SPL5的输入端AI;第四分流单元SPL4的输入端AI连接第三汇流缓冲单元CB3的输出端ABO;第三汇流缓冲单元CB3的第一输入端AI连接输入信号,第二输入端BI连接第五分流单元SPL5的第一输出端AO1;第五分流单元SPL5的第二输出端AO2作为环形振荡器模块101的输出端。

本实施方式中,采用输入信号(如低频直流脉冲)作为异或门单元XOR中时钟端TI和第二输入端BI的输入,使得异或门单元XOR能够产生脉冲输出(即,异或门单元XOR的AI端无信号输入、BI端有信号输入,单元电路的状态为“01”态,此时,TI端有信号输入,则TO端产生输出);再经由第五分流单元SPL5和第三汇流缓冲单元CB3形成一个反馈回路,使得异或门单元XOR能够不断地产生新的脉冲输出,由此输出脉冲序列。而采用终止信号作为异或门单元XOR中第一输入端AI的输入,使得异或门单元XOR无输出,不再产生新的脉冲输出(即,异或门单元XOR的AI端有信号输入、BI端有信号输入,单元电路的状态为“11”态,但该状态不稳定,会马上转变为“00”态,此时,TI端有信号输入,则TO端不产生输出,停止输出新的脉冲)。

其中,输出脉冲序列的频率由反馈回路中第五分流单元SPL5和第三汇流缓冲单元CB3之间的传输线JTL(即第五分流单元SPL5的第一输出端AO1和第三汇流缓冲单元CB3的第二输入端BI之间的传输线JTL)的总延时决定,而该总延时则可通过调节施加至该传输线JTL上的偏置电流来调节,从而实现调节输出脉冲序列的频率;也即,通过调节第五分流单元SPL5的第一输出端AO1和第三汇流缓冲单元CB3的第二输入端BI之间传输线JTL的偏置电流,来调节环形振荡器模块101输出脉冲序列的频率。

在第四种可能的实施方式中,如图20所示,环形振荡器模块101包括:约瑟夫森结J1及输出级101a;其中,约瑟夫森结J1的第一端连接输入信号,第二端接地,用于在输入信号的作用下产生脉冲序列;输出级101a连接约瑟夫森结J1的第一端和计数模块102的输出端,用于将约瑟夫森结产生的脉冲序列输出,并在终止信号的作用下停止脉冲序列输出。

其中,输出级101a可以采用非门单元NOT、非破坏性读出单元NDRO或异或门单元XOR实现;

在采用非门单元NOT实现时,非门单元NOT的时钟端TI连接约瑟夫森结J1的第一端,输入端AI连接计数模块102的输出端,输出端AO作为环形振荡器模块101的输出端;

在采用非破坏性读出单元NDRO实现时,非破坏性读出单元NDRO的时钟端TI和置位端SI连接约瑟夫森结J1的第一端,复位端RI连接计数模块102的输出端,输出端TO作为环形振荡器模块101的输出端;

在采用异或门单元XOR实现时,异或门单元XOR的时钟端TI和第二输入端BI连接约瑟夫森结J1的第一端,第一输入端AI连接计数模块102的输出端,输出端TO作为环形振荡器模块101的输出端。

本实施方式中,通过在约瑟夫森结J1上施加输入信号(如偏置电压),由于约瑟夫森交流效应,约瑟夫森结J1会输出相应频率的无限脉冲序列;通过改变输入偏置电压的值,可以改变输出脉冲序列的频率,关系式满足f=V/Φ

计数模块102连接环形振荡器模块101的输出端,用于对脉冲序列的个数进行计数,并在计数值达到设定值时产生终止信号,以此终止环形振荡器模块101输出脉冲序列。通过计数模块102的设计,避免了采用外部输入来终止环形振荡器模块101输出脉冲序列,进一步降低了对高频线缆的需求。

在一种可能的实施方式中,如图21所示,计数模块102包括:M个T触发器单元TFF及M个第四汇流缓冲单元CB4,二者间隔设置;M个第四汇流缓冲单元CB4的第一输入端AI对应连接M位预设码值set1-setm,M个第四汇流缓冲单元CB4通过第二输入端BI与M个T触发器单元TFF级联,第一个第四汇流缓冲单元CB4的第二输入端BI连接环形振荡器模块101的输出端,第M个T触发器单元TFF的输出端作为计数模块102的输出端;其中,通过调节预设码值来调节设定值,M为大于等于1的正数。

本实施方式中,T触发器单元TFF用作计数,最大计数值可达2

表1

在另一种可能的实施方式中,如图22所示,计数模块102包括:N个D触发器单元DFF;N个D触发器单元DFF级联,N个D触发器单元DFF的时钟端TI均连接第一个D触发器单元DFF的输入端AI并连接环形振荡器模块101的输出端,第N个D触发器单元DFF的输出端AO作为计数模块102的输出端;其中,通过调节D触发器单元DFF的个数来调节设定值,N为大于等于1的正数。本实施方式中,N个D触发器单元DFF构成N位移位寄存器,用于实现设定值为N的计数。

实施例二

如图23所示,本实施例提供一种多量子比特控制系统,该多量子比特控制系统包括:K个如实施例一记载的脉冲产生电路100,其中,K个脉冲产生电路100并行设置,且K为大于等于2的正数。利用并行设置的K个脉冲产生电路100分别控制一个量子比特,可实现多量子比特的控制。

实际应用中,K个脉冲产生电路100输出脉冲序列的频率可以完全相同,也可以完全不同,甚至可以部分相同;但为了避免量子比特之间的串扰问题,一般设置K个脉冲产生电路100输出脉冲序列的频率完全不同。另外,K个脉冲产生电路100输出脉冲的个数(即计数模块102的设定值)可以完全相同,也可以完全不同,甚至可以部分相同,这取决于具体应用需求,本实施例对此不做限制。

由于多量子比特控制系统包括多个脉冲产生电路100,而多个脉冲产生电路100中,各环形振荡器模块101采用非破坏性读出单元NDRO、非门单元NOT、异或门单元XOR或约瑟夫森结J1实现,对本实施例方案没有实质影响,只要能够产生设定频率的脉冲序列即可;同理,各计数模块102采用T触发器单元TFF或D触发器单元DFF实现,对本实施例方案也没有实质影响,只要能够完成设定值的计数即可,而采用T触发器单元TFF或D触发器单元DFF实现,区别仅在于是否需要接入预设码值。

在一种可能的实施方式中,该多量子比特控制系统还包括:译码器电路200,用于对输入进行译码操作并产生K个输出,以对应输入至K个脉冲产生电路100。

以K=7为例,若译码器电路200对输入进行译码操作后输出0000001,此时,第1个-第6个脉冲产生电路100因无输入而无输出,第7个脉冲产生电路100因有输入而输出脉冲序列;若译码器电路200对输入进行译码操作后输出1111111,此时,第1个-第7个脉冲产生电路均因有输入而输出脉冲序列;当然,具体哪个或哪几个脉冲产生电路100输出脉冲序列,取决于译码器电路200的输入,也即由具体需求决定,而译码器电路200基于输入按照特定译码规则进行译码操作,为本领域技术人员所公知的技术,此处就不再赘述。

进一步的,该多量子比特控制系统还包括:开关控制电路300,包括K个控制开关S1-SK,对应连接于译码器电路200的K个输出端和K个脉冲产生电路100的输入端之间。通过K个控制开关S1-SK的打开和闭合,实现K个脉冲产生电路100的分时段输出,以此实现K个量子比特的分时段控制。

当然,在该多量子比特控制系统不包括译码器电路200时,其也可以包括开关控制电路300,此时,该开关控制电路300中K个控制开关S1-SK的一端彼此相连并连接输入信号,另一端对应连接K个脉冲产生电路100的输入端。通过K个控制开关S1-SK的打开和闭合,实现K个脉冲产生电路100的分时段输出,以此实现K个量子比特的分时段控制。

在一种可能的实施方式中,对于K个脉冲产生电路100的各计数模块102而言,若至少有两个计数模块102通过预设码值来调节设定值,且其中至少有两个计数模块102具有相同的设定值,那么,该多量子比特控制系统还包括:分流电路,用于将一组预设码值分流成至少两组输入至相应计数模块102中,以此实现利用同一组预设码值来设置多个计数模块102计数的设定值,使多个计数模块102具有相同的计数设定值。

其中,分流电流400包括M个分流模块,每个分流模块对应一位预设码值,用于将该位预设码值分流成多位以施加至不同的计数模块102中;对于每个分流模块而言,又包括若干个分流单元SPL,各分流单元SPL按照二叉树排列方式连接,以实现一分二、二分四、四分八、八分十六等。

本实施例记载的多量子比特控制系统,可实现多通道量子比特的控制,通过对不同通道的脉冲产生电路100单独设计输出脉冲的个数及脉冲序列的频率,可实现对每个通道量子比特的单独控制,增加了量子比特位数扩展的灵活性和便捷性。

综上所述,本发明的一种脉冲产生电路及多量子比特控制系统,通过环形振荡器模块和计数模块的设计,仅需输入低频信号即可输出脉冲序列以实现对量子比特的控制,无需高频信号的输入,避免了高频线缆带来的硬件消耗,使得量子位数的扩展不再受限于制冷机对于线缆空间的限制,可以很便捷地对量子位数进行扩展控制;而且,本发明电路结构相对简单,功耗低,可以和量子比特集成控制,更符合对量子比特控制的低功耗需求。所以,本发明有效克服了现有技术中的种种缺点而具高度产业利用价值。

上述实施例仅例示性说明本发明的原理及其功效,而非用于限制本发明。任何熟悉此技术的人士皆可在不违背本发明的精神及范畴下,对上述实施例进行修饰或改变。因此,举凡所属技术领域中具有通常知识者在未脱离本发明所揭示的精神与技术思想下所完成的一切等效修饰或改变,仍应由本发明的权利要求所涵盖。

- 用于QUDIT和多量子比特电路的精确量子电路及电路合成

- 量子比特控制系统及波形校准电路