功率半导体器件封装结构及其制备方法

文献发布时间:2023-06-19 19:23:34

技术领域

本发明涉及功率半导体技术领域,尤其涉及一种功率半导体器件封装结构及其制备方法。

背景技术

功率半导体器件作为电能变换的核心器件,目前已经广泛应用于新能源、电动汽车、电力传输等领域。随着工业控制系统高功率密度的发展趋势,对功率半导体器件的导通电阻、散热能力、可靠性提出了更高的要求。传统的分立式功率器件封装结构由于封装内阻较大、单面散热结构,已经不能满足电力电子系统的高功率密度发展需求。此外,由于芯片尺寸的不断增大,芯片通流能力的提高必然会引起器件结温升高,传统的铝线键合互联方法所产生的热应力会导致封装结构疲劳,最终导致器件失效。

具体地,传统分立式器件封装结构主要包括金属基岛、芯片、键合线及塑封体构成。芯片通过铅锡焊料焊接在引线框架的金属基岛上,经过离子清洗后,通过铝线键合机进行芯片与引脚之间的互联,随后对器件进行塑封及引脚电镀,完成器件封装。

传统分立式器件封装结构为单面散热封装结构,散热能力不足导致器件通流能力受限。

传统分立式器件采用铝键合线进行芯片与引脚的互联,互联面积较小,导致器件封装存在着较大的寄生电阻。

传统分立式器件采用的封装形式,存在较大的封装热应力,器件封装可靠性较低。

发明内容

本发明的目的在于解决背景技术中的至少一个技术问题,提供一种功率半导体器件封装结构及其制备方法。

为实现上述目的,本发明提供一种功率半导体器件封装结构,包括:引线框架,支承在所述引线框架上的半导体芯片,支承在所述半导体芯片上的应力缓冲层,支承在所述应力缓冲层上的金属互联结构,以及将所述引线框架、所述半导体芯片、所述应力缓冲层和所述金属互联结构封装固定的塑封体;

所述金属互联结构远离所述应力缓冲层的表面与所述塑封体的一个表面位于同一水平面上,并且该表面设有第一散热区;

所述引线框架远离所述半导体芯片的表面与所述塑封体的另一个表面位于同一水平面上,并且该表面设有第二散热区。

根据本发明的一个方面,所述引线框架包括设置在其靠近所述半导体芯片的表面上的漏极焊接区,所述半导体芯片焊接在所述漏极焊接区上。

根据本发明的一个方面,所述引线框架包括栅极引脚和源极引脚,所述源极引脚与所述金属互联结构焊接。

根据本发明的一个方面,所述引线框架包括设置在靠近所述半导体芯片的表面上的导流槽,并且所述导流槽围绕所述漏极焊接区设置。

根据本发明的一个方面,所述应力缓冲层焊接在半导体芯片的另一个表面上,所述应力缓冲层采用电导率大于10

根据本发明的一个方面,所述金属互联结构包括设置在其靠近所述应力缓冲层的表面上的焊接区,所述应力缓冲层焊接在所述焊接区上。

根据本发明的一个方面,所述金属互联结构包括设置在其靠近所述应力缓冲层的表面上的凹槽区,所述凹槽区围绕所述焊接区设置,所述凹槽区设有连接所述塑封体的多个凹槽。

根据本发明的一个方面,所述金属互联结构的面积大于所述应力缓冲层的面积。

根据本发明的一个方面,所述金属互联结构包括引脚焊接区,所述引脚焊接区与所述源极引脚焊接,所述引脚焊接区上设有多个通孔。

为实现上述目的,本发明还提供一种功率半导体器件封装结构的制备方法,包括:

第一次焊接:

将半导体芯片的一个表面焊接在引线框架上;

将半导体芯片的另一个表面焊接在应力缓冲层上;

第一次清洗:

清洗所述第一次焊接后的结构;

第二次焊接:

将金属互联结构焊接在应力缓冲层上;

第二次清洗:

清洗所述第二次焊接后的结构;

封装:

通过塑封体封装固定所述第二次焊接后的结构。

根据本发明的一个方面,所述将半导体芯片的一个表面焊接在引线框架上为:

使用点胶机在引线框架上点高温焊膏,焊膏熔点大于300℃,完成点胶后,使用压模进行焊膏整形,使用钢网印刷出焊膏形状,然后使用贴片机将半导体芯片贴在焊膏上并保证中心对齐。

根据本发明的一个方面,所述将半导体芯片的另一个表面焊接在应力缓冲层上为:

使用点胶机在半导体芯片上点高温焊膏,焊膏熔点大于300℃,焊膏排布阵列与应力缓冲层的截面形状相同,焊膏点数为8个以上,然后使用贴片机将半导体芯片贴在焊膏上并保证中心对齐。

根据本发明的一个方面,所述将金属互联结构焊接在应力缓冲层上为:

使用点胶机在应力缓冲层上点低温焊膏,焊膏熔点为200℃~300℃,焊膏排布阵列与应力缓冲层的截面形状相同,焊膏点数为8个以上,敷设焊膏后将金属互联结构焊接在应力缓冲层上,根据半导体芯片结构,焊接后的金属互联结构边缘距离半导体芯片门极边缘的距离大于1.5mm。

根据本发明的一个方面,还包括:

在完成所述第一次焊接后,将所述第一次焊接后的结构放入回流焊设备进行回流焊接。

根据本发明的一个方面,还包括:

在完成所述第二次焊接后,将所述第二次焊接后的结构放入回流焊设备进行回流焊接。

根据本发明的一个方案,金属互联结构远离应力缓冲层的表面与塑封体的一个表面位于同一水平面上,并且金属互联结构的上表面设有第一散热区,外接的散热器可以安装在该第一散热区从上方对功率半导体器件进行散热。不仅如此,引线框架远离半导体芯片的表面与塑封体的另一个表面位于同一水平面上,并且该表面设有第二散热区,外接的散热器可以安装在该第二散热区从下方对功率半导体器件进行散热。如此设置,本发明的功率半导体器件封装结构可以实现从第一散热区及第二散热区进行散热(双面散热),可以大大降低器件工作状态下的结温,提高器件的通流能力,保证器件可长期可靠运行。

根据本发明的一个方案,引线框架包括设置在其靠近半导体芯片的表面上的漏极焊接区,半导体芯片的一个表面焊接在漏极焊接区上。如此设置,保证半导体芯片电极可通过引线框架基岛与外部PCB相连,同时半导体芯片可通过第二散热区进行散热。

根据本发明的一个方案,引线框架包括栅极引脚和源极引脚,源极引脚与金属互联结构焊接。如此设置,保证半导体芯片电极可通过引线框架引脚与外部PCB相连,同时芯片可通过第一散热区进行散热。

根据本发明的一个方案,应力缓冲层焊接在半导体芯片的另一个表面上,如此设置,使得本发明可通过应力缓冲层与半导体芯片电极直接相连,从而增大芯片的有效利用面积,降低器件封装寄生电阻及导通压降。

根据本发明的一个方案,应力缓冲层采用高导热、高导电材料,并且其热膨胀系数与所述半导体芯片的热膨胀系数相同或者相近。具体地,应力缓冲层采用电导率大于10

根据本发明的一个方案,金属互联结构包括设置在其靠近应力缓冲层的表面上的凹槽区,凹槽区围绕焊接区设置,凹槽区设有连接塑封体的多个凹槽,并且凹槽的直径为1-2mm,深度为1mm。如此设置,可以保证金属互联结构与塑封体的结合力。

根据本发明的一个方案,金属互联结构的面积大于应力缓冲层的面积,具体地,金属互联结构和应力缓冲层构成T形结构,如此设置,可以保证施加在顶部外接散热器上的外部压力可以有效地分散到塑封体中,以保证减小器件使用过程中外部散热器施加在半导体芯片上的机械应力。

根据本发明的一个方案,金属互联结构包括引脚焊接区,引脚焊接区与源极引脚焊接,引脚焊接区上设有多个通孔。如此设置,可以保证焊接过程中焊膏中的气泡可以排出,同时增加顶部的金属互联结构和塑封体的结合力。

根据本发明的一个方案,通过第一次高熔点焊膏焊接完成半导体芯片、引线框架及应力缓冲层的连接,通过第二次低熔点焊膏焊接完成金属互联结构和应力缓冲层的连接。由于器件中温度分布为从半导体芯片到散热区呈梯度减小变化,因此半导体芯片附近选择高熔点焊膏可以保证器件的长期运行可靠性。同时由于金属互联结构为非对称结构,利用低熔点焊膏的粘稠性可以减小金属互联结构的位移,保证器件封装外形的一致性。

根据本发明的方案,使得封装过程中各组件的相对位移控制在最小,保证器件焊接的一致性。同时,采用不同熔点的焊膏进行焊接,可以确保各结构件的焊接稳定性,实现器件的可靠运行。

附图说明

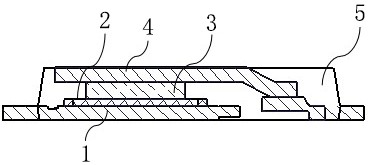

图1示意性表示根据本发明的一种实施方式的功率半导体器件封装结构的侧面剖视图;

图2示意性表示根据本发明的一种实施方式的引线框架的结构图;

图3示意性表示根据本发明的一种实施方式的应力缓冲层的结构图;

图4示意性表示根据本发明的一种实施方式的金属互联结构的结构图。

具体实施方式

现在将参照示例性实施例来论述本发明的内容。应当理解,论述的实施例仅是为了使得本领域普通技术人员能够更好地理解且因此实现本发明的内容,而不是暗示对本发明的范围的任何限制。

如本文中所使用的,术语“包括”及其变体要被解读为意味着“包括但不限于”的开放式术语。术语“基于”要被解读为“至少部分地基于”。术语“一个实施例”和“一种实施例”要被解读为“至少一个实施例”。

图1示意性表示根据本发明的一种实施方式的功率半导体器件封装结构的侧面剖视图,如图1所示,在本实施方式中,功率半导体器件封装结构,包括:引线框架1,焊接在引线框架1上的半导体芯片2,焊接在半导体芯片2上的应力缓冲层3,焊接在应力缓冲层3上的金属互联结构4,以及将引线框架1、半导体芯片2、应力缓冲层3和金属互联结构4封装固定的塑封体5。

在本实施方式中,金属互联结构4远离应力缓冲层3的表面(即图1中金属互联结构4的上表面)与塑封体5的一个表面(上表面)位于同一水平面上,并且金属互联结构4的上表面设有第一散热区,外接的散热器可以安装在该第一散热区从上方对功率半导体器件进行散热。不仅如此,在本实施方式中,引线框架1远离半导体芯片2的表面(即图1中引线框架1的下表面)与塑封体5的另一个表面(下表面)位于同一水平面上,并且该表面设有第二散热区,外接的散热器可以安装在该第二散热区从下方对功率半导体器件进行散热。如此设置,本发明的功率半导体器件封装结构可以实现从第一散热区及第二散热区进行散热(双面散热),可以大大降低器件工作状态下的结温,提高器件的通流能力,保证器件可长期可靠运行。

在本实施方式中,半导体芯片2可为功率MOS芯片、二极管芯片、IGBT芯片等功率芯片,半导体芯片2做双面可焊金属化处理。

进一步地,图2示意性表示根据本发明的一种实施方式的引线框架的结构图。如图2所示,在本实施方式中,引线框架1包括设置在其靠近半导体芯片2的表面上的漏极焊接区101,半导体芯片2的一个表面(下表面)焊接在漏极焊接区101上。如此设置,保证半导体芯片2电极可通过引线框架1基岛与外部PCB相连,同时半导体芯片2可通过第二散热区进行散热。

进一步地,如图2所示,在本实施方式中,引线框架1包括栅极引脚102和源极引脚103,源极引脚103与金属互联结构4焊接。如此设置,保证半导体芯片2电极可通过引线框架1引脚与外部PCB相连,同时芯片可通过第一散热区进行散热。

进一步地,如图2所示,在本实施方式中,引线框架1包括设置在靠近半导体芯片2的表面上的导流槽104,并且导流槽104围绕漏极焊接区101设置。如此设置,可以使得导流槽104可以在焊接大面积半导体芯片2时,能够防止焊膏溢出,同时增加引线框架1与塑封体5的接触面积,防止引线框架1与塑封体5分层。

进一步地,图3示意性表示根据本发明的一种实施方式的应力缓冲层的结构图。如图3所示,在本实施方式中,应力缓冲层3焊接在半导体芯片2的另一个表面(上表面)上,如此设置,使得本发明可通过应力缓冲层3与半导体芯片2电极直接相连,从而增大芯片的有效利用面积,降低器件封装寄生电阻及导通压降。

在本实施方式中,应力缓冲层3采用高导热、高导电材料,并且其热膨胀系数与所述半导体芯片2的热膨胀系数相同或者相近。具体地,应力缓冲层3采用电导率大于10

在本实施方式中,应力缓冲层3通过回流焊焊接在半导体芯片2上,其尺寸设计为距离半导体芯片2可焊区边缘大于0.45mm,以保证焊接过程中的焊膏溢出不会覆盖器件终端结构,导致器件漏电流增大。

进一步地,图4示意性表示根据本发明的一种实施方式的金属互联结构的结构图。如图4所示,在本实施方式中,金属互联结构4包括设置在其靠近应力缓冲层3的表面上的焊接区401,应力缓冲层3焊接在焊接区401上。

进一步地,如图4所示,在本实施方式中,金属互联结构4包括设置在其靠近应力缓冲层3的表面(即下表面)上的凹槽区402,凹槽区402围绕焊接区401设置,凹槽区402设有连接塑封体5的多个凹槽,并且凹槽的直径为1-2mm,深度为1mm。如此设置,可以保证金属互联结构4与塑封体5的结合力。

进一步地,在本实施方式中,金属互联结构4的面积大于应力缓冲层3的面积,具体地,如图1所示,金属互联结构4和应力缓冲层3构成T形结构,如此设置,可以保证施加在顶部外接散热器上的外部压力可以有效地分散到塑封体5中,以保证减小器件使用过程中外部散热器施加在半导体芯片2上的机械应力。

进一步地,如图4所示,在本实施方式中,金属互联结构4包括引脚焊接区403,引脚焊接区403与源极引脚103焊接,引脚焊接区403上设有多个通孔404。如此设置,可以保证焊接过程中焊膏中的气泡可以排出,同时增加顶部的金属互联结构4和塑封体5的结合力。

根据本发明的上述方案,可以实现功率半导体器件的双面散热,提高功率半导体器件的通流能力,在应用系统中,可以减小功率半导体器件的用量,降低功率半导体器件的使用成本。

根据本发明的功率半导体器件封装结构包含应力缓冲层及应力分散设计,可以降低器件的封装热应力,提高器件的封装可靠性。

根据本发明的功率半导体器件封装结构采用直接金属互联,可以显著降低器件封装寄生电阻及寄生电感,可降低器件损耗,提高器件性能。

为实现上述目的,本发明还提供一种功率半导体器件封装结构的制备方法,包括以下步骤:

第一次焊接:

将半导体芯片2的一个表面焊接在引线框架1上;

将半导体芯片2的另一个表面焊接在应力缓冲层3上;

第一次清洗:

清洗第一次焊接后的结构;

第二次焊接:

将金属互联结构4焊接在应力缓冲层3上;

第二次清洗:

清洗第二次焊接后的结构;

封装:

通过塑封体5封装固定第二次焊接后的结构,去除多余塑封体5,露出金属互联结构4和引线框架1上的第一散热区和第二散热区。

根据本发明的上述方案,本发明通过第一次高熔点焊膏焊接完成半导体芯片2、引线框架1及应力缓冲层3的连接,通过第二次低熔点焊膏焊接完成金属互联结构4和应力缓冲层3的连接。由于器件中温度分布为从半导体芯片2到散热区呈梯度减小变化,因此半导体芯片2附近选择高熔点焊膏可以保证器件的长期运行可靠性。同时由于金属互联结构4为非对称结构,利用低熔点焊膏的粘稠性可以减小金属互联结构4的位移,保证器件封装外形的一致性。

不仅如此,本发明的金属互联结构4的上表面设有第一散热区,外接的散热器可以安装在该第一散热区从上方对功率半导体器件进行散热。引线框架1的下表面设有第二散热区,外接的散热器可以安装在该第二散热区从下方对功率半导体器件进行散热。如此设置,通过上述方案得到功率半导体器件封装结构可以从两侧进行散热(即双面散热),保证散热性能,保证器件通流能力。

进一步地,根据本发明的一种实施方式,将半导体芯片2的一个表面焊接在引线框架1上为:

使用点胶机在引线框架1上点高温焊膏,焊膏熔点选择为大于300℃,完成点胶后,使用压模进行焊料整形。可选的,使用钢网印刷直接印刷出焊膏形状。然后,使用贴片机将半导体芯片2贴在金属基岛上,保证中心对齐。

进一步地,根据本发明的一种实施方式,将半导体芯片2的另一个表面焊接在应力缓冲层3上为:

使用点胶机在半导体芯片2上点高温焊膏,焊膏熔点选择为大于300℃,焊膏排布阵列与应力缓冲层截面形状相同,焊膏点数数量应保证在8个以上,以保证应力缓冲层3在焊接过程中不会偏移。然后,使用贴片机将半导体芯片2贴在金属基岛上,保证中心对齐。将引线框架1、半导体芯片2及应力缓冲层3放入回流焊设备进行回流焊接。

进一步地,根据本发明的一种实施方式,将金属互联结构4焊接在应力缓冲层3上为:

使用点胶机在应力缓冲层3上点低温焊膏,焊膏熔点为200℃~300℃,焊膏排布阵列与应力缓冲层3的截面形状相同,焊膏点数为8个以上,敷设焊膏后将金属互联结构4焊接在应力缓冲层3上,根据半导体芯片结构,焊接后的金属互联结构边缘距离半导体芯片门极边缘的距离大于1.5mm。将装好顶部的金属互联结构4的器件放入回流焊设备进行回流焊接。

进一步地,根据本发明的一种实施方式,顶部互联结构焊接完成后,按照传统分立式功率器件封装流程,进行门极引线键合、塑封、顶部塑封体去除、电镀、切记、打标及测试包装。

如上述具体制备功率半导体器件封装结构的方法,使得封装过程中各组件的相对位移控制在最小,保证器件焊接的一致性。同时,采用不同熔点的焊膏进行焊接,可以确保各结构件的焊接稳定性,实现器件的可靠运行。

根据本发明的另一种实施方式,也可以先将半导体芯片2和引线框架1焊接,将金属互联结构4和应力缓冲层3焊接,最后将应力缓冲层3和与半导体芯片2焊接。具体如下:

使用点胶机在引线框架1上点高温焊膏,焊膏熔点选择为大于300℃,完成点胶后,使用压模进行焊料整形。可选的,使用钢网印刷直接印刷出焊膏形状。然后,使用贴片机将半导体芯片2贴在金属基岛上,保证中心对齐。

使用点胶机在顶部的金属互联结构4上点高温焊膏,焊膏熔点选择为大于300℃,焊膏排布阵列与应力缓冲层3截面形状相同,焊膏点数数量应保证在8个以上,以保证应力缓冲层3在焊接过程中不会偏移。然后,使用贴片机将应力缓冲层3贴在金属互联结构4焊接区。根据芯片结构,顶部金属互联结构4边缘距离芯片门极边缘的距离应大于1.5mm。将引线框架1及半导体芯片2、应力缓冲层3及金属互联结构4放入回流焊设备进行回流焊接。

使用点胶机在顶部的应力缓冲层上点低温焊膏,焊膏熔点选择为200℃~300℃,焊膏排布阵列与应力缓冲层3截面形状相同,焊膏点数数量应保证在8个以上。将装好顶部金属互联结构4的器件放入回流焊设备进行回流焊接。

顶部互联结构焊接完成后,按照传统分立式功率器件封装流程,进行门极引线键合、塑封、顶部塑封料去除、电镀、切记、打标及测试包装。

如上述具体制备功率半导体器件封装结构的方法,使得封装过程中各组件的相对位移控制在最小,保证器件焊接的一致性。同时,采用不同熔点的焊膏进行焊接,可以确保各结构件的焊接稳定性,实现器件的可靠运行。

根据本发明的上述方案,使得根据本发明的功率半导体器件封装结构可以实现器件的双面散热,提高器件的通流能力,在应用系统中,可以减小器件的用量,降低器件的使用成本。根据本发明的功率半导体器件封装结构包含应力缓冲层级应力分散设计,可以降低器件的封装热应力,提高器件的封装可靠性。根据本发明的功率半导体器件封装结构采用直接金属互联,可以显著降低器件封装寄生电阻及寄生电感,可降低器件损耗,提高器件性能。

最后说明的是,以上优选实施例仅用以说明本发明的技术方案而非限制,尽管通过上述优选实施例已经对本发明进行了详细的描述,但本领域技术人员应当理解,可以在形式上和细节上对其作出各种各样的改变,而不偏离本发明权利要求书所限定的范围。

- 一种功率半导体器件封装结构及封装方法

- 一种功率半导体器件封装结构与封装方法

- 半导体功率器件的封装结构及封装结构的电极

- 一种半导体功率器件封装及其制备方法

- 半导体功率器件的封装件及封装半导体功率器件的方法

- 功率半导体器件封装结构和功率半导体器件模块