埋入式电路板以及埋入式电路板的制作方法

文献发布时间:2023-06-19 09:29:07

技术领域

本申请涉及电路板技术领域,特别是涉及埋入式电路板以及埋入式电路板的制作方法。

背景技术

随着电子产品向小型化、高密度、多功能的方向发展,电子产品内的各种元器件和互连线数目也逐渐增加,而且器件和互连线的物理尺寸也越来越小。因此,将各种有源无源器件组成的电子系统整合到一个普通封装体内的系统级封装技术已成为未来的重要趋势。

印制电路板中很多都有谐振电路,以及利用谐振电路构成带通滤波器。谐振电路一般由电容和电感并联而成。在高密度设计的印制电路板中,电感和电容的数量巨大,如何将这些数量巨大的器件整合是影响产品小型化的一个重要因素。

发明内容

本申请提供一种埋入式电路板以及埋入式电路板的制作方法,能够使得整个印刷电路板的表面器件减少,从而实现电路的小型化,同时,避免谐振波直接传递电子器件而导致电子器件逐渐松脱,甚至脱落,并能够避免制作贯通孔时损伤槽体内的电子器件。

一方面,本申请提供了一种埋入式电路板,包括:依次层叠设置的第一外层线路板、基板和第二外层线路板,其中,基板具有至少一槽体,至少一槽体位于第一外层线路板与第二外层线路板之间,第一外层线路板、基板和第二外层线路板上开设有贯通孔以形成谐振腔,槽体的侧壁与相邻贯通孔的侧壁之间的最小间距为50-400um;以及电子器件,嵌设在槽体内。

另一方面,本申请提供了一种埋入式电路板的制作方法,包括:提供具有至少一槽体的基板,槽体内嵌设有电子器件;将第一外层线路板和第二外层线路板分别设置到基板的相对两侧;压合第一外层线路板、基板和第二外层线路板,以固定第一外层线路板、基板和第二外层线路板;对第一外层线路板、基板和第二外层线路板进行开孔,以在第一外层线路板、基板和第二外层线路板上形成至少一个贯通孔,贯通孔作为谐振腔;其中,槽体的侧壁与相邻贯通孔的侧壁之间的最小间距为100-500um。

又一方面,本申请提供了一种移动设备,包括如前述的埋入式电路板。

再一方面,本申请提供了一种传感组件,包括如前述的埋入式电路板。

本申请的有益效果是:区别于现有技术的情况,本申请埋入式电路板的第一外层线路板、基板和第二外层线路板上开设有贯通孔以形成谐振腔,而基板的槽体内嵌设有电子器件,能够使得整个印刷电路板的表面器件减少,从而实现电路的小型化。同时,槽体的侧壁与相邻贯通孔的侧壁之间的最小间距为50-400um,能够避免谐振波直接传递电子器件而导致电子器件逐渐松脱,甚至脱落,并能够避免制作贯通孔时损伤槽体内的电子器件。

附图说明

为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。其中:

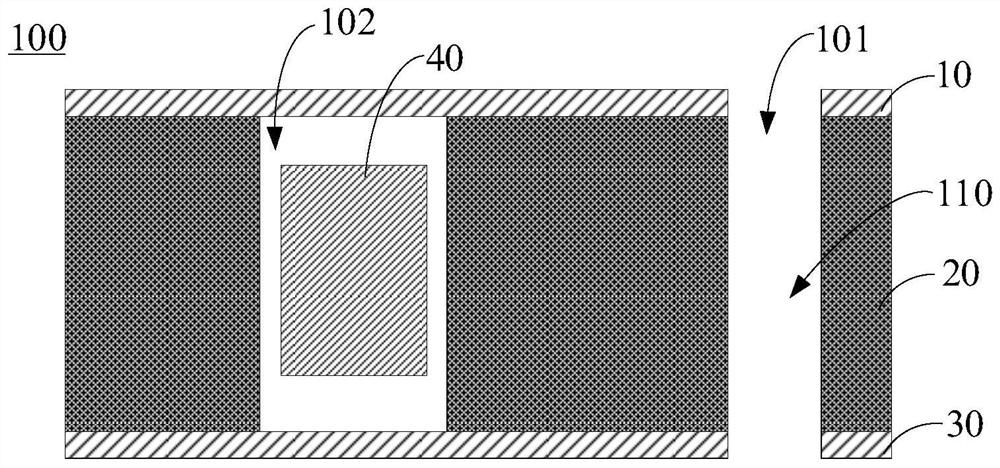

图1是本申请埋入式电路板第一实施例的结构示意图;

图2是本申请埋入式电路板第二实施例的结构示意图;

图3是本申请埋入式电路板第三实施例的结构示意图;

图4是本申请埋入式电路板第四实施例的结构示意图;

图5是本申请埋入式电路板第五实施例的结构示意图;

图6是本申请埋入式电路板的制造方法一实施例的流程示意图。

具体实施方式

下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本申请一部分实施例,而不是全部实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性的劳动前提下所获得的所有其他实施例,都属于本申请保护的范围。

参阅图1,本申请提出一种埋入式电路板100,埋入式电路板100包括:依次层叠设置的第一外层线路板10、基板20和第二外层线路板30。

第一外层线路板10位于基板20的上表面,第一外层线路板10可以为基板20上表面的铜层,第二外层线路板30位于基板20的下表面,第二外层线路板30可以为基板20下表面的铜层。

基板20具有至少一贯通孔101和至少一槽体102。槽体102的制作工艺采用控深铣,所谓控深铣就是控制Z方向的深度的一种铣床技术,由于受到铣床Z方向控深铣精度的限制。其中,槽体102的长度、宽度的都大于所需埋入芯片的尺寸,以使槽体102能足够容纳所需埋入的芯片。槽体102的形状可以为规则的长方体,或为梯形体,或阶梯状,可以根据实际的工艺要求进行设计,在此不做限制,说明书附图中为了较直观的表述,统一将槽体102表示成长方体的形状。

第一外层线路板10、基板20与第二外层线路板30开设有至少一贯通孔101之间,以形成谐振腔110。本实施例中,谐振腔110为方形的,在其他实施方式中,谐振腔110也可以为L型、圆形、U型或者蛇形。

进一步地,埋入式电路板100还包括电子器件40,电子器件40嵌设在基板20的槽体102内。其中,槽体102的数量可以与电子器件40的数量相同,此时一个槽体102中设置一个电子器件40,当然,槽体102的数量也可以与电子器件40的数量不同,具体为槽体102的数量小于电子器件40的数量,此时两个或两个以上的电子器件40可以同时设置在一个槽体102中。上述电子器件40可以为以物理振动为主要工作模式的器件,例如微型麦克风、微型扬声器、声波谐振器、微波谐振器、超声波换能器、传感器芯片、数字芯片中的至少一种,但并不局限于以上电子器件40。上述电子器件40也可以为调谐元件,调谐元件能够调节谐振腔110所对应的谐振器的谐振频点,其中,调谐元件为电容和/或电感。

进一步地,槽体102的侧壁与相邻贯通孔101的侧壁之间的最小间距为50-400um,例如100um、200um、400um或500um。优选地,槽体102的侧壁与相邻贯通孔101的侧壁之间的最小间距为200-450um,例如200um、300um、400um或450um。

其中,该谐振腔110的内周壁为绝缘内周壁。该谐振腔110的作用有别于金属化通孔,该谐振腔110不具备导通电流的功能,但是可以传导并放大声波震动、大气压力、温湿度等信息,使这些信息被埋设在槽体102的电子器件40(例如传感器芯片)感应到,从而转化成电信号,最终在移动设备、传感组件等产品中显示出来。

在其他实施例中,如图2所示,该谐振腔110的内周壁上设置有铜层70,以作为电连接层。

区别于现有技术的情况,本申请埋入式电路板100的第一外层线路板10、基板20和第二外层线路板30上开设有贯通孔101以形成谐振腔110,而基板20的槽体102内嵌设有电子器件40,能够使得整个印刷电路板100的表面器件减少,从而实现电路的小型化。同时,槽体102的侧壁与相邻贯通孔101的侧壁之间的最小间距为50-400um,能够避免谐振波直接传递电子器件40而导致电子器件40逐渐松脱,甚至脱落,并能够避免制作贯通孔101时损伤槽体102内的电子器件40。同时,可以实现多个电子器件埋入设置,且该多个电子器件可以共用一个谐振腔,防水性能佳且生产成本较低。

参阅图3,相邻两个谐振腔110A、110B共用同一腔壁120,其中腔壁120开设有耦合开窗130,耦合开窗130用于实现相邻两个谐振腔110A、110B之间的信号耦合。该耦合开窗130可以为普通感性耦合结构,或者为设有上下凸起结构的容性耦合结构。

本实施例中用相邻两个谐振腔110A、110B的腔体示意。相邻两个谐振腔110A、110B被一腔壁120隔开。进一步地。该腔壁120的耦合开窗130可以从腔壁120顶部延伸到底部,此时,耦合强度达到最大值。

进一步地,各个谐振腔110内分别放置有谐振子(图未示出),而在腔壁120的耦合开窗130中设置有具有特定形状的耦合块(图未示出),耦合块的两端部设有分别与两谐振子表面平行的端面,使得耦合块端面外围能形成与谐振子表面方向相同的电磁场,当二者足够靠近,则耦合块能够对谐振子表面外部的电磁场产生足够的微扰,从而提高相邻两个谐振腔110A、110B之间的耦合效果。

参阅图4,基板20包括依次交替层叠的若干层可熔融介质层22和若干层子体21,其中至少一层子体21中开设有槽体102。其中,子体21和可熔融介质层22压合后,至少部分可熔融介质层22流入电子器件40与槽体102的侧壁之间。

具体地,子体21可以是无铜芯板或者覆铜板,子体21选用无铜芯板的目的是将埋入式电路板100的厚度加厚,以足够厚度埋入电子器件40。当然,子体21也可选用覆铜板,覆铜板上可以设置线路以进行电路连接。

相邻子体21之间设有可熔融介质层22,其中,压合时,至少部分可熔融介质层22流入电子器件40与槽体102的侧壁之间并接触电子器件40,进而将各层子体21以及电子器件40粘合在一起。

可熔融介质层22为树脂、硅树脂胶中的一种绝缘材料或任意组合。具体地,树脂是指受热后有软化或熔融范围,软化时在外力作用下有流动倾向,常温下是固态、半固态,有时也可以是液态的有机聚合物。树脂可以为环氧树脂、有机硅树脂、聚酰亚胺树脂、酚醛树脂、聚氨酯、丙烯酸树脂等胶黏剂体系。硅树脂胶是一种无色透明液体,固化后具有一定的透气性及弹性,主要具有耐温特性、耐候性、电气绝缘性、生理惰性、低表面张力和低表面能。

参阅图5,进一步地,各层子体21以及相邻子体21之间的可熔融介质层22均开设有槽体102。即该槽体102贯穿各层子体21以及相邻子体21之间的可熔融介质层22。

进一步地,参阅图3和4,电子器件40的外表面包覆有封装体50,其中,子体21和可熔融介质层22压合后,至少部分可熔融介质层22流入封装体50与槽体102的侧壁之间并接触封装体50。

封装体50的材料为硅树脂胶。硅树脂胶是一种无色透明液体,固化后具有一定的透气性及弹性,主要具有耐温特性、耐候性、电气绝缘性、生理惰性、低表面张力和低表面能。

通过上述方式,本申请在电子器件40外表面包覆有以硅树脂胶为材料的封装体50,硅树脂胶的传热、导热、散热效果好,因此,该封装体50能耐高温,且具有极佳的热散失能力,在电子器件40工作时,电子器件40温度升高,封装体50能迅速将热释放出来。同时,以硅树脂胶为材料的封装体50与电子器件40、槽体102侧壁的结合力好,很大程度上解决了脱落、膨胀的问题。

进一步地,封装体50中设有金属片(图未示出),金属片设置于封装硅树脂胶中,金属片的一端与电子器件40电连接,另一端凸设于封装体50并电连接接地线路层、信号线路层或导电孔60。该金属片可以为纯金属制成,用到的金属材料包括但不限于铜、铜合金、铝、铝合金、铁、铁合金、镍、镍合金、金、金合金、银、银合金、铂族、铂族合金、铬、铬合金、镁、镁合金、钨、钨合金、钼、钼合金、铅、铅合金、锡、锡合金、铟、铟合金、锌或锌合金等。在另一实施例中,该金属片的材料也可以由金属基块和导电石墨片组成。由于导电石墨片的热阻较普通金属及合金的热阻小,可以在金属基块中嵌入导电石墨片使得导热更加迅速。

继续参阅图4,基板20上开设有用于层间连接的导电孔60,其中,电子器件40的连接端子通过导电孔60实现与第一线路层和/或第二线路层的电连接。

具体地,在基板20上还可以开设导通孔。在本实施例中,该导通孔贯穿各层子体21和各层可熔融介质层22,该导通孔内还设置有电连接子体21的信号层和/或接地层的导电层,以得到导电孔60。在本实施例中,可通过电镀的方式对导通孔进行金属化处理。具体地,可在含有欲镀金属的盐类溶液中,以导通孔的金属为阴极,通过电解作用,使镀液中欲镀金属的阳离子在导通孔的金属表面沉积出来,从而形成导电层。常用的用于电镀的金属包括但不限于钛、钯、锌、镉、金或黄铜等。当然,在其他实施例中,还可以通过例如涂覆的方式实现该导通孔的金属化处理。

可选地,设置一个或一个以上元器件(图未示出)在第一线路层或第二线路层远离基板20的一侧上,还可以有多个元器件分别设置在第一线路层远离基板20的一侧上、第二线路层远离基板20的一侧上,元器件通过第一线路层和/或第二线路层实现与电子器件40电连接。其中,元器件可以是麦克风芯片、电容元件、电阻元件、电源器件中的一种或几种。

区别于现有技术,本申请将数字芯片等电子器件埋设在基板中,而麦克风芯片等元器件仍表贴到贯通孔101上方,此种结构的好处是降低埋入式电路板100的整体厚度、体积,同时,由于数字芯片等电子器件位于基板内部且被完全包裹,谐振腔不会影响数字芯片,屏蔽性能更高,接收到的噪音等外界干扰更小,从而性能表现更好。

本申请的埋入式电路板100用于移动设备或传感组件。

参阅图6,本申请提出一种埋入式电路板的制作方法,包括:

S10:提供具有至少一槽体的基板,槽体内嵌设有电子器件。

在其他实施例中,可以先在基板上开设至少一槽体以及至少一贯通孔,再将电子器件嵌设到对应的槽体内。

S20:将第一外层线路板和第二外层线路板分别设置到基板的相对两侧。

S30:压合第一外层线路板、基板和第二外层线路板,以固定第一外层线路板、基板和第二外层线路板。

S40:对第一外层线路板、基板和第二外层线路板进行开孔,以在第一外层线路板、基板和第二外层线路板上形成至少一贯通孔,该贯通孔作为谐振腔。

在其他实施例中,可以分别在第一外层线路板、基板和第二外层线路板上开设贯通孔后,再层叠并压合第一外层线路板、基板和第二外层线路板。

其中,槽体的侧壁与相邻贯通孔的侧壁之间的最小间距为50-400um。

本申请的有益效果是:区别于现有技术的情况,本申请埋入式电路板的第一外层线路板、基板和第二外层线路板上开设有贯通孔以形成谐振腔,而基板的槽体内嵌设有电子器件,能够使得整个印刷电路板的表面器件减少,从而实现电路的小型化。同时,槽体的侧壁与相邻贯通孔的侧壁之间的最小间距为50-400um,能够避免谐振波直接传递电子器件而导致电子器件逐渐松脱,甚至脱落,并能够避免制作贯通孔时损伤槽体内的电子器件。同时,可以实现多个电子器件埋入设置,且该多个电子器件可以共用一个谐振腔,防水性能佳且生产成本较低。

本申请还提供一种移动设备,包括上述实施例的埋入式电路板100。

本申请还提供一种传感组件,包括上述实施例的埋入式电路板100。

以上所述仅为本申请的实施方式,并非因此限制本申请的专利范围,凡是利用本申请说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本申请的专利保护范围内。

- 埋入式电路板以及埋入式电路板的制作方法

- 埋入式电路板及其制作方法