线路板及其制作方法

文献发布时间:2023-06-19 09:29:07

技术领域

本申请涉及芯片埋入技术领域,特别是涉及一种线路板及其制作方法。

背景技术

随着电路板制备工艺的越来越完善,电子封装技术也越来越成熟。

今日的电子封装不但要提供芯片的保护,同时还要在一定的成本下满足不断增加的性能、可靠性、散热、功率分配等要求,同时由于用户对超薄,微缩,多功能的需求,而现有的电路板在制作工艺中集成度不高,且功耗和成本相对较高。

因此,提供一种集成度高、功耗低且成本低的线路板尤为必要。

发明内容

本申请主要提供一种线路板及其制作方法,以实现线路板的轻薄化及小型化。

为解决上述技术问题,本发明提供的一个技术方案是:提供一种线路板,包括:芯板,开设有槽体,所述槽体包括多个第一子槽体及多个位于所述第一子槽体下方且与所述第一子槽体位置对应的第二子槽体;芯片组件,设置于所述槽体中;所述芯片组件包括多个位于所述第一子槽体中的第一芯片及多个位于所述第二子槽体中的第二芯片;其中,每一所述第一芯片与其位置对应的所述第二芯片串联形成多个芯片组;所述多个芯片组相互并联,且所述多个芯片组一端连接第一电源信号层,另一端连接地线层。

其中,所述线路板还包括:第一线路层,设置在所述芯板的一侧;第二线路层,设置在所述芯板远离所述第一线路层的一侧;第一绝缘层,设置在所述芯板与所述第一线路层之间;第二绝缘层,设置在所述芯板与所述第二线路层之间;其中,所述第一线路层包括所述第一电源信号层及控制信号层;所述第二线路层包括所述地线层及第二电源信号层。

其中,所述线路板还包括:第一电源信号层,设置在所述芯板的一侧;第二电源信号层,设置在所述芯板远离所述第一电源信号层的一侧;第一绝缘层,设置在所述芯板与所述第一电源信号层之间;第二绝缘层,设置在所述芯板与所述第二电源信号层之间;位于所述第一电源信号层远离所述芯板的一侧的控制信号层;位于所述第二电源信号层远离所述芯板的一侧的地线层;位于所述第一电源信号层及所述控制信号层之间的第三绝缘层;位于所述第二电源信号层及所述地线层之间的第四绝缘层。

其中,每个所述第一芯片及所述第二芯片均包括:靠近所述第一线路层一侧的第二连接端子及第三连接端子,及靠近所述第二线路层的第一连接端子;其中,所述第一芯片的所述第一连接端子耦接与其位置对应的第二芯片的所述第二连接端子;所述第一芯片的第二连接端子耦接所述第一电源信号层,所述第一芯片的第三连接端子耦接所述控制信号层,所述第二芯片的第三连接端子耦接所述控制信号层,所述第二芯片的第一连接端子连接所述地线层。

其中,所述第二绝缘层对应所述第一芯片的第一连接端子的位置处具有第一导电孔,以将所述第二电源信号层与所述第一芯片的第一连接端子连接;所述第一绝缘层对应所述第二芯片的第二连接端子的位置处具有第二导电孔,以将所述第一电源信号层与所述第二芯片的第二连接端子连接;所述第一芯片及所述第二芯片之间具有第三导电孔,以将所述第一电源信号层及所述第二电源信号层连接,进而将所述第一芯片的所述第一连接端子与所述第二芯片的所述第二连接端子连接,以将所述第一芯片及所述第二芯片串联形成多个芯片组。

其中,所述第一绝缘层对应所述第一芯片及所述第二芯片的第三连接端子的位置处具有第四导电孔,以将所述第一芯片及所述第二芯片的第三连接端子与所述控制信号层连接;或所述第一绝缘层及所述第三绝缘层对应所述第一芯片及所述第二芯片的第三连接端子的位置处具有第四导电孔,以将所述第一芯片及所述第二芯片的第三连接端子与所述控制信号层连接。

其中,所述第一绝缘层对应所述第一芯片的所述第二连接端子的位置处具有第五导电孔,以将所述第一芯片的所述第二连接端子与所述第一电源信号层连接;所述第二绝缘层对应所述第二芯片的所述第一连接端子的位置处具有第六导电孔,以将所述第二芯片的所述第一连接端子与所述地线层电连接;或所述第一绝缘层对应所述第一芯片的所述第二连接端子的位置处具有第五导电孔,以将每一所述第一芯片的第二连接端子与所述第一电源信号层连接;所述第二绝缘层及所述第四绝缘层对应所述第二芯片的所述第一连接端子的位置处具有第六导电孔,以将每一所述第二芯片的所述第二连接端子与所述地线层电连接。

为解决上述即使问题,本发明提供的另一个技术方案为:提供一种线路板的制作方法,包括:提供芯板;在所述芯板上开设槽体,所述槽体包括多个第一子槽体及多个位于所述第一子槽体下方且与所述第一子槽体位置对应的第二子槽体;在所述槽体中放置芯片组件,所述芯片组件包括多个位于所述第一子槽体中的第一芯片及多个位于所述第二子槽体中的第二芯片,其中,每一所述第一芯片与其位置对应的所述第二芯片串联形成多个芯片组;所述多个芯片组相互并联,且所述多个芯片组一端连接第一电源信号层,另一端连接地线层。

其中,所述在所述槽体中放置芯片组件,所述芯片组件包括多个位于所述第一子槽体中的第一芯片及多个位于所述第二子槽体中的第二芯片;其中,每一所述第一芯片与其位置对应的所述第二芯片串联形成多个芯片组;所述多个芯片组相互并联,且所述多个芯片组一端连接第一电源信号层,另一端连接地线层的步骤之后包括:在所述芯板的一侧设置第一线路板,及在所述芯板远离所述第一线路层的一侧设置第二线路层;其中,所述第一线路层包括第一电源信号层及控制信号层,所述第二线路层包括地线层及第二电源信号层;在所述芯板及所述第一线路层之间设置第一绝缘层,及在所述芯板及所述第二线路层之间设置第二绝缘层;或在所述芯板的一侧设置第一电源信号层,及在所述芯板远离所述第一电源信号层的一侧设置第二电源信号层;在所述芯板及所述第一电源信号层之间设置第一绝缘层,及在所述芯板及所述第二电源信号层之间设置第二绝缘层;在所述第一电源信号层远离所述芯板的一侧设置控制信号层,及在所述第二电源信号层远离所述芯板的一侧设置地线层;在所述第一电源信号层及所述控制信号层之间设置第三绝缘层,及在所述第二电源信号层及所述地线层之间设置第四绝缘层。

其中,所述方法还包括:在所述第二绝缘层对应所述第一芯片的第一连接端子的位置处设置第一导电孔,在所述第一绝缘层对应所述第二芯片的第二连接端子的位置处设置第二导电孔,及在所述第一芯片及所述第二芯片之间设置贯穿所述芯板、所述第一绝缘层及所述第二绝缘层的第三导电孔,以将所述第一芯片的第一连接端子与所述第二芯片的第二连接端子连接;在所述第一绝缘层对应所述第一芯片的第二连接端子的位置处设置第五导电孔,以将所述第一芯片的所述第二连接端子与所述第一电源信号层连接;在所述第二绝缘层对应所述第二芯片的第一连接端子的位置处设置第六导电孔,以将所述第二芯片的所述第一连接端子与所述地线层连接;在所述第一绝缘层对应所述第一芯片及所述第二芯片的第三连接端子的位置处设置第四导电孔,以将所述第一芯片及所述第二芯片的第三连接端子与所述控制信号层连接。

本发明的有益效果,区别与现有技术,本发明提供的线路板包括芯板,芯板上开设有槽体,槽体包括多个第一子槽体及多个位于第一子槽体下方且与第一子槽体位置对应的第二子槽体;芯片组件设置于槽体中;芯片组件包括多个位于第一子槽体中的第一芯片及多个位于第二子槽体中的第二芯片;其中,每一第一芯片与其位置对应的第二芯片串联形成多个芯片组;多个芯片组相互并联,且多个芯片组一端连接第一电源信号层,另一端连接地线层。以此将芯片嵌入到线路板中与线路板结合,以实现线路板的轻薄化及小型化。

附图说明

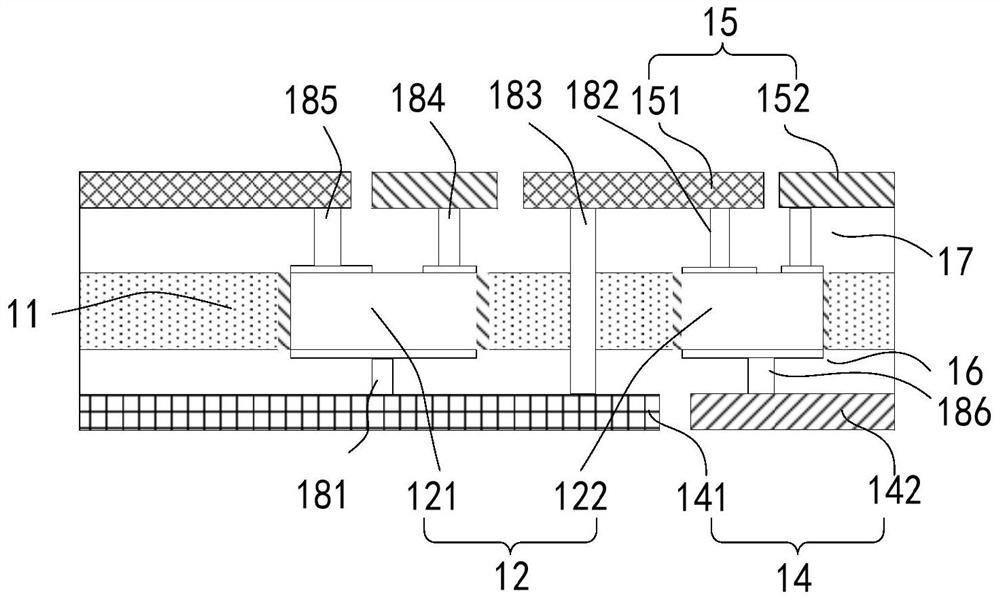

图1是本发明线路板的第一实施例的结构示意图;

图2是本发明线路板的槽体的结构示意图;

图3是本发明线路板的第二实施例的结构示意图;

图4是本发明线路板的制作方法的第一实施例的流程示意图;

图5是本发明线路板的制作方法的第二实施例的流程示意图;

图6是本发明线路板的制作方法的第三实施例的流程示意图;

图7是本发明线路板的制作方法的第四实施例的流程示意图。

具体实施方式

下面将结合本申请实施方式中的附图,对本申请实施方式中的技术方案进行清楚、完整地描述,显然,所描述的实施方式仅仅是本申请一部分实施方式,而不是全部实施方式。基于本申请中的实施方式,本领域普通技术人员在没有做出创造性的劳动前提下所获得的所有其他实施方式,都属于本申请保护的范围。

请参见图1,为本发明线路板的第一实施例的结构示意图。包括:芯板11及芯片组件12;芯板11上开设有槽体,请参见图2,槽体包括多个第一子槽体111,及位于第一子槽体111下方的多个第二子槽体112。在本实施例中,第一子槽体111及第二子槽体112呈阵列排布,且第二子槽体112位于第一子槽体111下方,且与第一子槽体111一一对应。芯片组件12包括位于第一子槽体111中的第一芯片121及位于第二子槽体112中的第二芯片122。本实施例以三个第一芯片121及三个第二芯片122为例进行说明。图1所示的结构示意图为线路板的侧视图。

在本实施例中,一个第一芯片121对应放置于一个第一子槽体111中,一个第二芯片122对应放置在一个第二子槽体113中。在另一实施例中,还可以一个槽体放置多个芯片,本实施例均以一个槽体放置一个芯片为例进行说明。

图1所示的线路板还包括第一线路层15及第二线路层14,第一线路层15及第二线路层14分别设置在芯板11的两侧,并通过第一绝缘层17及第二绝缘层16与芯板11连接。具体的,第一绝缘层17设置在芯板11与第一线路层15之间,用于将芯板11与第一线路层15连接;第二绝缘层16设置在芯板11与第二线路层14之间,用于将芯板11与第二线路层14连接。

本申请中,芯板11的材料为覆铜板,覆铜板为制作线路板的基础材料,包括基材板及覆盖在所述基材上的铜箔,所述基材板由纸基板、玻纤布基板、合成纤维布基板、无纺布基板、复合基板等材料浸以树脂,制成粘结片,由多张粘结片组合制成,在制作好的基材板单面或双面覆以铜箔,再进行热压固化以制成覆铜板。第一绝缘层17及第二绝缘层16为半固化片,其作为层压时的层间粘结层,具体地,所述半固化片主要由树脂和增强材料组成,在制作多层线路板时,通常采用玻纤布做增强材料,将其浸渍上树脂胶液,再经热处理预烘制成薄片,其加热加压下会软化,冷却后会固化,且具有黏性,在高温压合过程中能将相邻的两层黏合。

在本实施例中,位于第一子槽体111中的第一芯片121与位于第二子槽体112中的第二芯片122之间相互串联并形成多个芯片组,且多个芯片组并联,即多个芯片组一端连接第一电源信号层,另一端连接地线层。

具体的,第一芯片121及第二芯片122均包括第一连接端子、第二连接端子及第三连接端子。其中,第二连接端子及第三连接端子位于靠近第一线路层一侧,第一连接端子位于靠近第二线路层一侧。在第一芯片121与第二芯片122进行串联形成芯片组时,第一芯片121的第一连接端子连接与其位置对应的第二芯片122的第二连接端子。在各个芯片组相互并联时,芯片组的一端连接第一电源信号层,另一端连接地线层。

如图1所示,本实施例中的线路板中的第一线路层15包括互不连接的第一电源信号层151及控制信号层152;第二线路层14包括互不连接的第二电源信号层141及地线层142。

本实施例中,为实现第一芯片121与第二芯片122的串联,即为实现第一芯片121的第一连接端子与第二芯片122的第二连接端子之间的连接,第二绝缘层16对应第一芯片121的第一连接端子的位置处具有第一导电孔181,以将第二电源信号层141与第一芯片121的第一连接端子连接。第一绝缘层17对应第二芯片122的第二连接端子的位置处具有第二导电孔182,以将第一电源信号层151与第二芯片122的第二连接端子连接。第一芯片121及第二芯片122之间具有贯穿芯板11、第一绝缘层17及第二绝缘层16的第三导电孔183,以将第一电源信号层151及第二电源信号层141连接,进而将第一芯片121的第一连接端子与第二芯片122的第二连接端子连接,以将第一芯片121与第二芯片122串联。

本实施例中,为实现将芯片组相互并联,将每一第一芯片121的第二连接端子相互连接,将每一第二芯片122的第一连接端子相互连接。具体的,为实现将每一第一芯片121的第二连接端子相互连接,第一绝缘层17对应第一芯片121的第二连接端子的位置处具有第五导电孔185,以将每一第一芯片121的第二连接端子与第一电源信号层151连接;通过第一电源信号层151将第一芯片121的第二连接端子并联。为实现将每一第二芯片122的第一连接端子相互连接,第二绝缘层16对应第二芯片122的第一连接端子的位置处具有第六导电孔186,以将每一第二芯片122的第一连接端子与地线层142连接;通过地线层142将第二芯片122的第一连接端子并联。

进一步的,在本实施例中,第一绝缘层17对应第一芯片121及第二芯片122的第三连接端子的位置处具有第四导电孔184,第四导电孔184用于将第一芯片121及第二芯片122的第三连接端子与控制信号层152连接。

本实施例所示的线路板,通过在线路板中埋入多颗第一芯片121及第二芯片122,且使第一芯片121与对应的第二芯片122串联形成芯片组,使芯片组之间并联,以此实现埋入式线路板的轻薄化及小型化,并能够实现信号传输距离短及减少信号损失的目的。

请参见图3,为本发明线路板的第二实施例的结构示意图。包括:芯板21及芯片组件22;芯板21上开设有槽体,请参见图2,槽体包括行排列的多个第一子槽体111,及位于第一子槽体111下方的多个第二子槽体112。芯片组件22包括位于第一子槽体111中的第一芯片221及位于第二子槽体112中的第二芯片222。本实施例以三个第一芯片221及三个第二芯片222为例进行说明。图3所示的线路板的结构示意图为线路板的侧视图。

图3所示的线路板还包括第一电源信号层251及第二电源信号层241,第一电源信号层251及第二电源信号层241分别设置在芯板21的两侧,并通过第一绝缘层271及第二绝缘层261与芯板21连接。具体的,第一绝缘层271设置在芯板21与第一电源信号层251之间,用于将芯板21与第一电源信号层251连接;第二绝缘层261设置在芯板21与第二电源信号层241之间,用于将芯板21与第二电源信号层241连接。

本实施例所示的线路板还包括第三绝缘层272、第四绝缘层262、控制信号层252及地线层242。其中,控制信号层252位于第一电源信号层251远离芯板21的一侧,地线层242位于第二电源信号层241远离芯板21的一侧。第三绝缘层272位于第一电源信号层251及控制信号层252之间,用于将第一电源信号层251及控制信号层252粘合,第四绝缘层262位于第二电源信号层241及地线层242之间,用于将第二电源信号层241及地线层242粘合。

具体的,第一芯片221及第二芯片222均包括第一连接端子、第二连接端子及第三连接端子。在第一芯片221与第二芯片222进行串联以形成芯片组时,第一芯片221的第一连接端子连接与其位置对应的第二芯片222的第二连接端子。在每一芯片组之间相互并联时,芯片组的一端连接第一电源信号层251,另一端连接地线层242。具体地,第一芯片221的第二连接端子连接第一电源信号层251,第二芯片222的第一连接端子连接地线层242。

如图3所示,本实施例中,为实现第一芯片221与第二芯片222的串联,即为实现第一芯片221的第一连接端子与第二芯片222的第二连接端子之间的连接,第二绝缘层261对应第一芯片221的第一连接端子的位置处具有第一导电孔281,以将第二电源信号层241与第一芯片221的第一连接端子连接。第一绝缘层271对应第二芯片222的第二连接端子的位置处具有第二导电孔282,以将第一电源信号层251与第二芯片222的第二连接端子连接。第一芯片221及第二芯片222之间具有贯穿芯板21、第一绝缘层271及第二绝缘层261的第三导电孔183,以将第一电源信号层251与第二电源信号层241连接,进而将第一芯片221的第一连接端子与第二芯片222的第二连接端子连接,以将第一芯片221与第二芯片222串联。

本实施例中,为实现多个芯片组的相互并联,将每一第一芯片221的第二连接端子相互连接且连接至第一电源信号层251,将每一第二芯片222的第一连接端子相互连接且连接至地线层242。具体的,为实现将每一第一芯片221的第二连接端子相互连接,第一绝缘层271对应第一芯片221的第二连接端子的位置处具有第五导电孔285,以将每一第一芯片221的第二连接端子与第一电源信号层251连接;通过第一电源信号层251将第一芯片221的第二连接端子并联。为实现将第二芯片222相互并联,将每一第二芯片222的第一连接端子相互连接。具体的,为实现将每一第二芯片222的第一连接端子相互连接,第二绝缘层261对应第二芯片222的第一连接端子的位置处具有第六导电孔286,以将每一第二芯片222的第一连接端子与地线层242连接;通过地线层242将第二芯片222的第一连接端子并联。

进一步的,在本实施例中,第一绝缘层271及第三绝缘层272对应第一芯片221及第二芯片222的第三连接端子的位置处具有第四导电孔284,第四导电孔284用于将第一芯片221及第二芯片222的第三连接端子与控制信号层252连接。

本实施例所示的线路板,通过在线路板中埋入多颗第一芯片221及第二芯片222,且使第一芯片221与对应的第二芯片222串联形成芯片组,是、使芯片组之间相互并联,以此实现埋入式线路板的轻薄化及小型化,并能够实现信号传输距离短及减少信号损失的目的。

请参见图4,为本发明线路板的制作方法的第一实施例的流程示意图。包括:步骤S41:提供芯板。

本申请中,芯板的材料为覆铜板,覆铜板为制作线路板的基础材料,包括基材板及覆盖在所述基材上的铜箔,所述基材板由纸基板、玻纤布基板、合成纤维布基板、无纺布基板、复合基板等材料浸以树脂,制成粘结片,由多张粘结片组合制成,在制作好的基材板单面或双面覆以铜箔,再进行热压固化以制成覆铜板。

步骤S42:在所述芯板上开设槽体,所述槽体包括多个第一子槽体及多个位于所述第一子槽体下方且与所述第一子槽体位置对应的第二子槽体。

使用蚀刻、激光钻、机械钻等方式在芯板上开设槽体。本申请中由于放置的芯片为多颗且呈阵列排布,因此槽体包括第一子槽体及位于第一子槽体下方的第二子槽体,且第一子槽体及第二子槽体的位置一一对应。

步骤S43:在所述槽体中放置芯片组件,所述芯片组件包括多个位于所述第一子槽体中的第一芯片及多个位于所述第二子槽体中的第二芯片,其中,每一所述第一芯片与其位置对应的所述第二芯片串联形成多个芯片组;所述多个芯片组相互并联,且所述多个芯片组一端连接第一电源信号层,另一端连接地线层。

在槽体中设置芯片组件,其中芯片组件包括第一芯片及第二芯片,第一芯片放置于第一子槽体中,第二芯片放置于第二子槽体中。且第一芯片与相对应的第二芯片一一串联形成芯片组,多个芯片组相互并联,即多个芯片组一端连接第一电源信号层,另一端连接地线层。

具体地,请参照图5,为本发明线路板的制作方法的第二实施例的流程示意图,与上述图4所示的第一实施例相比,区别在于:在步骤S43之后还包括:

步骤S51:在芯板的一侧设置第一线路板,及在芯板远离第一线路层的一侧设置第二线路层;其中,第一线路层包括第一电源信号层及控制信号层,第二线路层包括地线层及第二电源信号层。

在芯板的两侧设置第一线路层及第二线路层。具体地,第一线路层及第二线路层均为在铜层上制作的线路网络。第一电源信号层及控制信号层为分别为第一线路层上的不同的线路网络,地线层及第二电源信号层分别为第二线路层上不同的线路网络。

步骤S52:在所述芯板及所述第一线路层之间设置第一绝缘层,及在所述芯板及所述第二线路层之间设置第二绝缘层。

在芯板及第一线路层之间设置第一绝缘层,以将芯板与第一线路层粘合。在芯板及所述第二线路层之间设置第二绝缘层,以将芯板与第二线路层粘合。具体地,第一绝缘层及第二绝缘层为半固化片,其作为层压时的层间粘结层,具体地,所述半固化片主要由树脂和增强材料组成,在制作多层线路板时,通常采用玻纤布做增强材料,将其浸渍上树脂胶液,再经热处理预烘制成薄片,其加热加压下会软化,冷却后会固化,且具有黏性,在高温压合过程中能将相邻的两层黏合。

请参见图6,为本发明线路板的制作方法的第三实施例的流程示意图,与图4所示的第一实施例相比,区别在于:在步骤S43之后还包括:

步骤S61:在所述芯板的一侧设置第一电源信号层,及在所述芯板远离所述第一电源信号层的一侧设置第二电源信号层。

其中,第一电源信号层及第二电源信号层均位于芯板的两侧,第一电源信号层及第二电源信号层为铜层制作的线路层。

步骤S62:在所述芯板及所述第一电源信号层之间设置第一绝缘层,及在所述芯板及所述第二电源信号层之间设置第二绝缘层。

其中,第一绝缘层及第二绝缘层为半固化片,在此不再赘述。

步骤S63:在所述第一电源信号层远离所述芯板的一侧设置控制信号层,及在所述第二电源信号层远离所述芯板的一侧设置地线层。

其中,控制信号层及地线层同样为铜层制作的线路层。具体地,控制信层位于第一电源信号层的外侧,地线层位于第二电源信号层的外侧。

步骤S64:在所述第一电源信号层及所述控制信号层之间设置第三绝缘层,及在所述第二电源信号层及所述地线层之间设置第四绝缘层。

其中,第四绝缘层及第三绝缘层与第一绝缘层及第二绝缘层相同,均为半固化片,在此不再赘述。

请参见图7,为本发明线路板的制作方法的第四实施例的流程示意图,与上述图5所示的第二实施例及图6所示的第三实施例相比,区别在于,还包括:

步骤S71:在所述第二绝缘层对应所述第一芯片的第一连接端子的位置处设置第一导电孔,在所述第一绝缘层对应所述第二芯片的第二连接端子的位置处设置第二导电孔,及在所述第一芯片及所述第二芯片之间设置贯穿所述芯板、所述第一绝缘层及所述第二绝缘层的第三导电孔,以将所述第一芯片的第一连接端子与所述第二芯片的第二连接端子连接。

通过连接第一芯片的第一连接端子及第二电源信号层的第一导电孔、连接第二芯片的第二连接端子及第一电源信号层的第二导电孔及连接第二电源信号层及第一电源信号层的第三导电孔将第一芯片的第一连接端子与第二芯片的第二连接端子连接,以使第一芯片及第二芯片形成相互串联的芯片组。

步骤S72:在所述第一绝缘层对应所述第一芯片的第二连接端子的位置处设置第五导电孔,以将所述第一芯片的所述第二连接端子与所述第一电源信号层连接;及在所述第二绝缘层对应所述第二芯片的第一连接端子的位置处设置第六导电孔,以将所述第二芯片的所述第一连接端子与所述地线层连接。

第五导电孔将第一芯片的第二连接端子与第一电源信号层连接,第六导电孔将第二芯片的第一连接端子与地线层连接,以将芯片组相互并联。

步骤S73:在所述第一绝缘层对应所述第一芯片及所述第二芯片的第三连接端子的位置处设置第四导电孔,以将所述第一芯片及所述第二芯片的第三连接端子与所述控制信号层连接。

第四导电孔将第一芯片及所述第二芯片的第三连接端子与所述控制信号层连接。

本发明提供的线路板及其制作方法,通过将多个芯片阵列排布且埋入在线路板中,以实现线路板的轻薄化及小型化。且使多颗芯片在线路板中有规律的进行串联及并联,以使信号传输距离短,减少信号的损失。

以上仅为本申请的实施方式,并非因此限制本申请的专利范围,凡是利用本申请说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本申请的专利保护范围内。

- 孔连接层的制作方法、线路板的制作方法及线路板

- 单层线路板、高层线路板及高层线路板的制作方法