用于释放薄膜的应力的原位高功率植入

文献发布时间:2023-06-19 09:30:39

技术领域

本公开的实施例通常关于制造集成电路。更具体而言,本文所描述的实施例提供了沉积用于图案化应用的高密度膜的技术。

背景技术

硬模用于制造NAND和动态随机存取存储器(dynamic random access memory;DRAM)装置。硬模通常用作在光刻图案化时的牺牲层,并且能够经由蚀刻工艺将特征图案化到半导体器件的一个或多个材料层上。例如,图案化的特征可以形成晶体管和互连,该晶体管和互连允许NAND和DRAM装置操作。

例如,硬模材料的一些重要性质是抗蚀刻性和压缩应力。当与待蚀刻的层(在下文中为“下层”)相比时,理想的硬模对在蚀刻工艺中使用的蚀刻剂具有高的抗蚀刻性。由此,可以比硬模快得多的速率蚀刻下层。理想的硬模也具有低压缩应力。较低压缩应力消除在硬模沉积之后不期望的基板弯曲,这可使装置制造进一步变得困难。

为了改进硬模的蚀刻选择性,已经开发了高密度碳膜和掺杂的碳膜。利用这些新膜的挑战中的一个是高密度碳膜呈现高压缩应力,这导致不期望的基板弯曲。

由此,在本领域中需要改进的形成硬模的方法,该方法呈现增加的蚀刻选择性,同时维持或减少硬模材料的压缩应力。

发明内容

本公开的实施例通常关于沉积用于图案化应用的高密度膜的技术。在一个实施例中,提供了一种处理基板的方法。所述方法包括:在形成在基板上的膜堆叠上方沉积碳硬模,其中基板经定位在处理腔室中设置的静电夹盘上;将离子植入碳硬模,其中沉积碳硬模和将离子植入碳硬模在相同处理腔室中执行;以及以循环方式重复沉积碳硬模和将离子植入碳硬模,直至达到预定厚度的碳硬模。

在另一实施例中,提供了一种处理基板的方法。所述方法包括:在基板上方沉积碳硬模,其中碳硬模是通过将RF偏压施加到静电夹盘以产生等离子体来沉积,所述基板定位在所述静电夹盘上;以及在基板上方沉积碳硬模时,使用RF偏压将离子从等离子体植入碳硬模,其中沉积碳硬模和将离子植入碳硬模同时在相同处理腔室中执行。

在又一实施例中,提供了一种处理基板的方法。所述方法包括:通过将具有第一功率水平的第一RF功率经由第一电极施加到静电夹盘,在基板上形成的膜堆叠上方沉积类金刚石碳硬模,其中基板经定位在静电夹盘上,在所述静电夹盘中设置第一电极;将离子植入类金刚石碳硬模,其中沉积类金刚石碳硬模和将离子植入类金刚石碳硬模在相同处理腔室中执行;以循环方式重复沉积类金刚石碳硬模和将离子植入类金刚石碳硬模,直至达到预定厚度的类金刚石碳硬模;图案化类金刚石碳硬模;使用图案化的类金刚石碳硬模蚀刻膜堆叠;以及移除类金刚石碳硬模。

附图说明

为了能够详细理解本公开的上述特征所用方式,可参考实施例进行对上文简要概述的本公开的更具体描述,一些实施例在附图中示出。然而,将注意,附图仅示出本公开的典型实施例,并且由此不被认为限制其范围,因为本公开可允许其他同等有效的实施例。

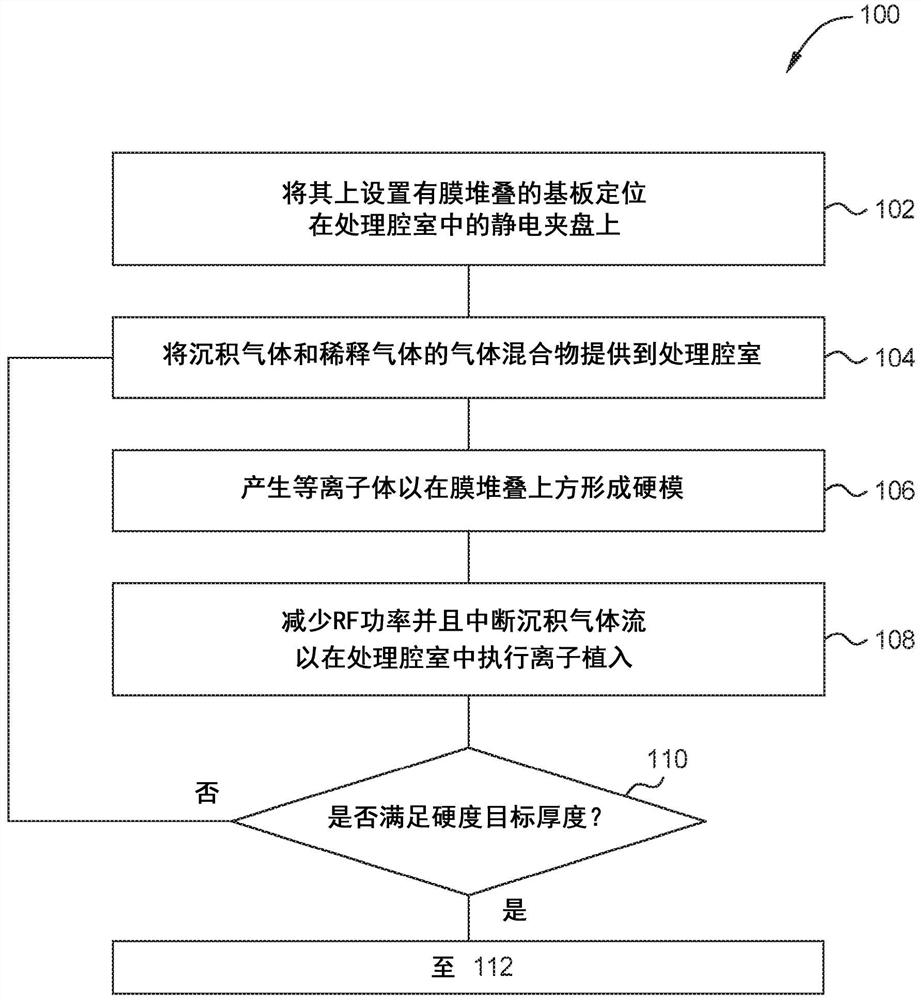

图1A和图1B是阐述根据本公开的实施例的用于在膜堆叠上形成硬模的方法的流程图。

图2A至图2F是示出根据图1A和图1B的方法的硬模形成顺序的堆叠的示意性横截面图。

图3A和图3B是阐述根据本公开的实施例的用于在膜堆叠上沉积硬模的方法的流程图。

图4是描绘对于根据本公开的一个或多个实施例形成的类金刚石碳层的(1)应力随偏压功率的变化以及(2)密度随偏压功率的变化的图。

图5是描绘对于根据本公开的一个或多个实施例形成的类金刚石碳层的应力随植入剂量变化的图。

图6是可用于实践本文阐述的方法的示例性处理的示意性横截面图。

为了便于理解,在可能的情况下,已使用相同附图标记标识图中共有的相同组件。可以预期,一个实施例的组件及特征可有利地并入其他实施例中,而无需进一步叙述。

具体实施方式

本文所描述的实施例包括改进的制造碳膜的方法,该碳膜具有高密度(例如,>1.8g/cc)、高模量(例如,>150GPa)、和低应力(例如,<-500MPa)。具体而言,公开了用于在沉积腔室中形成具有增加的硬度和降低的应力的高密度碳膜的原位沉积植入工艺。原位沉积植入工艺可以循环或同时方式执行以允许形成具有任何目标厚度而不限于离子穿透阈值的碳膜,若异位执行沉积和植入工艺,则会另外遇到目标厚度限于离子穿透阈值的情况。根据本文所描述的实施例制造的碳膜本质上是非晶的,并且与常规图案化膜相比,具有较高蚀刻选择性和非常大的模量(例如,>150GPa)以及较低应力(<-500MPa)。根据本文所描述的实施例制造的碳膜不仅具有低应力,还具有高sp

尽管在本公开中论述了高密度碳膜,可以预期,本公开的各个实施例也可以用于改进任何膜的膜应力、密度、或杨氏模量。此外,可以预期本公开的方面可用于利用硬模或保护性牺牲层的任何沉积工艺或图案化方案,诸如自对准的三重图案化(self-alignedtriple patterning;SATP)工艺、自对准的四重图案化(self-aligned quadruplepatterning;SAQP)工艺、通孔/孔收缩工艺、后道工艺(back end of line;BEOL)等等,如在各个半导体工艺(诸如NAND快闪应用、DRAM应用、或CMOS应用等等)中采用的。

本文所描述的实施例将在下文参考PECVD工艺描述,该工艺可以使用任何适当薄膜沉积系统执行。适当系统的示例包括可使用

图1A和图1B是阐述根据本公开的实施例的用于在基板上设置的膜堆叠上形成硬模的方法100的流程图。图2A至图2F是示出根据方法100的硬模形成顺序的堆叠200的示意性横截面图。硬模可以是上文描述的类金刚石碳层,并且可以用于在三维半导体器件的膜堆叠中制造类阶梯结构、或任何适当的装置制造应用。也应当理解,在图1A和图1B中描绘的操作可同时执行和/或以与图1A和图1B中描绘的顺序不同的顺序执行。

方法100通过将堆叠(诸如图2A描绘的堆叠200)定位到处理腔室(诸如PECVD腔室)中而开始于操作102。堆叠200可定位在PECVD腔室中设置的静电夹盘上。然而,任何适当的基板支撑件可用于替换静电夹盘。一旦堆叠200定位在静电夹盘上,将夹持电压(恒定或脉冲)施加到静电夹盘以将基板202夹紧到静电夹盘。堆叠200包括基板202和设置于其上的一层或多层。在如图所示的示例中,基板202其上设置有膜堆叠204。根据需要,基板202可以是硅基材料或任何适当绝缘材料或导电材料。例如,基板202可以是以下材料,诸如结晶硅(例如,Si<100>或Si<111>)、氧化硅、应变硅、锗硅、掺杂或未掺杂的多晶硅、掺杂或未掺杂的硅基板、以及图案化或未图案化的绝缘体上硅(silicon on insulator;SOI)、碳掺杂的氧化硅、氮化硅、掺杂硅、锗、砷化镓、玻璃、蓝宝石。基板202可具有各种尺寸,诸如200mm、300mm、及450mm或其他直径,以及矩形或方形平板形状。除非另外提及,否则本文描述的实施例和示例是在具有200mm直径、300mm直径、或450mm直径的基板上进行。在其中SOI结构用于基板202的实施例中,基板可包括在硅结晶基板上设置的嵌入介电层。在本文描绘的实施例中,基板202可以是结晶硅基板。

膜堆叠204可以是单层或数个垂直堆叠的层。例如,膜堆叠204可包括在膜堆叠204中重复形成的多对第一层(未图示)和第二层(未图示)。该对包括重复形成的交替的第一层和第二层,直至达到期望数量的多对第一层和第二层。膜堆叠204可以是半导体芯片(诸如三维存储器芯片)的一部分。在一个实施例中,膜堆叠204用于形成三维存储器芯片的多个栅极结构。在这种情况下,在膜堆叠204中形成的第一层可以是第一介电层,并且在膜堆叠204中形成的第二层可以是第二介电层。用于第一层和第二层的适当介电层可包括氧化硅、氮化硅、氮氧化硅、碳化硅、碳氧化硅、氮化钛、氧化物和氮化物的复合物、把氮化物层夹在中间的至少一个或多个氧化物层、及其组合等等。在一些实施例中,第一和第二介电层的一者或两者可以是具有大于4的介电常数的高介电常数材料。高介电常数材料的适当示例包括二氧化铪(HfO

在操作102期间,可调节若干工艺参数。在适于处理300mm基板的一个实施例中,处理容积中的处理压力可维持在约0.1mTorr至约10Torr(例如,约2mTorr至约50mTorr;或约5mTorr至约20mTorr)。处理温度和/或基板温度可维持在约-50摄氏度至约350摄氏度(例如,约0摄氏度至约50摄氏度;或约10摄氏度至约20摄氏度)。

在操作104处,使含烃气体流入处理腔室中。含烃气体可穿过气体分配组件(设置在静电夹盘上方的处理腔室顶部)或经由处理腔室的侧壁流入处理腔室中。含烃气体可包括至少一种烃化合物。烃化合物可以为任何液体或气体。在一个实施例中,烃化合物是气态烃。在另一实施例中,烃化合物可最初为液体,并且可经由汽化器或起泡器、或其他液体前驱物传递系统传递到处理容积。

在一个实施例中,烃化合物具有通式C

在一个实施例中,烃化合物是芳香族烃化合物,诸如苯、苯乙烯、甲苯、二甲苯、乙苯、苯乙酮、苯甲酸甲酯、乙酸苯酯、苯酚、甲酚、呋喃、及类似者,α-萜品烯、甲基异丙基苯、1,1,3,3-四甲基丁基苯、第三丁醚、第三丁基乙烯、甲基丙烯酸甲酯、和第三丁基糠基醚,具有化学式C

在一些实施例中,惰性气体(诸如氩气(Ar)和/或氦气(He))可与含烃气体一起供应到处理腔室中。其他惰性气体(诸如氮(N

在一些实施例中,含烃气体可进一步包括一种或多种稀释气体。适当的稀释气体可包括但不限于氦(He)、氩(Ar)、氙(Xe)、氢(H

在操作106处,如图2B中所示,等离子体在处理腔室中由气体混合物产生以在膜堆叠204上形成硬模206。可通过将第一RF功率(偏压或电源)施加到静电夹盘来产生等离子体。在约0.4MHz至约300MHz(例如,约11MHz至约60MHz)的频率下,第一RF功率可以是从约1千瓦至约10千瓦。在一个实施例中,以约2千瓦和约13.56MHz的频率提供第一RF功率。可经由在静电夹盘中设置的第一电极将第一RF功率从RF功率产生器提供到静电夹盘。在一些情况中,第一电极也可与夹持电源电连通,夹持电源提供直流(direct current;DC)功率以将基板202静电固定到静电夹盘的上表面。

另外或替代地,第一RF功率可施加到上部电极,诸如在与静电夹盘相对的处理腔室的顶部设置的喷头。在一些实施例中,第一RF功率可施加到上部电极、底部电极(例如,第一电极)、和围绕处理腔室的一部分的ICP线圈中的至少一者。ICP线圈可用于形成等离子体或调谐处理腔室内的等离子体的均匀性。取决于供电方案,顶部电极、底部电极、和ICP线圈可同时供电,或该三者中的两者可同时供电。所施加的RF频率可以在从数百kHz至数十MHz的范围内。多个频率也可以施加到顶部电极或底部电极以优化离子通量和入射到基板上的能量。

在一个实施例中,硬模206是如上文论述的类金刚石碳膜。硬模206可通过在膜堆叠204上方的毯覆式沉积工艺来沉积。注意到,在基板202上存在或不存在膜堆叠204的情况下,硬模206可在基板202的任何表面或任何部分上形成。在一些实施例中,在操作104和106期间维持在操作102期间建立的处理条件。在一个实施例中,在形成硬模206期间的处理腔室的压力维持在约2mTorr至约20mTorr。

在操作108处,如图2C中所示,在处理腔室中执行离子植入工艺以处理硬模206。在一个实施例中,离子植入工艺在执行硬模206的沉积工艺(即,操作106)的相同处理腔室中原位执行。在操作108期间,中断含烃气体的流动,同时可维持在操作104期间供应的惰性气体和/或稀释气体。同时,在操作106期间施加到静电夹盘的第一RF功率减少到足以维持等离子体的最小水平(即,在操作106和108期间等离子体是连续的)。例如,第一RF功率可从约2千瓦减小到约200瓦。

离子植入工艺是通过植入离子来执行,该离子为诸如来自惰性气体的连续流的离子、以及来自仍余留在等离子体中的含烃气体的离子。在一些实施例中,使用直流(directcurrent;DC)偏压将离子植入硬模206。DC偏压覆盖在降低的第一RF功率之上。特定而言,DC偏压将高单能离子驱动到硬模206中。可经由第二电极将DC偏压提供到静电夹盘。第二电极可设置在静电夹盘中并且与DC电源电气连通,该DC电源将偏压提供到第二电极。或者,可将DC偏压从夹持电源提供到第一电极。在任何情况下,DC偏压可在约2千伏与约15千伏之间。在一个实施例中,DC偏压在约5千伏与约12千伏之间,例如约8千伏。由于DC偏压是高的,DC偏压可以在离子植入工艺期间脉冲化。在各个实施例中,DC偏压的脉冲宽度可以是约1微秒至约1毫秒的数量级。在一些实施例中,在10Hz至约10kHz的脉冲频率下施加DC偏压,其中脉冲宽度为约5微秒至约30毫秒。

在一些实施例中,使用第二RF功率(偏压或电源)将离子植入硬模206。同样,第二RF功率覆盖在降低的第一RF功率之上。可经由在静电夹盘中设置的第三电极将第二RF功率从RF功率产生器提供到静电夹盘。在约0.4MHz至约300MHz(例如约11MHz至约60MHz)的频率下,第二RF功率可以是从约1千瓦至约10千瓦。在一个实施例中,以约2千瓦和约13.56MHz的频率提供第一RF功率。第二RF功率可以在离子植入工艺期间脉冲化。例如,第二RF功率可以以约10%至约80%的范围中的工作周期脉冲化,其中频率为约1Hz至约50kHz。

在使用第二RF功率并且沉积物质也用作植入物质(例如,来自含烃气体的H

无论离子植入工艺是使用DC偏压还是第二RF功率,因为关闭沉积气体(即,含烃气体)的流动,将几乎不发生或不发生硬模206的沉积。由此,DC偏压的脉冲或脉冲化的第二RF功率将沉积阶段和处理阶段(即,离子植入工艺)分开,从而使硬模206的形成和处理成为循环的沉积-处理工艺。在离子植入工艺期间,来自惰性气体的连续流的离子(诸如氩或氦离子)以及来自余留在等离子体中的含烃气体的离子由DC偏压或第二RF功率吸引或驱动,并且向前移动到硬模206。DC偏压或第二RF功率用于通过用离子撞击硬模206的表面来处理硬模206。因此,沉积的硬模206中的应力减少。

可执行离子植入工艺,直至植入离子达到穿透阈值,这归因于随着植入离子穿过硬模206行进,植入的离子逐渐失去能量。穿透阈值可由离子的穿透深度决定。或者,可执行离子植入工艺,直至达到预定的植入深度。预定的植入深度或离子穿透阈值可以在10纳米与1微米之间的范围中,这可取决于离子的类型和大小以及用于激发离子207的偏压而变化。

取决于期望的植入深度,植入能量可在约0.5keV与约60keV之间,例如约6keV至约45keV。离子剂量可在从约1x10

因为植入工艺在发生硬模沉积的相同处理腔室中发生,原位沉积-植入工艺是有利的。由此,可以沉积并处理硬模206,而不必破坏真空并且转移到异位植入工具。因此,改进总产量并且降低与异位植入工具相关联的成本。此外,由于植入离子具有穿透阈值,可异位处理的硬模的厚度受限。利用原位沉积/离子植入工艺,硬模的沉积和处理可以循环方式执行以在相同处理腔室中将硬模定制为可能地任何目标厚度。

在操作110处,作出决策,来确定已经处理的沉积的硬模206是否达到目标厚度。硬模206可具有对应于膜堆叠204的后续蚀刻要求的目标厚度。在一个示例中,硬模206的目标厚度在约0.5μm与约1.5μm之间,诸如约1.0μm。如果尚未达到硬模206的目标厚度,可在将经处理的硬模206的厚度再次与目标厚度进行比较之前执行沉积/离子植入工艺的另一循环(例如,操作104、106和108)。在植入离子达到预定植入或穿透深度但硬模206尚未达到期望厚度的一些实施例中,可以在将经处理的硬模206的厚度再次与目标厚度进行比较之前执行沉积/离子植入工艺的另一循环(例如,操作104、106和108)。重复原位硬模沉积和离子植入的循环工艺直至沉积的硬模206达到目标厚度。

在操作112处,一旦硬模206达到目标厚度,如图2D所示,在经处理的硬模206上方形成图案化的光刻胶层208。可利用能量源(诸如光能量)将特征或图案从光掩模转移到光刻胶208。在一个实施例中,光刻胶是聚合材料,并且图案化工艺通过193nm浸渍式光刻工艺或其他类似光刻工艺执行。类似地,激光也可用来执行图案化工艺。

在操作114处,如图2E中所示,经处理的硬模206通过例如光刻和一个或多个蚀刻工艺来图案化,以将特征从光刻胶208转移到硬模206。蚀刻工艺可在任何适当的蚀刻腔室(诸如等离子体蚀刻腔室)中执行。其后,光刻胶层208通过任何适当的工艺移除,诸如灰化工艺或湿式蚀刻工艺。

在操作116处,如图2F中所示,使用图案化的硬模206蚀刻膜堆叠204。膜堆叠204的蚀刻可在任何适当处理腔室(诸如等离子体蚀刻腔室)中执行。蚀刻剂(诸如氟碳)可用于移除膜堆叠204的暴露部分。蚀刻剂的活性物质是选择性的,使得该活性物质实质上不与硬模206的植入离子反应。因此,蚀刻剂对膜堆叠204具有选择性。蚀刻剂的适当示例可包括但不限于CF

图3A和图3B示出了根据本公开的实施例的用于在基板上设置的膜堆叠上沉积硬模的方法300的流程图。如图2A至图2F中所示,方法300可以用于处理堆叠200。由此,将关于图2A至图2F描述方法300。同样,沉积的硬模可以是如上文描述的类金刚石碳层,并且可以用于在膜堆叠中制造类阶梯结构,用于三维半导体器件或任何适当的装置制造应用。也应当理解,图3A和图3B中描绘的操作可同时执行和/或以与图3A和图3B中描绘的顺序不同的顺序执行。

方法300的操作302和304类似于操作102和104,并且因此出于简洁起见将不再描述。因此,如图2A所示,由在基板202上方沉积的膜堆叠204形成形成堆叠200。在操作306处,如图2B所示,硬模沉积和离子植入处理的同时工艺在处理腔室中执行以在膜堆叠204上形成硬模206。同时工艺可通过在处理腔室中由气体混合物(例如,含烃气体和惰性气体/稀释气体)产生等离子体来执行,以在膜堆叠204上方形成一层硬模206。等离子体可通过将高压RF偏压施加到静电夹盘而在基板水平处产生。在约0.4MHz至约300MHz(例如约11MHz至约60MHz)的频率下,高压RF偏压可在从约1千瓦至约15千瓦的范围中。在一个实施例中,以约8千瓦和约13.56MHz的频率提供高压RF偏压。可经由静电夹盘中设置的第三电极将高压RF偏压从RF功率产生器提供到静电夹盘。

在膜堆叠204上方沉积硬模206时,施加到静电夹盘的高压RF偏压也可以用作植入能量以从朝向生长的硬模206移动的气体混合物(即,含烃气体、惰性气体/稀释气体)吸引离子。由此,如图2C中所示,硬模206的离子植入处理与硬模沉积同时执行。离子由高压RF偏压吸引和加速以撞击硬模206的表面,由此减少硬模206的应力。

在一些实施例中,DC偏压可额外施加到静电夹盘以促进离子植入处理。来自气体混合物(即,含烃气体、惰性气体/稀释气体)的离子可以由DC偏压吸引和加速以撞击硬模206的表面,由此减少硬模206的应力。如上文关于图1A和图1B所论述,可以经由第二电极将DC偏压提供到静电夹盘,该第二电极可设置在静电夹盘中并且与DC电源电气连通。或者,可将DC偏压从夹持电源提供到第一电极。偏压可在约1千伏与约15千伏之间。在一个实施例中,DC偏压在约2千伏与约6千伏之间。在另一实施例中,偏压在约8千伏与约10千伏之间。类似于操作108,取决于期望的植入深度,植入能量可在约0.5keV与约60keV之间,例如约6keV至约45keV。离子剂量可在从约1x10

在任何情况下,气体混合物(例如,含烃气体及惰性气体/稀释气体)的流动在整个操作308中是连续的。由此,用于硬模沉积的沉积物质(例如,碳、氢等等的离子或中性物质)也可以用作离子植入处理的植入物质。如与硬模沉积和离子植入工艺由短工作周期RF或脉冲DC电压分开的实施例相比,硬模沉积和离子植入处理的原位工艺实现同时且更有效地沉积和处理硬模206。

在操作308处,作出决策以确定沉积/处理的硬模206是否达到目标厚度。硬模206可具有对应于膜堆叠204的后续蚀刻要求的目标厚度。在一个示例中,硬模206的目标厚度在约0.5μm与约1.5μm之间,诸如约1.0μm。若尚未达到硬模206的目标厚度,则可在将处理的硬模206的厚度再次与目标厚度进行比较之前执行沉积/离子植入工艺的另一循环(例如,操作304和306)。重复硬模沉积和离子植入处理的原位同时工艺,直至沉积/处理的硬模206达到目标厚度。

操作310、312、314和316类似于操作112、114、116和118,并且因此出于简便缘故将不描述。

图4是描绘对于根据上文关于图3A和图3B论述的一个或多个实施例形成的类金刚石碳层(例如,硬模)的(1)应力随偏压功率变化(由方形表示)以及(2)密度随偏压功率变化(由点表示)的图400。x轴表示偏压功率(瓦),并且y轴表示沉积膜的密度(g/cc)。如图4中示出,通常,随着偏压功率增加,所沉积膜的密度增加。特定而言,类金刚石碳层的应力在较高RF功率/离子能量下是较低的。

图5是描绘对于根据本公开的一个或多个实施例形成的类金刚石碳层(例如,硬模)的应力随植入剂量变化的图500。图500描绘了所沉积和使用约35keV的植入能量来后离子植入的类金刚石碳膜的应力数据。x轴表示沉积膜的应力(MPa),并且y轴表示植入剂量(A.U.)。如图5中示出,所沉积膜的应力在离子植入处理之后显著降低。

图6是可用于实践本文阐述的方法的任一个或组合的示例性处理的示意性横截面图。处理腔室600包括腔室盖组件601、一个或多个侧壁602和腔室底部604。腔室盖组件601包括腔室盖606、设置在腔室盖606中的喷头607以及设置在腔室盖606与一个或多个侧壁602之间的电气绝缘环608。喷头607、一个或多个侧壁602和腔室底部604一起限定处理容积605。穿过腔室盖606设置的进气口609流体耦接到气源610。穿过其中设置有多个开口611的喷头607用于将处理气体从气源610均匀地分配到处理容积605中。喷头607电气耦接到第一电源供应器612,诸如RF电源供应器,该电源供应器经由与其的电容耦接来供应功率以点燃并且维持处理气体的等离子体613。在其他实施例中,处理腔室600包含电感等离子体产生器,并且经由将RF功率电感耦接到处理气体来形成等离子体。

处理容积605经由真空出口614流体地耦接到真空源,诸如耦接到一个或多个专用真空泵,该真空出口将处理容积605维持在低大气条件下并且从该处理容积抽空处理气体和其他气体。在处理容积605中设置的基板支撑件615设置在可移动支撑轴616上,该可移动支撑轴密封地穿过腔室底部604(诸如由波纹管(未图示)围绕)在腔室底部604下方的区域中延伸。在本文中,处理腔室600经常规地配置以促进穿过在一个或多个侧壁602的一者中的开口618将基板617转移到基板支撑件615并且从基板支撑件615转移基板617,在基板处理期间该开口常规地用门或阀(未图示)密封。

在本文中,使用加热器(诸如电阻式加热组件619)和在基板支撑件615中设置的一个或多个冷却通道620中的一者或两者将在基板支撑件615上设置的基板617维持在期望的处理温度下。通常,一个或多个冷却通道620流体耦接到冷却剂源(未图示),诸如修改的具有相对高的电阻的水源或冷却剂源。在一些实施例中,基板支撑件615或其一个或多个电极621电气耦接到第二电源供应器622,诸如连续波(continuous wave;CW)RF电源供应器或脉冲RF电源供应器,该电源供应器向其供应偏压。

处理腔室600进一步包括系统控制器630,该系统控制器用于控制处理腔室600的操作并且实施本文阐述的方法。系统控制器630包括可编程中央处理单元,在本文中为中央处理单元(CPU 631),其可与存储器632(例如,非易失性存储器)和支持电路633一起操作。支持电路633耦接到CPU 631并且包含耦接到处理腔室600的各种部件的高速缓存、时钟电路、输入/输出子系统、电源供应器及其组合以促进其控制。CPU 631是用于控制处理腔室600的各种部件和子处理器的任何形式的通用计算机处理器的一者,诸如可编程逻辑控制器(programmable logic controller;PLC)。耦接到CPU 631的存储器632是非暂时性的,并且通常为容易获得的存储器中的一者或多者,诸如随机存取存储器(random accessmemory;RAM)、只读存储器(read only memory;ROM)、软盘驱动、硬盘、或任何其他形式的数字存储器(本地或远程)。

典型地,存储器632是呈含有指令的计算机可读取存储介质(例如,非易失性存储器)的形式,当由CPU 631执行时,该指令促进处理腔室600的操作。存储器632中的指令是呈程序产品的形式,诸如实施本公开的方法的程序。程序代码可符合数个不同程序化语言的任一种。在一个示例中,本公开可实施为在计算机可读取存储介质上存储的与计算机系统一起使用的程序产品。程序产品的程序定义实施例(包括本文描述的方法)的功能。

因此,提供了用于形成类金刚石碳硬模层的方法,该硬模层可用于形成半导体器件。通过利用原位硬模沉积离子植入工艺,硬模层可经沉积和处理,而不必破坏真空并且转移到异位植入工具。因此,改进总产量并且降低与异位植入工具相关联的成本。另外,硬模的沉积和处理可使用独立的等离子体源或一个高功率(高压)等离子体源以循环或同时的方式执行,来在相同处理腔室中将硬模定制为可能的任何目标厚度。此外,植入离子用于增加硬模的机械完整性和密度,同时维持或降低硬模的内部应力。硬模的增加的机械完整性和密度在蚀刻硬模之后降低线性弯曲,并且硬模的维持或降低的应力降低或消除不期望的基板弯曲或变形。总而言之,增加了硬模的蚀刻选择性。

尽管上述内容针对本公开的实施例,但是可在不脱离本公开的基本范围的情况下设计本公开的其他及进一步的实施例,并且其范围由以下权利要求书决定。

- 用于释放薄膜的应力的原位高功率植入

- 一种用于透射电镜原位加电场和应力的薄膜样品制备方法