处理器电路以及数据处理方法

文献发布时间:2023-06-19 11:57:35

技术领域

本公开内容涉及数据处理技术,尤指一种可减少载入指令所涉及的载入使用停滞的处理器电路及数据处理方法。

背景技术

为了减少从较低速之存储器存取数据或指令的时间,现今的中央处理单元均采用快取(cache)机制。借由适当的设计,快取机制通常可在几个时钟周期内获得所需的数据或指令,大幅提升系统性能。然而,在中央处理单元依序处理载入指令及加法指令的情形下,当该加法指令所需的数据为该载入指令欲读取的数据时,由于从本地存储器(或快取存储器,诸如静态随机存取存储器(static random access memory,SRAM))存取该欲读取的数据需要一段时间,因此,中央处理单元仍需等待几个时钟周期才能执行该加法指令。也就是说,现有采用快取机制的中央处理单元仍会发生载入使用(load-use)停滞(stall)的问题。

发明内容

有鉴于此,本公开的实施例提供一种可减少载入指令所涉及的管线停滞的问题,不管此载入指令是快取命中(hit)或是快取失误(miss)。

本公开的某些实施例包含一种处理器电路。该处理器电路包含指令解码单元、指令检测器、地址生成器以及数据缓冲器。该指令解码单元用以解码载入指令以产生解码结果。该指令检测器耦接于该指令解码单元,用以检测该载入指令是否处于载入使用情境。该地址生成器耦接于该指令解码单元,用以根据该解码结果产生该载入指令所要求的第一地址。该数据缓冲器耦接于该指令检测器以及该地址生成器,用以在该指令检测器检测出该载入指令处于该载入使用情境时,存储该地址生成器所产生的该第一地址,以及根据该第一地址存储该载入指令所要求的数据。

本公开的某些实施例包含一种数据处理方法。该数据处理方法包含以下步骤:接收载入指令,并检测该载入指令是否处于载入使用情境;对该载入指令进行解码以产生解码结果;根据该解码结果产生该载入指令所要求的第一地址;当检测出该载入指令处于该载入使用情境时,将该第一地址存储于数据缓冲器;以及根据该第一地址将该载入指令所要求的数据存储于该数据缓冲器。

附图说明

参照附图来阅读下文的实施方式,可清楚地理解本公开的多种形式。应注意到,根据本领域的标准惯例,附图中的各种特征并不一定是按比例进行绘制的。事实上,为了能够清楚地描述,可任意放大或缩小某些特征的尺寸。

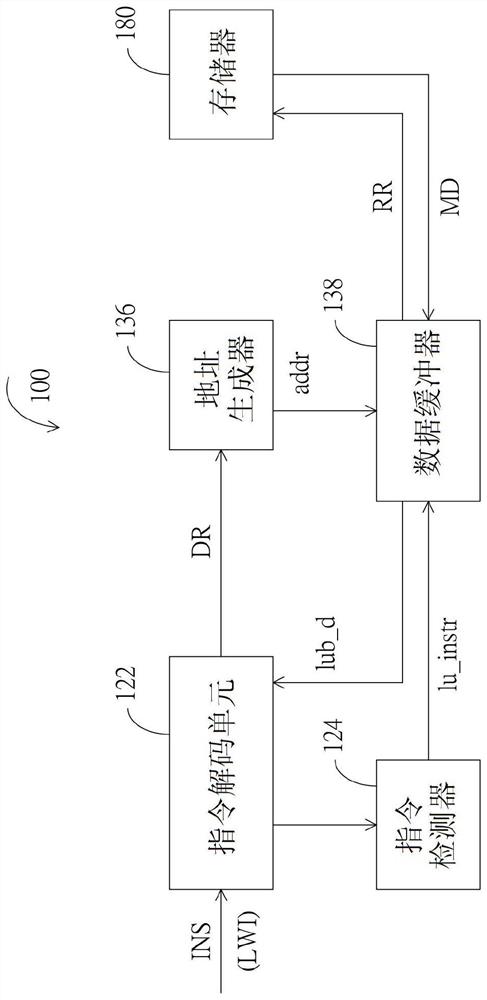

图1是依据本公开某些实施例之处理器电路的功能块示意图。

图2是图1所示之处理器电路之实施方式的示意图。

图3是图2所示之指令检测器所涉及的指令检测操作之实施方式的示意图。

图4是图2所示之数据缓冲器之实施方式的示意图。

图5示出了图2所示之处理器电路所涉及之用以处理存储器存取指令的数据处理方法的实施例的流程图。

图6示出了图2所示之处理器电路所涉及之用以处理存储器存取指令的数据处理方法的另一实施例的流程图。

图7示出了图4所示之存储空间在连续多个时钟周期中各自存储的信息的示意图。

图8是依据本公开的数据处理方法的实施例的流程图。

具体实施方式

以下公开内容提供了多种实施方式或例示,其能用以实现本公开内容的不同特征。下文所述之元件与配置的具体例子用以简化本公开内容。应该理解,这些叙述仅为例示,其本意并非用于限制本公开内容。举例来说,若将一元件描述为与另一元件「连接(connected to)」或「耦接(coupled to)」,则两者可直接连接或耦接,或两者之间可能出现其他中间(intervening)元件。

此外,本公开内容可能会在多个实施例中重复使用元件符号和/或标号。此种重复使用乃是基于简洁与清楚的目的,其本身不代表所讨论的不同实施例和/或组态之间的关系。再者,应该理解,本公开的实施例提供了许多可应用的概念,其可广泛地实施于各种特定场合。以下所讨论的实施例仅供说明的目的,并非用来限制本公开的范围。

通过提早准备待处理指令所需的数据,本公开的数据处理方案可减少/避免因为执行该待处理指令所造成的载入使用停滞。例如,在依序处理载入指令及加法指令的情形下,本公开的数据处理方案可提早准备该加法指令所需的数据(包含该载入指令所要求的数据),而无需等待该载入指令的执行结果回传,即可成功地执行该加法指令。进一步的说明如下。

图1是依据本公开某些实施例之处理器电路100的功能块示意图。处理器电路100可用来减少/避免因为执行指令串流(instruction stream)之中某一或某些指令所造成的载入使用停滞。处理器电路100可包含(但不限于)指令解码单元122、指令检测器124、地址生成器136以及数据缓冲器138。指令解码单元122用以解码指令串流INS之中彼此连续的多个指令,并可依序输出该多个指令各自的解码结果。例如,指令解码单元122可对指令串流INS之中的载入指令LWI进行解码,以产生解码结果DR。又例如,指令解码单元122可对指令串流INS之中其他的指令(诸如存储指令或运算指令)进行解码,以产生相应的解码结果。

指令检测器124耦接于指令解码单元122,用以检测指令串流INS之中是否包含处于载入使用情境的一个或多个载入指令,其中当载入指令处于该载入使用情境时,该载入指令可能会造成载入使用停滞。例如,指令检测器124可接收暂存于指令解码单元122的指令串流INS,进而对指令串流INS进行检测。又例如,指令检测器124可无需通过指令解码单元122,而直接接收指令串流INS以进行检测。

在此实施例中,处于该载入使用情境的载入指令可包含载入使用指令(load-useinstruction),其可能会导致在执行后续指令时产生载入使用停滞。例如,当指令检测器124检测出载入指令LWI为载入使用指令时,这代表了若处理器电路100使用载入指令LWI的执行结果来执行指令串流INS之中位于载入指令LWI之后的指令,将会造成载入使用停滞。在此实施例中,指令检测器124可判断出使用载入指令LWI的执行结果来执行该指令是否会发生载入使用数据风险(load-use data hazard)。当判断出使用载入指令LWI的执行结果来执行该指令会发生载入使用数据风险时,指令检测器124可检测出载入指令LWI为载入使用指令。

此外,指令检测器124可输出指示信号lu_instr,其可指示出指令解码单元122当前所处理的指令是否为一个处于该载入使用情境的载入指令。例如,在指令解码单元122当前所处理的指令是载入指令LWI的情形下,指示信号lu_instr可指示出载入指令LWI是否为载入使用指令。

地址生成器136耦接于指令解码单元122,用以根据各指令的解码结果产生该指令所涉及的地址。举例来说,地址生成器136可根据载入指令LWI的解码结果DR产生地址addr,作为载入指令LWI所要求的地址。

数据缓冲器138耦接于指令检测器124以及地址生成器136,用以在指令检测器124检测出载入指令可能会造成载入使用停滞时,存储地址生成器136所产生的该载入指令所要求的地址,并根据该载入指令所要求的地址来存储该载入指令所要求的数据。在此实施例中,当指令检测器124检测出载入指令LWI为载入使用指令时,数据缓冲器138可存储地址生成器136所产生的地址addr,以及根据地址addr存储数据lub_d,作载入指令LWI所要求的数据。

举例来说,在载入指令LWI所要求的数据尚未存储于数据缓冲器138的情形下,数据缓冲器138可发送读取请求RR至存储器180,以读取存储器180中地址addr所指向的数据MD,作为载入指令LWI所要求的数据。在某些实施例中,存储器180可以是处理器电路100的本地存储器或快取存储器。在某些实施例中,存储器180可以是外接于处理器电路100的外部存储器或辅助存储器。

值得注意的是,在处理器电路100需要使用载入指令LWI所要求的数据来执行待处理指令的情形下,由于数据缓冲器138可存储载入指令LWI所要求的数据(诸如数据lub_d),因此,指令解码单元122可从数据缓冲器138取得数据lub_d以供处理器电路100执行该待处理指令,而无需等待存储器180(诸如快取存储器或外部存储器)回传载入指令LWI的执行结果,故可减少/避免因为载入使用停滞。

为方便说明,以下采用具有管线架构的处理器电路来说明本公开的数据处理方案。然而,本公开并不以此为限。将本公开的数据处理方案应用于其他需要先前指令的执行结果以执行后续指令的电路架构,均遵循本公开的精神而落入本公开的范围。

图2是图1所示之处理器电路100之实施方式的示意图。为便于理解,处理器电路200可实施为具有管线架构的管线处理器,其中该管线架构可包含五个管线阶段,其可分別由指令获取阶段(instruction fetch stage)IF、指令解码阶段(instruction decodestage)ID、执行阶段(execution stage)EX、存储器存取阶段(memory access stage)MEM以及写回阶段(write back stage)WB来实施。然而,这并非用来限制本公开的内容。在某些实施例中,这五个管线阶段可由指令获取阶段、指令解码阶段、操作数获取阶段(operandfetch stage)、执行阶段以及写回阶段来实施。在某些实施例中,处理器电路200可单元具有大于或小于五个管线阶段的管线架构。这些设计上的相关变化均遵循本公开的精神。

在此实施例中,处理器电路200可包含图1所示之指令解码单元122、指令检测器124、地址生成器136以及数据缓冲器138。指令解码单元122和指令检测器124可位于同一管线阶段(诸如指令解码阶段ID),而地址生成器136和数据缓冲器138可位于同一管线阶段(诸如执行阶段EX),以减少/避免管线停滞的问题。相关的说明将在稍后描述。

此外,处理器电路200还可包含(但不限于)多个管线寄存器(pipeline register)201~204、指令获取单元210、执行单元232、存储器240、寄存器文件(register file,RF)252以及总线接口单元(bus interface unit,BIU)254。由于管线寄存器201位于指令获取阶段IF与指令解码阶段ID之间,故可称作指令获取/指令解码寄存器(IF/ID register)。相似地,管线寄存器202、管线寄存器203以及管线寄存器204可分別称作指令解码/执行寄存器(ID/EX register)、执行/存储器存取寄存器(EX/MEM register)以及存储器存取/写回寄存器(MEM/WB register)。

指令获取单元210位于指令获取阶段IF,用以存储指令串流INS,并根据程式计数器(program counter)(图2未示)提供的地址,将指令串流INS之中相对应的指令存储至管线寄存器201。

执行单元232位于执行阶段EX,用以根据管线寄存器202所提供之指令的解码结果来执行该指令,以及将该指令的执行结果存储于管线寄存器203,其中该指令的解码结果可包含用于执行该指令所需的地址和数据。在此实施例中,执行单元232可包含(但不限于)算术逻辑单元(arithmetic logic unit,ALU)233及乘法累加单元(multiplier-accumulatorunit,MAC)234。

存储器240位于存储器存取阶段MEM,并可作为图1所示之存储器180之实施方式。例如,存储器240可实施为处理器电路200的快取存储器。在此实施例中,存储器240用以根据管线寄存器203所提供之指令执行结果来进行存储器存取操作。例如,在写入操作中,存储器240可根据该指令执行结果将数据存储于地址addr所指向的位置。又例如,在读取操作中,存储器240可根据该指令执行结果输出地址addr所指向的数据MD1。

寄存器文件252和总线接口单元254均可位于写回阶段WB。寄存器文件252用以存储管线寄存器204所暂存之来自存储器240的数据。总线接口单元254可作为处理器电路200与外部存储器260之间的数据传输接口。在某些实施例中,寄存器文件252另可用来存储欲写入至外部存储器260的数据,或用来存储从外部存储器260读取的数据MD2。

请连同图2参照图3。图3是图2所示之指令检测器124所涉及的指令检测操作之实施方式的示意图。在此实施例中,指令检测器124可接收指令串流INS中先后传送至指令解码单元122的多个指令I0~I6,并将多个指令I0~I6分別暂存于指令检测器124之中的多个存储单元ibuf0~ibuf6。为方便说明,多个指令I0~I6可分別由载入指令load、加法指令add、载入指令load、加法指令add、减法指令sub、载入指令load以及左移逻辑指令sll来实施。指令检测器124可对多个指令I0~I6执行解码操作,以检测载入指令(诸如指令I0、指令I2或指令I5)是否为载入使用指令。

举例来说,在指令I0所要求的数据(存储器240中地址[r8]所指向的数据)从存储器240载入至寄存器r0(位于指令解码单元122中;图2未示)之前,执行于指令I0之后的指令I1(加法指令add)就会进入执行阶段EX,而需要使用寄存器r0的数据。因此,指令检测器124可检测出指令I0为处于载入使用情境的载入使用指令。此外,当指令I0进入执行阶段EX时,指令检测器124可输出具有第一信号电平(诸如高逻辑电平)的指示信号lu_instr,表示指令I0为载入使用指令。

相似地,对于指令I5来说,在指令I5所要求的数据(存储器240中地址[r9]所指向的数据)从存储器240载入至寄存器r2(位于指令解码单元122中;图2未示)之前,执行于指令I5之后的指令I6(左移逻辑指令sll)就会进入执行阶段EX,而需要使用寄存器r2的数据。因此,指令检测器124可检测出指令I5为载入使用指令。

对于指令I2来说,虽然在指令I2之后执行的指令I4所需的数据(指令解码单元122之中寄存器r1存储的数据)来自指令I2所要求的数据(存储器240中地址[r9]所指向的数据),不过,由于在指令I4进入执行阶段EX之前,指令I2所要求的数据已从存储器240载入至寄存器r1,因此,指令检测器124可检测出指令I2并非载入使用指令,并输出具有第二信号电平(诸如低逻辑电平)的指示信号lu_instr。

值得注意的是,图3所示之指令种、顺序及个数只是方便说明的目的,并非用来作为本公开的限制。由于所属领域中具有通常知识者应可了解图3所示之多个指令I0~I6的操作,故各指令的进一步说明在此便不再赘述。

基于上述指令检测操作,指令检测器124可在指令解码阶段ID中检测出载入指令LWI是否为载入使用指令。举例来说,在载入指令LWI是由指令I0或指令I5来实施的情形下,当载入指令LWI进入指令解码阶段ID时,指令检测器124可检测出载入指令LWI为载入使用指令,并输出具有该第一信号电平的指示信号lu_instr。此外,在载入指令LWI是由指令I2来实施的情形下,当载入指令LWI进入指令解码阶段ID时,指令检测器124可检测出载入指令LWI并非载入使用指令,而输出具有该第二信号电平的指示信号lu_instr。

在指令检测器124检测出载入指令LWI是载入使用指令之后,载入指令LWI所要求的数据可由数据缓冲器138在下一管线阶段(执行阶段EX)提供指令解码单元122。因此,在载入指令LWI的下一个指令需要马上使用载入指令LWI所要求的数据的情形下,该下一个指令所需的数据可在该下一个指令处于指令解码阶段ID时即已就绪。

请连同图2参照图4。图4是图2所示之数据缓冲器138之实施方式的示意图。数据缓冲器138可包含(但不限于)存储空间410以及控制电路420。存储空间410可采用触发器(图4未示)作为存储单元,以实现单时钟周期的数据存取。在此实施例中,存储空间410可包含N个入口(entry)E(0)~E(N-1),其分別对应于N个索引值idx(0)~idx(N-1),N为大于1之正整数。各入口可包含(但不限于)有效位元域V、锁定位元域L、标签域TG以及数据域DA。有效位元域V可表示是否有信息存入该入口。N个入口E(0)~E(N-1)于有效位元域V的内容可分別表示为有效位元V(0)~V(N-1)。锁定位元域L可表示该入口是否被锁定,以保护该入口所存储的信息不被修改。N个入口E(0)~E(N-1)于锁定位元域L的内容可分別表示为锁定位元L(0)~L(N-1)。标签域TG可用来识别该入口之数据域DA所存储的数据。例如,标签域TG可指示出该入口所存储的数据在存储器240(或外部存储器260)中的地址。N个入口E(0)~E(N-1)于标签域TG的内容可分別表示为标签TG(0)~TG(N-1)。N个入口E(0)~E(N-1)于数据域DA的内容可分別表示为数据DA(0)~DA(N-1)。

控制电路420包含(但不限于)比较电路422、缓冲器423、选择电路424、逻辑电路426以及控制器428。比较电路422用以将地址addr与标签TG(0)~TG(N-1)分別作比较,以产生命中信号lub_h。举例来说,当地址addr与标签TG(0)~TG(N-1)其中之一相匹配时,命中信号lub_h可具有特定的信号电平(诸如高逻辑电平);当地址addr未与标签TG(0)~TG(N-1)之中任一标签相匹配时,命中信号lub_h可具有另一特定的信号电平(诸如低逻辑电平)。在此实施例中,当命中信号lub_h指示出地址addr与标签TG(i)(i为小于N之自然数)相匹配时,比较电路422可将命中信号lub_h以及标签TG(i)相对应之有效位元V(i)和锁定位元L(i)存储至缓冲器423。

选择电路424可根据命中信号lub_h输出数据DA(0)~DA(N-1)其中之一。例如,当命中信号lub_h指示出地址addr与标签TG(i)(i为小于N之自然数)相匹配时,选择电路424可输出标签TG(i)相对应之数据DA(i),作为数据lub_d。

逻辑电路426可输出有效信号lub_dv,以指示出数据lub_d是否是有效/可用的。举例来说,在命中信号lub_h指示出地址addr与标签TG(i)(i为小于N之自然数)相匹配的情形下,当有效位元V(i)指示出有信息存储于入口E(i),且锁定位元L(i)指示出入口E(i)未被锁定时,有效信号lub_dv可输出具有特定的信号电平(诸如高逻辑电平),表示数据lub_d是有效/可用的。当有效信号lub_dv指示出数据lub_d是有效/可用时,指令解码单元122可从数据缓冲器138取得载入指令LWI所要求的数据(数据lub_d),减少/避免载入使用停滞的问题。

控制器428用以根据指示信号lu_instr选择性地存取存储空间410。举例来说,当指示信号lu_instr指示出载入指令LWI为载入使用指令时,控制器428可根据地址addr存取存储空间410之入口,进而更新该入口之有效位元域V、锁定位元域L、标签域TG和数据域DA至少其一。当指示信号lu_instr指示出载入指令LWI并非载入使用指令时,控制器428可不更改存储空间410所存储的信息。也就是说,存储空间410可以只存储与载入使用指令相关的信息。

值得注意的是,在操作中,控制电路420可以使存储空间410所存储的信息与存储器240所存储的信息(或外部存储器260所存储的信息)维持一致。举例来说,当处理器电路200用以处理存储器存取指令MAI时,指令解码单元122用以解码存储器存取指令MAI以产生解码结果DR’。存储器存取指令MAI可包含(但不限于)用来将数据写入存储器的存储指令,以及用来读取存储器所存储之数据的载入指令。此外,地址生成器136用以根据解码结果DR’产生地址addr,其可为存储器存取指令MAI所要求的地址。控制电路420可检查地址addr是否已存储于存储空间410。当地址addr已存储于存储空间410时,控制电路420可将存储空间410中地址addr所指向的数据,更新为存储器存取指令MAI所要求的数据。因此,指令解码单元122直接从数据缓冲器134所取得的数据与存储于存储器(存储器240或外部存储器260)的数据一致。

图5示出了图2所示之处理器电路200所涉及之用以处理存储器存取指令MAI的数据处理方法的实施例的流程图。在此实施例中,图2所示之处理器电路200所包含的数据缓冲器138可单元图4所示之架构来执行相关的操作。此外,存储器存取指令MAI可由存储指令来实施。

请一并参照图2、图4和图5,在步骤502中,执行阶段EX可开始执行该存储指令。该存储指令用以将写入数据存储于存储器240,其中该写入数据被存储于指令解码单元122之寄存器。在步骤504中,地址生成器136可根据该存储指令的解码结果产生地址addr,亦即该存储指令所要求的地址。地址生成器136可将地址addr输出至数据缓冲器138。

在步骤506中,比较电路422可将地址addr与标签TG(0)~TG(N-1)作比较,以检查地址addr是否已存储于存储空间410。若检查出addr已存储于存储空间410(例如,命中信号lub_h具有低逻辑电平),执行步骤508。若检查出地址addr并未存储于存储空间410(例如,命中信号lub_h具有高逻辑电平),执行步骤512。

在步骤508中,控制器428可将存储空间410中地址addr所指向的入口的数据域DA更新为该写入数据。举例来说,当地址addr与标签TG(i)相匹配时,控制器428可将入口E(i)之数据DA(i)更新为该写入数据。

在步骤510中,控制器428可根据置换策略(replacement policy)更新N个入口E(0)~E(N-1)的存取顺序。举例来说,控制器428可采用最近最少使用(least recentlyused,LRU)之置换策略。因此,控制器428可将最近一次存取的入口E(i)设定为最常使用的入口。在某些实施例中,控制器428可采用非最近使用(not most recently used,NMRU)之置换策略、随机置换策略或其他置换策略。在控制器428采用随机置换策略的某些实施例中,可省略步骤510。

在步骤512中,执行阶段EX可经由管线寄存器203发送存储请求至存储器240,其中该存储请求包含该写入数据和地址生成器136所产生之地址addr。若存储器240之中包含与地址addr相匹配的地址,则存储器240可将该写入数据存储于存储器240之中。若当存储器240之中不具有与地址addr相匹配的地址时,该存储请求可总线接口单元254传送至外部存储器260,以将该写入数据存储于外部存储器260中地址addr所指向的存储位置。在步骤514中,结束该存储指令。

图6示出了图2所示之处理器电路200所涉及之用以处理存储器存取指令MAI的数据处理方法的另一实施例的流程图。在此实施例中,图2所示之处理器电路200所包含的数据缓冲器138可采用图4所示之架构来执行相关的操作。此外,存储器存取指令MAI可由载入指令来实施。

请一并参照图2、图4和图6,在步骤602中,执行阶段EX可开始执行该载入指令。该载入指令用以将读取数据载入至指令解码单元122之寄存器。在步骤604中,地址生成器136可根据该载入指令的解码结果产生地址addr,亦即该载入指令所要求的地址。地址生成器136可将地址addr输出至数据缓冲器138。

在步骤606中,比较电路422可将地址addr与标签TG(0)~TG(N-1)作比较,以检查地址addr是否已存储于存储空间410。若检查出addr已存储于存储空间410,则执行步骤608;反之,执行步骤616。

在步骤608中,控制器428可检查地址addr所指向的入口是否有被锁定。举例来说,在地址addr与标签TG(i)相匹配的情形下,控制器428可检查入口E(i)之有效位元域L是否具有特定的位元模式,以判断入口E(i)是否被锁定。若判断出入口E(i)未被锁定,执行步骤610;反之,执行步骤614。在此实施例中,当入口E(i)之锁定位元L(i)的位元值等于0时,控制器428可判断入口E(i)未被锁定;当入口E(i)之锁定位元L(i)的位元值等于1时,控制器428可判断入口E(i)被锁定。

在步骤610中,控制器428可根据置换策略更新N个入口E(0)~E(N-1)的存取顺序。举例来说,控制器428可采用最近最少使用之置换策略。因此,控制器428可将最近一次存取的入口E(i)设定为最常使用的入口。在某些实施例中,控制器428可采用非最近使用之置换策略、随机置换策略或其他置换策略。在控制器428采用随机置换策略的某些实施例中,可省略步骤610。

在步骤612中,选择电路424可将入口E(i)之数据DA(i)作为数据lub_d,使数据缓冲器138可将数据lub_d回传给管线核心,诸如指令解码单元122。此外,逻辑电路426可输出具有特定的信号电平(诸如高逻辑电平)之有效信号lub_dv,以指示出数据lub_d是有效/可用的。

在步骤614中,数据缓冲器138可发送读取请求RR至存储器240,以读取存储器240中地址addr所指向的数据,其中该读取请求包含地址addr。

在步骤616中,控制器428可根据指示信号lu_instr判断该载入指令是否为载入使用指令。若是,执行步骤618;反之,执行步骤614。

在步骤618中,控制器428可根据置换策略,选择N个入口E(0)~E(N-1)其中的一个入口,以将地址addr存储于该入口之标签域TG。在此实施例中,控制器428可采用最近最少使用之置换策略,将地址addr存储于最近最少使用的入口E(i)的标签域TG。在某些实施例中,控制器428也可采用其他置换策略来存储地址addr。

在步骤620中,控制器428可设定入口E(i)之有效位元域V的内容表示入口E(i)已存入信息。举例来说,控制器428可将有效位元V(i)的位元值设为「1」。此外,由于该载入指令所要求的数据尚未存储于入口E(i)之数据域DA,控制器428可将入口E(i)之锁定位元域L设定为特定的位元模式,以保护入口E(i)所存储的信息不被不同于该载入指令的其他指令修改。在此实施例中,控制器428可将锁定位元L(i)的位元值设为「1」。

在步骤622中,存储器240可根据该读取请求检查存储器240之中是否存储有该载入指令所要求的数据。若检查出存储器240之中存储该载入指令所要求的数据,执行步骤624;反之,执行步骤626。举例来说,若检查出存储器240之中包含与地址addr相匹配的地址,则可判断存储器240之中存储有该载入指令所要求的数据。

在步骤624中,存储器240可将存储器240之中地址addr所指向的数据MD1回传给管线核心,诸如指令解码单元122。数据MD1作为该载入指令所要求的数据。

在步骤626中,数据缓冲器138可经由总线接口单元254发送读取请求RR至外部存储器260,以读取外部存储器260中地址addr所指向的数据MD2,其中数据MD2作为该载入指令所要求的数据。

在步骤628中,控制器428可根据指示信号lu_instr判断是否要更新存储空间410所存储的信息。若判断出需要更新存储空间410所存储的信息,执行步骤630;反之,执行步骤640。举例来说,当指示信号lu_instr具有特定的信号电平(诸如高逻辑电平)时,控制器428可判断需要更新存储空间410所存储的信息。

在步骤630中,控制器428可将入口E(i)之数据域DA更新为存储器240所回传的数据MD1。在步骤632中,由于地址addr和该载入指令所要求的数据均存储至入口E(i),因此,控制器428可将入口E(i)之锁定位元域L设定为另一特定的位元模式,以允许入口E(i)所存储的信息被修改。在此实施例中,控制器428可将锁定位元L(i)的位元值设为0。

在步骤634中,控制器428可根据指示信号lu_instr判断是否要更新存储空间410所存储的信息。若判断出需要更新存储空间410所存储的信息,执行步骤636;反之,执行步骤640。举例来说,当指示信号lu_instr具有特定的信号电平(诸如高逻辑电平)时,控制器428可判断需要更新存储空间410所存储的信息。

在步骤636中,控制器428可将入口E(i)之数据域DA更新为外部存储器260所回传的数据MD2。在步骤638中,由于地址addr和该载入指令所要求的数据均存储至入口E(i),因此,控制器428可将入口E(i)之锁定位元域L设定为另一特定的位元模式,以允许入口E(i)所存储的信息被修改。在此实施例中,控制器428可将锁定位元L(i)的位元值设为0。步骤640中,结束该载入指令。

为了便于理解本公开的内容,下文以数据缓冲器呼应连续多个指令而执行的操作的实施方式,来说明本公开所提供的数据处理方案。图7示出了图4所示之存储空间410在连续多个时钟周期C0~C8中各自存储的信息的示意图。在此实施例中,存储空间410可包含4个入口E(0)~E(3)(即N等于4)以存储执行指令所需的信息。此外,各入口之标签域TG和数据域DA的内容均可由16进制(亦即,「0x」)来表示。

请一并参照图2、图4和图7,当时钟周期CC0开始时,存储空间410之中对应于索引值idx(0)的入口E(0)已存储了地址0x2000以及数据0xaa。此外,入口E(0)之有效位元域V和锁定位元域L分別设为「1」和「0」。

在时钟周期CC0中,载入指令load1进入执行阶段EX,乘法指令mull进入指令解码阶段ID,其中执行乘法指令mull不会用到载入指令load1的目的寄存器所存储的数据。地址生成器136根据载入指令load1的解码结果产生载入指令load1所要求的地址0x3000(即地址addr)。此外,载入指令load1为载入使用指令。因此,数据缓冲器138可接收地址0x3000以及具有高逻辑电平的指示信号lu_instr。

由于地址0x3000尚未存储于存储空间410之中,因此,比较电路422可产生具有低逻辑电平的命中信号lub_h。控制器428可根据置换策略选择入口E(1),以将地址addr存储于入口E(1)之标签域TG。此外,控制器428可将入口E(1)之有效位元域V和锁定位元域L设为「1」。在某些实施例中,时钟周期CC0所涉及的操作可由图6所示之多个步骤602、604、606、616、618、620来实施。

接下来,当时钟周期CC0之后的时钟周期CC1开始时,存储空间410之中入口E(1)已存储了地址0x3000,且入口E(1)之有效位元域V和锁定位元域L均设为「1」。在时钟周期CC1中,载入指令load1进入存储器存取阶段MEM,乘法指令mull进入执行阶段EX,以及另载入指令load2进入指令解码阶段ID。控制器428可接收存储器240所回传的数据MD1,其为存储器240之中地址0x3000所指向的数据0xbb。因此,控制器428可将入口E(1)之数据域DA设为数据0xbb,并且将入口E(1)之锁定位元域L设为「0」。在某些实施例中,时钟周期CC1所涉及的操作可由图6所示之多个步骤614、622、624、628、630、632来实施。

在时钟周期CC1之后的时钟周期CC2中,乘法指令mull进入存储器存取阶段MEM,载入指令load2进入执行阶段EX,以及加法指令add2进入指令解码阶段ID。地址生成器136根据载入指令load2的解码结果产生载入指令load2所要求的地址0x3000(即地址addr)。载入指令load2为载入使用指令,其中执行加法指令add2需使用载入指令load2的目的寄存器所存储的数据。

由于载入指令load2所要求的地址0x3000已存储于入口E(1),因此,比较电路422可产生具有高逻辑电平的命中信号lub_h。逻辑电路426可输出具有高逻辑电平之有效信号lub_dv。选择电路424可将存储于入口E(1)之数据0xbb作为数据lub_d,使数据缓冲器138可将载入指令load2所要求的数据0xbb回传给指令解码单元122。因此,加法指令add2所需的数据0xbb在加法指令add2进入执行阶段EX之前即已就绪。在某些实施例中,时钟周期CC2所涉及的操作可由图6所示之多个步骤604、606、608、610、612来实施。

在时钟周期CC2之后的时钟周期CC3中,载入指令load2进入存储器存取阶段MEM,加法指令add2进入执行阶段EX,以及另一载入指令load3进入指令解码阶段ID。由于加法指令add2所需的数据0xbb已就绪,处理器电路200可成功地执行加法指令add2。

在时钟周期CC3之后的时钟周期CC4中,加法指令add2进入存储器存取阶段MEM,载入指令load3进入执行阶段EX,以及另一载入指令load4进入指令解码阶段ID。地址生成器136根据载入指令load3的解码结果产生载入指令load3所要求的地址0x4000。此外,载入指令load3为载入使用指令。因此,数据缓冲器138可接收地址0x4000以及具有高逻辑电平的指示信号lu_instr。

由于地址0x4000尚未存储于存储空间410之中,因此,比较电路422可产生具有低逻辑电平的命中信号lub_h。控制器428可根据置换策略选择入口E(2),以将地址addr存储于入口E(2)之标签域TG。此外,控制器428可将入口E(2)之有效位元域V和锁定位元域L设为「1」。在某些实施例中,时钟周期CC4所涉及的操作可由图6所示之多个步骤602、604、606、616、618、620来实施。

在时钟周期CC4之后的时钟周期CC5中,载入指令load3进入存储器存取阶段MEM,载入指令load4进入执行阶段EX,以及逻辑左移指令sll进入指令解码阶段ID。地址生成器136根据载入指令load4的解码结果产生载入指令load4所要求的地址0x4000。此外,载入指令load4为载入使用指令。因此,数据缓冲器138可接收地址0x4000以及具有高逻辑电平的指示信号lu_instr。此外,控制器428可接收存储器240所回传的数据MD1,其为载入指令load3所要求的数据0xcc。

由于载入指令load4所要求的地址0x4000已存储于入口E(2),因此,比较电路422可产生具有高逻辑电平的命中信号lub_h。值得注意的是,在控制器428将入口E(2)之数据域DA设为数据0xcc之前,由于入口E(2)之锁定位元域L仍是「1」,因此,有效信号lub_dv仍具有低逻辑电平,代表载入指令load4所要求的数据尚未就绪。在入口E(2)之数据域DA设为数据0xcc之后,控制器428可将入口E(2)之锁定位元域L设为「0」,并将入口E(2)所存储之数据0xcc提供给指令解码单元122。借由锁定位元域L,处理器电路200可确保载入指令load4在执行阶段EX所载入的数据是载入指令load3所要求的数据。在某些实施例中,时钟周期CC5所涉及的操作可由图6所示之多个步骤604、606、608、610、612来实施。

在时钟周期CC5之后的时钟周期CC6中,载入指令load4进入存储器存取阶段MEM,逻辑左移指令sll进入执行阶段EX,以及存储指令store1进入指令解码阶段ID。

在时钟周期CC6之后的时钟周期CC7中,逻辑左移指令sll进入存储器存取阶段MEM,存储指令store1进入执行阶段EX,以及加法指令add4进入指令解码阶段ID。存储指令store1用以将写入数据0xdd存储于存储器240中,其中地址生成器136根据存储指令store1的解码结果产生存储指令store1所要求的地址0x2000。由于存储指令store1所要求的地址0x2000已存储于入口E(0),因此,比较电路422可产生具有高逻辑电平的命中信号lub_h。此外,控制器428可将入口E(0)之数据域DA更新为写入数据0xdd。在某些实施例中,时钟周期CC7所涉及的操作可由图5所示之多个步骤502、504、506、508、510来实施。

在时钟周期CC7之后的时钟周期CC8中,存储指令store1进入存储器存取阶段MEM,以及加法指令add4进入执行阶段EX。存储器240可将写入数据0xdd存储于存储器240中地址0x2000所指向的存储位置。

由于所属领域中的通常知识者在阅读图1~图6相关的段落说明之后,可以了解图7所示之各时钟周期中的操作细节,因此进一步的说明在此便不再赘述。

本公开所提供之数据处理方案可归纳于图8。图8是依据本公开的数据处理方法的实施例的流程图。以下基于图2所示的处理器电路200来说明数据处理方法800。然而,所属技术领域中具有通常知识者应该理解,数据处理方法800可用于控制图1所示之处理器电路100而不致于脱离本公开内容之范围。此外,在某些实施方式中,亦可在数据处理方法800执行其他操作。在某些实施方式中,可利用不同的顺序或不同操作来进行数据处理方法800。

在步骤802中,接收载入指令,并检测该载入指令是否处于载入使用情境。例如,指令检测器124可检测载入指令LWI是否为载入使用指令。在某些实施例中,指令检测器124可判断使用载入指令LWI的执行结果来执行指令是否会发生载入使用数据风险,进而检测出载入指令LWI是否为载入使用指令,其中该指令在载入指令LWI之后被执行。

在步骤804中,对该载入指令进行解码以产生解码结果。例如,指令解码单元122可对载入指令LWI进行解码以产生解码结果DR。

在步骤806中,根据该解码结果产生该载入指令所要求的地址。例如,地址生成器136可根据解码结果DR产生载入指令LWI所要求的地址addr。

在步骤808中,当检测出该载入指令处于该载入使用情境时,将该地址存储于数据缓冲器。例如,当指令检测器124检测出载入指令LWI为该载入使用指令时,数据缓冲器138可存储地址addr。

在步骤810中,根据该地址将该载入指令所要求的数据存储于该数据缓冲器。例如,数据缓冲器138可根据地址addr存储载入指令LWI所要求的数据。

由于所属技术领域中具有通常知识者在阅读上述对应于图1~图7的相关段落内容之后,应该理解数据处理方法800的每一操作,因此,为求简洁起見,进一步的说明在此便不再赘述。

上文的敘述简要地提出了本公开某些实施例之特征,而使得本公开所属技术领域具有通常知识者可更全面地理解本公开的多种形式。本公开所属技术领域具有通常知识者应该明白,其可容易地利用本公开作为基础,来设计或更改其他过程和结构,以实现与此处所述之实施方式相同的目的和/或达到相同的优点。本公开所属技术领域具有通常知识者应当明白,这些均等的实施方式仍属于本公开之精神和范围,且其可进行各种变更、替代和更改,而不会脱离本公开之精神和范围。

【符号说明】

100、200:处理器电路

122:指令解码单元

124:指令检测器

136:地址生成器

138:数据缓冲器

180:存储器

201~204:管线寄存器

232:执行单元

233:算术逻辑单元

234:乘法累加单元

240:存储器

252:寄存器文件

254:总线接口单元

260:外部存储器

410:存储空间

420:控制电路

422:比较电路

423:缓冲器

424:选择电路

426:逻辑电路

428:控制器

502~514、602~640、802~810:步骤

800:数据处理方法

IF:指令获取阶段

ID:指令解码阶段

EX:执行阶段

MEM:存储器存取阶段

WB:写回阶段

ibuf0~ibuf6:存储单元

E(0)~E(N-1):入口

V:有效位元域

L:锁定位元域

TG:标签域

DA:数据域

INS:指令串流

LWI:载入指令

MAI:存储器存取指令

I0~I6:指令

lub_d、MD、MD1、MD2:数据

lub_instr:指示信号

lub_dv:有效信号

lub_h:命中信号

addr:地址

RR:读取请求

DR、DR’:解码结果

CC0~CC8:时钟周期

- 一种矩阵乘法器、数据处理方法、集成电路器件及处理器

- 一种缓存数据处理方法、电路、处理器及芯片