成像装置和电子设备

文献发布时间:2023-06-19 12:11:54

技术领域

本公开涉及一种成像装置和电子设备。

背景技术

在诸如CMOS图像传感器等成像装置的检查期间,特别是在批量生产中的分类检查期间,实际上进行成像,并且使用成像信号将装置分类为无缺陷装置和缺陷装置。具体地,通过检查基于成像信号的图像中是否包括诸如白点和黑点等缺陷来进行故障检查。

然而,在基于实际成像的故障检查中,不可能检查信号处理单元的操作。鉴于此,为了能够检查信号处理单元的操作,已经提出了一种能够在不实际进行成像的情况下进行故障检查的检查方法(例如,参见专利文献1)。专利文献1公开了一种技术,其设置有保持各像素阵列的像素信号的保持单元,并且利用该技术能够通过将期望的数据信号输入到保持单元而无需进行成像来进行基于期望的数据信号的操作检查。

引用列表

专利文献

专利文献1:日本专利申请特开第2009-77173号公报

发明内容

发明要解决的问题

作为诸如CMOS图像传感器等成像装置,所谓的列AD成像装置是常见的,其包括对应于其中像素以矩阵状二维排列的像素阵列单元的像素阵列布置的模数转换电路。另一方面,近年来,已经开发了所谓的像素并行AD成像装置,其包括分别对应于像素阵列单元的像素(像素电路)设置的模数转换电路。

在像素并行AD成像装置中,模数转换电路的面积,特别是用于锁存数字码的锁存电路的面积大于列AD成像装置的面积,并且由此增大了故障的可能性。因此,需要一种能够进行全面故障检测的电路。例如,在具有24M像素(6000水平×4000垂直)并且作为列AD型的成像装置中,通常将总共两行的锁存电路安装在垂直方向的两侧,以用于读出像素阵列单元的像素信号。另一方面,像素并行AD型的成像装置配备有用于与像素的数量相同的4000行的锁存电路。

因此,在像素并行AD成像装置中,通过简单比较,锁存电路的数量是列AD成像装置的锁存电路的数量的2000倍,并且需要能够进行全面故障检测的电路。尽管上述专利文献1公开了一种在列AD成像装置中能够基于期望的数据信号进行操作检查而无需实际进行成像的技术,但是专利文献1中公开的现有技术并未考虑在像素并行AD成像装置中对与像素一样多的锁存电路以及与其相关联的电路进行全面故障检测。

本公开的目的是提供一种成像装置以及包括该成像装置的电子设备,该成像装置能够对像素并行AD成像装置中对应于像素(像素电路)设置的锁存电路以及与其相关联的电路进行全面的故障检测。

问题的解决方案

用于实现上述目的的根据本公开的成像装置具有

堆叠型芯片结构,其中堆叠有至少两个半导体芯片,即第一半导体芯片和第二半导体芯片,所述第一半导体芯片设置有包括光电转换元件的像素电路,所述第二半导体芯片包括对应于所述像素电路设置的模数转换电路。

所述模数转换电路包括:在模数转换之后保持数字码的锁存电路;以及在模数转换之后传输所述数字码的传输电路。

此外,设置有对所述模数转换电路进行故障检测的故障检测电路。

所述故障检测电路通过将用于故障检测的测试模式经由所述传输电路写入所述锁存电路、然后经由所述传输电路从所述锁存电路读出所述测试模式并且将所述读出的测试模式与期望值进行比较来进行故障检测。

此外,用于实现上述目的的根据本公开的电子设备包括如上所述构成的成像装置。

附图说明

图1是示意性地示出根据本公开的实施方案的成像装置的堆叠型芯片结构的分解立体图。

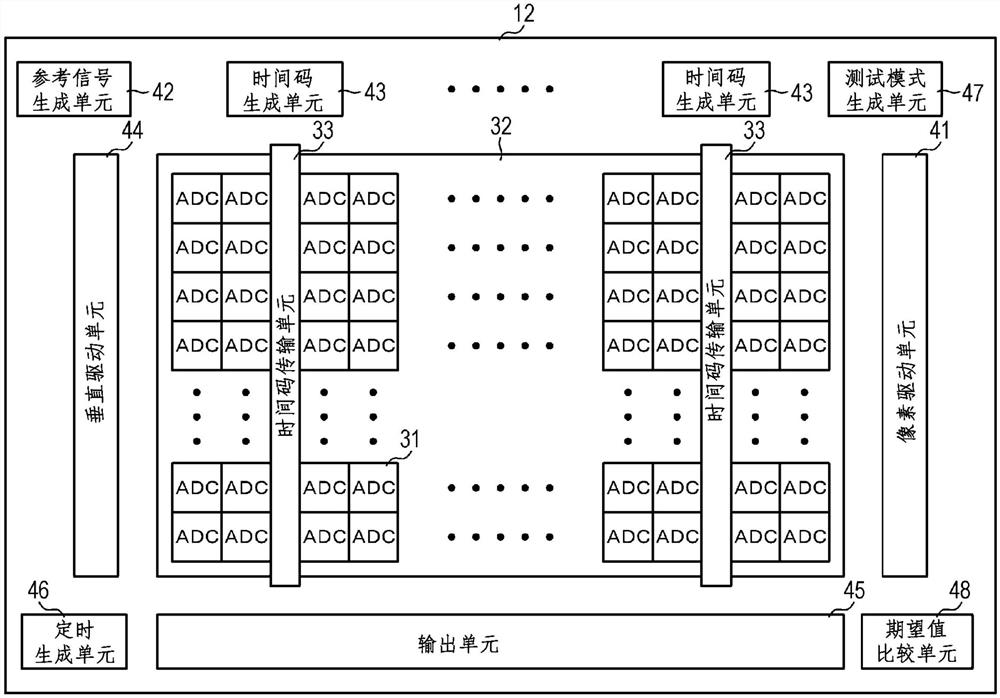

图2是示出根据本公开的实施方案的成像装置中的像素阵列单元的具体构成例的框图。

图3是示出根据本公开的实施方案的成像装置中的模数转换电路的具体构成例的框图。

图4是示出根据本公开的实施方案的成像装置中的模数转换电路的数据存储单元的基本构成例的框图。

图5是用于说明根据本公开的实施方案的成像装置中的模数转换电路的操作示例的时序波形图。

图6是示出根据本公开的实施方案的成像装置中的时间码生成单元的具体构成例的框图。

图7是示出根据本公开的实施方案的成像装置中的测试模式生成单元的具体构成例的框图。

图8是示出测试模式生成单元在正常计数操作期间的信号路径(点线)的图。

图9是示出测试模式生成单元在故障检测(BIST)操作期间的信号路径(间断线)的图。

图10是示出测试模式生成单元中各个信号之间的时序关系的时序波形图。

图11是示出测试模式生成单元中的格雷码生成器(Gray code generator)的具体构成例的框图。

图12是示出格雷码生成器在正常计数操作期间的信号路径(点线)的图。

图13是示出格雷码生成器在故障检测(BIST)操作期间的信号路径(间断线)的图。

图14是示出根据本公开的实施方案的成像装置中的期望值比较单元的具体构成例的框图。

图15A是用作测试模式的交替模式的说明图,并且图15B是切换交替模式的含义的说明图。

图16是示出作为由故障检测电路进行故障检测的目标的电路的主要部分的构成例的框图。

图17是示出根据示例1的故障检测处理的过程的示例的流程图。

图18是示意性地示出根据示例1的故障检测处理中的步骤S11的具体处理的说明图。

图19是示意性地示出根据示例1的故障检测处理中的步骤S12的具体处理的说明图。

图20是示意性地示出根据示例1的故障检测处理中的步骤S13的具体处理的说明图。

图21是示意性地示出根据示例1的故障检测处理中的步骤S14的具体处理的说明图。

图22是示出根据示例2的故障检测处理的时序波形图。

图23是根据示例3的故障检测处理的操作的概念图。

图24是示出根据本公开的技术的适用例的图。

图25是示意性地示出作为根据本公开的电子设备的示例的成像系统的构成例的框图。

图26是示出作为根据本公开的技术可以适用的移动体控制系统的示例的车辆控制系统的示意性构成例的框图。

图27是示出移动体控制系统中的成像单元的安装位置的示例的图。

具体实施方式

在下文中,将参照附图详细说明用于实施根据本公开的技术的方式(在下文中,称为实施方案)。根据本公开的技术不限于实施方案,并且实施方案中的各种数值等是说明性的。在下面的说明中,对于相同的元件或具有相同功能的元件使用相同的附图标记,并且将省略重复的说明。注意,将按以下顺序给出说明。

1.根据本公开的成像装置和电子设备的总体说明

2.根据实施方案的成像装置

2-1.堆叠型芯片结构的构成例

2-2.第二半导体芯片的电路部的构成例

2-3.模数转换电路的构成例

2-4.数据存储单元的构成例例

2-5.模数转换电路的操作示例

2-6.时间码生成单元的构成例

3.根据实施方案的故障检测电路(内置自检(BIST:Built-In Self Test))

3-1.测试模式生成单元的构成例

3-2.格雷码生成器的构成例

3-3.期望值比较单元的构成例

3-4.交替模式

3-5.故障检测处理

3-5-1.示例1(故障检测处理的基本形式)

3-5-2.示例2(示例1的变形例:正常操作期间的故障检测示例)

3-5-3.示例3(示例1的变形例:针对IR压降的对策示例)

4.变形例

5.应用例

6.根据本公开的技术的适用例

6-1.根据本公开的电子设备(成像系统的示例)

6-2.移动体的应用例

7.本公开的可能构成

<根据本公开的成像装置和电子设备的总体说明>

在根据本公开的成像装置和电子设备中,测试模式可以是其中逻辑“1”和逻辑“0”被交替排列的交替模式。此外,测试模式可以是其中交替模式的逻辑与用于生成测试模式的时钟信号同步地反相的切换模式。

在包括上述优选构成和方式的根据本公开的成像装置和电子设备中,通过对从像素电路输出的信号电平进行模数转换而获得的数据被定义为D相数据,并且通过对复位电平进行模数转换而获得的数字数据被定义为P相数据。在这种情况下,模数转换电路可以具有:

作为锁存电路的用于测试模式写入的锁存电路、用于P相读出的锁存电路和用于D相读出的锁存电路;以及

作为传输电路的用于测试模式写入的传输电路、用于P相读出的传输电路和用于D相读出的传输电路。

此外,在包括上述优选构成和方式的根据本公开的成像装置和电子设备中,故障检测电路可以:经由用于测试模式写入的传输电路将测试模式写入用于测试模式写入的锁存电路;然后,经由用于P相读出的传输电路从用于P相读出的锁存电路读出测试模式;然后,经由用于测试模式写入的传输电路再次将测试模式写入用于测试模式写入的锁存电路;然后,经由用于D相读出的传输电路从用于D相读出的锁存电路读出测试模式。

此外,在包括上述优选构成和方式的根据本公开的成像装置和电子设备中,故障检测电路可以进行期望值比较,以评估经由用于P相读出的传输电路从用于P相读出的锁存电路读出的测试模式和经由用于D相读出的传输电路从用于D相读出的锁存电路读出的测试模式是否与期望值一致。另外,可以在垂直消隐时段(vertical blanking period)内进行期望值比较的处理。

此外,在包括上述优选构成和方式的根据本公开的成像装置和电子设备中,当传输电路以预定数量为单位划分成组时,故障检测电路当执行传输电路的故障检测时,针对每个组部分地进行故障检测。

<根据实施方案的成像装置>

[堆叠型芯片结构的构成例]

根据本公开的实施方案的成像装置具有堆叠型芯片结构,其中堆叠有至少两个半导体芯片,即第一半导体芯片和第二半导体芯片。图1示出了根据本公开的实施方案的成像装置的堆叠型芯片结构的分解立体图。

图1所示的堆叠型芯片结构具有两层结构,其中堆叠有两个半导体芯片,即第一半导体芯片11和第二半导体芯片12。这里,其中堆叠有两个半导体芯片的两层结构被描述为堆叠型芯片结构,但是也可以使用其中堆叠有三个以上的半导体芯片的多层结构。

在具有两层结构的芯片结构中,第一层中的第一半导体芯片11是包括像素阵列单元22的像素芯片,在像素阵列单元22中包括光电转换元件(例如,光电二极管)的像素电路21以矩阵状二维地排列。第二层中的第二半导体芯片12是设置有包括模数转换单元32的电路部的电路芯片,该模数转换单元32具有一套对应于以矩阵状二维地排列的像素电路21布置的模数转换(ADC)电路31。

如上所述,根据本公开的成像装置具有堆叠型芯片结构,并且是其中模数转换电路31分别对应于第一半导体芯片11的像素电路21布置的像素并行AD成像装置。第一层中的第一半导体芯片11的像素电路21和第二层中的第二半导体芯片12的模数转换电路31分别经由诸如Cu-Cu连接(铜-铜连接)等连接部23(参见图3)彼此连接。

第一半导体芯片11上的每个像素电路21将与由像素中的光电转换元件(例如,光电二极管)接收的光量相对应的电荷量的信号电荷转换成电信号,以获得模拟形式的像素信号V

更具体地,像素电路21产生复位电平和信号电平作为模拟形式的像素信号V

[第二半导体芯片的电路部的构成例]

图2示出了示出根据本公开的实施方案的成像装置中的第二半导体芯片12的电路部,即,包括模数转换单元32的电路部的具体构成例的框图。

在第二半导体芯片12上的模数转换单元32周围,形成有电路部,该电路部包括像素驱动单元41、参考信号生成单元42、时间码生成单元43、垂直驱动单元44、输出单元45、定时生成单元46、测试模式生成单元47、期望值比较单元48等。下面将具体说明第二半导体芯片12的电路部的各组件的功能。

像素驱动单元41驱动第一半导体芯片11上的像素电路21。参考信号生成单元42包括数模转换(DAC)电路等,并且生成其中电平(电压)随时间单调减小的所谓的斜坡波形参考信号V

设置有多个时间码生成单元43。此外,模数转换单元32设置有与时间码生成单元43相同数量的时间码传输单元33。即,时间码生成单元43和时间码传输单元33以一一对应的关系设置。时间码传输单元33传输由时间码生成单元43生成的时间码。

时间码生成单元43生成用于在模数转换电路31中将从像素电路21提供的模拟形式的像素信号V

时间码表示在模数转换期间模拟形式的像素信号V

垂直驱动单元44基于从定时生成单元46提供的定时信号来执行驱动,以使输出单元45输出由模数转换单元32的各模数转换电路31数字化的像素信号。

在垂直驱动单元44的驱动下,输出单元45对从模数转换单元32的各个模数转换电路31提供的像素信号进行预定的数字信号处理,然后将所得的信号输出到第二半导体芯片12的外部。预定的数字信号处理的示例包括黑电平校正处理和相关双采样(CDS)处理。

定时生成单元46包括用于生成各种定时信号的定时生成器等,并且将所生成的各种定时信号提供给像素驱动单元41、参考信号生成单元42、垂直驱动单元44、输出单元45等。

测试模式生成单元47和期望值比较单元48用于由稍后所述的故障检测电路(内置自检:BIST)进行的故障检测。测试模式生成单元47生成用于故障检测(故障检查)的测试模式。稍后将说明测试模式生成单元47的细节。

期望值比较单元48将故障检测电路的输出值与期望值进行比较,并且基于故障检测输出无缺陷产品/缺陷产品的评估结果。稍后将说明期望值比较单元48的细节。

[模数转换电路的构成例]

图3是示出根据本公开的实施方案的成像装置中的模数转换电路31的具体构成例的框图。这里,示出了与一个像素电路21相对应的一个模数转换电路31。

从第一半导体芯片11上的像素电路21输出的模拟形式的像素信号V

模数转换电路31包括比较电路34和数据存储单元35,并且将模拟形式的像素信号V

比较电路34包括差分输入电路341、电压转换电路342和正反馈电路343。

差分输入电路341将从像素电路21提供的模拟形式的像素信号V

电压转换电路342将从差分输入电路341提供的指示像素信号V

正反馈电路343基于电压转换电路342的输出信号将比较结果信号VCO提供给数据存储单元35,该比较结果信号VCO在像素信号V

当比较电路34的比较结果信号VCO被逻辑反相时,数据存储单元35保持时间码。然后,数据存储单元35输出与复位电平相对应的时间码作为P相数据。此外,数据存储单元35输出与信号电平相对应的时间码作为D相数据。

[数据存储单元的构成例]

图4是示出根据本公开的实施方案的成像装置中的模数转换电路31的数据存储单元35的具体构成例的框图。

数据存储单元35具有锁存电路控制单元351和D(D是整数)个锁存电路352,其中D是与D相数据的位长度相同的数量。锁存电路控制单元351根据来自垂直驱动单元44(参见图2)的控制信号WORD将比较电路34的比较结果信号VCO的值(逻辑值“0”或“1”)锁存到D个锁存电路352中的一个中。

锁存电路352经由局部位线LBL

[模数转换电路的操作示例]

这里,将参照图5说明包括具有上述构成的数据存储单元35的模数转换电路31的操作。图5是用于说明根据本公开的实施方案的成像装置中的模数转换电路31的操作示例的时序波形图。

以作为垂直同步信号V

在图5的时序波形图中,数据总线是时间码传输单元33(参见图2)中的转发器(repeater)电路的数据。数据存储单元35的锁存电路控制单元351继续经由局部位线LBL将从时间码传输单元33传输的数据写入锁存电路352,并且在比较电路34的比较结果信号VCO被逻辑反相时的时刻t

在时刻t

所有像素的曝光在时刻t

在时刻t

在输出单元45中,通过获取各像素的D相数据和P相数据之间的差来进行用于去除像素的固定模式噪声的相关双采样(CDS)处理。然后,将CDS处理后的数据作为实际像素数据输出到外部。

[时间码生成单元的构成例]

图6是示出根据本公开的实施方案的成像装置中的时间码生成单元的具体构成例的框图。

根据本实施方案的时间码生成单元43具有二进制计数器431、二进制-格雷转换单元(binary to Gray conversion unit)432、接收器433和多个驱动器434,并且生成用于模数转换电路31中的模数转换的时间码。

二进制计数器431与通过接收器433输入的主时钟MCK同步地对二进制计数值进行计数。二进制计数器431包括多级D型触发器4311。

在二进制计数器431中,主时钟MCK被输入到第一级中的触发器4311的时钟端CK。前一级中的触发器4311的xQ输出(Q输出的反相输出)被输入到第二级以及后续级中的触发器4311的时钟端CK。然后,每级的触发器4311的xQ输出用作触发器4311的D输入,并且作为相应数字的位提供给二进制-格雷转换单元432。

二进制-格雷转换单元432将从二进制计数器431提供的二进制计数值转换为格雷码,并且将其作为时间码输出。针对时间码中的每位设置驱动器434,并且驱动器434分别输出时间码的对应位FF

<根据实施方案的故障检测电路>

随后,将说明根据本公开的实施方案的故障检测电路(BIST)。除了配线的断开和短路以外,根据本实施方案的故障检测电路还用于检测模数转换电路31的锁存电路352、与其相关联的电路(例如,时间码传输单元33中的转发器电路)等的故障。故障检测电路包括生成测试模式的测试模式生成单元47以及将故障检测电路的输出值(在下文中,可以称为“BIST输出值”)与期望值进行比较的期望值比较单元48。

下面将说明测试模式生成单元47和期望值比较单元48的具体构成。

[测试模式生成单元]

图7示出了根据本公开的实施方案的成像装置中的测试模式生成单元47的具体构成例。

测试模式生成单元47包括二进制计数器471、格雷码生成器472、加法器473和选择器474,并且生成用于故障检测的测试模式。

二进制计数器471包括具有与测试模式的位长度相同级数的D型触发器4711。在二进制计数器471中,时钟信号CLOCK被输入到第一级中的触发器4711的时钟端CK。二进制计数器471的操作基本上与时间码生成单元43的二进制计数器431的操作相同。

在二进制计数器471中,每级中的触发器4711的Q输出作为相应数字的位被提供给格雷码生成器472,并且经由加法器473被提供给选择器474作为其第一输入(0)。此外,触发器4711的xQ输出(Q输出的反相输出)被提供给选择器474作为其第三输入(2)。

在正常计数操作期间,格雷码生成器472响应于故障检测许可信号BIST_ENABLE将由二进制计数器471计数的二进制计数值转换成格雷码,并且将结果作为测试模式生成单元47的输出数据COUNTER_OUT[11:0]输出。稍后将说明格雷码生成器472的细节。

加法器473对触发器4711的Q输出进行递增计数(+1),并且将其作为第一输入(0)提供给选择器474。

选择器474使用测试模式初始值INIT_VAL[11:0]作为第二输入(1)。基于故障检测许可信号BIST_ENABLE,选择器474在故障检测(BIST)操作期间选择第二输入(1)或第三输入(2),并且在正常计数操作期间选择第一输入(0),并且将所选的输入用作触发器4711的D输入。

在具有上述构成的二进制计数器471中,当选择器474选择第一输入(0)时,进行正常计数操作。具体地,在正常计数操作期间,触发器4711的Q输出用作触发器4711的D输入,并且由格雷码生成器472转换成格雷码的数据作为测试模式生成单元47的输出数据COUNTER_OUT[11:0]输出。

当选择器474选择第二输入(1)时,在二进制计数器471中设定任意码的测试模式初始值INIT_VAL[11:0]。然后,二进制计数器471的输出数据通过格雷码生成器472,并且作为测试模式生成单元47的输出数据COUNTER_OUT[11:0]输出。

然后,当选择器474选择第三输入(2)时,进行故障检测(BIST)操作。具体地,在故障检测操作期间,触发器4711的xQ输出用作触发器4711的D输入,从而在二进制计数器471中,进行其中触发器4711的Q输出的逻辑“1”和逻辑“0”与时钟信号CLOCK同步地被反相的切换操作。然后,二进制计数器471的二进制计数值通过格雷码生成器472,并且作为切换模式输出。

正常计数操作期间的信号路径在图8中由点线表示,并且故障检测(BIST)操作期间的信号路径在图9中由间断线表示。此外,图10示出了测试模式生成单元47中的各个信号的时序波形图。图10的时序波形图示出了测试模式初始值INIT_VAL[11:0]、故障检测许可信号BIST_ENABLE、时钟信号CLOCK以及测试模式生成单元47的输出数据COUNTER_OUT[11:0]之间的时序关系。

具有上述构成的测试模式生成单元47具有能够生成切换模式的电路构成,其中在正常计数操作期间通过应用用作二进制计数器471的触发器4711将触发器4711的Q输出与时钟信号CLOCK同步地切换为测试模式。通过将切换模式用作测试模式,可以提高稍后所述的故障检测(缺陷产品的分类)的全面性。

[格雷码生成器的构成例]

图11示出了测试模式生成单元47中的格雷码生成器472的具体构成例。

格雷码生成器472包括多个异或电路(EOR)4721和比异或电路4721多一个的选择器4722。多个异或电路4721将从二进制计数器471输出的二进制码(二进制计数值)转换成格雷码。

选择器4722使用从多个异或电路4721输出的格雷码作为它们的第一输入(0),并且将从二进制计数器471输出的二进制码用作它们的第二输入(1)和第三输入(2)。然后,选择器4722基于故障检测许可信号BIST_ENABLE在正常计数操作期间选择从多个异或电路4721输出的格雷码,并且在故障检测(BIST)操作期间选择从二进制计数器471输出的二进制码。

具有上述构成的格雷码生成器472中的正常计数操作期间的信号路径在图12中由点线表示,并且故障检测操作期间的信号路径在图13中由间断线表示。

[期望值比较单元]

图14示出了根据本公开的实施方案的成像装置中的期望值比较单元48的具体构成例。

期望值比较单元48具有分别与故障检测电路的输出值,即,BIST输出值的位相对应地设置的异或电路(EOR)481以及使用异或电路481的输出作为输入的负或电路482。异或电路481针对各位接收期望值和BIST输出值作为输入。

具有上述构成的期望值比较单元48将故障检测电路的BIST输出值[11:0]与期望值[11:0]进行比较,并且输出比较结果作为基于故障检测的无缺陷产品/缺陷产品的评估结果。具体地,当故障检测电路的BIST输出值[11:0]全部与期望值[11:0]一致时,期望值比较单元48输出高电平比较结果,而即使仅一位与期望值不一致,也输出低电平比较结果。

[交替模式]

作为用于检测诸如配线的断开和短路等故障的测试模式,优选其中逻辑“1”和逻辑“0”被交替排列的交替模式。原因如下。如图15A所示,如果不是交替模式,则由于尘埃等无法检测出配线短路,但是如果是交替模式,则可以检测出配线短路。

此外,如图15B所示,优选的是,测试模式是通过切换交替模式获得的切换模式。如图10的时序波形图所示,可以通过与二进制计数器471的时钟信号CLOCK同步的切换操作来实现切换模式。由于将通过切换交替模式获得的切换模式用作测试模式的故障检测,因此可以特别地进行相邻配线之间的短路的全面的故障检测。

[故障检测处理]

随后,将说明具有上述构成的故障检测电路进行的故障检测处理的具体示例。图16示出了作为故障检测的目标的电路的主要部分的构成例。

(示例1)

示例1是故障检测处理的基本形式。示例1的构成例包括独立的并且分别专用于时间码设定(写入)、P相读出(读出)和D相读出(读出)的锁存电路352

注意,尽管示例1具有独立的并且分别专用于时间码设定、P相读出和D相读出的电路构成,但是可以使用它们共同的电路构成。然而,例如,如果使用独立的电路构成,则可以进行其中写入P相数据,然后在读出P相数据的同时写入D相数据的并行处理。因此,从高速处理的角度来看,使用独立的电路构成的情况与使用其中无法进行并行处理的共用电路构成的情况相比更加有利。

图17是示出根据示例1的故障检测处理的过程的示例的流程图。在以下所述的故障检测(BIST)处理中,用于时间码设定(写入)的传输电路331

在故障检测处理中,首先,将基于从格雷码生成器472输出的任意码的测试模式经由写入传输通道设定在用于写入的锁存电路352

接下来,经由P相读出传输通道从用于P相读出的锁存电路352

接下来,与步骤S11的处理相同,将基于任意码的测试模式经由写入传输通道设定在用于写入的锁存电路352

接下来,经由D相读出传输通道从用于D相读出的锁存电路352

接下来,进行期望值比较,以评估经由P相读出传输通道读出并保持在SRAM 52中的数据(测试模式)以及经由D相读出传输通道读出并保持在SRAM 53中的数据(测试模式)是否与期望值一致(步骤S15)。然后,如果期望值比较的比较结果表明它们彼此一致,则输出高电平比较结果(步骤S16),并且如果期望值比较的比较结果表明它们彼此不一致,则输出低电平比较结果(步骤S17)。此后,结束用于故障检测的一系列处理。

利用根据上述示例1的故障检测处理,可以全面地检测与像素相对应地设置的锁存电路和与其相关联的电路的故障。具体地,示例1涵盖用于写入的锁存电路352

另外,尽管根据本公开的成像装置具有堆叠型芯片结构,并且除非像素芯片(第一半导体芯片11)和电路芯片(第二半导体芯片12)接合在一起,否则不会完成操作,但是故障检测(BIST)可以仅在电路芯片中完成,因此,可以在接合之前挑选出有缺陷的芯片。具体地,例如,由于在将电路晶片接合到像素晶片之前,可以仅在电路晶片中进行故障检测,因此,仅电路晶片中的无缺陷的电路芯片可以传送到接合步骤。因此,可以提高成品率,从而可以降低成像装置的成本。此外,根据配备有该故障检测电路的成像装置,可以获得不具有诸如白点和黑点等缺陷的高质量的拍摄图像。

(示例2)

示例2是示例1的变形例,并且是在正常操作期间进行故障检测的示例。图22示出了示出根据示例2的故障检测处理的时序波形图。

如图22的时序波形图所示,在正常操作期间的垂直消隐时段进行根据示例1的故障检测处理中的步骤S15的比较处理,即将P相/D相与BIST期望值进行比较(P_BIST/D_BIST)的处理。通过以这种方式在正常操作期间进行故障检测,其不仅可以应用于初始故障的检测,而且可以应用于作为稍后发生的故障的自故障的检测。具体地,当稍后发生故障时,成像装置本身可以检测故障并且设定故障标记。

(示例3)

示例3是示例1的变形例,并且是避免由于故障检测(BIST)期间的过大的IR压降而导致的故障的示例。图23示出了根据示例3的故障检测处理的操作的概念图。

对整个成像装置的转发器电路(图16中的传输电路331

鉴于此,在根据示例3的故障检测处理中,转发器电路(图23的示例中的REP000~REP1000)中的预定数量的转发器电路,例如,16个转发器电路被分组为一组,并且部分地针对各组进行转发器电路的故障检测,而不是一次针对所有转发器电路进行故障检测。结果,可以抑制功耗的增加,从而可以避免由于故障检测(BIST)期间过大的IR压降而导致的故障。

<变形例>

尽管上面已经基于优选实施方案说明了根据本公开的技术,但是根据本公开的技术不限于该实施方案。在上述实施方案中所述的成像装置的构成和结构仅是示例性的,并且可以适当地进行改变。

<应用例>

如图24所示,例如,上述根据本实施方案的成像装置可以用于感测诸如可见光、红外光、紫外光和X射线等光的各种装置。下面列出了各种装置的具体示例。

·诸如数码相机和具有相机功能的便携式设备等拍摄用于观赏的图像的装置

·用于诸如自动停车、驾驶员状态识别等安全驾驶的诸如拍摄汽车的前侧、后侧和周围的环境以及汽车的内部等的图像的车载传感器、监视行进车辆或道路的监视相机或测量车辆之间的距离的测距传感器等用于交通的装置

·用于诸如电视、冰箱或空调等家用电器的装置,其拍摄用户的手势的图像并根据该手势进行操作

·诸如内窥镜和通过接收红外光进行血管造影的装置等用于医疗保健的装置

·诸如用于预防犯罪的监控相机和用于个人身份认证的相机等用于安保的装置

·诸如拍摄皮肤的图像的皮肤测量装置和拍摄头皮的图像的显微镜等用于美容的装置

·诸如动作相机和用于运动用途的可穿戴式相机等用于运动的装置

·诸如监测农田和农作物状态的相机等用于农业的装置

<根据本公开的技术的应用例>

根据本公开的技术可以适用于各种产品。下面将说明更具体的应用例。

[根据本公开的电子设备]

这里,将说明本技术适用于以下电子设备的情况,这些电子设备包括:诸如数码相机或摄像机等成像系统;以及诸如移动电话等具有成像功能的移动终端装置;使用图像读出单元中的成像元件的复印机等。

(成像系统的示例)

图25是示出作为根据本公开的电子设备的示例的成像系统的构成例的框图。

如图25所示,根据本示例的成像系统100包括具有透镜组等的成像光学系统101、成像单元102、数字信号处理器(DSP)电路103、帧存储器104、显示装置105、记录装置106、操作系统107、电源系统108等。然后,在该构成中,DSP电路103、帧存储器104、显示装置105、记录装置106、操作系统107和电源系统108经由总线109互相连接。

成像光学系统101捕获来自被摄体的入射光(图像光),并且在成像单元102的成像表面上形成图像。成像单元102将通过光学系统101在成像表面上形成图像的入射光量转换成以像素为单位的电信号,并且将该电信号作为像素信号输出。DSP电路103进行一般的相机信号处理,例如,白平衡处理、去马赛克处理、伽马校正处理等。

帧存储器104适合用于在DSP电路103中的信号处理期间存储数据。显示装置105包括诸如液晶显示装置或有机电致发光(EL)显示装置等面板型显示装置,并且显示由成像单元102拍摄的运动图像或静止图像。记录装置106将由成像单元102拍摄的运动图像或静止图像记录在诸如便携式半导体存储器、光盘或硬盘驱动器(HDD)等记录介质上。

操作系统107根据用户执行的操作来发出用于成像装置100的各种功能的操作指令。电源系统108适当地向电源目标供应各种电源,这些电源是用于DSP电路103、帧存储器104、显示装置105、记录装置106和操作系统107的操作电源。

在具有上述构成的成像系统100中,根据上述实施方案的成像装置可以用作成像单元102。根据成像装置,可以通过根据本公开的技术适用的故障检测(BIST)来提高成品率,这有助于成像系统100的成本降低。另外,可以获得不具有诸如白点和黑点等缺陷的高质量的拍摄图像。

[移动体的应用例]

根据本公开的技术(本技术)可以适用于各种产品。例如,根据本公开的技术可以被实现为安装在诸如汽车、电动汽车、混合动力汽车、摩托车、自行车、个人移动装置、飞机、无人机、船、机器人、建筑机械和农业机械(拖拉机)等任何类型的移动体上的成像装置。

图26是示出作为可以应用根据本公开的技术的移动体控制系统的示例的车辆控制系统的示意性构成例的框图。

车辆控制系统12000包括经由通信网络12001彼此连接的多个电子控制单元。在图1021所示的示例中,车辆控制系统12000包括驱动系统控制单元12010、车身系统控制单元12020、车外信息检测单元12030、车内信息检测单元12040和综合控制单元12050。此外,微型计算机12051、声音/图像输出单元12052和车载网络接口(I/F)12053被示出为综合控制单元12050的功能构成。

驱动系统控制单元12010根据各种程序控制与车辆的驱动系统相关的装置的操作。例如,驱动系统控制单元12010用作以下装置的控制装置:诸如内燃机或驱动电机等用于产生车辆的驱动力的驱动力产生装置;用于将驱动力传递至车轮的驱动力传递机构;用于调整车辆的转向角的转向机构;以及用于产生车辆的制动力的制动装置等。

车身系统控制单元12020根据各种程序控制安装到车身上的各种装置的操作。例如,车身系统控制单元12020用作无钥匙进入系统、智能钥匙系统、电动窗装置或诸如车头灯、车尾灯、刹车灯、转向信号灯或雾灯等各种灯的控制装置。在这种情况下,车身系统控制单元12020可以接收从可以用作钥匙的便携式装置传输过来的无线电波或各种开关的信号。车身系统控制单元12020接收这些无线电波或信号的输入,并且控制车辆的门锁装置、电动窗装置和灯等。

车外信息检测单元12030检测关于配备有车辆控制系统12000的车辆的外部的信息。例如,车外信息检测单元12030与成像单元12031连接。车外信息检测单元12030使成像单元12031拍摄车辆外部的图像,并且接收所拍摄的图像。在接收的图像的基础上,车外信息检测单元12030可以对诸如人、车辆、障碍物、标道路记或路面上的符号等物体执行检测处理或距这些物体的距离的检测处理。

成像单元12031是光学传感器,其用于接收光并且输出与接收的光的光量对应的电信号。成像单元12031可以输出电信号作为图像,或可以输出电信号作为距离测量的信息。此外,成像单元12031接收的光可以是可见光,或可以是诸如红外线等不可见光。

车内信息检测单元12040检测关于车辆内部的信息。例如,车内信息检测单元12040与检测驾驶员状态的驾驶员状态检测单元12041连接。驾驶员状态检测单元12041例如可以包括拍摄驾驶员的图像的相机。在从驾驶员状态检测单元12041输入的检测信息的基础上,车内信息检测单元12040可以计算驾驶员的疲劳程度或驾驶员的集中程度,或可以判断驾驶员是否正在打瞌睡。

微型计算机12051可以在关于车辆内部和外部的信息(该信息是由车外信息检测单元12030或车内信息检测单元12040获得的)的基础上计算驱动力产生装置、转向机构或制动装置的控制目标值,并向驱动系统控制单元12010输出控制命令。例如,微型计算机12051可以执行旨在实现先进驾驶员辅助系统(ADAS:advanced driver assistancesystem)的功能的协同控制,该功能包括:车辆的碰撞避免或撞击减轻、基于车间距离的跟车行驶、车辆速度维持行驶、车辆碰撞警告或车辆偏离车道警告等。

此外,微型计算机12051可以执行旨在用于自动驾驶的协同控制,其在关于车辆周围情况的信息(该信息是由车外信息检测单元12030或车内信息检测单元12040获得的)的基础上通过控制驱动力产生装置、转向机构或制动装置等使车辆自主行驶,而不需要驾驶员的操作等。

此外,微型计算机12051可以在关于由车外信息检测单元12030获得的车辆外部的信息的基础上向车身系统控制单元12020输出控制命令。例如,微型计算机12051可以执行旨在防止眩光的协同控制,其包括基于车外信息检测单元12030检测到的前方车辆或对向车辆的位置控制车头灯并从远光灯变为近光灯。

声音/图像输出单元12052将声音和图像中的至少一种的输出信号传输到输出装置,该输出装置能够在视觉上或听觉上将信息通知车辆的乘客或车辆的外部。在图26的示例中,音频扬声器12061、显示单元12062和仪表面板12063被示出为输出装置。例如,显示单元12062可以包括车载显示器和平视显示器中的至少一者。

图27是示出成像单元12031的安装位置的示例的图。

在图27中,车辆12100包括作为成像单元12031的成像单元12101、12102、12103、12104和12105。

例如,成像单元12101、12102、12103、12104和12105设置在车辆12100的前鼻、侧视镜、后保险杠和后门上的位置以及车辆12100的车厢内部挡风玻璃的上部上的位置。设置到前鼻上的成像单元12101和设置到车辆的车厢内部挡风玻璃的上部上的成像单元12105主要获得车辆12100的前方环境的图像。设置到侧视镜上的成像单元12102和12103主要获得车辆12100的侧面环境的图像。设置到后保险杠或后门上的成像单元12104主要获得车辆12100的后方环境的图像。由成像单元12101和12105获得的车辆的前方环境的图像主要用于检测前方车辆、行人、障碍物、交通信号、交通标志或车道等。

需要指出的是,图27示出了成像单元12101至12104的图像拍摄范围的示例。图像拍摄范围12111表示设置到前鼻上的成像单元12101的图像拍摄范围。图像拍摄范围12112和12113分别表示设置到侧视镜上的成像单元12102和12103的图像拍摄范围,并且图像拍摄范围12114表示设置到后保险杠或后门上的成像单元12104的图像拍摄范围。例如,通过叠加由成像单元12101至12104拍摄的图像数据可以获得从上方观看到的车辆12100的俯瞰图像。

成像单元12101至12104中的至少一者可以具有获得距离信息的功能。例如,成像单元12101至12104中的至少一者可以是包括多个成像元件的立体相机,或者可以是包括用于相位差检测的像素的成像元件。

例如,微型计算机12051在从成像单元12101至12104获得的距离信息的基础上获得车辆12100和图像拍摄范围12111到12114内的每个三维物体之间的距离和距离的时间变化(相对于车辆12100的相对速度),并且可以提取特别是在车辆12100行驶的道路上最靠近车辆12100并且在与车辆12100的行驶方向基本上相同的方向上以预定速度(例如,等于或大于0千米/小时)行驶的三维物体作为前方车辆。此外,微型计算机12051可以通过预先设定在车辆12100和前方车辆之间要保持的距离来执行自动制动控制(包括跟车停止控制)或自动加速控制(包括跟车启动驱动控制)等。以这种方式,可以执行旨在实现自动驾驶的协同控制,而不需要驾驶员的操作等。

例如,微型计算机12051可以在从成像单元12101至12104获得的距离信息的基础上将三维物体的三维物体数据分类为摩托车、标准尺寸车辆、大型车辆、行人以及诸如电线杆等其他三维物体的三维物体数据,提取数据,并使用数据来自动避开障碍物。例如,微型计算机12051将车辆12100周围的障碍物分类为车辆12100的驾驶员可以看到的障碍物以及驾驶员难以看到的障碍物。然后,微型计算机12051确定表示与每个障碍物碰撞的危险程度的碰撞风险。当碰撞风险等于或高于预先设定值并且因此存在碰撞可能性的情况下,微型计算机12051可以通过经由音频扬声器12061或显示单元12062向驾驶员输出警告或通过经由驱动系统控制单元12010强制减速或者进行避让转向来执行驱动辅助以避免碰撞。

成像单元12101至12104中的至少一者可以是检测红外光的红外相机。例如,微型计算机12051可以通过确定成像单元12101至12104拍摄的图像是否包括行人来识别行人。例如,识别行人的方法包括:通过在由作为红外相机的成像单元12101至12104的拍摄图像中提取特征点的步骤以及对表示物体轮廓的一系列特征点执行图案匹配处理,从而确定物体是否是行人的步骤。当微型计算机12051确定成像单元12101至12104拍摄的图像中包括行人并且识别出行人时,声音/图像输出单元12052控制显示单元12062,使得在识别出的行人上叠加显示方形轮廓以强调行人。此外,声音/图像输出单元12052可以控制显示单元12062,使得表示行人的图标等显示在期望的位置处。

上面已经说明了可以应用根据本公开的技术的车辆控制系统的示例。例如,根据本公开的技术可以应用于上述构成中的成像单元12031等。然后,通过将根据本公开的技术应用于成像单元12031等,可以通过故障检测(BIST)来提高成品率,从而可以构造便宜的车辆控制系统。另外,可以获得不具有诸如白点和黑点等缺陷的高质量的拍摄图像。

<本公开的可能构成>

需要指出的是,本公开的技术可以具有以下构成。

<

[A-1]一种成像装置,所述成像装置具有堆叠型芯片结构,其中堆叠有至少两个半导体芯片,即第一半导体芯片和第二半导体芯片,所述第一半导体芯片设置有包括光电转换元件的像素电路,所述第二半导体芯片包括对应于所述像素电路设置的模数转换电路,

所述模数转换电路包括:在模数转换之后保持数字码的锁存电路;以及在模数转换之后传输所述数字码的传输电路,

所述成像装置包括对所述模数转换电路进行故障检测的故障检测电路,

其中,所述故障检测电路通过将用于故障检测的测试模式经由所述传输电路写入所述锁存电路、然后经由所述传输电路从所述锁存电路读出所述测试模式并且将所述读出的测试模式与期望值进行比较来进行故障检测。

[A-2]根据上述[A-1]所述的成像装置,

其中,所述测试模式是其中逻辑“1”和逻辑“0”被交替排列的交替模式。

[A-3]根据上述[A-2]所述的成像装置,

其中,所述测试模式是其中所述交替模式的逻辑与用于生成所述测试模式的时钟信号同步地反相的切换模式。

[A-4]根据上述[A-1]至[A-3]中任一项所述的成像装置,

其中,当通过对从所述像素电路输出的信号电平进行模数转换获得的数据被定义为D相数据,并且通过对复位电平进行模数转换获得的数字数据被定义为P相数据时,

所述模数转换电路具有:

作为所述锁存电路的用于测试模式写入的锁存电路、用于P相读出的锁存电路和用于D相读出的锁存电路;以及

作为所述传输电路的用于测试模式写入的传输电路、用于P相读出的传输电路和用于D相读出的传输电路。

[A-5]根据上述[A-4]所述的成像装置,

其中,所述故障检测电路:

经由所述用于测试模式写入的传输电路将所述测试模式写入所述用于测试模式写入的锁存电路;

然后,经由所述用于P相读出的传输电路从所述用于P相读出的锁存电路读出所述测试模式;

然后,经由所述用于测试模式写入的传输电路再次将所述测试模式写入所述用于测试模式写入的锁存电路;然后,

经由所述用于D相读出的传输电路从所述用于D相读出的锁存电路读出所述测试模式。

[A-6]根据上述[A-5]所述的成像装置,

其中,所述故障检测电路进行期望值比较,以评估经由所述用于P相读出的传输电路从所述用于P相读出的锁存电路读出的所述测试模式和经由所述用于D相读出的传输电路从所述用于D相读出的锁存电路读出的所述测试模式是否与期望值一致。

[A-7]根据上述[A-6]所述的成像装置,

其中,所述故障检测电路在垂直消隐时段内进行所述期望值比较的处理。

[A-8]根据上述[A-1]至[A-7]中任一项所述的成像装置,

其中,当所述传输电路以预定数量为单位划分成组时,

所述故障检测电路当执行所述传输电路的故障检测时部分地针对每个所述组进行故障检测。

<

[B-1]一种包括成像装置的电子设备,所述成像装置具有堆叠型芯片结构,其中堆叠有至少两个半导体芯片,即第一半导体芯片和第二半导体芯片,所述第一半导体芯片设置有包括光电转换元件的像素电路,所述第二半导体芯片包括对应于所述像素电路设置的模数转换电路,

所述模数转换电路包括:在模数转换之后保持数字码的锁存电路;以及在模数转换之后传输所述数字码的传输电路,

所述成像装置包括对所述模数转换电路进行故障检测的故障检测电路,

其中,所述故障检测电路通过将用于故障检测的测试模式经由所述传输电路写入所述锁存电路、然后经由所述传输电路从所述锁存电路读出所述测试模式并且将所述读出的测试模式与期望值进行比较来进行故障检测。

[B-2]根据上述[B-1]所述的电子设备,

其中,所述测试模式是其中逻辑“1”和逻辑“0”被交替排列的交替模式。

[B-3]根据上述[B-2]所述的电子设备,

其中,所述测试模式是其中所述交替模式的逻辑与用于生成所述测试模式的时钟信号同步地反相的切换模式。

[B-4]根据上述[B-1]至[B-3]中任一项所述的电子设备,

其中,当通过对从所述像素电路输出的信号电平进行模数转换获得的数据被定义为D相数据,并且通过对复位电平进行模数转换获得的数字数据被定义为P相数据时,

所述模数转换电路具有:

作为所述锁存电路的用于测试模式写入的锁存电路、用于P相读出的锁存电路和用于D相读出的锁存电路;以及

作为所述传输电路的用于测试模式写入的传输电路、用于P相读出的传输电路和用于D相读出的传输电路。

[B-5]根据上述[B-4]所述的电子设备,

其中,所述故障检测电路:

经由所述用于测试模式写入的传输电路将所述测试模式写入所述用于测试模式写入的锁存电路;

然后,经由所述用于P相读出的传输电路从所述用于P相读出的锁存电路读出所述测试模式;

然后,经由所述用于测试模式写入的传输电路再次将所述测试模式写入所述用于测试模式写入的锁存电路;然后,

经由所述用于D相读出的传输电路从所述用于D相读出的锁存电路读出所述测试模式。

[B-6]根据上述[B-5]所述的电子设备,

其中,所述故障检测电路进行期望值比较,以评估经由所述用于P相读出的传输电路从所述用于P相读出的锁存电路读出的所述测试模式和经由所述用于D相读出的传输电路从所述用于D相读出的锁存电路读出的所述测试模式是否与期望值一致。

[B-7]根据上述[B-6]所述的电子设备,

其中,所述故障检测电路在垂直消隐时段内进行所述期望值比较的处理。

[B-8]根据上述[B-1]至[B-7]中任一项所述的电子设备,

其中,当所述传输电路以预定数量为单位划分成组时,

所述故障检测电路当执行所述传输电路的故障检测时部分地针对每个所述组进行故障检测。

附图标记列表

11 第一半导体芯片(像素芯片)

12 第二半导体芯片(电路芯片)

21 像素电路

22 像素阵列单元

31 模数转换电路

32 模数转换单元

33 时间码传输单元

34 比较电路

35 数据存储单元

41 像素驱动单元

42 参考信号生成单元

43 时间码生成单元

44 垂直驱动单元

45 输出单元

46 定时生成单元

47 测试模式生成单元

48 期望值比较元

331

331

331

351 锁存电路控制单元

352 锁存电路

352

352

352

- 滤光组件、成像装置、电子设备和电子设备的成像方法

- 成像元件、成像装置、电子设备、阈值计算装置和成像方法