PECVD法沉积本征非晶硅薄膜的方法、电池制备方法及电池

文献发布时间:2023-06-19 19:07:35

技术领域

本发明涉及异质结电池领域,特别是一种PECVD法沉积本征非晶硅薄膜的方法、电池制备方法及电池。

背景技术

随着太阳能电池的发展,电池转换效率越来越高。异质结电池作为高效电池的发展方向之一,在产业中所占比重越来越高。

硅基异质结电池是一种利用晶体硅基板和非晶硅薄膜制成的混合型太阳电池,其特征是在单晶硅片的正反两侧分别沉积成型掺杂非晶硅薄膜,并在掺杂非晶硅薄膜之上形成透明导电层,在透明导电层上形成电极。硅基异质结电池的PN结由于存在着异质界面,该异质界面复合活性高,对其有效的钝化是异质结电池的核心关键技术。

为了抑制异质界面的高复合活性,在掺杂非晶硅薄膜与单晶硅片之间还形成有一层本征非晶硅薄膜,该本征非晶硅薄膜作为单晶硅片的表面的非晶硅钝化层,能对硅片表面进行有效钝化,极大的降低表面复合速率,同时较大的带隙宽度同单晶硅片形成PN结后可得到较大的内建电场,使得异质结电池具有更高的开路电压。

生长非晶硅通常使用射频等离子体沉积技术(RF-PECVD),在非晶硅薄膜生长过程中常见的问题是非晶硅薄膜在单晶硅片上出现外延生长,一旦出现外延生长,本征非晶硅薄膜的钝化效果就会大打折扣,影响异质结电池的开路电压和转换效率;为了抑制非晶硅薄膜的外延生长在成型本征非晶硅薄膜的时候一般采用高沉积速率,但采用高沉积速率会造成本征非晶硅薄膜的成长不致密,从而影响钝化效果。

因此,如何控制本征非晶硅薄膜的形成以更好的实现钝化效果具有重要的意义。

发明内容

本发明的目的是提供一种PECVD法沉积本征非晶硅薄膜的方法,以解决现有技术中的不足,它能够有效的避免由于射频功率的骤减在非晶硅薄膜上形成的硅粉层,提升了本征非晶硅薄膜的钝化效果。

本发明提供了一种PECVD法沉积本征非晶硅薄膜的方法,包括如下步骤:

以硅烷为反应气体,在硅片衬底上依次沉积第一本征非晶硅膜层和第二本征非晶硅膜层,其中,所述第一本征非晶硅膜层沉积时的沉积速率V1为0.4nm/s-1.2nm/s;第二本征非晶硅膜层沉积时的射频功率W2小于第一本征非晶硅膜层沉积时的射频功率W1;

以硅烷和氢气的混合气体为反应气体,在第二本征非晶硅膜层之上沉积成型第三本征非晶硅膜层。

进一步的,第二本征非晶硅膜层沉积时的射频功率W2与第一本征非晶硅膜层沉积时的射频功率W1之间的差值δW不超过600W。

进一步的,第一本征非晶硅膜层和第二本征非晶硅膜层均在第一反应腔内沉积成型,且在第二本征非晶硅膜层沉积时第一反应腔内的压强降低。

进一步的,第三本征非晶硅膜层的沉积速率V3小于V1;第三本征非晶硅膜层的沉积速率V3在0.03nm/s-0.3nm/s之间。

进一步的,所述第三本征非晶硅膜层的厚度大于第一本征非晶硅膜层和第二本征非晶硅膜层的厚度之和。

进一步的,在第三本征非晶硅膜层沉积成型时,硅烷和氢气的混合气体中硅烷/氢气比值范围为5:1-1:20。

进一步的,所述第二本征非晶硅膜层包括依次沉积在第一本征非晶硅膜层上的若干分层,若干分层沉积时的射频功率随沉积次序依次递减且均小于第一本征非晶硅膜层沉积时的射频功率。

本发明还公开了一种电池制备方法,包括以下步骤:

提供一N型硅片衬底并对N型硅片衬底制绒、清洗;

采用所述的PECVD法沉积本征非晶硅薄膜的方法在N型硅片衬底的上、下两侧分别沉积成型上本征非晶硅薄膜和下本征非晶硅膜层;

在上本征非晶硅薄膜的上侧沉积成型N型掺杂层;

在下本征非晶硅薄膜的下侧沉积成型P型掺杂层;

在P型掺杂层的下侧和N型掺杂层的上侧分别设置透光导电层;

在所述透光导电层上形成电极。

本发明实施例还公开了一种电池,包括:

N型硅片衬底;

设置在所述N型硅片衬底上、下两侧的上本征非晶硅薄膜、下本征非晶硅膜层;所述上本征非晶硅膜层和所述下本征非晶硅膜层均采用所述的PECVD法沉积本征非晶硅薄膜的方法沉积成型;

P型掺杂层,设置在所述下本征非晶硅膜层的下侧;

N型掺杂层,设置在所述上本征非晶硅薄膜的上侧;

透光导电层,设置在所述N型掺杂层的上侧和P型掺杂层的下侧;

电极,设置在所述透光导电层上并与透光导电层电性连接。

与现有技术相比,本发明本实施例在第一本征非晶硅膜层和第三本征非晶硅膜层之间沉积形成第二本征非晶硅膜层,并在第二本征非晶硅膜层在沉积成型的时候,射频源发出的射频功率减弱。避免了射频源从高射频功率骤减为零的情况的出现,进而避免了由于射频功率的骤减在非晶硅薄膜上形成的硅粉层,提升了本征非晶硅薄膜的钝化效果。

附图说明

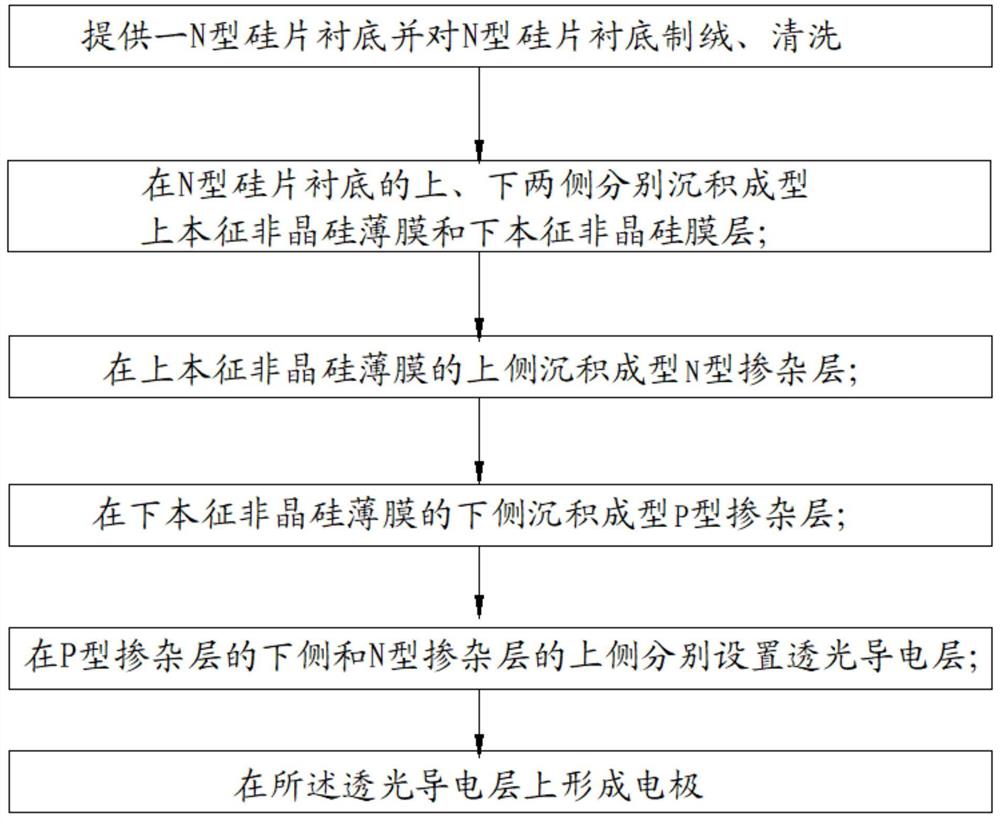

图1是本发明实施例公开的电池的制备方法的流程示意图;

图2是本发明实施例公开的电池的结构示意图。

具体实施方式

下面通过参考附图描述的实施例是示例性的,仅用于解释本发明,而不能解释为对本发明的限制。

本发明的实施例:公开了一种PECVD法沉积本征非晶硅薄膜的方法,包括如下步骤:

以硅烷为反应气体,在硅片衬底上依次沉积第一本征非晶硅膜层和第二本征非晶硅膜层,其中,所述第一本征非晶硅膜层沉积时的沉积速率V1为0.4nm/s-1.2nm/s;第二本征非晶硅膜层沉积时的射频功率W2小于第一本征非晶硅膜层沉积时的射频功率W1;第一本征非晶硅膜层和第二本征非晶硅膜层均在第一反应腔内沉积成型;

以硅烷和氢气的混合气体为反应气体,在第二本征非晶硅膜层之上沉积成型第三本征非晶硅膜层,第三本征非晶硅膜层可以是单层膜结构,也可以是含不同SiH4/H2比例的多层膜结构;第三本征非晶硅膜层在第二反应腔内沉积成型。

本实施例公开的本征非晶硅薄膜一共包括三层,三层本征非晶硅薄膜依次沉积成型在硅片衬底上,硅片衬底可以为N型单晶硅片,第一本征非晶硅膜层直接沉积成型在硅片衬底上,并且第一本征非晶硅膜层沉积时采用较高的沉积速率,较高的沉积速率能够有效的抑制非晶硅薄膜的外延生长。

之所以会产生非晶硅薄膜的外延生长是因为硅片衬底为晶体硅,晶体硅的表面态具有较多的未饱和的悬挂键,如果沉积速率低,在非晶硅薄膜沉积的时候会优先与晶体硅的悬挂键结合,从而造成悬挂键所在位置形成外延生长。

采用高沉积速率使非晶硅膜层在沉积的时候电离出的大量的Si离子或者基团来不及选择,在硅片衬底的上表面同时沉积,因此有效的避免了非晶硅薄膜的外延生长。本实施例中第一本征非晶硅膜层沉积时的功率设置为0.4nm/s-1.2nm/s,在该区间内的沉积速率能够有效的抑制非晶硅膜层的外延生长。

高沉积速率虽然能够有效的抑制非晶硅薄膜的外延生长,但是会造成本征非晶硅薄膜成长的不致密,从而影响钝化效果。为了使本征非晶硅膜层具有较好的钝化效果一般会在第一本征非晶硅膜层上采用低沉积速率形成第三本征非晶硅膜层,并且在第三本征非晶硅膜层沉积成型的时候反应气源内会掺杂有氢气。也就是第三本征非晶硅膜层沉积成型的时候在反应腔内的气体是硅烷和氢气的混合气体,掺杂氢气能够使反应气源电离出更多的Si-H键,更多的Si-H键有利于钝化。

由于在第三本征非晶硅膜层沉积的时候采用的是氢气和硅烷形成的混合气体,与第一本征非晶硅膜层沉积的时候只使用硅烷作为反映气源不同,为了保持生产制造的连续性,一般将第一本征非晶硅膜层和第三本征非晶硅膜层在不同的反应腔内完成。

在第一反应腔内沉积第一本征非晶硅膜层,并且在第一反应腔内供给的气源是硅烷;在第二反应腔内沉积第三本征非晶硅膜层,并且在第二反应腔内供给的气源是硅烷与氢气的混合气体。如果在一个反应腔内沉积成型需要较长的换气时间,从而影响了设备的生产连续性。

在第一本征非晶硅膜层沉积完成后需要更换不同的反应腔,在对反应腔进行更换的时候需要关闭射频源,这样造成了在第一本征非晶硅膜层沉积后射频源发出的射频功率从一个很高的状态骤减为零,此时在第一反应腔的腔内会弥漫着大量电离后的Si离子或基团,这些离子或基团量较大无法被泵体及时抽走,因此容易在第一本征非晶硅上沉积一层硅粉层,硅粉层的存在会影响本征非晶硅薄膜的钝化效果。

为了避免上述技术问题的出现,本实施例创造性的在第一本征非晶硅膜层和第三本征非晶硅膜层之间沉积形成第二本征非晶硅膜层,第二本征非晶硅膜层和第一本征非晶硅膜层均在第一反应腔内沉积形成,并且在沉积成型的过程中第一反应腔内供给的反应气源均为硅烷。

第二本征非晶硅膜层在沉积成型的时候,射频源发出的射频功率W2相比于第一本征非晶硅膜层在沉积成型的时候所使用的射频功率W1更小。第二本征非晶硅膜层和第一本征非晶硅膜层在第一反应腔内连续沉积成型,在第一本征非晶硅膜层沉积成型后直接将射频源从高射频功率降低至第二本征非晶硅膜层沉积时需要的低射频功率,然后再沉积成型第二本征非晶硅膜层之后将射频源关闭。

第二本征非晶硅膜层的设置避免了射频源从高射频功率骤减为零的情况的出现,进而避免了由于射频功率的骤减在非晶硅薄膜上形成的硅粉层,提升了本征非晶硅薄膜的钝化效果。

进一步的,第二本征非晶硅膜层沉积时的射频功率W2与第一本征非晶硅膜层沉积时的射频功率W1之间的差值δW不超过600W。第二本征非晶硅膜层沉积时的射频源的射频功率的骤减量不能超出600W,在超出600W后容易出现硅粉层的沉积。

在具体实施例中第一本征非晶硅膜层沉积时的射频功率一般为400-1000W,第二本征非晶硅膜层沉积时的射频功率一般为100-300W。

第三本征非晶硅膜层在沉积时的速率偏低,相应的射频功率一般也较第一本征非晶硅膜层沉积时小,在具体实施例中,所述第三本征非晶硅膜层沉积时的射频功率为150W-400W。

为了更好的避免硅粉层的形成,第二本征非晶硅膜层沉积时第一反应腔内的压强P2小于第一本征非晶硅膜层沉积时第一反应腔内的压强P1。压强的降低能够减少第一反应腔内的气体总量,从而使电离出的气体分子也减少。

在具体实施例中,第一本征非晶硅膜层沉积时第一反应腔内的压强的取值范围为0.5-0.7torr,第二本征非晶硅膜层沉积时第一反应腔内的压强的取值范围为0.2-0.5torr。

相应的也可以通过控制气源的流量降低进入反应腔内的气体的量,从而降低电离出的气体分子。在本实施例中,仅通过改变气压改变反应腔内的气体的量。在第一本征非晶硅膜层沉积时,第一反应腔内的硅烷的流量的取值范围为500-2000sccm,在第二本征非晶硅膜层沉积时,第二反应腔内的硅烷的流量的取值范围为500-2000sccm。

上述实施例给出的是在第一本征非晶硅膜层与第三本征非晶硅膜层之间沉积形成一层第二本征非晶硅膜层。在另一实施例中所述第二本征非晶硅膜层包括若干分层,若干分层沉积时的射频功率随沉积次序依次递减且均小于第一本征非晶硅膜层沉积时的射频功率。若干分层中最先沉积在第一本征非晶硅膜层上的一层在沉积时的射频功率最大,随着不断向上沉积射频功率不断的降低。

可以理解的是,在分层依次不断向上沉积的时候,第一反应腔内的压强也逐渐降低,压强的降低能够降低反应腔内硅烷的含量,从而使电离出的气体分子也减少。

第三本征非晶硅膜层作为最上层的一层膜层,其主要起到钝化的作用,因此为了保证其有较好的钝化效果,所述第三本征非晶硅膜层沉积成型时的的沉积速率V3小于V1;作为优选的方案第三本征非晶硅膜层的沉积速率V3的取值范围在0.03nm/s-0.3nm/s之间。第二本征非晶硅膜层的沉积速率V2的取值范围在0.1nm/s-0.3nm/s之间。

第二本征非晶硅膜层实际上是属于第一本征非晶硅膜层和第二本征非晶硅膜层之间的过渡层,第二本征非晶硅膜层实际上是在分档关闭射频源的过程中在第一本征非晶硅膜层上的产物。第一本征非晶硅膜层主要起到抑制非晶硅膜层外延生长的作用,第三本征非晶硅膜层主要起到钝化的作用,而第二本征非晶硅膜层主要是防止射频源在骤减后出现硅粉层,钝化的作用微弱,因此,将第二本征非晶硅膜层的厚度设置成不高于第一本征非晶硅膜层的厚度。同时,所述第三本征非晶硅膜层的厚度大于第一本征非晶硅膜层和第二本征非晶硅膜层的厚度之和。第三本征非晶硅膜层主要起钝化作用,因此厚度设置的要大于前两者。

在具体的实施例中,所述第一本征非晶硅膜层的厚度的取值范围在1nm-3nm之间,第二本征非晶硅膜层的厚度的取值范围在0.5-2nm之间,第三本征非晶硅膜层的厚度的取值范围在2nm-10nm之间。

为了更好的使第三本征非晶硅膜层起到钝化效果,在第三本征非晶硅膜层沉积成型时,硅烷和氢气的混合气体中硅烷/氢气比值范围为5:1-1:20。

本发明还给出了一具体实施例1,为了验证采用本发明方案的实施例1具有显著的进步对比设置了两组对比实验,在对比实验1中,在成型本征非晶硅薄膜的时候采用的是两个沉积速率控制,并沉积成两层。在对比实验1中先以高速沉积速率沉积形成起到抑制非晶硅膜层外延生长的第一膜层,然后再以低沉积速率沉积形成起到钝化作用的第二膜层。在对比实验2中在成型本征非晶硅薄膜的时候则采用单一的沉积速率直接沉积成型本征非晶硅薄膜。

具体的,实施例1的方案中形成的本征非晶硅薄膜的具体方法如下:

首先,在第一反应腔内,以硅烷为反应气源沉积形成第一本征非晶硅膜层,沉积过程中第一反应腔内的温度控制在200℃,第一反应腔内的压强控制在0.6torr,硅烷SiH4在第一反应腔内的供给的流量控制在1000sccm,采用射频化学气相沉积方法时的射频功率W1为500W,沉积速率控制在0.7nm/s,沉积厚度控制在2.2nm;

其次,在第一反应腔内,以硅烷为反应气源沉积形成第二本征非晶硅膜层,在第二本征非晶硅膜层沉积的过程中,第一反应腔内的温度控制在200℃,第一反应腔内的压强控制在0.5torr,硅烷SiH4在第一反应腔内的供给的流量控制在1000sccm,采用射频化学气相沉积方法时的射频功率W2为250W,沉积速率控制在0.2nm/s,沉积厚度控制在1.2nm;在第二本征非晶硅膜层沉积完成后需要关闭第一反应腔内的射频源,然后将硅片衬底转移到第二反应腔内继续沉积成型;

最后,在第二反应腔内沉积成型第三本征非晶硅膜层,在第三本征非晶硅膜层沉积的时候第二反应腔内的温度控制在200℃,第二反应腔内的压强控制在0.6torr,此时在第二反应腔内的反应气源为硅烷和氢气的混合气体,其中硅烷与氢气的混合比SiH4/H2=500:1000,在第三本征非晶硅膜层沉积的时候,采用射频化学气相沉积方法时的射频功率W3为150W,沉积速率控制在0.1nm/s,沉积的厚度控制在4.2nm。

对比实验1的具体方案如下:

首先,在第一反应腔内,以硅烷为反应气源沉积第一膜层,沉积过程中第一反应腔内的温度控制在200℃,第一反应腔内的压强控制在0.6torr,硅烷SiH4在第一反应腔内供给的流量控制在1000sccm,采用射频化学气相沉积方法时射频功率控制在500W,沉积速率控制在0.7nm/s,沉积厚度控制在2.2nm;

然后,在第二反应腔内,以硅烷和氢气的混合气体为反应气源沉积第二膜层,在第二膜层的沉积过程中,第二反应腔内的温度控制在200℃,第二反应腔内的压力控制在0.6torr,第二反应腔内的反应气源中硅烷和氢气的混合比SiH4/H2=500:1000,采用射频化学气相沉积方法时的射频功率为150W,沉积速率控制在0.1nm/s,沉积厚度控制在5.4nm。

对比实验2的具体方案如下:

在第二反应腔内沉积成型本征非晶硅薄膜,其中本征非晶硅薄膜沉积成型时的温度控制在200℃,在本征非晶硅薄膜沉积成型的时候的压强控制在0.6torr,本征非晶硅薄膜沉积时第二反应腔内供给的反应气体为硅烷和氢气的混合气体,其中硅烷和氢气的混合比例为SiH4/H2=500:500,在本征非晶硅薄膜沉积时射频源的射频功率控制在200W,沉积速率控制在0.15nm/s,厚度控制在5.4nm。

为了验证实施例1的有益性,分别对具有实施例1、对比实验1和对比实验2的本征非晶硅薄膜的电池片进行了相关参数的测试,测试结果如下所示:

测试结果显示:

对于电池片的开路电压(Voc),采用实施例1的本征非晶硅薄膜的电池片相较于采用对比实验1的本征非晶硅薄膜的电池片提升了1.5mV,相比于采用对比实验2的本征非晶硅薄膜的电池片提升了1.7mV;

对于填充因子(FF)用实施例1的本征非晶硅薄膜的电池片相较于采用对比实验1的本征非晶硅薄膜的电池片提升了0.2%,用实施例1的本征非晶硅薄膜的电池片相较于采用对比实验2的本征非晶硅薄膜的电池片0.5%;

对于转换效率(EFF)用实施例1的本征非晶硅薄膜的电池片相较于采用对比实验1的本征非晶硅薄膜的电池片提升了提升0.09%,用实施例1的本征非晶硅薄膜的电池片相较于采用对比实验2的本征非晶硅薄膜的电池片提升了0.21%。

由此可见采用本申请实施例公开的方法沉积形成的非晶硅薄膜的较好的钝化效果,具有该本征非晶硅薄膜的电池片的开路电压具有较大提升,同时电池片的填充因子(FF)以及转换效率(EFF)都得到大幅提升,提高了电池片的使用效率。

如图2所示,本发明还公开了一种电池制备方法,包括以下步骤:

提供一N型硅片衬底并对N型硅片衬底制绒、清洗;

采用上述所述的PECVD法沉积本征非晶硅薄膜的方法在N型硅片衬底的上、下两侧分别沉积成型上本征非晶硅薄膜和下本征非晶硅膜层;

在上本征非晶硅薄膜的上侧沉积成型N型掺杂层;

在下本征非晶硅薄膜的下侧沉积成型P型掺杂层;

在P型掺杂层的下侧和N型掺杂层的上侧分别设置透光导电层;

在所述透光导电层上形成电极。

如图1所示,本发明的另一实施例还公开了一种异质结电池,包括:

N型硅片衬底;

设置在所述N型硅片衬底上、下两侧的上本征非晶硅薄膜、下本征非晶硅膜层;

P型掺杂层,设置在所述下本征非晶硅薄膜的下侧;

N型掺杂层,设置在所述上本征非晶硅膜层的上侧;

透光导电层,设置在所述N型掺杂层的上侧和P型掺杂层的下侧;

电极,设置在所述透光导电层上并与透光导电层电性连接。

以上依据图式所示的实施例详细说明了本发明的构造、特征及作用效果,以上所述仅为本发明的较佳实施例,但本发明不以图面所示限定实施范围,凡是依照本发明的构想所作的改变,或修改为等同变化的等效实施例,仍未超出说明书与图示所涵盖的精神时,均应在本发明的保护范围内。

- 非晶薄膜后氢化处理方法及硅异质结太阳电池制备方法

- 一种用箱体式PECVD设备制备非晶硅锗薄膜电池的方法

- 具有渐变锗组分本征层的非晶硅薄膜太阳电池及其制备方法