半导体元件的制造方法、半导体元件以及半导体装置

文献发布时间:2024-01-17 01:20:32

技术领域

本公开涉及半导体元件的制造方法、半导体元件以及半导体装置。

背景技术

在专利文献1中,记载了使用自支撑GaN系基板并通过ELO(Epitaxial LateralOver Growth,外延横向过生长)法制作的SBD(Schottky Barrier Diode,肖特基势垒二极管)。

在先技术文献

专利文献

专利文献1:JP专利第6070422号公报

发明内容

1个方式所涉及的半导体元件的制造方法包含:第1工序,在基板的表面上形成具有开口的掩模;第2工序,从由所述开口露出的所述表面起,使半导体沿着所述掩模外延生长,生长第1半导体层;和第3工序,生长第2半导体层,在位于层叠方向上与所述基板相反的一侧且设置电极的表面,从所述表面的端部到所述电极的宽度比所述掩模的宽度小。

1个方式所涉及的半导体元件通过上述的半导体元件的制造方法而被制造,在半导体元件的内部,所述掩模存在于所述基板与所述第1半导体层之间。

1个方式所涉及的半导体装置包含通过上述的半导体元件的制造方法而被制造的半导体元件。

附图说明

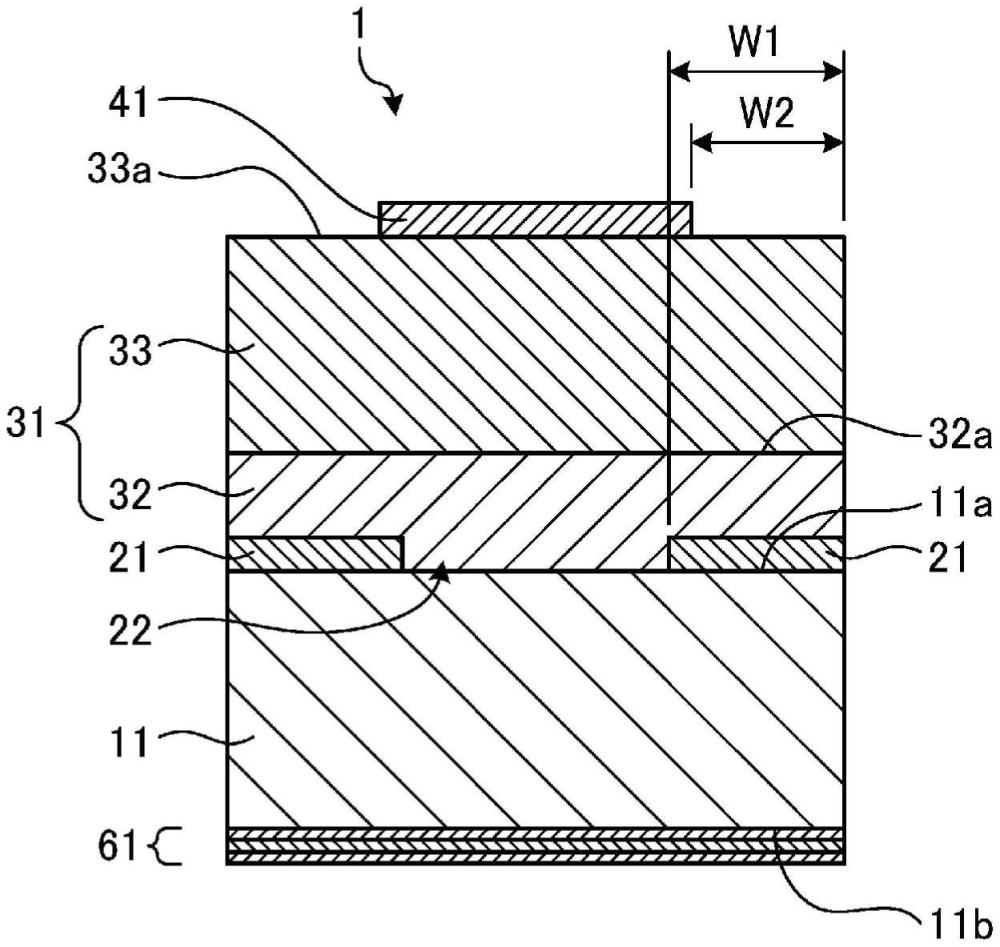

图1是用于说明实施方式所涉及的半导体元件的截面示意图。

图2是用于说明实施方式所涉及的半导体元件的制造方法以及半导体元件的截面示意图。

图3是用于说明实施方式所涉及的半导体元件的俯视示意图。

图4是用于说明实施方式所涉及的半导体元件以及半导体装置的示意图。

图5是用于说明实施方式所涉及的半导体元件的制造方法的工序图。

图6是用于说明实施方式所涉及的半导体装置的制造方法的工序图。

图7是用于说明实施方式的变形例1所涉及的半导体元件的一例的截面示意图。

图8是用于说明实施方式的变形例1所涉及的半导体装置的制造方法的工序图。

图9是用于说明实施方式的变形例2所涉及的半导体元件的截面示意图。

图10是用于说明实施方式的变形例3所涉及的半导体元件的截面示意图。

具体实施方式

使用自支撑GaN系基板制造的SBD会在设有阳极电极的表面的端部耐压部在各种方向上产生结晶缺陷。在端部耐压部,沿着电场方向在表面产生结晶缺陷的情况下,即使覆盖绝缘膜,也会产生成为泄漏源的杂质能级。如此地,沿着电场方向产生的结晶缺陷成为泄漏电流的路径。由此,SBD的耐压性降低。

以下说明实施方式所涉及的半导体元件1的制造方法、半导体元件1以及半导体装置2。半导体元件1是逆变器以及转换器这样的电路变换器的开关电路中使用的功率半导体。

[实施方式]

(制造方法)

图1是用于说明实施方式所涉及的半导体元件的截面示意图。图2是用于说明实施方式所涉及的半导体元件的制造方法以及半导体元件截面示意图。图3是用于说明实施方式所涉及的半导体元件的俯视示意图。图4是用于说明实施方式所涉及的半导体元件以及半导体装置的示意图。

如图1到图3所示那样,通过实施方式所涉及的制造方法制造的半导体元件1在基板11上形成半导体层31。半导体层31在基板11按从近到远的顺序层叠作为n+型半导体层的GaN层(第1半导体层)32、作为n-型半导体层的GaN层(第2半导体层)33。在半导体元件1的内部,掩模21存在于基板11与GaN层32之间。如图4所示那样,半导体装置2包含这样制造的半导体元件1。

参考图1、图2、图5来说明半导体元件1的制造方法。图5是用于说明实施方式所涉及的半导体元件的制造方法的工序图。半导体元件1的制造方法沿着图5所示的工序执行。

图1、图2所示的基板11是n+型的自支撑GaN。基板11控制n型杂质的掺杂量,以使得成为10

基板11表层的与GaN层的表面11a相反的一侧的背面11b可以被未图示的硅基板等GaN以外支承。支承基板11表层的GaN层的背面11b的基板例如可以是蓝宝石基板或SiC(Silicon Carbide,碳化硅)基板。

首先,在图2所示的基板11表层的GaN层的表面11a形成基于SiO

掩模21可以包含成为半导体层31中的施主的元素。作为掩模21的材料,可以使用W以及Ti等金属、SiN、AlN等氮化物、Al

从掩模21的开口22露出与开口22对应的部分的基板11的表面11a。另外,位于基板11的两端的表面11a可以被掩模21覆盖。此外,也可以基板11的侧面或背面的整体被掩模21覆盖。也可以会与后述的气相生长法中所用的原料气体接触的面当中的除了开口22以外的整体被掩模21覆盖。

与掩模21的层叠方向正交的横向的宽度w1例如为10μm以上。掩模21的层叠方向的厚度例如为100nm。

接下来,如图2所示那样,使用上述的ELO技术,从由开口22露出的基板11的表面11a起形成作为半导体层31的GaN层(步骤ST12)(第2工序)。更详细地,使用ELO技术,在未图示的外延装置中,从由开口22露出的基板11的表面11a起沿着掩模21使GaN外延生长,使高杂质浓度的n+型的GaN层32外延生长。

GaN层32从由开口22露出的表面11a起,在开口22的层叠方向的上方在纵向上生长,在比开口22更靠外周侧横向地生长。GaN层32的表面32a大致平坦。GaN层32在结晶生长时从构成掩模21的材料自动掺杂杂质。在杂质是Si(Silicon,硅)时,GaN层32是被高浓度掺杂的n+半导体层。GaN层32控制n型杂质的掺杂量,以使得成为10

进而,为了得到所期望的杂质浓度分布,形成低杂质浓度的GaN层33,以使得覆盖GaN层32(步骤ST13)(第3工序)。更详细地,从GaN层32的表面32a起形成低杂质浓度的n-型的GaN层33。

选择纵向的生长比横向的生长更优势地生长的条件,使GaN层33从GaN层32的表面32a起生长。GaN层33的表面33a大致平坦。GaN层33的表面33a是位于与基板11在层叠方向上相反的一侧且设置上表面电极的表面。GaN层33是n-半导体层。GaN层33控制n型杂质的掺杂量,以使得成为小于10

如以上那样,如图1、图2所示那样,从由开口22露出的表面11a起沿着掩模21使半导体外延生长,来制作具有半导体层31的半导体元件1。半导体层31在基板11上作成,从表面起在层叠方向上外延生长作为n+型半导体层的GaN层32以及作为n-型半导体层的GaN层33。

如图3所示那样,半导体元件1在从层叠方向的上方来看的层叠方向观察下成为六边形状。这是因为,外延生长中的结晶的生长方向是决定了的。半导体元件1的半导体层31在开口22的层叠方向的上方在纵向上生长结晶,在比开口22更靠外周侧在横向上生长结晶。由此,半导体元件1的GaN层33的表面33a中的结晶缺陷在中央部在纵向上延伸,在比中央部更外周侧在横向上延伸。

接下来,参考图1、图6来说明包含半导体元件1的半导体装置2的制造方法。图6是用于说明实施方式所涉及的半导体装置的制造方法的工序图。半导体装置2的制造方法在沿着图5所示的工序制作半导体元件1后,沿着图6所示的工序执行。步骤ST21到步骤ST22在进行步骤ST11到步骤ST13后进行。

在基板11的与半导体层31相反的以侧的背面11b形成背面电极61(步骤ST21)。更详细地,在基板11的背面11b例如通过建设等形成背面电极61。

背面电极61例如是在Al层实施Ti、Ni、Au镀覆而得到的结构。另外,背面电极61的形成可以在形成后述的肖特基电极41后形成。在包含提高温度的工序的情况下等,通过最后进行步骤ST21,能避免给背面电极61带来的影响。

在半导体层31的GaN层33的表面33a形成作为金属层(势垒金属)的肖特基电极41(步骤ST22)。由此,设置GaN层33与肖特基电极41的肖特基结。

肖特基金属膜41例如是Ni、Al、Pd等。肖特基金属膜41位于在层叠方向上与基板11相反的一侧。肖特基金属膜41设于GaN层33的表面33a的中央部。从GaN层33的表面33a的端部到肖特基金属膜41的宽度(端部耐压部的宽度)w2比掩模21的宽度w1小。在GaN层33的表面33a,将从表面33a的端部到肖特基金属膜41称作端部耐压部。

通过以上来制造半导体元件1。所制造的半导体元件1例如能作为具有肖特基结的SBD使用。在所制造的半导体元件1的内部,掩模21存在于基板11与GaN层32之间。

也可以同时并行实施以上说明的制造工艺,以使得同时制造多个半导体元件1。在该情况下,在掩模21条带状地形成多个开口22。通过使一个半导体元件1与一个开口22对应,能同时制作多个半导体元件1。

在条带状的掩模的情况下,结晶成为2边较长的六边形状,较长的2边的截面图成为图4那样。

同时制造的各半导体元件1可以分离成单片来作为半导体装置2。在需要大容量化的情况下,作为一例,也可以在多个半导体元件1共享基板11以及背面电极61地如图4所示那样安装,作为半导体装置2来利用。具体地,如图4所示那样,通过将共通的背面电极61与安装基板200上的一个电极焊盘201管芯键合,来将各个未图示的上表面电极金属膜通过键合引线52与其他电极焊盘202连接。如此地,通过对安装基板200进行安装,能将多个二极管并联连接来大容量化地利用。这时,将多个半导体元件1制造成在固定方向上并排。半导体元件1在层叠方向观察下,在相对于半导体元件1所并排的方向的大致正交方向上设为长条的形状。通过将半导体元件1并排成这样的形状,能加大二极管的接合面积。如此地制造的半导体元件1能配合用途作为各种半导体装置2利用。

通过以上,在本实施方式中,在半导体元件1的内部,掩模21存在与基板11与GaN层32之间。在本实施方式中,从GaN层33的表面33a的端部到肖特基金属膜41的宽度w2比掩模21的宽度w1小。在本实施方式中,在开口22的层叠方向的上方,纵向地生长结晶,在比开口22更靠外周侧,横向地生长结晶。在本实施方式中,端部耐压部中的结晶缺陷的方向为横向。由此,根据本实施方式,在端部耐压部,能减少沿着会成为半导体元件1的泄漏电流的路径的电场方向的结晶缺陷的产生。本实施方式能提升SBD的耐压性。

在本实施方式中,掩模21的宽度w1例如是10μm以上。本变形例能缩窄端部耐压部的宽度w2(<w1)。根据本变形例,能提高半导体元件1的通电区域的比率。本实施方式由于能将半导体元件1小型化,因此,能削减成本。

[变形例1]

参考图7、图8来说明实施方式的变形例1。图7是用于说明实施方式的变形例1所涉及的半导体元件的一例的截面示意图。图8是用于说明实施方式的变形例1所涉及的半导体装置的制造方法的工序图。如图7所示那样,变形例1所涉及的半导体元件1具有台面构造以及场板构造。半导体装置2包含这样的半导体元件1。另外,图7为了说明而将高低差描绘得大。在以下的图中也同样。

说明包含半导体元件1的半导体装置2的制造方法。步骤ST11、步骤ST12与实施方式同样地进行。换言之,半导体元件1与实施方式同样地制作。步骤ST21与实施方式同样地进行。即,在进行实施方式的步骤ST11到步骤ST21后执行步骤ST22到步骤ST25的工序。

对GaN层33的一部分进行干式蚀刻(步骤ST22)。更详细地,对GaN层33的表面33a的一部分进行干式蚀刻。具体地,对GaN层33的外周部进行干式蚀刻。GaN层33的表面33a的端部具有台面构造。换言之,剩余的GaN层33的外周部具有台面高低差33s。GaN层33的外周部在比表面33a更靠近GaN层32的位置、换言之低一级的位置具有表面33c。

在露出的GaN层33的表面33a形成做出肖特基结的肖特基金属膜41(步骤ST23)。通过肖特基金属膜41,覆盖露出的GaN层33的表面33a。由此,设置GaN层33与肖特基金属膜41的肖特基结。

形成作为绝缘层的绝缘膜42(步骤ST24)。绝缘膜42覆盖露出的GaN层33和肖特基金属膜41的外周部地配置。绝缘膜42具有:覆盖肖特基金属膜41的外周部的壁部421;覆盖GaN层33的侧面33b的壁部422;和覆盖GaN层33的表面33c的壁部423。壁部421在中央部具有露出肖特基金属膜41的开口。壁部422从壁部421的外周侧的端部向层叠方向的下方延伸。壁部423从壁部422的层叠方向的下方的端部向外周侧延伸。

在肖特基金属膜41上以及绝缘膜42上形成上表面电极金属膜43(步骤ST25)。上表面电极金属膜43在绝缘膜42上形成所谓场板。从上表面电极金属膜43露出绝缘膜42的壁部423的外周侧的端部。

背面电极形成工序即步骤ST21在其退火温度下不会给肖特基金属膜41、绝缘膜42、上表面电极金属膜43带来影响的情况下,也可以在步骤ST25之后进行。

通过以上来制造具有台面构造以及场板构造的半导体元件1。由于通过具有场板,能缓和加在上表面电极的端部的电场,因此,成为耐压高的器件。场板可以与上部电极分离。

在本变形例中,通过具有台面高低差33s,能缓和加在上表面电极的端部的电场。在本变形例中,通过具有场板,能缓和加在上表面电极的端部的电场。由此,根据本变形例,能制造提高了浪涌耐量电流的半导体元件1。根据本变形例,能制造提高了耐压性的半导体元件1。

在本变形例中,端部耐压部中的结晶方向为横向,减少了沿着会成为半导体元件1的泄漏电流的路径的电场方向的表面的结晶缺陷的产生。由此,本变形例能降低台面高低差33s的层叠方向的高度。本变形例能缩窄端部耐压部的宽度w2。由此,本变形例能提高半导体元件1的通电区域的比率。根据本实施方式,由于能将半导体元件1小型化,因此,能削减成本。

[变形例2]

参考图9来说明实施方式的变形例2。图9是用于说明实施方式的变形例2所涉及的半导体元件的截面示意图。变形例2所涉及的半导体元件1具有台面构造、场板构造以及沟槽构造。

说明包含半导体元件1的半导体装置2的制造方法。步骤ST11到步骤ST13与实施方式同样地进行。换言之,半导体元件1与实施方式同样地制作。步骤ST21与实施方式同样地进行。即,在进行从实施方式的步骤ST11到步骤ST21后,执行步骤ST22到步骤ST25的工序。在以下中,说明与变形例1不同的工序。

在步骤ST22,通过干式蚀刻来在GaN层33形成台面高低差33s以及沟槽构造33t。更详细地,剩余的GaN层33的外周部具有台面高低差33s。在比剩余的GaN层33的外周部更靠内侧具有槽状的沟槽构造33t。在GaN层33中,在未形成台面高低差33s以及沟槽构造33t的部分残留表面33a的一部分。

在步骤ST23,在比台面高低差33s更靠内侧残留的表面33a上形成肖特基金属膜41。

在步骤ST24,覆盖未被肖特基金属膜41覆盖的GaN层33的露出面,来形成绝缘膜42。

在步骤ST25,在肖特基金属膜41上以及绝缘膜42上形成上表面电极金属膜43。

通过以上来制造具有台面构造、场板构造以及沟槽构造的半导体元件1。

在本变形例中,通过具有沟槽构造,能缓和加在上表面电极的中央部的电场。根据本变形例,能制造更加提高耐压性的半导体元件1。

[变形例3]

参考图10来说明实施方式的变形例3。图10是用于说明实施方式的变形例3所涉及的半导体元件的截面示意图。变形例3所涉及的半导体元件1具有台面构造、场板构造以及JBS构造。变形例3所涉及的半导体元件1的半导体层31在基板11按从近到远的顺序层叠作为n+型半导体层的GaN层(第1半导体层)32、作为n-型半导体层的GaN层(第2半导体层)33、作为p+型半导体层的GaN层(第1半导体层)34。

说明包含半导体元件1的半导体装置2的制造方法。在变形例3中,在执行步骤ST11到步骤ST13后,执行未图示的步骤ST14。

进而,为了得到所期望的高杂质浓度分布,形成高杂质浓度的p+型的GaN层34,以使得覆盖GaN层33(步骤ST14)。

GaN层34控制p型杂质的掺杂量,以使得成为10

步骤ST21以及步骤ST25与变形例2同样地进行。

在步骤ST22,对GaN层34以及GaN层33的一部分进行干式蚀刻,来形成台面高低差33s以及沟槽构造33t。

在步骤ST23,对在比台面高低差33s更靠内侧残留于中央的GaN层34、以及在比GaN层33更靠外侧露出的GaN层34以及GaN层33上形成肖特基金属膜41。换言之,肖特基金属膜41在层叠方向观察下将中央部和端部除外来配置。

在步骤ST24,覆盖未被肖特基金属膜41覆盖的GaN层33的露出面来形成绝缘膜42。

通过以上来制造具有台面构造、场板构造以及JBS构造的半导体元件1。另外,具有JBS构造的半导体元件1并不限定于此。例如,半导体元件1也可以是肖特基势垒二极管。

在本变形例中,通过具有JBS构造,能缓和加在上表面电极的中央部的电场。根据本变形例,能制造更加提高了耐压性的半导体元件1。本变形例能减少泄漏电流。

本申请所公开的实施方式能在不脱离发明的要旨以及范围的范围内变更。进而,本申请所公开的实施方式以及其变形例能适宜组合。

为了完整且清晰地公开添附的权利要求所涉及的技术而关于特征性的实施方式进行了记载。但添附的权利要求并不应限定于上述实施方式,构成为在本说明书所示的基础的事项的范围内由该技术领域的本领域技术人员创造的全部变形例以及能代替的结构具体化。

符号说明

1半导体元件

2半导体装置

11基板

11a表面

21掩模

22开口

31半导体层

32GaN层(第1半导体层)

33GaN层(第2半导体层)

61背面电极

200安装基板

201电极焊盘

202电极焊盘。

- 半导体装置、半导体装置的制造方法以及半导体封装的制造方法

- 用于储存和运输半导体元件的装置及其制造方法

- 树脂组合物、树脂膜、半导体层叠体、半导体层叠体的制造方法及半导体装置的制造方法

- 树脂组合物、树脂膜、半导体层叠体、半导体层叠体的制造方法及半导体装置的制造方法

- 成膜方法、真空处理装置、半导体发光元件的制造方法、半导体发光元件、半导体电子元件的制造方法、半导体电子元件、照明装置

- 成膜方法、真空处理装置、半导体发光元件的制造方法、半导体发光元件、半导体电子元件的制造方法、半导体电子元件、照明装置