半导体装置及其制作方法

文献发布时间:2023-06-19 11:42:32

技术领域

本揭露实施例是有关于一种半导体装置及其制作方法。

背景技术

由于各种电子组件(例如,晶体管、二极管、电阻器、电容器等)的集成密度的持续提高,半导体行业已经历快速增长。在很大程度上,集成密度的这一提高是源自最小特征大小(minimum feature size)的连番减小,此使更多的组件能够集成到给定的面积中。随着近来对小型化、较高的速度、较大的频宽、较低的功率损耗及较少的延迟的需求的增加,对半导体管芯的翘曲控制技术的需要也随着增加。

发明内容

本揭露实施例提供一种半导体装置,所述半导体装置包括第一半导体管芯、第二半导体管芯、绝缘包封体及翘曲控制图案。所述第一半导体管芯包括有源表面及与所述有源表面相对的后表面。所述第二半导体管芯设置在所述第一半导体管芯的所述有源表面上。所述绝缘包封体设置在所述第一半导体管芯的所述有源表面上并侧向包封所述第二半导体管芯。所述翘曲控制图案设置在所述第一半导体管芯的所述后表面上并部分覆盖所述后表面。

本揭露实施例提供一种半导体装置,所述半导体装置包括中介层、半导体装置、第二绝缘包封体、以及底部填料。所述半导体装置设置在所述中介层上并电连接到所述中介层,所述半导体装置包括:第一半导体管芯,包括第一表面及与所述第一表面相对的第二表面;第二半导体管芯,与所述第一半导体管芯的所述第一表面接合;第一绝缘包封体,设置在所述第一半导体管芯的所述第一表面上并侧向包封所述第二半导体管芯,其中所述第一绝缘包封体的多个侧壁实质上与所述第一半导体管芯的多个侧壁对齐;以及翘曲控制图案,设置在所述第一半导体管芯的所述第二表面上并部分覆盖所述第二表面。所述第二绝缘包封体设置在所述中介层上并侧向包封所述半导体装置。所述底部填料设置在所述半导体装置与所述中介层之间。

本揭露实施例提供一种半导体装置的制作方法,包括:提供包括多个第一半导体管芯的半导体晶片;将多个第二半导体管芯设置在所述半导体晶片上,使得所述多个第二半导体管芯电连接到所述半导体晶片的所述多个第一半导体管芯;用形成在所述半导体晶片上的第一绝缘包封体侧向包封所述多个第二半导体管芯;在所述半导体晶片的后表面上形成多个翘曲控制图案;以及将所述半导体晶片单体化以形成多个半导体装置,所述多个半导体装置中的每一者包括所述多个第一半导体管芯中的至少一个第一半导体管芯、所述多个第二半导体管芯中的至少一个第二半导体管芯、以及所述多个翘曲控制图案中的至少一个翘曲控制图案。

附图说明

结合附图阅读以下详细说明,会最好地理解本公开的各个方面。应注意,根据本行业中的标准惯例,各种特征并非按比例绘制。事实上,为论述清晰起见,可任意增大或减小各种特征的尺寸。

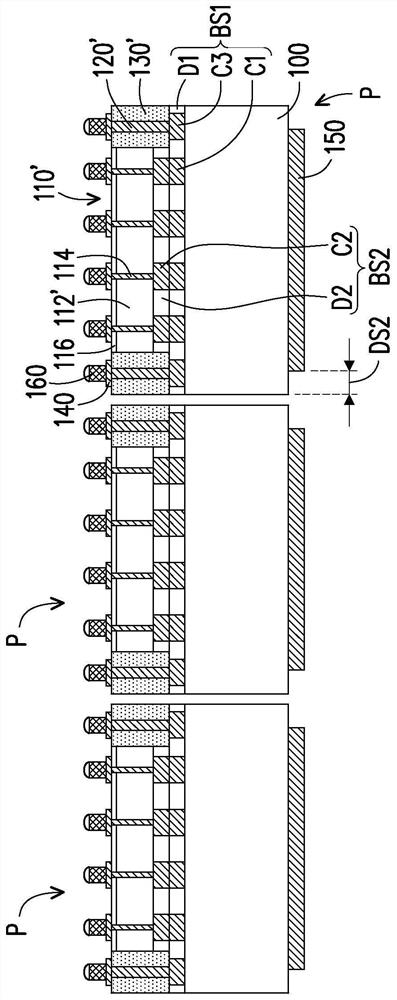

图1到图7是示意性示出根据本公开一些实施例的制作系统集成电路(system onintegrated circuit,SoIC)组件的工艺流程的剖视图。

图8到图11是示意性示出根据本公开一些其他实施例的制作封装结构的工艺流程的剖视图。

图12是示意性示出根据本公开一些其他实施例的封装结构的俯视图。

图13是示意性示出根据本公开一些替代实施例的沿着图12所示的截面线A-A’切割的封装结构的剖视图。

图14是示意性示出根据本公开一些替代实施例的沿着图12所示的截面线B-B’切割的封装结构的剖视图。

图15是示意性示出根据本公开一些其他实施例的衬底上晶片上芯片(Chip-on-Wafer-on-Substrate,CoWoS)结构的剖视图。

[符号的说明]

100:半导体管芯/第一半导体管芯

110:第二半导体管芯

110’:半导体管芯

112、112’:半导体衬底

114:半导体穿孔

116:介电层

120、120’:绝缘体穿孔

130:绝缘材料

130’:绝缘包封体

140:重布线路结构

150:翘曲控制图案

160:导电凸块

170:中介层

172:穿孔

174:凸块焊盘

176:导电端子

180:绝缘材料

182:绝缘包封体

182a:第一悬垂部分

190:存储器立方体

200:衬底

210:导电端子

A-A’、B-B’:截面线

BS1:第一接合结构

BS2:第二接合结构

C1:第一接合导体

C2:第二接合导体

C3:导体

D1:第一接合介电层

D2:第二接合介电层

DS1、DS2:侧向距离

OP:第二悬垂部分

P:半导体组件

P1、P2:封装结构

P3:CoWoS结构

SL1、SL2:切割道

UF1、UF2:底部填料

W1、W1’:半导体晶片

W2:中介层晶片

具体实施方式

以下公开内容提供用于实作所提供主题的不同特征的许多不同的实施例或实例。以下描述组件及设置形式的具体实例以简化本公开。当然,这些仅为实例且不旨在进行限制。举例来说,以下说明中将第一特征形成在第二特征“上方”或第二特征“上”可包括其中第一特征与第二特征被形成为直接接触的实施例,且也可包括其中第一特征与第二特征之间可形成有附加特征、进而使得所述第一特征与所述第二特征可能不直接接触的实施例。另外,本公开可能在各种实例中重复使用参考编号和/或字母。这种重复使用是出于简洁及清晰的目的,而不是自身表示所论述的各种实施例和/或配置之间的关系。

此外,为易于说明,本文中可能使用例如“之下(beneath)”、“下方(below)”、“下部的(lower)”、“之上(above)”、“上部的(upper)”等空间相对性用语来描述图中所示的一个元件或特征与另一(其他)元件或特征的关系。所述空间相对性用语旨在除图中所绘示的取向外还囊括装置在使用或操作中的不同取向。设备可具有其他取向(旋转90度或其他取向),且本文中所用的空间相对性描述语可同样相应地进行解释。

本公开也可包括其他特征及工艺。举例来说,可包括测试结构以帮助对三维(three-dimensional,3D)封装或三维集成电路(three-dimensional integratedcircuit,3DIC)装置进行验证测试。所述测试结构可例如包括在重布线层中或在衬底上形成的测试焊盘(test pad),以便能够对3D封装或3DIC进行测试、对探针和/或探针卡(probecard)进行使用等。可对中间结构以及最终结构执行验证测试。另外,可将本文中所公开的结构及方法与包括对已知良好管芯进行中间验证的测试方法结合使用,以提高良率并降低成本。

图1到图7是示意性示出根据本公开一些实施例的制作系统集成电路(SoIC)组件的工艺流程的剖视图。

参照图1,提供包括多个第一半导体管芯100的半导体晶片W1。第一半导体管芯100可以是逻辑管芯、系统芯片(System-on-Chip,SoC)管芯或其他合适的半导体管芯。半导体晶片W1可包括半导体衬底及设置在半导体衬底上的内连结构。半导体晶片W1的半导体衬底可包括晶体硅衬底(例如,晶片)。根据设计要求,半导体衬底可包括各种掺杂区(例如,p型衬底或n型衬底)。在一些实施例中,掺杂区可掺杂有p型或n型掺杂剂。掺杂区可掺杂有:p型掺杂剂,例如硼或BF

内连结构可包括堆叠的层间介电层(interlayered dielectric layer)及嵌入在堆叠的层间介电层中的内连配线(interconnect wiring),并且内连配线电连接到形成在半导体衬底中的半导体装置(例如,FinFET)。层间介电层的材料可包括氧化硅(SiO

半导体晶片W1还可包括形成在第一半导体管芯100上方的第一接合结构BS1。第一接合结构BS1可包括第一接合介电层D1及嵌入在第一接合介电层D1中的多个第一接合导体C1。第一接合介电层D1的材料可以是氧化硅(SiO

将多个第二半导体管芯110拾取并放置在半导体晶片W1上,使得第二半导体管芯110电连接到半导体晶片W1的第一半导体管芯100。在一些实施例中,第二半导体管芯110可以是存储器管芯,例如静态随机存取存储器(Static Random Access Memory,SRAM)管芯、存储器堆叠或其他合适的存储器管芯。第二半导体管芯110可各自包括半导体衬底112、设置在半导体衬底112上的内连结构、以及嵌入在半导体衬底112中的多个半导体穿孔(through semiconductor via,TSV)114。第二半导体管芯110的内连结构可包括堆叠的层间介电层及嵌入在堆叠的层间介电层中的内连配线,并且内连配线电连接到形成在半导体衬底112中的半导体装置(例如,FinFET)。层间介电层的材料可包括氧化硅(SiO

在一些实施例中,第二半导体管芯110通过第一接合结构BS1及第二接合结构BS2电连接到半导体晶片W1的第一半导体管芯100。第一接合结构BS1与第二接合结构BS2可彼此接合。当执行第二半导体管芯110与半导体晶片W1的接合工艺时,第二接合结构BS2的第二接合导体C2与第一接合结构BS1的第一接合导体C1对齐,并且可实现第二半导体管芯110与半导体晶片W1之间的亚微米对齐精度(sub-micron alignment precision)。一旦第二半导体管芯110与半导体晶片W1对齐,便可执行芯片到晶片(chip-to-wafer,CoW)的接合,使得半导体管芯110接合到半导体晶片W1。

在一些实施例中,为促进第二半导体管芯110与半导体晶片W1之间的芯片到晶片(CoW)的接合,执行第一接合结构BS1及第二接合结构BS2的接合表面的表面准备(surfacepreparation)。所述表面准备可包括例如表面清洁(cleaning)及活化(activation)。可对第一接合结构BS1及第二接合结构BS2的接合表面执行表面清洁,以移除第一接合导体C1、第一接合介电层D1、第二接合导体C2及第二接合介电层D2的接合表面上的多个颗粒。通过例如湿法清洁来清洁第一接合结构BS1及第二接合结构BS2的接合表面。不仅可移除颗粒,而且可移除在第一接合导体C1及第二接合导体C2的接合表面上形成的天然氧化物。在第一接合导体C1及第二接合导体C2的接合表面上形成的天然氧化物可通过在湿法清洁中使用的化学物质来移除。

在清洁第一接合结构BS1及第二接合结构BS2的接合表面之后,可执行第一接合介电层D1及第二接合介电层D2的顶表面的活化,以发展高接合强度。在一些实施例中,执行等离子体活化以处理第一接合介电层D1及第二接合介电层D2的接合表面。当第一接合介电层D1的经活化的接合表面与第二接合介电层D2的经活化的接合表面接触时,第二半导体管芯110的第二接合介电层D2与第一接合介电层D1被预接合(pre-bond)。在预接合第一接合介电层D1与第二接合介电层D2之后,第一接合导体C1与第二接合导体C2实体接触。

在预接合第一接合介电层D1与第二接合介电层D2之后,完成了第一接合结构BS1与第二接合结构BS2之间的混合接合(hybrid bonding)。第二半导体管芯110与半导体晶片W1的混合接合还可包括用于介电接合的处理及用于导体接合的热退火。执行用于介电接合的处理以加强第一接合介电层D1与第二接合介电层D2之间的接合。用于介电接合的处理可在介于约100摄氏度到约150摄氏度范围内的温度下执行。在执行用于介电接合的处理之后,执行用于导体接合的热退火(thermal annealing),以促进第一接合导体C1与第二接合导体C2之间的接合。用于导体接合的热退火可在介于约300摄氏度到约400摄氏度范围内的温度下执行。用于导体接合的热退火的工艺温度高于用于介电接合的处理的工艺温度。由于用于导体接合的热退火是在相对较高的温度下执行的,因此在第一接合导体C1与第二接合导体C2之间的接合界面(bonding interface)处可能发生金属扩散(metal diffusion)及晶粒生长(grain growth)。在执行用于导体接合的热退火之后,第一接合介电层D1被接合到第二接合介电层D2,且第一接合导体C1被接合到第二接合导体C2。第一接合导体C1与第二接合导体C2之间的导体接合可以是通孔到通孔(via-to-via)的接合、焊盘到焊盘(pad-to-pad)的接合或通孔到焊盘(via-to-pad)的接合。

可执行其他类型的接合工艺来接合第二半导体管芯110与半导体晶片W1中的第一半导体管芯100。

如图1所示,在半导体晶片W1上方形成多个绝缘体穿孔(through insulator via,TIV)120。绝缘体穿孔120电连接到第一接合结构BS1中的多个导体C3,并且导体C3没有被第二半导体管芯110覆盖。绝缘体穿孔120与第二半导体管芯110间隔开一定距离。在一些实施例中,绝缘体穿孔120的高度可大于第二半导体管芯110的厚度。在一些替代实施例中,绝缘体穿孔120的高度可小于或实质上等于第二半导体管芯110的厚度。

参照图2及图3,在半导体晶片W1上方形成绝缘材料130以覆盖第二半导体管芯110及绝缘体穿孔120。在一些实施例中,绝缘材料130通过包覆成型(over-molding)工艺或沉积工艺形成,使得第二半导体管芯110及绝缘体穿孔120被绝缘材料130完全覆盖。在执行包覆成型工艺或沉积工艺之后,可执行研磨工艺以减小绝缘材料130、第二半导体管芯110及绝缘体穿孔120的厚度,使得在半导体晶片W1上形成经厚度减小的多个半导体管芯110’、经高度减小的多个绝缘体穿孔120’及绝缘包封体130’。在执行研磨工艺之后,从半导体管芯110’的后表面露出半导体穿孔114。在一些实施例中,上述研磨工艺包括机械研磨工艺、化学机械抛光(chemical mechanical polishing,CMP)工艺或其组合。

在一些替代实施例中,可在形成绝缘包封体130’之后形成经高度减小的绝缘体穿孔120’。举例来说,通过激光钻孔工艺、光刻工艺、以及随后的刻蚀工艺或其他合适的图案化工艺来图案化绝缘包封体130’,使得在绝缘包封体130’中形成多个穿孔,并且在绝缘包封体130’中界定的穿孔中填充导电材料以形成绝缘体穿孔120’。在绝缘包封体130’中形成穿孔之后,可通过导电材料的沉积工艺及随后的CMP工艺来形成绝缘体穿孔120’。在半导体管芯110’及绝缘包封体130’上方沉积金属材料(例如,铜),以填充在绝缘包封体130’中界定的穿孔,且然后通过CMP工艺抛光金属材料,直到露出半导体管芯110’及绝缘包封体130’。

如图2及图3所示,在执行研磨工艺之后,可执行半导体衬底112的凹陷工艺,使得形成经厚度减小的多个半导体衬底112’,并且半导体穿孔114可从半导体衬底112’的后表面略微突出。在执行半导体衬底112的凹陷工艺之后,形成多个介电层116以覆盖半导体衬底112’的后表面。介电层116的顶表面可实质上与绝缘包封体130’的顶表面齐平。在一些实施例中,介电层116可通过介电材料的沉积工艺及随后的CMP工艺形成。介电材料(例如,氮化硅)可沉积在半导体衬底112’及绝缘包封体130’的后表面上方,以填充由上述凹陷工艺形成的多个凹陷,且然后通过CMP工艺抛光介电材料,直到露出绝缘包封体130’的顶表面。

可在半导体管芯110’及绝缘包封体130’上方形成重布线路结构140。重布线路结构140电连接到半导体晶片W1’的第一半导体管芯(又称“半导体管芯”)100及半导体管芯110’。如图3所示,重布线路结构140电连接到半导体管芯110’的半导体穿孔114及嵌入绝缘包封体130’中的绝缘体穿孔120’。在一些实施例中,重布线路结构140包括凸块焊盘(bumppad)及重布线配线(redistribution wiring),其中随后形成的导电凸块160(图6中所示)形成在重布线路结构140的凸块焊盘上。

如图3所示,半导体管芯110’各自包括半导体衬底112’、半导体穿孔114及介电层116,半导体管芯110’的厚度实质上等于绝缘包封体130’的厚度,并且半导体管芯110’被绝缘包封体130’侧向包封。换句话说,绝缘包封体130’与半导体管芯110’的侧表面接触,并且半导体管芯110’的后表面(即,介电层116)被绝缘包封体130’以可接触的方式露出。在图3中未示出的一些替代实施例中,由于研磨工艺的研磨选择性,半导体管芯的厚度略小于或大于绝缘包封体的厚度。换句话说,绝缘包封体的顶表面可略高于或略低于半导体管芯的后表面。

参照图3及图4,可对半导体晶片W1执行薄化工艺,使得半导体晶片W1的厚度减小,并且形成经薄化的半导体晶片W1’。在一些实施例中,将图3所示的所得结构上下翻转,并且执行研磨工艺以使半导体晶片W1变薄。上述用于薄化半导体晶片W1的研磨工艺可包括机械研磨工艺、化学机械抛光(CMP)工艺或其组合。在执行半导体晶片W1的薄化工艺之前,图3所示的半导体晶片W1可具有约750微米或大于750微米的厚度。在执行半导体晶片W1的薄化工艺之后,图4中所示的经薄化的半导体晶片W1’可具有介于约700微米到约1550微米范围内的厚度。

参照图5,在半导体晶片W1’的后表面上形成多个翘曲控制图案150。翘曲控制图案150可以是电浮动的。在一些实施例中,翘曲控制图案150通过导电材料的沉积工艺及随后的图案化工艺形成。可通过镀覆工艺在半导体晶片W1’的后表面上形成导电材料(例如,铜),并且可通过光刻及刻蚀工艺使形成在半导体晶片W1’的后表面上的经镀覆的导电材料图案化。翘曲控制图案150的厚度可介于约5微米到约15微米的范围内,以适当地最小化半导体晶片W1’的翘曲。翘曲控制图案150可包括彼此间隔开侧向距离DS1的矩形图案。在一些实施例中,翘曲控制图案150尽可能多地覆盖半导体晶片W1’的后表面。翘曲控制图案150的面积(即,被翘曲控制图案150覆盖或占据的面积)可以是A1,半导体晶片W1’的后表面的面积可以是A2,并且A1对A2的比率可介于约70%到约99.9%的范围内。两个相邻翘曲控制图案150之间的侧向距离DS1可介于约120微米到约3000微米的范围内。形成在半导体晶片W1’的后表面上的翘曲控制图案150可抵消内连配线(例如,铜配线、铜焊盘、铝焊盘或其组合)的热膨胀,使得半导体晶片W1’的翘曲可被控制及最小化。

参照图5及图6,在形成翘曲控制图案150之后,将图5所示的所得结构上下翻转,并且执行晶片级凸块工艺(wafer level bumping process)以在重布线路结构140上形成多个导电凸块160。导电凸块160可以是微凸块,并且每个微凸块可包括落在重布线路结构140上的铜柱及覆盖铜柱的焊料。在一些实施例中,通过溅射工艺在半导体管芯110’及绝缘包封体130’的后表面上形成晶种层;通过光刻工艺在晶种层上形成图案化的光刻胶层以覆盖半导体管芯110’及绝缘包封体130’的后表面,使得位于重布线路结构140的凸块焊盘上方的晶种层的一些部分被图案化的光刻胶层暴露出;执行镀覆工艺,使得导电凸块160形成在重布线路结构140的凸块焊盘上;且使用导电凸块160作为刻蚀掩模通过刻蚀工艺移除晶种层的一些部分。

在一些实施例中,如图6所示,在形成翘曲控制图案150之后,在重布线路结构140上形成导电凸块160。在一些替代实施例中,在半导体晶片W1的薄化工艺(图4中所示)之前,在重布线路结构140上形成导电凸块160。换句话说,可在形成翘曲控制图案150之前在重布线路结构140上形成导电凸块160。

如图6所示,在形成翘曲控制图案150及导电凸块160之后,获得包括半导体晶片W1’、半导体管芯110’、绝缘体穿孔120’、绝缘包封体130’、重布线路结构140、翘曲控制图案150及导电凸块160的重构晶片。

参照图6及图7,沿着切割道SL1执行用于单体化重构晶片的晶片锯切工艺,从而获得经单体化的多个半导体组件P(例如,经单体化的多个SoIC组件)。在一些实施例中,通过刀片将图6所示的重构晶片单体化以形成经单体化的半导体组件P,并且当执行晶片锯切工艺时,翘曲控制图案150不与刀片接触。举例而言,切割道SL1的宽度可介于约60微米到约1000微米的范围内。如上所述,在两个相邻翘曲控制图案150之间的侧向距离DS1介于约120微米到约3000微米的范围内的实施例中,翘曲控制图案150可与在重构晶片的晶片锯切工艺中使用的刀片保持安全距离。因此,在重构晶片的晶片锯切工艺中使用的刀片的寿命可增加。

每个半导体组件P可包括至少一个半导体管芯100、至少一个半导体管芯110’、多个绝缘体穿孔120’、绝缘包封体130’、重布线路结构140、至少一个翘曲控制图案150及多个导电凸块160。半导体管芯100可包括有源表面及与有源表面相对的后表面。半导体管芯110’可设置在半导体管芯100的有源表面上。绝缘体穿孔120’穿过绝缘包封体130’,其中绝缘体穿孔120’电连接到半导体管芯100及重布线路结构140。绝缘包封体130’可设置在半导体管芯100的有源表面上,并且侧向包封半导体管芯110’。翘曲控制图案150可设置在半导体管芯100的后表面上并部分覆盖所述后表面。重布线路结构140可设置在半导体管芯110’及绝缘包封体130’上,其中重布线路结构140电连接到半导体管芯100及半导体管芯110’。多个导电凸块160可设置在重布线路结构140上并电连接到重布线路结构140。

在一些实施例中,在经单体化的半导体组件P中,翘曲控制图案150的侧壁与半导体管芯100的侧壁分开侧向距离DS2。侧向距离DS2可介于约30微米到约1000微米的范围内,并且翘曲控制图案150的厚度可介于约5微米到约15微米的范围内。由于翘曲控制图案150抵消内连配线的热膨胀,因此通过翘曲控制图案150可很好地控制及最小化经单体化的半导体组件P的翘曲。

图8到图11是示意性示出根据本公开一些其他实施例的制作封装结构的工艺流程的剖视图。

参照图8,提供包括多个中介层(interposer)170的中介层晶片W2。中介层晶片W2的每个中介层170可包括多个穿孔172及电连接到穿孔172的多个凸块焊盘174。中介层晶片W2可以是硅中介层晶片或其他合适的半导体中介层晶片。将经单体化的半导体组件P拾取并放置在中介层晶片W2上方,并且可执行芯片到晶片(CoW)的接合工艺以将经单体化的半导体组件P与中介层晶片W2接合。在一些实施例中,将经单体化的半导体组件P在中介层晶片W2上翻转,使得经单体化的半导体组件P的导电凸块160可通过回焊(reflow)工艺与中介层晶片W2的凸块焊盘174接合。

在将经单体化的半导体组件P接合到中介层晶片W2之后,可在经单体化的半导体组件P与中介层晶片W2之间形成底部填料(underfill)UF1,使得经单体化的半导体组件P的导电凸块160被底部填料UF1侧向包封。底部填料UF1可通过分配工艺及随后的固化工艺形成在中介层晶片W2上方。在一些实施例中,底部填料UF1的材料包括二氧化硅(SiO

参照图9,在中介层晶片W2的顶表面上方形成绝缘材料180,以包封经单体化的半导体组件P及底部填料UF1。在一些实施例中,通过包覆成型工艺或沉积工艺形成绝缘材料180,使得经单体化的半导体组件P被绝缘材料180完全覆盖。绝缘材料180可覆盖翘曲控制图案150的顶表面及侧壁。在形成绝缘材料180之后,可在中介层晶片W2的底表面上形成多个导电端子176。在一些实施例中,导电端子176包括受控塌陷芯片连接凸块(ControlledCollapse Chip Connection bump,C4凸块)。在一些替代实施例中,导电端子176包括通过球安装工艺(ball mount process)及随后的回焊工艺形成的焊球。

参照图9及图10,在形成绝缘材料180之后,可执行研磨工艺以部分移除绝缘材料180从而形成绝缘包封体182,其中绝缘包封体182侧向包封经单体化的半导体组件P。在一些实施例中,在执行包覆成型工艺或沉积工艺之后,执行单步或多步研磨工艺以减小绝缘材料180的厚度,直到露出翘曲控制图案150的顶表面。在执行研磨工艺之后,翘曲控制图案150的顶表面从绝缘包封体182的顶表面露出,并且翘曲控制图案150的顶表面可实质上与绝缘包封体182的顶表面齐平。在一些替代实施例中,由于研磨工艺的研磨选择性,翘曲控制图案150的顶表面可略高于或低于绝缘包封体182的顶表面。绝缘包封体182覆盖翘曲控制图案150的侧壁。在一些实施例中,上述用于部分移除绝缘材料180的研磨工艺包括机械研磨工艺、化学机械抛光(CMP)工艺或其组合。

在形成绝缘包封体182及导电端子176之后,获得包括中介层晶片W2、经单体化的半导体组件P、绝缘包封体182及导电端子176的重构晶片。

参照图10及图11,沿着切割道SL2执行用于单体化图10所示的重构晶片的晶片锯切工艺,从而获得经单体化的多个封装结构P1。在一些实施例中,通过刀片将图10所示的重构晶片单体化,以形成经单体化的封装结构P1。经单体化的封装结构P1可包括中介层170、半导体组件P、绝缘包封体182及底部填料UF1。半导体组件P设置在中介层170上并电连接到中介层170。半导体组件P包括半导体管芯100、半导体管芯110’、绝缘包封体130’及翘曲控制图案150。半导体管芯100包括有源表面及与有源表面相对的后表面。半导体管芯110’与半导体管芯100的有源表面接合。绝缘包封体130’设置在半导体管芯100的有源表面上,并侧向包封半导体管芯110’,其中绝缘包封体130’的侧壁实质上与半导体管芯100的侧壁对齐。翘曲控制图案150设置在半导体管芯100的后表面上并部分覆盖所述后表面。绝缘包封体182设置在中介层170上并侧向包封半导体组件P。底部填料UF1设置在半导体组件P与中介层170之间。

半导体组件P还可包括设置在半导体管芯110’及绝缘包封体130’上的重布线路结构140,其中重布线路结构140电连接到半导体管芯100及半导体管芯110’。半导体组件P还可包括设置在重布线路结构140上并电连接到重布线路结构140的导电凸块160。翘曲控制图案150的侧壁可与半导体管芯100的侧壁分开侧向距离DS2,并且侧向距离DS2可介于约30微米到约1000微米的范围内。在一些实施例中,半导体管芯100的后表面的一部分被绝缘包封体182覆盖,并且绝缘包封体182与翘曲控制图案150的侧壁接触。绝缘包封体182可包括在半导体管芯100的后表面的一些部分上方延伸的第一悬垂部分182a,并且第一悬垂部分182a与翘曲控制图案150的侧壁接触。此外,第一悬垂部分182a的厚度可实质上等于翘曲控制图案150的厚度。在一些替代实施例中,由于绝缘包封体182的研磨工艺的研磨选择性,第一悬垂部分182a的厚度略高于或低于翘曲控制图案150的厚度。

图12是示意性示出根据本公开一些其他实施例的封装结构的俯视图。图13是示意性示出根据本公开一些替代实施例的沿着图12所示的截面线A-A’切割的封装结构的剖视图。图14是示意性示出根据本公开一些替代实施例的沿着图12所示的截面线B-B’切割的封装结构的剖视图。

参照图11到图14,经单体化的封装结构P2类似于经单体化的封装结构P1,除了经单体化的封装结构P2还包括设置在中介层170上并电连接到中介层170的多个存储器立方体(memory cube)190,其中底部填料UF1填充中介层170与半导体组件P之间的间距以及半导体组件P与存储器立方体190之间的多个间隙。在一些实施例中,如图13所示,底部填料UF1包括在半导体管芯110的后表面的一部分上方的多个第二悬垂部分OP,并且第二悬垂部分OP与翘曲控制图案150接触。此外,第一悬垂部分182a及第二悬垂部分OP的厚度可实质上等于翘曲控制图案150的厚度。在一些替代实施例中,由于研磨工艺的研磨选择性,第一悬垂部分182a及第二悬垂部分OP的厚度略高于或低于翘曲控制图案150的厚度。

绝缘包封体182的第一悬垂部分182a与底部填料UF1的第二悬垂部分OP接触,并且在第一悬垂部分182a与第二悬垂部分OP之间形成界面。在一些实施例中,第一悬垂部分182a的宽度可大于第二悬垂部分OP的宽度。在一些替代实施例中,第一悬垂部分182a的宽度可实质上等于或小于第二悬垂部分OP的宽度。

图15是示意性示出根据本公开一些其他实施例的衬底上晶片上芯片(CoWoS)结构的剖视图。

参照图15,提供包括经单体化的封装结构P2、衬底200及底部填料UF2的CoWoS结构P3。经单体化的封装结构P2的中介层170设置在衬底200上,中介层170通过导电端子176电连接到衬底200。此外,CoWoS结构P3可包括多个导电端子210。在一些实施例中,导电端子210包括通过球安装工艺及随后的回焊工艺形成的焊球。由于可很好地控制经单体化的封装结构P2的翘曲,因此可确保CoWoS结构P3的可靠性。

根据本公开的一些实施例,提供一种包括第一半导体管芯、第二半导体管芯、绝缘包封体及翘曲控制图案的结构。所述第一半导体管芯包括有源表面及与所述有源表面相对的后表面。所述第二半导体管芯设置在所述第一半导体管芯的所述有源表面上。所述绝缘包封体设置在所述第一半导体管芯的所述有源表面上并侧向包封所述第二半导体管芯。所述翘曲控制图案设置在所述第一半导体管芯的所述后表面上并部分覆盖所述后表面。在一些实施例中,所述结构还包括:重布线路结构,设置在所述第二半导体管芯及所述绝缘包封体上,其中所述重布线路结构电连接到所述第一半导体管芯及所述第二半导体管芯。在一些实施例中,所述结构还包括:多个导电端子,设置在所述重布线路结构上并电连接到所述重布线路结构。在一些实施例中,所述结构还包括:多个半导体穿孔,穿过所述第二半导体管芯,其中所述多个半导体穿孔电连接到所述重布线路结构。在一些实施例中,所述结构还包括:多个绝缘体穿孔,穿过所述绝缘包封体,其中所述多个绝缘体穿孔电连接到所述第一半导体管芯及所述重布线路结构。在一些实施例中,在所述结构中,所述翘曲控制图案的侧壁与所述第一半导体管芯的侧壁分开一个距离,所述距离介于约30微米到约1000微米的范围内,并且所述翘曲控制图案的厚度介于约5微米到约15微米的范围内。

根据本公开的一些其他实施例,提供一种包括中介层、半导体装置、第二绝缘包封体及底部填料的结构。所述半导体装置设置在所述中介层上并电连接到所述中介层。所述半导体装置包括第一半导体管芯、第二半导体管芯、第一绝缘包封体及翘曲控制图案。所述第一半导体管芯包括有源表面及与所述有源表面相对的后表面。所述第二半导体管芯与所述第一半导体管芯的所述有源表面接合。所述第一绝缘包封体设置在所述第一半导体管芯的所述有源表面上并侧向包封所述第二半导体管芯,其中所述第一绝缘包封体的多个侧壁实质上与所述第一半导体管芯的多个侧壁对齐。所述翘曲控制图案设置在所述第一半导体管芯的所述后表面上并部分覆盖所述后表面。所述第二绝缘包封体设置在所述中介层上并侧向包封所述半导体装置。所述底部填料设置在所述半导体装置与所述中介层之间。在一些实施例中,所述半导体装置还包括:重布线路结构,设置在所述第二半导体管芯及所述第一绝缘包封体上,其中所述重布线路结构电连接到所述第一半导体管芯及所述第二半导体管芯。在一些实施例中,所述半导体装置还包括:多个导电端子,设置在所述重布线路结构上并电连接到所述重布线路结构。在一些实施例中,在所述结构的所述半导体装置中,所述翘曲控制图案的侧壁与所述第一半导体管芯的侧壁分开一定距离,并且所述距离介于约30微米到约1000微米的范围内。在一些实施例中,在所述结构中,所述第一半导体管芯的所述后表面的一部分被所述第二绝缘包封体覆盖,并且所述第二绝缘包封体与所述翘曲控制图案的侧壁接触。在一些实施例中,在所述结构中,所述第二绝缘包封体包括在所述第一半导体管芯的所述后表面的所述部分上方延伸的第一悬垂部分,并且所述第一悬垂部分与所述翘曲控制图案的所述侧壁接触。在一些实施例中,所述结构还包括:多个存储器立方体,设置在所述中介层上并电连接到所述中介层,其中所述底部填料填充所述中介层与所述半导体装置之间的间距以及所述半导体装置与所述多个存储器立方体之间的多个间隙。在一些实施例中,在所述结构中,所述底部填料包括位于所述第一半导体管芯的所述后表面的一部分上方的第二悬垂部分,并且所述第二悬垂部分与所述翘曲控制图案接触。在一些实施例中,所述结构还包括衬底,其中所述中介层电连接到所述衬底并设置在所述衬底与所述半导体装置之间。

根据本公开的一些其他实施例,提供一种方法。提供包括多个第一半导体管芯的半导体晶片。将多个第二半导体管芯设置在所述半导体晶片上,使得所述多个第二半导体管芯电连接到所述半导体晶片的所述多个第一半导体管芯。由形成在所述半导体晶片上的第一绝缘包封体侧向包封所述多个第二半导体管芯。在所述半导体晶片的后表面上形成多个翘曲控制图案。将所述半导体晶片单体化以形成多个半导体装置,所述多个半导体装置中的每一者包括所述多个第一半导体管芯中的至少一个第一半导体管芯、所述多个第二半导体管芯中的至少一个第二半导体管芯、以及所述多个翘曲控制图案中的至少一个翘曲控制图案。在一些实施例中,在所述方法中,通过刀片将所述半导体晶片单体化以形成所述多个半导体装置,并且在将所述半导体晶片单体化时,所述多个翘曲控制图案不与所述刀片接触。在一些实施例中,所述方法还包括:将所述多个半导体装置安装在中介层晶片上方;以及用第二绝缘包封体侧向包封所述多个半导体装置,其中所述第二绝缘包封体包括多个第一悬垂部分,所述多个第一悬垂部分中的每一者在所述多个第一半导体管芯的一个的所述后表面的一部分上方延伸,并且所述多个第一悬垂部分与所述多个翘曲控制图案的多个侧壁接触。在一些实施例中,所述方法还包括:在用所述第二绝缘包封体侧向包封所述多个半导体装置之前,在所述多个半导体装置与所述中介层晶片之间形成多个底部填料。在一些实施例中,在所述方法中,形成所述第二绝缘包封体包括:在所述中介层晶片上方形成绝缘材料以覆盖所述多个半导体装置;以及部分移除所述绝缘材料以形成所述第二绝缘包封体并露出所述多个翘曲控制图案。

以上概述了若干实施例的特征,以使所属领域中的技术人员可更好地理解本公开的各个方面。所属领域中的技术人员应理解,其可容易地使用本公开作为设计或修改其他工艺及结构的基础来施行与本文中所介绍的实施例相同的目的和/或实现与本文中所介绍的实施例相同的优点。所属领域中的技术人员还应认识到,这些等效构造并不背离本公开的精神及范围,而且他们可在不背离本公开的精神及范围的条件下对其作出各种改变、代替及变更。

- 固态摄像装置及其制作方法、摄像设备、半导体装置及其制作方法以及半导体衬底

- 半导体元件用外延基板、半导体元件、半导体元件用外延基板的制作方法、以及半导体元件的制作方法