芯片贴装装置以及半导体器件的制造方法

文献发布时间:2023-06-19 09:47:53

技术领域

本公开涉及芯片贴装装置,例如能够应用于扇出型面板级封装用的裸芯片放置。

背景技术

在电子部件安装的领域中,有如下的工序,即,在通过以封固树脂将在层叠于临时基板和在临时基板上的粘接层上配置的多个半导体芯片一并封固而形成了具有多个半导体芯片和覆盖多个半导体芯片的封固树脂的封固体之后,从封固体剥离包含粘接层在内的临时基板,接着在贴附有封固体的粘接层的面上形成再布线层。在该情况下,再布线层与半导体芯片的接合精度依赖临时基板上的芯片的定位精度。于是,需要在向临时基板上安装半导体芯片时的定位精度。

现有技术文献

专用文献1:JP特开2014-45013号公报

专用文献2:JP特开2018-133353号公报

通过对临时基板附加贴装目标位置的定位修正用标记,使用该标记位置对贴装定位位置进行修正,能够提高在临时固定时的半导体芯片相对于临时基板的定位精度。然而,将标记附加到临时基板上的哪个位置根据半导体芯片的构造或尺寸、最终的半导体芯片与封固体的配置关系来决定。即,需要准备具有基于最终产品的构造或尺寸、部件配置的规定的标记的临时基板。因此,由于必须针对每个产品制作多个具有规定的标记的临时基板,所以存在成本上升这样的问题。

发明内容

本公开的课题在于,提供一种在没有被附加标记的临时基板上以高定位精度将半导体芯片(裸芯片)安装于临时基板的芯片贴装装置。

若简单说明本公开中代表性的概要则如下所示。

即,芯片贴装装置构成为具备:将所拾取的裸芯片载置于具有多个区域的基板的上表面的贴装头;使所述贴装头移动的驱动部;拍摄所述裸芯片的摄像装置;以及控制所述驱动部和所述摄像装置的控制装置。所述控制装置向所述基板贴装第一裸芯片以及第二裸芯片,以所述第一裸芯片以及所述第二裸芯片为基准贴装第三裸芯片,以所述第一裸芯片或者所述第二裸芯片、以及所述第三裸芯片为基准贴装裸芯片。

发明效果

根据上述芯片贴装装置,能够提高裸芯片放置的精度。

附图说明

图1是示出芯片贴装装置的概要的图。

图2是示出比较例中的贴装有基板基准裸芯片的基板的俯视图。

图3是示出以图2的基板基准裸芯片为基准位置贴装有多个裸芯片的基板的俯视图。

图4是示出实施方式中的贴装方法的流程图。

图5是示出实施方式中的贴装有基准裸芯片的基板的俯视图。

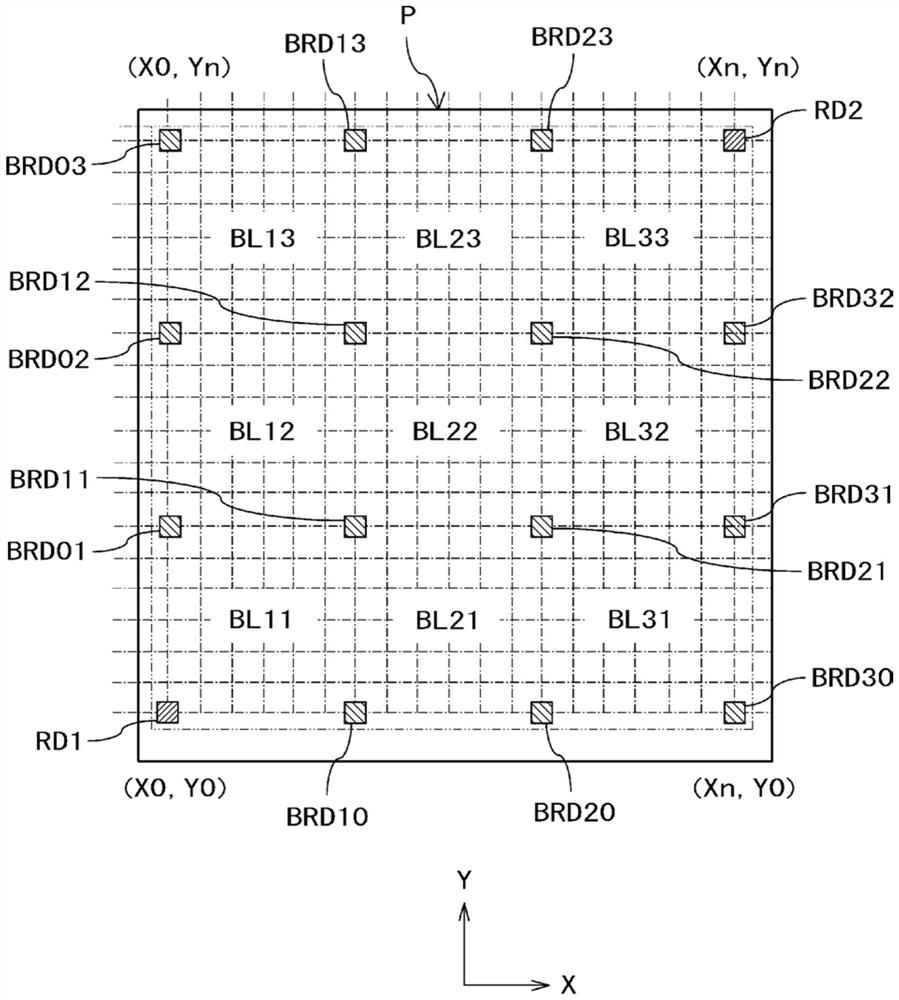

图6是示出以图5的基板基准裸芯片为基准位置贴装有块基准裸芯片的基板的俯视图。

图7是示出以图6的基板基准裸芯片以及块基准裸芯片为基准位置贴装有裸芯片的基板的俯视图。

图8是示出贴装有最初的块内的所有裸芯片的基板的俯视图。

图9是说明第一变形例中的贴装方法的图。

图10是说明第二变形例中的贴装方法的图。

图11是示出第四变形例中的贴装有基板基准裸芯片以及块基准裸芯片的基板的俯视图。

图12是示出第五变形例中的以基板基准裸芯片以及块基准裸芯片为基准位置贴装有裸芯片的基板的俯视图。

图13是示出实施例中的倒装芯片贴装机的概略的俯视图。

图14是说明在图13中从箭头A方向观察时拾取倒装头、转移头以及贴装头的动作的图。

图15是示出图13的裸芯片供给部的主要部分的概略剖视图。

图16是示出利用图13的倒装芯片贴装机实施的贴装方法的流程图。

图17是示出第六变形例中的以基板基准裸芯片以及块基准裸芯片为基准位置贴装有裸芯片的基板的俯视图。

其中附图标记说明如下:

BH:贴装头

BD:芯片贴装装置

CM:摄像装置

CNT:控制装置

MM:存储装置

D:裸芯片

RD1:基板基准裸芯片(第一裸芯片)

RD2:基板基准裸芯片(第二裸芯片)

BRD:块基准裸芯片(第三裸芯片)

P:基板

10:倒装芯片贴装机(芯片贴装装置)

41:贴装头

43:Y横梁(驱动部)

44:基板识别摄像头(摄像装置)

7:控制装置

具体实施方式

以下,利用附图对比较例、实施方式、变形例以及实施例进行说明。在此,在以下的说明中,有时对同一构成要素标注同一附图标记,省略重复的说明。此外,为了使说明更明确,与实际的形态相比,有时示意性地示出附图中的各部分的宽度、厚度、形状等,但只不过为一例,不限定对本发明的解释。

扇出型晶片级封装(Fan Out Wafer Level Package:FOWLP)为在超过芯片面积的宽区域形成再布线层的封装。扇出型面板级封装(Fan Out Panel Level Package:FOPLP)是将FOWLP的一并制造的思考方法进一步突破而得到的封装。FOWLP通过在直径为300mm的晶片载置多个硅裸芯片且一并实施封装的制造,减少每一个封装的制造成本。将这种一并制造的思考方法应用于比晶片更大的面板(面板状的基板)为FOPLP。面板使用印刷基板或者玻璃基板(例如液晶面板制造用基板等)。

FOPLP的制造工艺存在很多种类,其中之一的方法为,将从晶片拾取的裸芯片借助在基板上涂敷的粘接性的主剂而贴装在作为临时基板的面板(以下,称为基板)上并进行临时固定,再利用封固树脂一并封固,从基板将该封固体剥离并进行再布线或焊盘(PAD)的形成。在该方法中,为了维持成品率、品质,而需要高精度地在基板上安装裸芯片,因裸芯片的小型化、高密度布线化而要求3~5μm等的高精度。

面向制造装置的高精度化,考虑有在基板上事先配置成为定位的基准的标记等并进行对准的方法,但对基板进行加工而形成目标标记的情况下,在制造的部件尺寸变更的情况等下,基板(作为模具)的再使用很困难,在此基础上,在基板上以3~5μm以内的精度形成对准标记需要花费成本,基板的成本的上升关联封装价格的上升。因此,需要在无标记的无图案的基板上高精度地安装裸芯片,制造装置会变成高价。为了减少FOPLP的成本而需要实现能够以高精度且低价安装的制造装置。

于是,发明人研究了在基板贴装裸芯片,并以该裸芯片作为定位基准的技术(比较例)。使用图1~3对此进行说明。图1是示出芯片贴装装置的概要的图。图2是示出比较例中的贴装有基板基准裸芯片的基板的俯视图。图3是示出图2的以基板基准裸芯片作为基准位置而贴装有多个裸芯片的基板的俯视图。

如图1所示,芯片贴装装置BD具有在基板P贴装裸芯片D的贴装头BH、拍摄裸芯片D或基板P的摄像装置CM、和控制贴装头BH以及摄像装置CM的控制装置CNT。

如图2所示,首先,在基板P上定义成为整体的基准的两点,控制装置CNT利用贴装头BH以芯片贴装装置BD的精度在该位置贴装基板基准裸芯片RD1、RD2。在此,基板P在俯视下为矩形状,一边沿X轴方向延伸,与一边相交的另一边沿Y轴方向延伸。搭载有用双点划线的四条直线示出的裸芯片D的区域DR为比基板P小的矩形区域。例如在本比较例中,基板基准裸芯片RD1贴装在区域DR的左下端,基板基准裸芯片RD2贴装在右上端。基板基准裸芯片RD1、RD2可以分别为左上、右下等。在区域DR内的沿X轴方向以及Y轴方向延伸的点划线的直线的交点贴装有裸芯片D。此外,基板基准裸芯片RD1、RD2与裸芯片D同样地,为产品裸芯片。

在贴装后,控制装置CNT利用摄像装置CM拍摄基板基准裸芯片RD1、RD2,识别(测量)基板基准裸芯片RD1、RD2的位置,并将该位置以及距离保存至存储装置MM。

接着,控制装置CNT从晶片拾取由贴装头BH贴装的裸芯片D,利用摄像装置CM识别基板基准裸芯片RD1、RD2的位置,计算出基板基准裸芯片RD1、RD2的位置以及从贴装时起的位置变化量。根据算出结果,以RD1、RD2作为基准,基于位置以及距离的变化量计算贴装的位置、间距、斜率,对贴装裸芯片D的位置进行修正计算。然后,以修正计算结果为基础,如图3所示,依次贴装裸芯片D。在此,FOPLP的尺寸很大(例如、515mm×510mm等),需要在没有设有定位基准的基板上以3~5μm等的高精度、且大量地贴装裸芯片。但是,因环境的温度变化或工艺所需要的基板温度的变化、装置的经时变化等的影响,在贴装过程中基板的伸缩等有时会发生变化,影响贴装后的精度。例如,如图3所示,若从右上的基板基准裸芯片RD2的下方进行基于基板基准裸芯片RD1、RD2的两点基准的贴装,则产生因在贴装过程中的经时变化引起的贴装偏移PA。该贴装偏移PA包括因与基板基准裸芯片RD2相距的距离变远而受影响的误差以及因从基准测定经过了时间而使基板的伸缩等发生变化从而引起的误差等。

<实施方式>

利用图1、4~8说明减少上述贴装偏移的实施方式。图4是示出实施方式中的贴装方法的流程图。图5是示出实施方式中的贴装有基板基准裸芯片的基板的俯视图。图6是示出以图5的基板基准裸芯片为基准位置贴装有块基准裸芯片的基板的俯视图。图7是示出以图6的基板基准裸芯片以及块基准裸芯片为基准位置贴装有裸芯片的基板的俯视图。图8是示出贴装有最初的块内的所有裸芯片的基板的俯视图。

例如,就FOPLP而言,将配置在基板P上的裸芯片D分成作为一组的区域的块来实施用于再布线形成的图案曝光,因此,精度只要在该块内获得贴装间距精度即可。于是,实施方式的控制装置CNT对基板P贴装作为第一裸芯片的基板基准裸芯片RD1以及作为第二裸芯片的基板基准裸芯片RD2,将基板基准裸芯片RD1以及基板基准裸芯片RD2作为基准而贴装作为第三裸芯片的块基准裸芯片BRD,以基板基准裸芯片RD1或者基板基准裸芯片RD2、以及块基准裸芯片BRD为基准贴装裸芯片。

更具体来说,通过以图4示出的这种顺序贴装裸芯片D,能够应对贴装精度、基板经时变化以及热膨胀修正。

(步骤S1:基板基准裸芯片的贴装)

如图5所示,首先,控制装置CNT与比较例同样地,对基板P定义成为整体的基准的两点,在该位置通过贴装头BH贴装作为第一裸芯片的基板基准裸芯片RD1以及作为第二裸芯片的基板基准裸芯片RD2。在此,优选将基板基准裸芯片RD1和基板基准裸芯片RD2尽可能分离,例如,贴装在基板P上的区域DR的对角中的右上端和左下端。在此,基板P在俯视下,由第一边SD1、与该第一边SD1交叉的第二边SD2、与该第二边SD2交叉且与所述第一边SD1相对置的第三边SD3、与该第三边SD3交叉且与所述第二边SD2相对置的第四边SD4构成为矩形状。第一边SD1以及第三边SD3沿Y轴方向延伸,第二边SD2以及第四边SD4沿X轴方向延伸。

更具体来说,控制装置CNT将基板基准裸芯片RD1贴装于区域DR的左下端((X0、Y0)),将基板基准裸芯片RD2贴装于右上端((Xn、Yn))。控制装置CNT在区域DR内的沿X轴方向以及Y轴方向延伸的点划线的直线的交点贴装裸芯片D。即,控制装置CNT在后述的多个块BL中的、与由第一边SD1和第二边SD2构成的第一角部C1最近的作为第一区域的块贴装基板基准裸芯片RD1,在与由第三边SD3和第四边SD4构成的第二角部C2最近的作为第二区域的块贴装基板基准裸芯片RD2。在此,块BL为后述的多个块的总称。

在贴装后,控制装置CNT利用摄像装置CM拍摄基板基准裸芯片RD1、RD2,对该位置进行识别(测量),将左下的基板基准裸芯片RD1的位置(X0、Y0)以及右上的基板基准裸芯片RD2的位置(Xn、Yn)、以及这些位置之间的距离保存至存储装置MM。此外,基板基准裸芯片RD1、RD2与裸芯片D同样为产品裸芯片。

(步骤S2:块基准裸芯片的贴装)

接着,如图6所示,控制装置CNT通过贴装头BH将在步骤S1中贴装了成为上述的各块的基准的块基准裸芯片BRD后的基板基准裸芯片RD1、RD2贴装于基准。在此,块基准裸芯片BRD为后述的多个块基准裸芯片的总称。此时,控制装置CNT也利用摄像装置CM拍摄贴装的各块基准裸芯片BRD的位置,以在步骤S1中贴装的基板基准裸芯片RD1、RD2为基准识别位置并测量距离,将各块基准裸芯片BRD的位置(距离)保存至存储装置MM。此外,块基准裸芯片BRD与裸芯片D同样为产品裸芯片。在此,基板P的区域DR被划分成9个块BL,贴装了14个块基准裸芯片BRD。各块BL为矩形状的区域,为相同大小(面积)。

更具体来说,在从基板基准裸芯片RD1通过并沿X轴方向延伸的点划线与从基板基准裸芯片RD2通过并沿Y轴方向延伸的点划线的交点(Xn、Y0)贴装有块基准裸芯片BRD30。另外,在从基板基准裸芯片RD1通过并沿Y轴方向延伸的点划线与从基板基准裸芯片RD2通过并沿X轴方向延伸的点划线的交点(X0、Yn)贴装有块基准裸芯片BRD03。另外,在基板基准裸芯片RD1与块基准裸芯片BRD30之间以等间隔贴装有块基准裸芯片BRD10、BRD20。另外,在基板基准裸芯片RD1与块基准裸芯片BRD03之间以等间隔贴装有块基准裸芯片BRD01、BRD02。另外,在块基准裸芯片BRD30与基板基准裸芯片RD2之间以等间隔贴装有块基准裸芯片BRD31、BRD32。另外,在块基准裸芯片BRD03与基板基准裸芯片RD2之间以等间隔贴装有块基准裸芯片BRD13、BRD23。另外,在块基准裸芯片BRD10与块基准裸芯片BRD13之间以等间隔贴装有块基准裸芯片BRD11、BRD12。另外,在块基准裸芯片BRD20与块基准裸芯片BRD23之间以等间隔贴装有块基准裸芯片BRD21、BRD22。

(步骤S3:裸芯片的贴装)

接着,如图7所示,控制装置CNT以在步骤S1中贴装的基板基准裸芯片RD1、RD2的某一个和在步骤S2中贴装的各块基准裸芯片BRD为基准位置,通过贴装头BH贴装各块内的裸芯片D(步骤S3)。

更具体来说,在贴装各裸芯片D前,控制装置CNT利用摄像装置CM拍摄块基准裸芯片BRD以及基板基准裸芯片RD1或者基板基准裸芯片RD2,识别块基准裸芯片BRD的位置、和远离该位置一方的基板基准裸芯片的位置,测量距离(步骤S31)。控制装置CNT计算与在步骤S2中进行测量时的块基准裸芯片BRD的位置以及距离之差,计算基板P的伸缩量并修正贴装位置(步骤S32)。控制装置CNT通过贴装头BH将裸芯片D贴装在修正后的贴装位置(步骤S33)。此外,在图7中,示出在块BL33内贴装裸芯片D的例子,作为块BL33的块基准裸芯片而使用基板基准裸芯片RD2,作为基板基准裸芯片而使用基板基准裸芯片RD1。

若块BL33内的裸芯片D的贴装结束(在步骤S34中判断为是的情况),则移动至下个块(步骤S36)。例如,将下个块设为块BL32,在块BL32中,反复进行步骤S31~S34来贴装裸芯片D。在该情况下,如图8所示,作为块基准裸芯片而使用块基准裸芯片BRD32,作为基板基准裸芯片而使用基板基准裸芯片RD1。以后,使用位于各块的右上的块基准裸芯片。

以后,控制装置CNT例如按照块BL32、BL31、BL23、BL22、BL21、BL13、BL12、BL11的顺序进行块内的裸芯片D的贴装。若贴装所有块内的裸芯片D(在步骤S35中判断为是的情况)则结束。在贴装块BL31、BL23、BL22、BL13内的裸芯片D的情况下,作为基板基准裸芯片而使用基板基准裸芯片RD1。在贴装块BL21、BL12内的裸芯片D的情况下,作为基板基准裸芯片而使用基板基准裸芯片RD1或者基板基准裸芯片RD2。在贴装块BL11内的裸芯片D的情况下,作为块基准裸芯片而使用块基准裸芯片BRD11,作为基板基准裸芯片而使用基板基准裸芯片RD2。此外,块BL33、BL32、BL31、BL23、BL22、BL21、BL13、BL12、BL11为相同大小。

此外,在因错误等停止之后再次启动生产时,也修正因停止的时间造成的变化的影响等,因此,控制装置CNT在开始生产时识别块基准裸芯片和基板基准裸芯片并进行基板伸缩的修正。

在上述的贴装方法中,在由图8的椭圆包围的区域BL10、BL20、BL30、BL01、BL02、BL03没有贴装裸芯片D。在贴装于这些区域的情况下,例如,与上述的块同样地将这些区域看作块。在此,这些块为一行或者一列的区域,为比上述的块小的区域。在该情况下,作为基板基准裸芯片而使用基板基准裸芯片RD1,作为块基准裸芯片而分别使用块基准裸芯片BRD10、BRD20、BRD30、BRD01、BRD02、BRD03并贴装裸芯片D。

作为其他贴装方法而将区域BL10、BL20、BL30、BL01、BL02、BL03包含在其他块来贴装裸芯片D。在该情况下,块的大小不会相同。具体来说,区域BL10、BL01包含在块BL11内,区域BL20包含在块BL21内,区域BL30包含在块BL31内,区域BL02包含在块BL12内,区域BL03包含在块BL13内。

<变形例>

以下,针对代表的变形例例示几种。在以下的变形例的说明中,相对于具有与在上述实施方式中说明的同样的构成以及功能的部分,使用与上述实施方式同样的附图标记。然后,针对相关部分的说明,在技术上不矛盾的范围内适当援用上述实施方式中的说明。另外,上述实施方式的一部分、以及多个变形例的全部或者一部分在技术上不矛盾的范围内能够适当组合应用。

(第一变形例)

使用图9说明第一变形例的贴装方法。图9是说明第一变形例中的贴装方法的图,是示出贴装有最初的块内的所有裸芯片的基板的俯视图。

在贴装各裸芯片D前,在若进行步骤S31、S32的贴装位置修正则生产性下降的情况下,在块尺寸变小而能够以短时间贴装的情况下,控制装置CNT也可以仅在各块内的贴装开始时进行步骤S31、S32的贴装位置修正。第一变形例的贴装方法的其他步骤与实施方式的贴装方法相同。

如图9所示,在块BL33中,仅在贴装基板基准裸芯片RD2的正下方的裸芯片D时,控制装置CNT进行步骤S31、S32的贴装位置修正,在贴装块BL33内的其他裸芯片时,控制装置CNT不进行步骤S31的贴装位置测量,使用在贴装正下方的裸芯片D时使用的测定值(步骤S31)的结果而实施步骤S32的修正。同样地,在块BL32中,在仅贴装块基准裸芯片BRD32的正下方的裸芯片D时,控制装置CNT进行步骤S31、S32的贴装位置修正,在贴装块BL32内的其他裸芯片时,控制装置CNT不进行步骤S31、S32的贴装位置修正,使用在贴装正下方的裸芯片D时所使用的测定值(步骤S31)的结果,实施步骤S32的修正。也同样进行其他块内的裸芯片D的贴装。由此,与实施方式相比能够大幅度削减步骤S31的贴装位置修正的次数。

(第二变形例)

使用图10说明第二变形例的贴装方法。图10是说明第二变形例中的贴装方法的图,是示出贴装有最初的块内的四列的裸芯片的基板的俯视图。

在第一变形例的各块的贴装开始时的步骤S31、S32的贴装位置修正中,从定义的块尺寸到贴装需要时间,在存在热膨胀或经时变化的影响的情况下,可以在块内的各列的贴装开始时实施步骤S31、S32的贴装位置修正。第二变形例的贴装方法的其他步骤与实施方式的贴装方法相同。

如图10所示,在块BL33中,在贴装第一列的最初的裸芯片D(基板基准裸芯片RD2的正下方的裸芯片D)、第二列的最初的裸芯片D、……、以及第六列(最后的列)的最初的裸芯片D时,控制装置CNT不进行步骤S31、S32的贴装位置修正,在贴装各列的第二个以后的裸芯片时,控制装置CNT不进行步骤S31、S32的贴装位置修正。由此,与实施方式相比能够削减步骤S31、S32的贴装位置修正的次数。

(第三变形例)

在第一变形例中在块内的贴装开始时,在第二变形例中在块内的列的贴装开始时,通过贴装位置而决定步骤S31、S32的贴装位置修正的实施时期,但可以设定贴装经过个数、经过时间等,在超过设定时每隔规定间隔实施步骤S31、S32的贴装位置修正。第三变形例的贴装方法的其他步骤与实施方式的贴装方法相同。

(第四变形例)

图11是示出第四变形例中的贴装有基板基准裸芯片以及块基准裸芯片的基板的俯视图。

控制装置CNT在多个块BL中的、与由第一边SD1和第二边SD2构成的第一角部C1最近的作为第一区域的块BL11贴装基板基准裸芯片RD1,在与由第三边SD3和第四边SD4构成的第二角部C2最近的作为第二区域的块BL66贴装基板基准裸芯片RD2。

在实施方式的步骤S1中,控制装置CNT将基板基准裸芯片RD1贴装在区域DR的左下端,将基板基准裸芯片RD2贴装在右上端。在步骤S2中,控制装置CNT在各块的右上贴装块基准裸芯片BRD。另一方面,在第四变形例的步骤S1中,如图11所示,控制装置CNT在左下的块BL11的右下贴装基板基准裸芯片RD1,在右上的块BL66的右下贴装基板基准裸芯片RD2。在步骤S2中,控制装置CNT除了块BL11、BL66,而在各块的右下贴装块基准裸芯片BRD。控制装置CNT在块BL12、BL13、BL14、BL15、BL16、……、BL61、BL62、BL63、BL64、BL65分别贴装块基准裸芯片BRD12、BRD13、BRD14、BRD15、BRD16、……、BRD61、BRD62、BRD63、BRD64、BRD65。即,控制装置CNT在作为第一区域的块BL11以及作为第二区域的块BL66没有贴装作为第三裸芯片的块基准裸芯片BRD。

由此,能够将各块的形状或者大小设为相同。此外,可以在各块的左上贴装有块基准裸芯片BRD,在左下的块BL11的左上贴装有基板基准裸芯片RD1,在右上的块BL66的左上贴装有基板基准裸芯片RD2。

(第五变形例)

图12是示出第五变形例中的贴装有基板基准裸芯片以及块基准裸芯片的基板的俯视图。

在实施范式中,控制装置CNT利用设于一个贴装台(Y横梁)的贴装头贴装裸芯片D,但在第五变形例中,控制装置CNT利用设于两个贴装台(Y横梁)的贴装头交替拾取裸芯片D并贴装于基板P。

控制装置CNT例如贴装第四变形例同样地基板基准裸芯片RD1、RD2、块基准裸芯片BRD。此时,可以利用设于一个贴装台(Y横梁)的贴装头进行贴装,也可以利用设于两个贴装台(Y横梁)的贴装头进行贴装。

控制装置CNT例如使用第一贴装台(Y横梁)的贴装头,基于基板基准裸芯片RD1以及块基准裸芯片BRD36而在块BL36贴装裸芯片D,利用第二贴装台(Y横梁)的贴装头,基于基板基准裸芯片RD1以及基板基准裸芯片RD2而在块BL66贴装裸芯片D。此时,控制装置CNT利用设于两个贴装台(Y横梁)的贴装头交替拾取裸芯片D贴装于基板P。

(第六变形例)

图17是示出第六变形例中的以基板基准裸芯片以及块基准裸芯片为基准位置贴装有裸芯片的基板的俯视图。

在第六变形例中,对块基准裸芯片的配置加以改善,像实施方式中的图8的区域BL10、BL20、BL30等那样,尽管贴装有块基准裸芯片BRD,但不设置不贴装裸芯片D的位置。即,设为在图8中的左端的一列以及下端的一行不贴装基板基准裸芯片以及块基准裸芯片。在此,第六变形例的块的数量以及在各块内载置的裸芯片的数量与实施方式相同。另外,如图17所示,不将块BL12、BL13的块基准裸芯片BRD12、BRD13配置在块内的右上而是配置在左下。另外,不设置块BL11的块基准裸芯片BRD11,并且将基板基准裸芯片RD1配置在块BL11内的左下。此外、基板基准裸芯片RD1配置在图8中的基板基准裸芯片RD1的右上,错开一个裸芯片大小的量。

由此,能够确保基准裸芯片间的距离,并且设为块的端全部包含在各块内的布局,不限于贴装有上述这种块基准裸芯片BRD,没有不贴装裸芯片D的区域BL01、BL01、BL03、BL10、BL20、BL30这样的区域,能够高效地进行贴装。

以下,作为实施例而说明应用于FOPLP的例子,但不限于此,能够应用于使用临时基板的封装。

【实施例】

图13是示出实施例中的倒装芯片贴装机的概略的俯视图。图14是说明在图13中从箭头A方向观察时拾取倒装头、转移头以及贴装头的动作的图。

作为芯片贴装装置的倒装芯片贴装机10大体具有裸芯片供给部1、拾取部2、转移部8、中间台部3、贴装部4、搬运部5、基板供给部6K、基板搬出部6H、以及监视并控制各部分的动作的控制装置7。

首先,裸芯片供给部1向基板P供给要安装的裸芯片D。裸芯片供给部1具有保持划分后的晶片11的晶片保持台12、从晶片11上推裸芯片D的用虚线示出的上推单元13、和晶片环供给部18。裸芯片供给部1通过未图示的驱动机构沿XY方向移动,使拾取的裸芯片D移动至上推单元13的位置。晶片环供给部18具有收容有晶片环14(参照图14)的晶片盒,依次将晶片环14供给至裸芯片供给部1,来更换至新的晶片环14。裸芯片供给部1以能够从晶片环14拾取期望的裸芯片D的方式使晶片环14移动至拾取点。晶片环14为固定晶片11、能够安装于裸芯片供给部1的夹具。

拾取部2具有拾取并翻转裸芯片D的拾取倒装头21、和升降、旋转、翻转筒夹22以及使其X方向移动的未图示的各驱动部。通过这种构成,拾取倒装头21拾取裸芯片,使拾取倒装头21旋转180度,使裸芯片D的凸块翻转而朝向下表面,使裸芯片D成为交付至转移头81的姿势。

转移部8从拾取倒装头21接受翻转的裸芯片D,载置于中间台31。转移部8具备与拾取倒装头21同样地具有在前端吸附保持裸芯片D的筒夹82的转移头81、和使转移头81沿Y方向移动的Y驱动部83。

中间台部3具有临时载置裸芯片D的中间台31以及台识别摄像头34。中间台31能够利用未图示的驱动部在Y轴方向上移动。

贴装部4从中间台31拾取裸芯片D,并贴装在搬运来的基板P上。在此,作为基板P而使用玻璃面板。贴装部4具备与拾取倒装头21同样地具有在前端吸附保持裸芯片D的筒夹42的贴装头41、使贴装头41沿Y轴方向移动的作为驱动部的Y横梁43、拍摄基板基准裸芯片RD1、RD2(参照图5)等且识别贴装位置的作为摄像装置的基板识别摄像头44、和X横梁45。如图12所示,X横梁45设于搬运轨51、52的附近,Y横梁43以跨过贴装台BS之上的方式沿Y轴方向延伸,两端部通过X横梁45而在X轴方向上自由移动地被支承。

贴装头41为具有通过真空吸附而自由装卸地保持裸芯片D的筒夹42的装置,沿Y轴方向以及Z轴方向自由往返移动地安装于Y横梁43。贴装头41具有保持并搬运从中间台31拾取的裸芯片D,在吸附固定于贴装台BS的基板P上安装裸芯片D的功能。此外,在贴装头41与X横梁45相比向中间台31侧移动的情况下,以使筒夹42变得比X横梁45高的方式使贴装头41上升。

通过这种构成,贴装头41从中间台31拾取裸芯片D,基于基板识别摄像头44的摄像数据而向基板P贴装裸芯片D。贴装头41对应于实施方式的贴装头BH,基板识别摄像头44对应于实施方式的摄像装置CM。

搬运部5具有供基板P沿X轴方向移动的搬运轨51、52。搬运轨51、52平行设置。通过这种构成,从基板供给部6K搬出基板P,沿搬运轨51、52移动至贴装位置为止,并到贴装后基板搬出部6H为止移动,向基板搬出部6H交付基板P。在向基板P贴装裸芯片D的过程中,基板供给部6K搬出新的基板P,在搬运轨51、52上待机。

控制装置7具备保存监视并控制倒装芯片贴装机10的各部分的动作的程序(软件)的存储器、和执行在存储器中保存的程序的中央处理装置(CPU)。例如,控制装置7获取来自基板识别摄像头44以及基板识别摄像头44的图像信息、贴装头41的位置等的各种信息并保存至存储器,控制贴装头41的贴装动作等各构成要素的各动作。

图15是示出图13的裸芯片供给部的主要部分的概略剖视图。如图15所示,裸芯片供给部1具备保持晶片环14的扩展环15、将在晶片环14保持且粘接有多个裸芯片D的切割带16沿水平定位的支承环17、用于向上方上推裸芯片D的上推单元13。为了拾取规定的裸芯片D,上推单元13通过未图示的驱动机构沿上下方向移动,裸芯片供给部1沿水平方向移动。此外,基板基准裸芯片RD1、RD2、块基准裸芯片BRD与裸芯片D同样地位于晶片11内。

接着,使用图16说明在实施例的倒装芯片贴装机中实施的贴装方法(半导体器件的制造方法)。图16是示出用图13的倒装芯片贴装机实施的贴装方法的流程图。在下述步骤之前,搬入保持具有裸芯片D的切割带16的晶片环14,搬入具有多个区域的基板P。

(步骤S21:晶片裸芯片拾取)

控制装置7以使拾取的裸芯片D位于上推单元13的正上方的方式移动晶片保持台12,将剥离对象裸芯片定位于上推单元13和筒夹22。以使上推单元13的上表面接触切割带16的背面的方式移动上推单元13。此时,控制装置7将切割带16吸附至上推单元13的上表面。控制装置7一边对筒夹22抽真空一边使其下降,使其着落于剥离对象的裸芯片D上,来吸附裸芯片D。控制装置7使筒夹22上升,从切割带16剥离裸芯片D。由此,裸芯片D由拾取倒装头21拾取。步骤S1中的基板基准裸芯片RD1、RD2以及步骤S2中的块基准裸芯片BRD与裸芯片D同样地由拾取倒装头21拾取。

(步骤S22:拾取倒装头移动)

控制装置7从拾取位置向翻转位置移动拾取倒装头21。

(步骤S23:拾取倒装头翻转)

控制装置7使拾取倒装头21旋转180度,使裸芯片D的凸块面(表面)翻转而朝向下表面,而设为将裸芯片D交付至转移头81的姿势。基板基准裸芯片RD1、RD2以及块基准裸芯片BRD也与裸芯片D同样地由拾取倒装头21翻转。

(步骤S24:转移头交付)

控制装置7从拾取倒装头21的筒夹22由转移头81的筒夹82拾取裸芯片D,进行裸芯片D的交付。基板基准裸芯片RD1、RD2以及块基准裸芯片BRD也与裸芯片D同样地进行交付。

(步骤S25:拾取倒装头翻转)

控制装置7使拾取倒装头21翻转,使筒夹22的吸附面朝向下方。

(步骤S26:转移头移动)

在步骤S25之前或者与其并行地,控制装置7将转移头81移动至中间台31。

(步骤S27:中间台裸芯片载置)

控制装置7将保持在转移头81的裸芯片D载置于中间台31。基板基准裸芯片RD1、RD2以及块基准裸芯片BRD也与裸芯片D同样地载置于中间台。

(步骤S28:转移头移动)

控制装置7使转移头81移动至裸芯片D基板基准裸芯片RD1、RD2、块基准裸芯片BRD)的交付位置。

(步骤S29:中间台位置移动)

在步骤S28之后或者与其并行地,控制装置7使中间台31移动至与贴装头41进行交付的位置。

(步骤S2A:贴装头交付)

控制装置7通过贴装头41的筒夹从中间台31拾取裸芯片D,进行裸芯片D的交付。基板基准裸芯片RD1、RD2以及块基准裸芯片BRD也与裸芯片D同样地被交付。

(步骤S2B:中间台位置移动)

控制装置7使中间台31移动至与转移头81的交付位置。

(步骤S2C:贴装头移动)

控制装置7将保持有贴装头41的筒夹42的裸芯片D移动至基板P上。

(步骤S2D:贴装)

控制装置7将由贴装头41的筒夹42从中间台31拾取的裸芯片D(基板基准裸芯片RD1、RD2、块基准裸芯片BRD)贴装至涂敷有粘接性的主剂(粘接层)的基板P上。更具体来说,控制装置7在步骤S1中将基板基准裸芯片RD1、RD2贴装于基板P上,在步骤S2中将块基准裸芯片BRD贴装于基板P上,在步骤S3中将裸芯片D贴装于基板P上。

(步骤S2E:贴装头移动)

控制装置7使贴装头41移动至与中间台31的交付位置。

另外,在步骤S2E之后,控制装置7利用基板搬出部6H从搬运轨51、52取出贴装有基板基准裸芯片RD1、RD2、块基准裸芯片BRD以及裸芯片D的基板P。从倒装芯片贴装机10搬出基板P。

此后,在通过封固树脂将配置在基板P的粘接层上的多个裸芯片(半导体芯片)一并封固而形成具有多个半导体芯片和覆盖多个半导体芯片的封固树脂的封固体之后,从封固体剥离基板P,接着在贴附有封固体的基板P的面上形成再布线层,制造FOPLP。

以上,基于实施方式、变形例以及实施例具体说明了由本发明人提出的发明,但本发明不限于上述实施方式、变形例以及实施例,当然也能够进行各种各样的变更。

例如,在实施例中,以拾取部2、转移部8、中间台部3以及贴装部4为一个的例子进行了说明,但拾取部2、转移部8、中间台部3以及贴装部4也可以分别为二组。

另外,在实施例中,说明了在Y横梁43设有一个贴装头41的例子,但也可以设置多个贴装头。

另外,在实施例中对倒装芯片贴装机进行了说明,但也能够应用于不翻转从裸芯片供给部拾取的裸芯片地进行贴装的芯片贴装机。

- 半导体制造装置、半导体器件的制造方法及芯片贴装机

- 芯片贴装机、贴装方法及半导体器件的制造方法