电光封装及制造方法

文献发布时间:2023-06-19 09:52:39

对(多个)相关申请的交叉引用

本申请要求2018年4月12日提交的题为“PACKAGING OF OPTICAL AND ELECTRONICCOMPONENTS”的美国临时申请号62/656,757的优先权和利益,并要求2019年4月4日提交的题为“OPTICAL ENGINE”的美国临时申请号62/829,519的优先权和利益,其两者的全部内容通过引用被并入本文中。

技术领域

根据本公开的实施例的一个或多个方面涉及封装,并且更具体地,涉及电光封装以及用于制造这种封装的方法。

背景技术

将电子电路与电光系统结合以用于调制光、检测调制的光以及与光纤对接的系统具有广泛的应用。在这种系统的设计中,由于各种原因(包括光学元件之间的对准需要、热管理需要以及在一些应用中对高速操作的要求),实现紧凑性和低成本可能具有挑战性。

因此,需要一种改进的电光封装以及用于制造这种封装的方法。

发明内容

根据本发明的一些实施例,提供了一种系统,包括:耦合到光纤阵列的第一电光芯片;以及耦合到所述第一电光芯片的第一物理介质相关的集成电路。

在一些实施例中,该系统还包括第一重分布层和平行于第一重分布层的第二重分布层,第一物理介质相关的集成电路在第一重分布层和第二重分布层之间;第一重分布层和第二重分布层之间的第一通孔芯;耦合到光纤阵列的第一光学插入器芯片,第一电光芯片通过第一光学插入器芯片耦合到光纤阵列;第一导体阵列,其固定到第一重分布层和第一光学插入器芯片;以及在第二重分布层的外表面上的第二导体阵列。

在一些实施例中,第一物理介质相关的集成电路和第一通孔芯是单个硅集成电路的部分。

在一些实施例中,该系统还包括在第一重分布层和第二重分布层之间的包覆模,该包覆模包封第一物理介质相关的集成电路和第一通孔芯。

在一些实施例中,第一光学插入器芯片包括V形槽的阵列,光纤阵列中的每个光纤在相应V形槽中。

在一些实施例中,该系统还包括有机基板,该有机基板在其表面上具有多个导电焊盘,以及在第二导体阵列和导电焊盘之间的插座。

在一些实施例中,插座包括弹性体的绝缘层和延伸通过弹性体的绝缘层的多个导体。

在一些实施例中,第一电光芯片包括调制器,该系统还包括:第二电光芯片,其包括光电探测器;以及耦合到第二电光芯片的第二物理介质相关的集成电路。

在一些实施例中:该系统包括在第二导体阵列和导电焊盘之间的有机基板和插座;在第一物理介质相关的集成电路与有机基板之间的导电路径包括插座的导体中的一部分;并且在第二物理介质相关的集成电路与有机基板之间的导电路径包括插座的导体中的一部分。

在一些实施例中,第二电光芯片通过第一光学插入器芯片耦合到光纤阵列。

在一些实施例中:在第一物理介质相关的集成电路与有机基板之间的导电路径包括第一通孔芯的导体中的一部分;并且在第二物理介质相关的集成电路和有机基板之间的导电路径包括第一通孔芯的导体中的一部分。

在一些实施例中,该系统还包括第二光学插入器芯片,其中第二电光芯片通过第二光学插入器芯片耦合到光纤阵列。

在一些实施例中,该系统还包括第二通孔芯,其中:在第一物理介质相关的集成电路和有机基板之间的导电路径包括第一通孔芯的导体中的一部分;并且在第二物理介质相关的集成电路和有机基板之间的导电路径包括第二通孔芯的导体中的一部分。

在一些实施例中,从第一电光芯片延伸到第一物理介质相关的集成电路的导电路径的长度小于500微米。

在一些实施例中,从第一电光芯片延伸到第一物理介质相关的集成电路的导电路径的长度小于350微米。

根据本发明的一些实施例,提供了一种用于制造封装的方法,该方法包括:在载体晶片上形成第一重分布层;将通孔芯附接到第一重分布层;将物理介质相关的集成电路附接到第一重分布层;向通孔芯上以及向物理介质相关的集成电路上模制包覆模;研磨包覆模的上表面;以及在包覆模的上表面上形成第二重分布层。

在一些实施例中,该方法还包括:从载体晶片上去除中间产品,该中间产品包括:第一重分布层、通孔芯、物理介质相关的集成电路、包覆模;以及第二重分布层。

在一些实施例中,该方法还包括在第二重分布层上形成多个导电柱。

在一些实施例中,该方法还包括将电光芯片附接到包括多个导电迹线和多个V型槽的光学插入器芯片。

在一些实施例中,该方法还包括将中间产品附接到光学插入器芯片,该中间产品包括:第一重分布层;通孔芯;物理介质相关的集成电路;包覆模;以及第二重分布层,以便形成通过多个导电迹线中的一迹线从物理介质相关的集成电路到电光芯片的导电路径。

在一些实施例中,该方法还包括将光纤固定在多个V形槽之一中。

附图说明

将参考说明书、权利要求书和附图来领会和理解本公开的这些以及其他特征和优点,其中:

图1是根据本公开的实施例的扇出晶片级封装的侧视截面图;

图2A是根据本公开的实施例的芯片上封装结构的俯视截面图;

图2B是根据本公开的实施例的芯片上封装结构的侧视截面图;

图2C是根据本公开的实施例的包括芯片上封装结构的系统的一部分的侧视截面图;

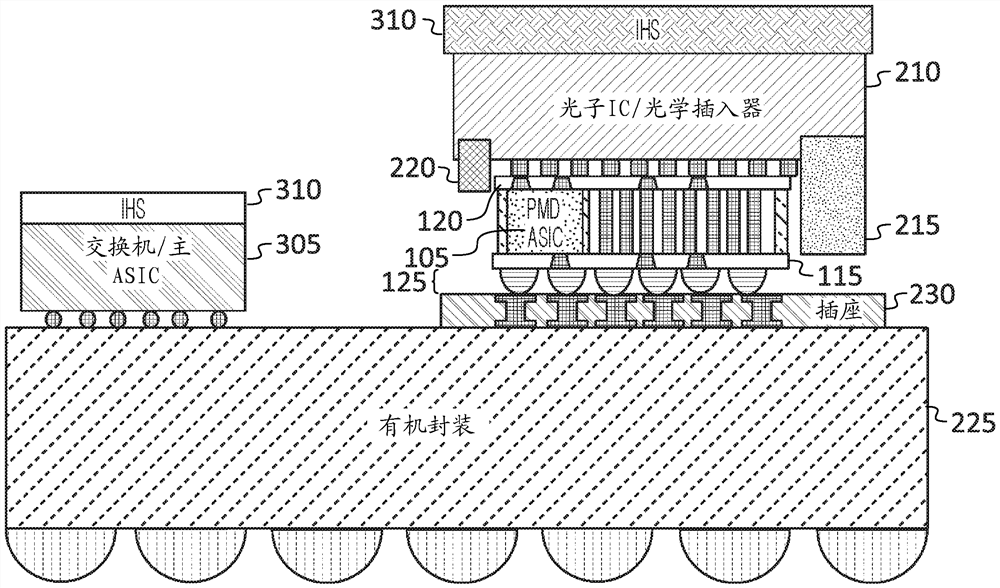

图3是根据本公开的实施例的包括芯片上封装结构的系统的一部分的侧视截面图;

图4A是根据本公开的实施例的包括芯片上封装结构的系统的一部分的俯视图;

图4B是根据本公开的实施例的包括芯片上封装结构的系统的一部分的俯视图;

图4C是根据本公开的实施例的包括芯片上封装结构的系统的一部分的俯视图;

图5A是根据本公开的实施例的用于制造封装的方法的流程图;

图5B是根据本公开的实施例的用于制造封装的方法的流程图;

图6A是根据本公开的实施例的包括芯片上封装结构的系统的透视图;

图6B是根据本公开的实施例的包括芯片上封装结构的系统的俯视图;

图7A是根据本公开的实施例的在封装的制造中的中间产品的侧视截面图;

图7B是根据本公开的实施例的在封装的制造中的中间产品的侧视截面图;

图7C是根据本公开的实施例的在封装的制造中的中间产品的侧视截面图;

图7D是根据本公开的实施例的在封装的制造中的中间产品的侧视截面图;

图7E是根据本公开的实施例的在封装的制造中的中间产品的侧视截面图;

图7F是根据本公开的实施例的在封装的制造中的中间产品的侧视截面图;

图7G是根据本公开的实施例的在封装的制造中的中间产品的侧视截面图;

图7H是根据本公开的实施例的在封装的制造中的中间产品的侧视截面图;和

图7I是根据本公开的实施例的在封装的制造中的中间产品的侧视截面图。

具体实施方式

以下结合附图阐述的详细描述旨在作为对根据本公开提供的电光封装及制造方法的示例性实施例的描述,并且不旨在代表可以构造或利用本公开所用的唯一形式。该描述结合所图示的实施例阐述了本公开的特征。然而,应理解,相同或等同的功能和结构可以通过不同的实施例来实现,所述不同的实施方式也旨在被涵盖在本公开的范围内。如本文中其他地方所表示的,相似的元件编号旨在指示相似的元件或特征。

图1示出根据一些实施例的扇出晶片级封装。扇出晶片级封装包括(i)物理介质相关(PMD)的专用集成电路(ASIC)105和夹在两个重分布层(RDL)——上部RDL 115和下部RDL120之间的通孔芯110,(ii)可以用作上部RDL 115上的第一层互连或第二层互连的互连125,以及(iii)用于第一层互连、在下部RDL 120的下表面上的具有焊料帽的多个铜柱130。球栅阵列或插座可以用作上部RDL 115上的第二层互连。在一些实施例中,上部RDL 115上的互连125是具有焊料帽的另外多个铜柱,并且可能适合用作第一层互连。通孔芯110可以包括在诸如环氧树脂(或“模具”)、覆铜FR4、玻璃或硅的电介质中的相对较高(例如150微米-200微米高)的铜柱或铜通孔的阵列(例如350微米节距的正方形阵列)。在一些实施例中,PMD ASIC 105和通孔芯110可以是单个硅集成电路(其可以被称为具有有源电路的硅插入器)的一部分(例如,它们可以被制造在单个硅基板中或单个硅基板上)。每个RDL 115、120可以由具有导电迹线和导电通孔的聚酰亚胺层组成;每个RDL 115、120可以依次包括多个层,即,其可以包括一个或多个RDL。上部RDL 115和下部RDL 120中的每一个可以是包括多达四个单层RDL的复合RDL(单层RDL具有一个绝缘层,并且可能具有(i)在其两个表面上的导电迹线,以及(ii)通过绝缘层的导电通孔)。PMD ASIC 105可以在其“前表面”或下表面上(在图1的取向上),即在与下部RDL 120接触的表面上具有电连接。包覆模135(例如,环氧树脂包覆模)可以包封PMD ASIC 105和通孔芯110。

图2A和2B示出了根据一些实施例的“芯片上封装”结构。芯片上封装结构包括扇出晶片级封装和光子集成电路(PIC),其又包括光学插入器210、光纤盖215和电光芯片220。电光芯片220可以包括调制器阵列(例如,如所示的电吸收调制器(EAM)的阵列)和/或激光器阵列(在这种情况下,光子集成电路可以称为“发射器PIC”或“TX PIC”)或光电探测器阵列(在这种情况下,光子集成电路可以称为“接收器PIC”或“RX PIC”),或调制器(和/或激光器)和光电探测器两者。

光学插入器210可以包括V形槽的阵列,该阵列用于对准通过光纤盖215固定在适当位置(并用环氧树脂固定在适当位置,环氧树脂也可以固定光纤盖215)的多个光纤、模式转换器(例如,锥形波导)阵列,以及用于电光芯片和/或激光芯片的腔。沿任一方向行进的光可耦合在光学插入器210上的第一波导和电光芯片220上的第二波导之间;每个第一波导的一端可以充分接近第二波导的对应端,并与第二波导的对应端充分好地对准和模式匹配,以使光以最小的损耗在波导之间耦合。如果电光芯片220包括光电探测器阵列,则PMDASIC 105可以包括用于放大来自光电探测器的信号的跨阻放大器的阵列;如果电光芯片220包括调制器阵列,则PMD ASIC 105可以包括调制器驱动电路的阵列。

在操作中,如果电光芯片220包括光电探测器阵列,则光到达光纤,耦合到模式转换器,传播到光电探测器阵列,并转换为电信号,所述电信号由PMD ASIC 105放大。如果电光芯片包括调制器阵列,则未调制的光到达光纤的第一子集,耦合到模式转换器的第一子集,传播到调制器阵列,并根据由PMD ASIC 105供应的信号进行调制,并且调制的光通过模式转换器的第二子集传播回来,并通过光纤的第二子集被馈送出去。图2C示出了通过插座230连接到有机封装或印刷电路板225的芯片上封装结构,如下面进一步详细描述的。

芯片上封装结构可以用于交换机和光学器件的封装内集成。图3示出了包括芯片上封装结构的系统,该系统通过插座230连接到有机封装225(例如,连接到有机封装225的有机基板的上表面上的多个导电焊盘)。插座230可以包括弹性体的绝缘层和延伸通过弹性体层的多个导体。插座230可以是例如可从Ironwood Electronics(ironwoodelectronics.com)获得的几种弹性体中导体插座中的任何一个。在一些实施例中,不使用插座230,而是通过回流工艺将芯片上封装结构连接到有机封装225。在有机封装225上的还有交换机ASIC 305或“主”ASIC,其可以是提供分组交换功能的CMOS ASIC。在一些实施例中,代替交换机ASIC或除交换机ASIC之外,有机封装可以包括一个或多个GPU、FPGA或其他集成数字电路。在一些实施例中,如所示出的,交换机ASIC 305直接连接到有机封装225;在其他实施例中,它直接连接到高密度封装(例如,它封装在高密度封装中),该高密度封装进而连接到有机封装。PHY电路可以是交换机ASIC 305的一部分,或者它可以在单独的PHY芯片中实现。例如,交换机ASIC 305和每个PMD ASIC 105之间的接口可以是高速串行接口,在这种情况下,交换机ASIC 305可以包括多个串行器/解串器电路,或者该接口可以是并行接口,在这种情况下,交换机ASIC 305中用于与每个PMD ASIC 105对接的电路可以是重定时电路,或者情况可能是如下那样:在交换机ASIC 305中不需要附加电路来与每个PMD ASIC 105对接。

一个或多个集成散热器(IHS)310可以(i)为光学插入器210以及(ii)通过光学插入器210和具有焊料帽的短铜柱130的阵列为PMD ASIC 105提供热管理。由(i)光学插入器上的IHS 310、(ii)扇出晶片级封装和(iii)插座230组成的堆叠可通过机械装置(诸如合适的夹具)固定到有机封装225上。从PMD ASIC 105到电光芯片220的电路径可以是从PMDASIC 105的前表面、通过下部RDL 120(其与PMD ASIC 105的前表面相邻)、通过具有焊料帽的短铜柱130、以及通过光学插入器210上的短导电迹线的短路径(例如,短于500微米或短于300微米的路径),所述光学插入器210可以通过共晶接合连接到电光芯片220。热量可能从PMD ASIC 105向上流动通过下部RDL 120、通过具有焊料帽的短铜柱130的阵列、并且通过光学插入器210、到达光学插入器上的IHS 310。交换机ASIC 305(或PHY芯片,如果存在的话)与芯片上封装结构之间的电连接可以由有机封装225中的导电迹线和延伸通过插座230内的弹性体层的导体形成。例如,交换机ASIC 305(或PHY芯片,如果存在的话)与PMD ASIC105之间的高速串行链路可以从交换机ASIC 305(或PHY芯片,如果存在的话)延伸通过有机封装225内或上的迹线、通过插座230、通过互连125、通过上部RDL 115的层、通过具有焊料帽的铜柱130、通过下部RDL 120并进入PMD ASIC 105。这种连接的总长度可以可缩放(例如,通过将芯片上封装结构移动得更靠近交换机ASIC 305使得在芯片上封装结构之间存在足够的间隙并且交换机ASIC散发的热量不会使芯片上封装结构的性能降级至不可接受的程度)以满足例如超短距离(USR)、极短距离(VSR)或特短距离(XSR)要求。

图4A示出了根据一个实施例的系统(其可以被称为光驱动器1(LD1),选项1),在其中例如通过共享的插座230将芯片上单独的接收器和发射器封装结构连接到有机封装225。在图4A中,光学插入器210和下部RDL 120被绘制为透明的,使得可以看到这些元件下方的部分的相对位置。对准销405可以用于维持芯片上封装结构与有机封装225之间或插座230与有机封装225之间的对准。在图4A的实施例中,芯片上单独的接收器和发射器封装可以在安装在插座230上之前被单独测试。

图4B示出了根据一个实施例的系统(其可以称为光驱动器1(LD1),选项2),在其中单个芯片上封装结构,其包括共享光学插入器210和通孔芯110的单独的接收器(光电探测器(“PD”))和发射器(调制器(“Mod”))电光芯片,通过插座230连接到交换机ASIC 305。图4C示出了根据一个实施例的系统(其可以称为光驱动器2),该系统与图4B的系统的不同之处在于:PHY电路410(发送PHY电路(“Tx Phy”)和接收PHY电路(“Rx Phy”))被集成到芯片上封装结构中。与图4A的实施例相比,图4B和图4C的实施例可以具有如下优点:具有较低的制造成本;图4A的实施例优点可以具有如下优点:使得能够独立替换芯片上的单独的接收器和发射器封装结构。

图5A示出了根据一些实施例的用于制造芯片上封装结构或“光驱动器”的方法。图5B示出了根据一些实施例的系统集成方法。图6A和6B示出了根据一些实施例的集成系统,其包括用于高达51.2 Tb/s的操作的共同封装的交换机ASIC 305和芯片上封装结构。

图7A-7I示出了根据一些实施例的用于制造扇出晶片级封装,将其固定到包括光学插入器和电光芯片的子组件以及附接光纤的方法。下部RDL 120在载体晶片上形成(例如,通过旋涂)(图7A和7B),通孔芯110和PMD ASIC 105附接到下部RDL 120(图7C),包覆模135被模制到中间产品上并研磨平坦(图7D),上部RDL 115形成在包覆模135的上表面上,并且中间产品从载体晶片上脱落,并且中间产品倒置(或“翻转”)(图7E)。形成具有焊料帽的铜柱130(图7F),再次将中间产品倒置并在“芯片上封装附接”操作中附接至PIC(图7G),形成互连125(例如,形成球栅阵列的球)(图7H),并且将光纤放置在V形槽中(例如,与光学插入器210被动地对准),并且将光纤盖215固定在适当位置(图7I)。

为了便于描述,本文中可以使用空间相对术语,诸如“在……下方”、“在……以下”、“下部”、“在……之下”、“在……之上”、“上部”等等来描述如图中所图示的一个元件或特征与另外的(一个或多个)元件或(一个或多个)特征的关系。将理解的是,这种空间相对术语旨在涵盖除了附图中描绘的取向之外的在使用或操作中的设备的不同取向。例如,如果附图中的设备被翻转,则被描述为“在其他元件或特征以下或之下或下方”的元件然后将被定向为“在其他元件或特征之上”。因此,示例术语“在……以下”和“在……之下”可以涵盖“在……之上”和“在……之下”两个方位。设备可以以其他方式定向(例如,旋转90度或以其他定向),并且应当相应地解释本文中使用的空间相对描述语。另外,还将理解的是,当一层被称为在两层“之间”时,它可以是这两个层之间的唯一层,或者也可以存在一个或多个中间层。

将理解的是,当元件或层被称为:“在另一元件或层上”、“连接至另一元件或层”、“耦合到另一元件或层”或“与另一元件或层邻近”时,其可以直接在另一元件或层上、连接至另一元件或层、耦合到另一元件或层或与另一元件或层邻近,或者可以存在一个或多个中间元件或层。相反,当元件或层被称为“直接在另一元件或层上”,“直接连接至另一元件或层”,“直接耦合到另一元件或层”或“与另一元件或层紧邻”时,没有中间元件或层存在。

本文中列举的任何数值范围旨在包括在所列举范围内的具有相同数值精度的所有子范围。例如,范围“1.0至10.0”旨在包括在所列举的最小值1.0和所列举的最大值10.0之间(并且包括它们)的所有子范围,即,具有等于或大于1.0的最小值和等于或小于10.0的最大值,诸如,例如2.4至7.6。本文列举的任何最大数值限制旨在包括其中包括的所有较低数值限制,并且本说明书中列举的任何最小数值限制旨在包括其中包括的所有较高数值限制。

尽管在本文中已经具体地描述和说明了电光封装和制造方法的示例性实施例,但是许多修改和变化对于本领域技术人员将是显而易见的。因此,应理解,根据本公开的原理的电光封装和制造方法可以不同于如本文中具体描述的那样来体现。本发明还在所附权利要求及其等同物中来限定。

- 带封装壳体电光装置、投射显示装置、封装壳体及制造方法

- 树脂绝缘层的制造方法、电光装置用基板、电光装置的制造方法和电光装置