集成电路封装及其形成方法

文献发布时间:2023-06-19 11:17:41

背景技术

各种各样的电子组件、例如用于植入式医疗器件(IMD)的那些电子组件采用电子电路,例如用于对人体组织提供电刺激和/或监测生理状况。这样的IMD 可以将冲击能量和刺激脉冲形式的电疗能量输送到选定的身体组织。这些IMD 通常包括用于在规定条件下产生电能的输出电路,以及至少一根带有刺激电极的引线,所述刺激电极用于将电能输送到选定的组织。例如,已经开发了心脏起搏器和植入式心脏复律除颤器(ICD),以用于在心动过缓发作期间维持期望的心率,或者在检测到严重的心律不齐时对心脏进行心脏复律或除颤治疗。还已知其他刺激神经、大脑、肌肉和器官组织的医疗器件以用于治疗多种病症。

当前可用的IMD(包括ICD和植入式脉冲发生器(IPG))通常包括:金属外壳,该金属外壳被密封,因此不渗透体液;安装到该外壳的插头或连接器组件,用于与一根或多根引线进行电气和机械连接。这样的器件还具有与外部器件通信的遥测功能。在过去的几年中,IMD已从相对庞大的器件发展为功能日益强大的复杂小型器件。例如,对心脏复律/除颤引线和电极进行了许多改进,心脏复律/除颤引线和电极使心脏复律/除颤的能量能够精确地输送到上下心腔的选定的一个或多个部分,从而显著降低心脏复律或除颤所需的传递的冲击能量。高压输出电路也已经得到改进,以提供单相、双相或多相心脏复律/除颤冲击或脉冲波形,有时使用心脏复律/除颤电极的特定组合,这样有效地降低所需的冲击能量使心脏复律或除颤。

IMD的小型化推动包括电子电路部件在内的所有IMD部件的尺寸减小和成本降低,其中期望增加密度和减小此类部件的尺寸,使得整个电路可以更紧凑。随着IMD的尺寸减小,IMD的电子电路被形成为集成电路以适配在最小空间内。此外,由于部件的尺寸也被减小,因此期望改进IMD封装内的尺寸的使用。

对这种期望的一种响应是通过对器件的封装的技术改进,其中通过诸如重组晶片封装的封装技术来包括输出电路。特别地,在重构晶片封装(也称为扇出晶片级封装)中的开发努力集中在生产更薄和更小的电子封装。

发明内容

通常,本公开提供了集成电路封装以及形成这种封装的方法的各种实施例。所述集成电路封装可以包括衬底,所述衬底具有玻璃芯层以及设置在玻璃芯层的第一主表面与第二主表面之间的腔。设置在所述玻璃芯层的所述腔中的管芯可以被电连接至第一图案化导电层和第二图案化导电层中的至少一个,其中所述第一图案化导电层被设置成邻近所述玻璃芯层的第一主表面,并且所述第二图案化导电层被设置成邻近所述玻璃芯层的第二主表面。在一或多个实施例中,包封体可以设置在所述腔中、在所述管芯与所述腔的侧壁之间。

一方面,本公开提供了一种集成电路封装,所述集成电路封装包括具有玻璃芯层的衬底,其中所述玻璃芯层包括第一主表面、第二主表面和设置在所述玻璃芯层的第一主表面与第二主表面之间的腔。所述封装还包括:设置在所述玻璃芯层的腔中的管芯;设置在所述腔中、在所述管芯与所述腔的侧壁之间的的包封体;被设置成邻近所述玻璃芯层的第一主表面的第一图案化导电层;以及被设置成邻近所述玻璃芯层的第二主表面的第二图案化导电层。所述封装还包括导电通孔,所述导电通孔设置在所述玻璃芯层中并且在所述玻璃芯层的所述第一主表面与所述第二主表面之间延伸,其中,所述导电通孔被电连接至所述第一图案化导电层和所述第二图案化导电层中的至少一个。所述管芯被电连接至所述第一图案化导电层和第二图案化导电层中的至少一个。

在另一方面,本公开提供一种形成集成电路封装的方法。所述方法包括:通过玻璃芯层在所述玻璃芯层的第一主表面与第二主表面之间设置腔;将载体层设置在所述玻璃芯层上、在所述腔上方;以及将管芯设置在所述玻璃芯层的所述腔内。所述方法进一步包括:将介电层设置在所述玻璃芯层的第一主表面上并且在所述腔上方,以使所述玻璃芯层位于所述介电层与所述载体层之间;将第一图案化导电层设置在所述介电层上;以及从所述玻璃芯层去除所述载体层。另外,所述方法包括邻近所述玻璃芯层的第二主表面设置第二图案化导电层,以及将所述管芯电连接至第一图案化导电层和第二图案化导电层中的至少一个。

除非另有说明,否则本文提供的所有标题都是为了方便读者,并且不应用于限制标题后面的任何文本的含义。

术语“包括”及其变型在说明书和权利要求书中出现这些术语时不具有限制性含义。这样的术语应被理解为暗示包括陈述的步骤或元件或者步骤或元件的组,但不排除任何其他步骤或元件或者步骤或元件的组。

在本申请中,诸如“一(a)”、“一(an)”和“该”之类的术语并非旨在仅指单数实体,而是包括其具体示例可用于说明的通用类别。术语“一(a)”、“一(an)”和“该”与术语“至少一个”可互换使用。列表后面的短语“至少一个”和“包括至少一个”是指列表中的任何一个项目以及列表中两个或更多个项目的任意组合。

列表后面的短语“至少一个”和“包括至少一个”是指列表中的任何一个项目以及列表中两个或更多个项目的任意组合。

如本文中所使用的,除非内容另有明确指示,否则术语“或”通常以包含“和/ 或”的含义使用。

术语“和/或”是指所列要素中的一个或全部,或所列要素中的任何两个或更多个的组合。

如本文结合测量的量所使用的,术语“约”是指如进行测量并行使与测量目的和所使用的测量设备的精度相称的仔细水平的本领域技术人员所期望的测量的量的变化。在本文中,“最多”的数字(例如,最多50)包括该数量(例如,50)。

同样在本文中,通过端点列举的数字范围包括归入该范围内的所有数字以及端点(例如,1至5包括1、1.5、2、2.75、3、3.80、4、5等)。

根据下面的详细描述,本公开的这些和其他方面将是显而易见的。但是,在任何情况下,以上发明内容都不应解释为是对所要求保护的主题的限制,该主题仅由所附权利要求书定义,可以在起诉期间进行修改。

附图说明

在整个说明书中,参考了附图,其中,相同的附图标记表示相同的元件,并且其中:

图1是集成电路封装的一个实施例的示意性截面图。

图2是图1的集成电路封装的管芯的主表面的示意性俯视图。

图3A-图3I是形成集成电路封装的一个实施例的各种截面图,其中,图3A 是芯层的示意性截面图;图3B是设置在芯层中的腔的示意性截面图;图3C是设置在芯层上的载体的示意性截面;图3D是设置在芯层的腔中的管芯的示意性截面图;图3E是设置在芯层上、在腔上方的第一介电层的示意性截面图;图3F 是从芯层去除的载体和设置在芯层上的第二介电层的示意性截面图;图3G是设置在第一介电层内的场板和第二介电层的外表面上的图案化导电层的示意性截面图;图3H是设置在第一介电层的外表面上的图案化的导电层的示意性截面图;以及图3I是设置在第二介电层的外表面上的导电垫的示意性截面图。

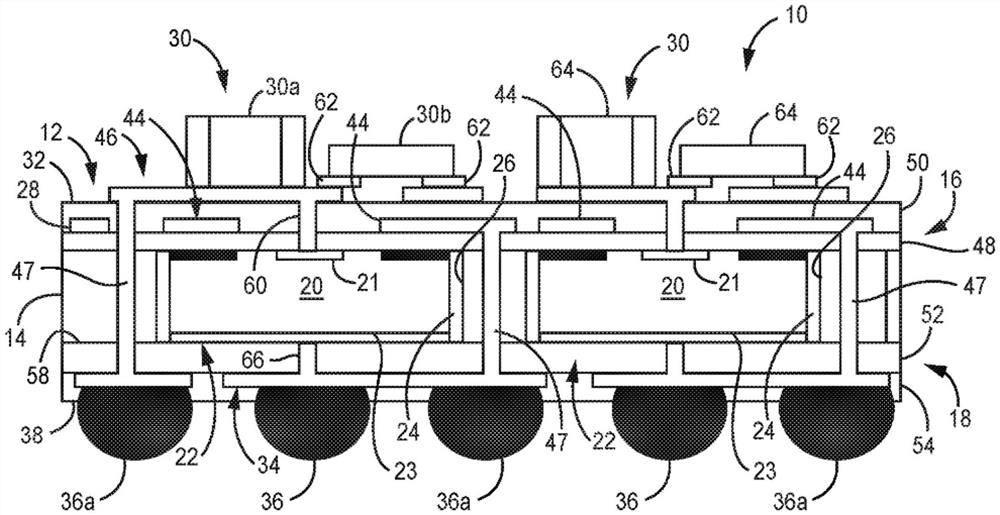

图4是包括集成电路封装的植入式医疗器件的一个实施例的示意性平面图。

图5是集成电路封装的另一实施例的示意性截面图。

具体实施方式

通常,本公开提供了集成电路封装以及形成这种封装的方法的各种实施例。所述集成电路封装可以包括衬底,所述衬底具有玻璃芯层以及设置在玻璃芯层的第一主表面与第二主表面之间的腔。设置在所述玻璃芯层的所述腔中的管芯可以被电连接至第一图案化导电层和第二图案化导电层中的至少一个,其中所述第一图案化导电层被设置成邻近所述玻璃芯层的第一主表面,并且所述第二图案化导电层被设置成邻近所述玻璃芯层的第二主表面。在一或多个实施例中,包封体可以设置在所述腔中、在所述管芯与所述腔的侧壁之间。

微电子元件(诸如半导体芯片或管芯)通常是扁平体,其电连接触头设置在外表面上,其中电连接触头被连接至元件本身的内部电路。微电子元件通常被封装以形成集成电路封装或组件,该集成电路封装或组件具有带有端子的可通过表面安装的表面,这些端子电连接到元件的内部触点。然后可以将封装或组件连接到测试装备,以确定封装的器件是否符合期望的性能标准。一旦被测试,封装可以被连接到更大的电路,例如,诸如植入式医疗器件的电子产品中的电路。用于这种微电子元件的封装或组件可以包括本文所述的集成电路封装。

集成电路封装的一个或多个实施例可以提供优于现有封装的一个或多个益处。例如,将一个或多个管芯设置在设置于集成电路封装的芯层中的腔中可以提供比现有封装更小的封装尺寸(即,高度)。此外,由于管芯可以是倒装芯片管芯(当将管芯设置在芯层的腔内时,倒装芯片管芯可以通过设置在管芯的顶表面或底表面上的一个或多个管芯触点电连接),所以可以不需要引线键合来将管芯连接到封装的图案化导电层。本文描述的用于形成这种封装的方法的各种实施例还可以在一个工艺流程中封装多个管芯和其他部件,从而降低制造这些集成电路封装的成本。在一个或多个实施例中,与封装的管芯的互连的寄生电感可以低于由引线键合产生的寄生电感。这可以使管芯以较高的频率工作,并且还可以减少切换大电流时的感应电压尖峰。此外,本文描述的封装的一个或多个实施例的总体电阻可以表现出减小的电阻损耗和增加的电流容量。此外,本文描述的一个或多个封装可以包括管芯的多个触点,以分布在封装的源极和漏极垫上方。这样的配置可以降低管芯中的电流密度,增加最大电流能力,并且降低功率损耗。这样的构造还可以允许热量通过封装的两个或更多个侧面从管芯吸收。此外,本文描述的封装的一个或多个实施例可以允许部件和集成电路封装彼此堆叠以形成三维高压堆叠结构。

芯层可以包括任何合适的一种或多种材料。在一个或多个实施例中,芯层可以是玻璃芯层。可以使用任何合适的一种或多种技术来制造这种玻璃芯层。与可用于芯层的其他类型的材料(例如,硅)相比,玻璃芯层可以提供改善的介电性能。这种改进的介电性质可以允许将一个或多个导电层直接设置在芯层上,而无需首先将介电层设置在芯层与图案化导电层之间。此外,玻璃芯层的一个或多个实施例可以表现出改善的抗翘曲性。

图1-图2是集成电路封装10的一个实施例的各种视图。集成电路封装10 包括衬底12,该衬底具有设置在第一介电层16与第二介电层18之间的芯层14。一个或多个管芯20均被设置在芯层14的腔22中。此外,包封体24设置在每个管芯22中的相应的管芯20和腔的侧壁26之间。封装10还包括设置在第一介电层16内的第一图案化导电层28。一个或多个器件30设置在第一介电层16 的外表面32上,使得第一图案化导电层28在一个或多个器件与芯层14之间。一个或多个器件30被电连接至一个或多个管芯20。封装10还包括设置在第二介电层18内的第二图案化导电层34。在一个或多个实施例中,一个或多个导电垫36可以设置在第二介电层18的外表面38上或中,使得第二图案化导电层34 在导电垫与芯层14之间。此外,在一个或多个实施例中,导电垫36中的一个或多个可以使用如本文进一步描述的任何一种或多种合适的技术被电连接至一个或多个管芯20。

衬底12可以包括任何合适的衬底。此外,衬底12可以包括任何合适的一种或多种材料,例如金属、聚合物或无机材料及其组合。在一个或多个实施例中,衬底12可以是在各种导体、通孔、管芯等之间提供电隔离的非导电或介电衬底。为了方便起见且无意进行限制,图1将衬底12描绘为整体(即,单)层。在一或多个实施例中,衬底12可以包括任何合适数量的层,其中这些层可以由相同或不同的材料形成。此外,衬底12可以具有任何合适的尺寸。例如,衬底 12可以具有在与第一介电层16的外表面32正交的方向上测量的任何合适的厚度。此外,可以使用任何适当的一种或多种技术来形成衬底12。

在一个或多个实施例中,衬底12包括设置在第一介电层16和第二介电层18之间的芯层14。芯层14可以包括任何合适的一种或多种材料,例如,本文中关于衬底12描述的相同材料。在一个或多个实施例中,芯层14可以包括玻璃、石英、蓝宝石、FR4(阻燃剂4)、陶瓷等中的一种或多种。在一个或多个实施例中,芯层14提供整个衬底12。此外,在一个或多个实施例中,可以在芯层14上设置一个或多个附加层以形成衬底12。例如,在一个或多个实施例中,可以在芯层14的一个或两个表面上设置一个或多个图案化导电层(未示出)以提供衬底12。

芯层14可以包括一个或多个腔22。可以使用任何合适的一种或多种技术在芯层14中形成腔22。在一或多个实施例中,一个或多个腔22可以完全延伸穿过芯层14。此外,在一个或多个实施例中,在正交于第一介电层16的外表面 32的方向上测量的一个或多个腔22的深度或高度可以小于芯层的厚度,使得这样的腔不穿过芯层14。每个腔22在平行于第一介电层16的外表面32的平面中可以采取任何合适的形状,例如椭圆形、矩形、多边形等。

每个腔22包括一个或多个侧壁24。每个侧壁24可以在与第一介电层16的外表面32正交的平面中(即,在图1的平面中)采取任何合适的形状。在一个或多个实施例中,侧壁24可以具有与第一介电层16的外表面32正交的平坦表面。在一个或多个实施例中,一个或多个侧壁24可以呈锥形,以使得腔22的横截面积在正交于第一介电层16的外表面32的方向上变化。此外,在一个或多个实施例中,一个或多个侧壁24可以包括一个或多个弯曲部分。

腔24可以具有任何合适的尺寸。在一个或多个实施例中,至少一个腔24 可以在平行于第一介电层16的外表面32的方向上具有大于设置在腔中的管芯 20的宽度的宽度。在一个或多个实施例中,腔24的宽度可以等于设置在其中的管芯20的宽度,使得管芯与腔的侧壁24的一个或多个部分接触。

第一介电层16和第二介电层18可以包括任何合适的一种或多种材料,例如,聚酰亚胺、双马来酰亚胺三嗪、聚苯并恶唑、光致抗蚀剂、玻璃、石英、蓝宝石等。在一个或多个实施例中,第一介电层16和第二介电层18中的至少一个包括电绝缘材料。此外,第一介电层16和第二介电层18可以具有任何合适的尺寸。在一个或多个实施例中,第一介电层16和第二介电层18中的至少一个可以包括两个或更多个层或子层,并且每个子层可以包括相同或不同的材料。例如,第一介电层16包括第一子层48和第二子层50。此外,第二介电层 18包括第一子层52和第二子层54。第一介电层16的第一子层48和第二子层 50可以使用任何合适的一种或多种技术设置在一起。在一个或多个实施例中,第一子层48和第二子层50可以被层压在一起以形成第一介电层16。类似地,第二介电层18的第一子层52和第二子层54可以使用任何合适的一种或多种技术设置在一起。在一个或多个实施例中,第一子层52和第二子层54可以被层压在一起以形成第二介电层18。尽管描绘为每个包括两个子层,但是第一介电层16和第二介电层18均可以包括任何合适数量的子层。

可以使用任何合适的一种或多种技术来形成第一介电层16和第二介电层18。在一个或多个实施例中,第一介电层16和第二介电层18中的至少一个可以被形成在衬底12上。在一个或多个实施例中,第一介电层16和第二介电层18中的至少一个可以分开形成,然后例如通过将第一介电层和第二介电层中的一个或两个层压到衬底而被连接至衬底12。

如本文所述,集成电路封装10可以包括一个或多个管芯20。此外,封装 10可以包括以任何合适的布置或阵列设置的任何合适数量的管芯20。在一或多个实施例中,一个或多个管芯20可以设置在芯层14的腔22中。尽管被描绘为每个腔22包括一个管芯20,但是在一个或多个实施例中,两个或更多个管芯可以被设置在单个腔内。在一个或多个实施例中,一个或多个管芯20可以设置在腔22中,使得管芯完全在腔内。例如,每个管芯20可以具有在正交于第一介电层16的外表面32的方向上测量的管芯高度,该高度不大于其中设置管芯的腔22的高度。在一或多个实施例中,一个或多个管芯20的管芯高度可以大于相应的管芯设置在其中的腔22的高度。

封装10可以包括任何合适类型的一个或多个管芯20。在一个或多个实施例中,封装10可以包括一个或多个可以在例如植入式医疗器件(例如,参见图4 的植入式医疗器件200)中使用的高压管芯。如本文所用,术语“高压管芯”是指电子部件或器件,该电子部件或器件可以在部件的任何两个电端子或触点之间以大于约50V的电势操作。这样的高压部件可以进一步在大于约100V的直流电压下工作,甚至可以进一步在大于约500V、1000V、1600V、3000V甚至更高、也许在数十倍数千伏或更高的直流电压下工作。在一或多个实施例中,封装10可以包括一个或多个低压管芯。在一个或多个实施例中,一个或多个管芯 20可以包括一个或多个场效应晶体管(FET)、金属氧化物半导体(MOS)、 MOSFET、绝缘栅双极结晶体管(IGBT)、晶闸管、双极晶体管、二极管、MOS 控制晶闸管、电阻器、电容器等。尽管图1的管芯20被图示为在同一平面上,但是在一个或多个实施例中,管芯可以以堆叠关系进行布置。

在一个或多个实施例中,一个或多个管芯20可以包括设置在管芯的主表面42上的场终止结构40(图2)。在一个或多个实施例中,主表面42面对场板44 (图1),场板可以被电连接至第一图案化导电层28、第二图案化导电层34、和设置在第二介电层18的外表面38上或中的导电垫36中的至少一个如本文进一步所述。

场终止结构40可以包括使用任何合适的一种或多种材料制造的任何合适的一种导体或多种导体。此外,场终止结构40可以包括适于至少部分地控制管芯 20内的电场传播以减轻或防止雪崩击穿的任何合适的结构。例如,在一个或多个实施例中,场终止结构40可以包括台面型结构。当超过管芯材料(例如硅) 的临界电场时,可能会发生此类击穿。在一个或多个实施例中,场终止结构40 可以在N型衬底中包括一个或多个浮动P型环。P型环可以占据管芯20的外表面42处的体积,并且可以导致管芯的N型材料中的耗尽区在电场可能最大的管芯表面上扩展得更远。这些P型环占据的体积可能会迫使管芯20的N型衬底中的耗尽区在外表面42处和管芯内部扩展到更大的面积和距离(因为电荷平衡需要被维持以用于主反向偏置P-N结)。这些P型环可以以一种方式间隔开,以在整个表面42上以及在管芯20内提供相对一致的电场。如图2所示,场终止结构40可以包括一个或多个环,所述一个或多个环可以以任何合适的形状或图案设置在管芯20的外表面42上。

可以使用任何合适的一种或多种技术将管芯20电连接至第一图案化导电层 28、第二图案化导电层34、第三图案化导电层46和一个或多个导电垫36中的至少一个。在一个或多个实施例中,可以通过第一介电层16的第一子层48设置一个或多个通孔60,以将管芯20的一个或多个顶部接触件21电连接至第一图案化导电层28。此外,在一个或多个实施例中,可以通过第二介电层18的第一子层52设置一个或多个通孔66,以将管芯20的一个或多个底部接触件23电连接至第二图案化导电层34。

设置在芯层14的一个或多个腔22内的还有包封体24。包封体24可以设置在腔22的任何合适的一个或多个部分中。在一或多个实施例中,包封体24设置在腔22中、在管芯20与腔的侧壁26的一个或多个部分之间。包封体24可以包括任何合适的一种或多种材料,例如UV固化型或热固化型包封材料,例如BCB、聚苯并二恶唑、环氧树脂、光致抗蚀剂以及环氧树脂,诸如日本信越化学株式会社(Shin-Etsu Chemical Co.,Ltd.)制造的SINR3170硅氧烷树脂、长濑公司(Nagase)制造的R4507 EMC(环氧模化合物)、住友公司(Sumitomo,etc) 制造的G730 EMC。可以利用任何合适的一种或多种技术将包封体24设置在腔内。在一个或多个实施例中,第一介电层16的一部分可以形成包封体24,如本文中进一步描述的。包封体24可以适于将管芯20至少部分地包封在腔22内,使得管芯保留在腔中。

如本文中提到的,可以使用任何合适的一种或多种技术将包封体24设置在腔22中、在管芯20与腔的侧壁26之间。在一个或多个实施例中,包封体24 可以包括第一介电层16的一部分。例如,管芯20可以设置在腔22内,并且第一介电层16可以通过例如将第一介电层层压到芯层而设置在芯层14(或衬底 12)上。在层压过程期间,第一介电层16的一部分可以流入腔22中、管芯20 与腔的侧壁26之间,使得该部分至少部分地将管芯包封在腔内。在第一介电层 16包括子层的一个或多个实施例中,设置在芯层(或衬底12)上的第一子层48的一个或多个部分可以流入腔22中以形成包封体24。

设置在第一介电层16内的是第一图案化导电层28。第一介电层16可以包括设置在第一介电层上或内的任何合适数量的图案化导电层。在一个或多个实施例中,第一介电层16可以包括设置在第一介电层16的外表面32上的第三图案化导电层46。此外,第一图案化导电层28和第三图案化导电层46可以包括任何合适类型的一个或多个导电层,例如一个或多个重新分布层。可以使用设置在第一介电层16内的一个或多个导电通孔47将第一图案化导电层28和第三图案化导电层46电连接至另外的图案化导电层、器件、导电垫等。第一图案化导电层28和第三图案化导电层46可以包括任何合适的一种或多种导电材料,并且可以使用本文中进一步描述的任何合适的一种或多种技术来形成。此外,可以使用任何合适的一种或多种技术将第一图案化导电层28和第三图案化导电层46设置在第一介电层16内或上。

第一图案化导电层28可以设置在第一介电层16内的任何合适位置。在一个或多个实施例中,第一图案化导电层28可以设置在第一介电层16的第一子层48与第二子层50之间。

此外,第二图案化导电层34设置在第二介电层18内。第二图案化导电层 34可以包括任何合适的图案化导电层,例如,关于第一图案化导电层28描述的相同的图案化导电层。第二介电层18可以包括设置在第二介电层内或上的任何合适数量的图案化导电层。在一个或多个实施例中,第二图案化导电层34可以设置在第二介电层18的第一子层52与第二子层54之间。第二图案化导电层34 可以通过通孔66电连接至管芯20中的至少一个、通过通孔47电连接至第一图案化导电层28、通过通孔47电连接至第三图案化导电层46和电连接到一个或多个导电垫36。

一个或多个器件30设置在第一介电层16的外表面32上。集成电路封装10 可以包括任何合适数量的器件30。此外,集成电路封装10可以包括任何合适的器件,例如,电容器、电阻器、无源集成电容器系统、逻辑电路、模拟电路等中的至少一个。一个或多个器件30可以设置在第一介电层16的外表面32上,使得第一图案化导电层28位于器件与芯层14之间。

可以使用任何合适的一种或多种技术将器件30中的一个或多个电连接至管芯20中的一个或多个。例如,在图1所示的实施例中,第一器件30a和第二器件30b通过第三图案化导电层46和穿过第一介电层16设置的通孔60电连接至管芯20。可以使用任何合适的一种或多种技术将器件30a、30b电连接至第三图案化导电层46。在一个或多个实施例中,器件30的一个或多个器件触点62可以电连接至第三图案化导电层46。器件触点62可以相对于第三图案化导电层 46设置在任何合适的位置。例如,在一个或多个实施例中,器件触点62可以设置在器件30与第三图案化导电层46之间。在一个或多个实施例中,一个或多个器件触点62可以设置在器件30的顶表面64上,并且引线键合至第三图案化导电层46(未示出)。

在第二介电层18的外表面54上设置一个或多个导电垫36。导电垫36可以设置在第二介电层18上或中的任何合适位置。此外,集成电路封装10可以包括任何合适数量的导电垫36。导电垫36可以包括任何合适类型的电连接器,例如焊球、焊料、凸块、铜柱、具有焊帽的铜柱、导电聚合物、顺应性互连件等。在一个或多个实施例中,导电垫36被设置为使得第二图案化导电层34位于导电垫与芯层14之间。此外,在一个或多个实施例中,一个或多个导电垫36被电连接至一个或多个管芯30。例如,如图I所示,导电垫36通过从第二图案化导电层34延伸至管芯的通孔66被电连接至管芯20。在一个或多个实施例中,一个或多个导电垫36可以被电连接至第二图案化导电层34、一个或多个管芯 20、第一图案化导电层28、第三图案化导电层46和一个或多个器件30中的至少一者。此外,在一个或多个实施例中,可以使用任何合适的一种或多种技术将一个或多个导电垫36电连接至一个或多个场板44。

场板44可以在任何合适的位置设置在集成电路封装10上或内部。在图1 所示的实施例中,场板44设置在第一介电层16内,使得场板中的一个或多个与管芯20中的一个或多个间隔开。场板44可以包括第一图案化导电层28的一部分,或者与第一图案化导电层分离。在一个或多个实施例中,场板44中的一个或多个可以与第一图案化导电层28同时形成。场板44可以包括任何合适的场板,例如在授予Boone等人的标题为“RECONSTITUTED WAFERPACKAGE WITH HIGH VOLTAGE DISCRETE ACTIVE DICE AND INTEGRATED FIELD PLATE FORHIGH TEMPERATURE LEAKAGE CURRENT STABILITY(具有高压离散有源骰子和集成场板的用于高温泄漏电流稳定性的重构晶片封装)”的美国专利No.8,664,756中描述的场板。

在一个或多个实施例中,场板44与管芯20以最佳间隔间隙间隔开,该最佳间隔间隙足够大以防止绝缘体的介电击穿,但是足够接近以建立足够强的场来控制系统。可以基于第一介电层16的介电材料的特性以及管芯20的测试和/ 或操作条件来确定用于间隔的最佳距离。在一个或多个实施例中,所考虑的特性可以包括封装10的操作条件,包括诸如关于第一介电层16的介电材料的击穿特性的操作电压和温度之类的条件。在一个或多个实施例中,场板44与管芯 20之间的间隔间隙的距离可替代地或另外地基于用于形成第一介电层16的材料的介电强度来确定。在一个或多个实施例中,取决于给定部件的操作和/或测试参数,该间隔间隙可以为至少约25μm至不大于约300μm。间隔间隙的设计和选择中的控制因素是场板44将有效直至管芯20的最大击穿强度,以防止在室温和更高温度下场效应泄漏。例如,旨在125℃下以80%的额定电压工作的1000 V MOSFET可以具有场板44,该场板与场终止结构40间隔开50至200μm范围内的距离。作为另一个示例,约50μm至约75pm的间距可以防止介电击穿,并且确保在高温泄漏电流测试期间在以其额定1600V的80%和高达150℃的温度下操作的管芯的电流稳定性。结果,对于给定的介电材料,部件或管芯的额定电压越高,需要在管芯20与场板44之间的间距间隙越大,以防止介电击穿并且确保泄漏电流的稳定性并消除或基本防止室温下的场效应泄漏。此外,将场板44定位在第一介电层16内可以允许独立于场板44的间距要求来确定各个导电垫36的尺寸。

在一个或多个实施例中,场板44的至少一部分在正交于第一介电层16的外表面32的方向上与管芯20的场终止结构40重叠。在一个或多个实施例中,场板44基本上与场终止结构40重叠,即,场板的大部分表面积与场终止结构的大部分表面积重叠。作为实施例的说明,包括大部分的比例可以是51%或75%或85%或98%或这些百分比内的任何变体。在一或多个实施例中,场板44的表面积可以延伸超过场终止结构40的表面积。在一个或多个实施例中,场板44 的尺寸可以被确定为与管芯20的前侧面的表面积基本共同延伸。在一或多个实施例中,场板44的尺寸可以基于场终止结构40的平面表面积来确定。这样,场板44具有至少为场终止结构40的表面积的尺寸的表面积。在一个或多个实施例中,如果存在多个同心的场终止结构40,则场板44可以形成在相应的多个单独的场板中,每个场板具有其各自场终止结构的表面积,或者可以形成为单个场板其表面积近似于包括同心终端环的整个环形圈的表面积。在场板44的表面积基于场终止结构40的尺寸来确定尺寸的实施例中,场板的表面积可以与场终止结构的表面积共同延伸和/或可以延伸超过场终止结构的表面积。另外,场板44与场终止结构40对准或直接定位在场终止结构上方或大体在相同的竖直平面中。

在一或多个实施例中,场板44可以适于接收偏置电压以在管芯20与场板之间产生电场。偏置电压的大小可以至少与施加到管芯20的偏置电压的大小一样大,其中电压具有相同的极性。例如,对于具有N型衬底的封装10,将正偏置电压施加到场板44,并且该正偏置电压的大小至少可以与施加到管芯20的最大正偏置电压的大小一样大。类似地,对于具有p型衬底的封装10,将负偏置电压施加到场板44,并且该负偏置电压的大小至少可以与施加到管芯20的最大负偏置电压的大小一样大。如果部件具有单向阻挡特性,诸如MOSFET和二极管,则场板44可以直接连接至管芯20的端子。在管芯20具有双向阻挡的一个或多个实施例中,例如晶闸管,可以切换场板44上的电压。无论哪种情况,场板44以促进大多数载流子在场终止结构40处的轻掺杂表面区域的表面积累的极性偏置。

场板44可以被电连接至设置在第二介电层18的外表面38上的一个或多个第二导电垫36a。场板44可以使用任何合适的一种或多种技术被连接至第二导电垫36a。在一个或多个实施例中,场板44可以通过在第一介电层16与第二介电层18之间延伸的通孔47被电连接至第二导电垫36a。

如本文所述,集成电路封装的一个或多个实施例可以包括玻璃芯层。例如,图5是集成电路封装300的另一实施例的示意性截面图

封装300包括衬底302,该衬底包括玻璃芯层304,该玻璃芯层包括第一主表面306、第二主表面308以及设置在玻璃芯层的第一主表面与第二主表面之间的腔310。封装300进一步包括设置在玻璃芯层304的腔310中的管芯312,以及设置在管芯与腔的侧壁316之间的腔中的包封体314。第一图案化导电层318 可以设置成邻近玻璃芯层304的第一主表面306。如本文中所使用的,术语“邻近第一主表面”是指元件或部件被设置为相比距玻璃芯层的第二主表面308更靠近玻璃芯层304的第一主表面306。封装300进一步包括设置成邻近玻璃芯层 304的第二主表面308的第二图案化导电层320。如本文中所使用的,术语“邻近第二主表面”是指元件或部件被设置为相比距玻璃芯层的第一主表面306更靠近玻璃芯层304的第二主表面308。封装300还包括设置在玻璃芯层304中的一个或多个导电通孔322,所述一个或多个通孔在玻璃芯层的第一主表面306与第二主表面308之间延伸。在一个或多个实施例中,导电通孔322可以被电连接至第一图案化导电层318和第二图案化导电层320中的至少一个。此外,管芯 312使用任何合适的一种或多种技术被电连接至第一图案化导电层318和第二图案化导电层320中的至少一个。在一个或多个实施例中,管芯312被电连接至第一图案化导电层318和第二图案化导电层320中的每个。

在一个或多个实施例中,封装300可以包括设置在第一图案化导电层318 和第二图案化导电层320中的至少一个上的一个或多个器件(未示出)。这样的一个或多个器件可以包括任何合适的器件,例如图1的封装10的器件30。一个或多个器件可以使用任何合适的一种或多种技术被电连接至第一图案化导电层 318和第二图案化导电层320中的至少一个。

邻近玻璃芯层304的第一主表面306设置的是第一图案化导电层318。在一个或多个实施例中,第一图案化导电层318可以被直接设置在玻璃芯层304的第一主表面306上。在一个或多个实施例中,介电层324可以设置在第一图案化导电层318与玻璃芯层304的第一主表面306之间。介电层324可以包括任何合适的一个或多个介电层,例如,图1的封装10的第一介电层16。介电层 324可以使用任何合适的一种或多种技术被设置在玻璃芯层304的第一主表面 306上,例如介电层可以被层压到玻璃芯层。

此外,第二图案化导电层320可以被直接设置在玻璃芯层304的第二主表面318上。在一个或多个实施例中,第二介电层(例如,封装10的第二介电层 18)可以设置在第二图案化导电层320与玻璃芯层304的第二主表面308之间。第二介电层320可以使用任何合适的一种或多种技术被设置在玻璃芯层304的第二主表面308上,例如第二介电层可以被层压到玻璃芯层。

设置在管芯312与腔310的侧壁316之间的是包封体314。包封体314可以包括适合于包封管芯的任何合适的一种或多种材料,例如本文中关于图I的封装 10的包封体24所描述的相同材料。在一个或多个实施例中,包封体314可以包括如本文关于封装10的第一介电层16所描述的介电层324的一个或多个部分。

设置在玻璃芯层304的腔310内的管芯312可以包括任何合适的器件或电路,例如本文关于封装10的管芯20描述的相同的器件或电路。在一或多个实施例中,管芯312可以包括高压电气部件。在一或多个实施例中,管芯312可以包括低压部件。

可以利用任何合适的一种或多种技术来形成图1至图2的集成电路封装10 以及图5的集成电路封装300。例如,图3A-图3I是形成集成电路封装10的方法100的一个实施例的各种示意性截面图。尽管参考图1至图2的集成电路封装10进行了描述,但是方法100可以用于形成任何合适的集成电路封装。此外,方法100被示出为包括一个管芯20;然而,该方法可以用于形成包括两个或更多个管芯的集成电路封装。在一或多个实施例中,方法100可以用于同时利用一个或多个晶片来形成两个或更多个集成电路封装10。

在图3A中,提供芯层14。在一个或多个实施例中,一个或多个附加层可以设置在芯层14的一个或两个主表面上以提供衬底12。如图3B中所示,可以使用任何合适的一种或多种技术,例如钻孔、激光钻孔、化学蚀刻、等离子蚀刻、冲压等,在芯层14中形成一个或多个腔22。此外,可使用任何合适的一种或多种技术来形成一个或多个通孔47。例如,在一个或多个实施例中,可以使用任何合适的一种或多种技术来形成开口,并且可以将导电材料设置在开口内以形成导电通孔47。在一或多个实施例中,可以在已形成图案化导电层28、34、46(如果包括的话)之后形成通孔47。

在图3C中,载体层102可以设置在芯层14的底表面104上并且在腔22上方。载体层102可以包括任何合适的载体或传输体。在一个或多个实施例中,可以在载体层102与芯层14的底表面104之间设置合适的释放层(未示出)。此外,可选的玻璃层(未示出)可以设置在载体层102上,使得载体层在可选的玻璃层与芯层14之间。这种可选的玻璃层可以在集成电路封装10的处理期间为芯层14提供额外的支撑。

管芯20可以使用任何适当的一种或多种技术设置在图3D中的腔22内。在腔22完全延伸通过芯层14的实施例中,管芯20可以直接放置在载体层102或释放层上,所述释放层设置在载体层上。

在图3E中,第一介电层16可以设置在芯层14上并且在腔22上方,使得芯层可以使用任何合适的一种或多种技术在第一介电层16与载体层102之间。在第一介电层16包括子层的实施例中,第一子层48可以如图3E所示设置在芯层16上。在一个或多个实施例中,第一介电层16的第一子层48可以设置在芯层14上,使得第一子层的一部分或多个部分流入腔中,以在腔的侧壁26与管芯20之间提供包封体24。在一个或多个实施例中,第一介电层16(或第一介电层的第一子层48)可以被层压到芯层14。

如图3F所示,载体层102可以使用任何合适的一种或多种技术来去除。此外,第二介电层18可以使用任何合适的一种或多种技术被设置在芯层14上,例如第二介电层或第二介电层的子层可以被层压到芯层上。在第二介电层18包括两个或更多个子层的实施例中,第一子层52可以设置在芯层14上。

在图3G中,第一图案化导电层28可以使用任何合适的一种或多种技术设置在第一介电层16的第一子层48上或内。例如,在一个或多个实施例中,连续导电层可以设置在第一子层48上,并且连续导电层然后可以使用任何合适的一种或多种技术(例如光刻胶施加、光刻、化学镀、电镀、化学蚀刻、干法蚀刻、物理气相沉积等)进行图案化。在一个或多个实施例中,场板44可以使用任何合适的一种或多种技术设置在第一介电层16内,使得场板与管芯20间隔开。在一个或多个实施例中,第一图案化导电层28可包括场板44。

此外,第二图案化导电层34可以使用任何合适的一种或多种技术,例如用于形成第一图案化导电层28的相同技术而被设置在第二介电层18的第一子层 52上。在形成第一图案化导电层28和第二图案化导电层34之前,可以通过第一子层48设置一个或多个通孔60,使得第一图案化导电层28被电连接至管芯 20。此外,可以通过第二介电层18的第一子层52形成一个或多个通孔66,使得第二图案化导电层34被电连接至管芯20。可以利用任何合适的技术来形成通孔60、66。此外,通孔47可以使用任何合适的一种或多种技术延伸通过第一介电层16的第一子层48并且被电连接至第一图案化导电层28。通孔47也可以使用任何合适的一种或多种技术延伸通过第二介电层18的第一子层52。

在图3H中,第一介电层16的第二子层50可以使用任何合适的一种或多种技术设置在第一图案化导电层28和第一子层48上。在一个或多个实施例中,第二子层50可以设置在整个第一图案化导电层28上方。第三图案化导电层46 可以使用任何合适的一种或多种技术,例如用于形成第一图案化导电层28的相同技术被设置在第二子层50上。此外,可以使用任何合适的一种或多种技术在第一介电层的外表面32和管芯20之间延伸穿过第一介电层16的通孔60,使得管芯被电连接至第三图案化导电层46。在一个或多个实施例中,通孔47可以延伸通过第一介电层16的第二子层40,使得第三图案化导电层46被电连接至第一图案化导电层28和第二图案化导电层34。

此外,如图3H所示,第二介电层18的第二子层54可以使用任何合适的一种或多种技术设置在第二介电层的第一子层52上。第二子层54可以设置在第二图案化导电层34和第二介电层18的第一子层52的一个或多个部分上方。在一个或多个实施例中,集成电路封装10不包括第二子层54。

在图3I中,一个或多个导电垫36可以使用任何合适的一种或多种技术设置在第二介电层18上或中。在一个或多个实施例中,一个或多个导电垫36可以被电连接至第一图案化导电层28、管芯20、第二图案化导电层34、第三图案化导电层46和一个或多个器件30中的至少一者(图1)。尽管被示出为至少部分地设置在第二子层54内,但是导电垫36可以设置在第二子层的外表面38上。

本文描述的集成电路封装的各种实施例可以在任何合适的电子系统中使用。例如,本文描述的集成电路封装的一个或多个实施例可以用于IMD、ICD、IPG、插入式心脏监护仪、植入式诊断监护仪、深部脑刺激器、植入式神经刺激器、可注射神经刺激器、植入式心室辅助器件等。图4是植入式医疗器件(IMD) 200的一个实施例的示意性平面图。IMD 200包括壳体202和设置在壳体内的电子部件204。电子部件204可以包括任何合适的电子器件,例如电容器、电阻器、无源集成电容器系统、逻辑电路、模拟电路、晶体、加速度计、RF电路、天线、变压器、连接器等中的至少一种。在一个或多个实施例,电子部件204包括集成电路封装206。封装206可以包括任何合适的集成电路封装,例如图1至图2 的集成电路封装10以及图5的封装300。集成电路封装206可以使用任何适当的一种或多种技术被电连接至其他电子部件204。电源208也设置在IMD的壳体202内,该电源使用任何合适的一种或多种技术被电连接至电子部件。电源可以包括任何合适的电源或电源的组合,例如一个或多个电池、电容器、电感耦合能量器件、光伏器件、β伏打器件、α伏打器件和热电器件。

根据本公开的方面的示例方法包括以下。

示例1:一种形成集成电路封装的方法,所述方法包括:通过玻璃芯层、在所述玻璃芯层的第一主表面与第二主表面之间设置腔;将所述载体层设置在所述玻璃芯层上、在所述腔上方;将管芯设置在所述玻璃芯层的腔内;将介电层设置在所述玻璃芯层的第一主表面上并且在所述腔上方,使得所述玻璃芯层在所述介电层与所述载体层之间;将第一图案化导电层设置在所述介电层上;从所述玻璃芯层去除所述载体层;邻近所述玻璃芯层的第二主表面设置第二图案化导电层;将所述管芯电连接至所述第一图案化导电层和所述第二图案化导电层中的至少一个上。

示例2:根据示例1的方法,进一步包括:通过所述玻璃芯层设置导电通孔,使得其在所述玻璃芯层的第一主表面与第二主表面之间延伸。

示例3:根据示例1或2所述的方法,其中,将所述介电层设置在所述玻璃芯层的第一主表面上并且在所述腔上方进一步包括:将所述介电层的至少一部分设置在所述腔中、在所述管芯与所述腔的侧壁之间。

示例4:根据示例1至3中的任一项的方法,进一步包括:将器件设置在所述第一图案化导电层上,其中所述器件通过在第一图案化导电层与所述管芯之间延伸的通孔被电连接至所述管芯。

示例5:根据示例1至4中的任一项的方法,进一步包括:将第二介电层设置在所述第二图案化导电层与玻璃芯层的第二主表面之间。

示例6:根据示例1至5中的任一项所述的方法,其中,所述管芯被电连接至所述第一图案化导电层和第二图案化导电层中的每一个。

实施例7:根据实施例1至6中的任一项的方法,其进一步包括:在将所述管芯设置在所述玻璃芯层的腔中之前,将玻璃层设置在所述载体层上,使得所述载体层位于所述玻璃层与玻璃芯层之间。

本文引用的所有参考文献和出版物均通过引用而明确地将其整体并入本公开,除非它们可能直接与本公开矛盾。讨论了本公开的例示性实施方式,并且已经参考了在本公开的范围内的可能的变型。在不脱离本公开的范围的情况下,本公开中的这些和其他变型和修改对于本领域技术人员将是显而易见的,并且应当理解,本公开不限于本文阐述的例示性实施方式。因此,本公开仅由下面提供的权利要求限制。

- 集成电路封装及其形成方法、晶圆级集成电路封装结构

- 集成电路封装件及其形成方法