SiC半导体衬底及其制造方法和制造装置

文献发布时间:2023-06-19 12:07:15

技术领域

本发明涉及一种具有台阶高度被控制的生长层的SiC半导体衬底及其制造方法和制造装置。

背景技术

SiC(碳化硅)半导体装置由于与Si(硅)和GaAs(砷化镓)半导体装置相比能够实现高耐压和高效率、高温动作,因而正在面向产业化进行开发。

通常,在相对于装置制造中使用的(0001)具有微小倾斜的SiC衬底的表面处形成有台阶-平台结构。以往在SiC衬底的表面控制中,被视为问题的是,在装置制造过程中台阶聚簇(bunching),导致形成台阶聚簇。

已知该台阶聚簇对SiC半导体装置的特性产生不良影响。具体地,分别已知存在以下情况:(1)当在形成有台阶聚簇的表面处进行外延生长时,在外延生长层(以下称为外延层)的表面处发生由台阶聚簇引起的缺陷;(2)在通过在外延层的表面处形成氧化膜而制造的MOSFET等SiC半导体装置中,台阶聚簇的存在对动作性能和可靠性产生致命的影响。

针对这种问题,已提出了各种用于抑制台阶聚簇的发生的技术。例如,在专利文献1中记载了这样的技术:在化学气相淀积(CVD:Chemical Vapor Deposition)法中,将SiC外延生长所需的量的SiH

现有技术文献

专利文献

专利文献1:日本特开2013-34007号公报

发明内容

发明要解决的问题

另外,当上述(1)和(2)的台阶聚簇的问题进一步加剧时,期望的是控制在SiC衬底的表面处形成的台阶高度并提供对装置制造优选的表面。即,如果控制台阶高度,则可以有助于在外延生长和氧化膜形成中解决由台阶-平台结构引起的问题,结果可以提高装置的动作性能和可靠性。

然而,尽管认为专利文献1记载的技术可以抑制台阶聚簇的发生,但是该技术并非能够控制SiC衬底的表面的台阶高度的生长方法。

本发明的目的是提供一种具有台阶高度被控制的生长层的SiC半导体衬底及其制造方法及其制造装置。

用于解决问题的手段

为了解决上述问题,本发明的一种实施方式的SiC半导体衬底的制造方法包括用于使SiC衬底在SiC-Si平衡蒸气压环境下生长的生长步骤。

这样,通过使SiC衬底在SiC-Si平衡蒸气压环境下生长,可以提供生长层的台阶高度被控制的SiC半导体衬底。

在该方式中,所述生长步骤在通过Si蒸气压空间被排气的原料供给空间内配置所述SiC衬底并使其生长。

这样,由于原料供给空间通过Si蒸气压空间被排气(抽真空),因而可以长时间保持原料供给空间内的SiC-Si平衡蒸气压环境。

所述配置步骤配置Si原子供给源和C原子供给源并进行生长,以使所述原料供给空间内的原子数比Si/C超过1。

通过以这样的原子数比Si/C配置Si原子供给源和C原子供给源,可以在原料供给空间内容易地形成SiC-Si平衡蒸气压环境。

在该方式中,所述生长步骤在1600℃以上的温度进行。

通过在这样的温度区进行生长,可以使SiC衬底高速生长。

此外,本发明还涉及一种SiC半导体衬底。即,本发明的一实施方式的SiC半导体衬底包括排列有一个单位晶格高度的台阶。

这样,由于排列有一个单位晶格高度的台阶,因而可以有助于解决在外延生长时发生由台阶聚簇引起的缺陷的问题、MOSFET等中的由台阶-平台结构引起的问题等,结果可以提高动作性能和可靠性。

在该方式中,其特征在于,所述生长层是4H-SiC。

此外,本发明还涉及上述的SiC半导体衬底的制造装置。即,本发明的一实施方式的SiC半导体衬底的制造装置包括:原料供给空间,用于向SiC衬底供给Si原子和C原子并使其生长;Si蒸气压空间,形成有Si蒸气压环境;和高温真空炉,能够加热所述原料供给空间,其中,所述原料供给空间通过所述Si蒸气压空间被排气。

这样,由于原料供给空间通过Si蒸气压空间被排气(抽真空),因而可以在原料供给空间内长时间保持对生长优选的原子数比Si/C。

在该方式中,所述原料供给空间具有Si原子供给源和C原子供给源,并且所述Si原子供给源和所述C原子供给源配置成使所述原料供给空间内的原子数比Si/C超过1。

通过采用这样的结构,可以在原料供给空间内形成SiC-Si平衡蒸气压环境。

在该方式中,在所述原料供给空间内设置有温度向着所述SiC衬底下降的温度梯度。

通过这样的温度梯度设置,可以将Si原子和C原子输送到SiC衬底,并且可以提高生长速度。

在该方式中,包括:原料容器,具有所述原料供给空间;和浸碳容器,具有所述Si蒸气压空间。

在该方式中,所述高温真空炉具有:主加热室,能够加热所述原料供给空间;预加热室,连接到所述主加热室;以及移动装置,用于使所述原料供给空间移动,其中,所述移动装置构成为能够在所述主加热室和所述预加热室之间移动。

这样,通过采用能够使原料供给空间从主加热室移到预加热室的结构,能够使SiC衬底急速升温和降温。

此外,本发明还涉及一种用于减少SiC半导体衬底的基底面位错的方法。即,本发明的一种实施方式的一种用于减少SiC半导体衬底的基底面位错的方法是用于使一个单位晶格高度的台阶排列在SiC半导体衬底的表面处的方法,在包括用于使SiC衬底生长的生长步骤的SiC半导体衬底的制造方法中,包括用于使SiC衬底在SiC-Si平衡蒸气压环境下生长的生长步骤。

在该方式中,所述生长步骤配置Si原子供给源和C原子供给源并进行生长以使原料供给空间内的原子数比Si/C超过1。

发明的效果

根据所公开的技术,可以提供一种具有台阶高度被控制的生长层的SiC半导体衬底及其制造方法及其制造装置。

其他问题、特征和优点将通过在结合附图和权利要求书时阅读以下描述的用于实施本发明的方式而变得显而易见。

附图说明

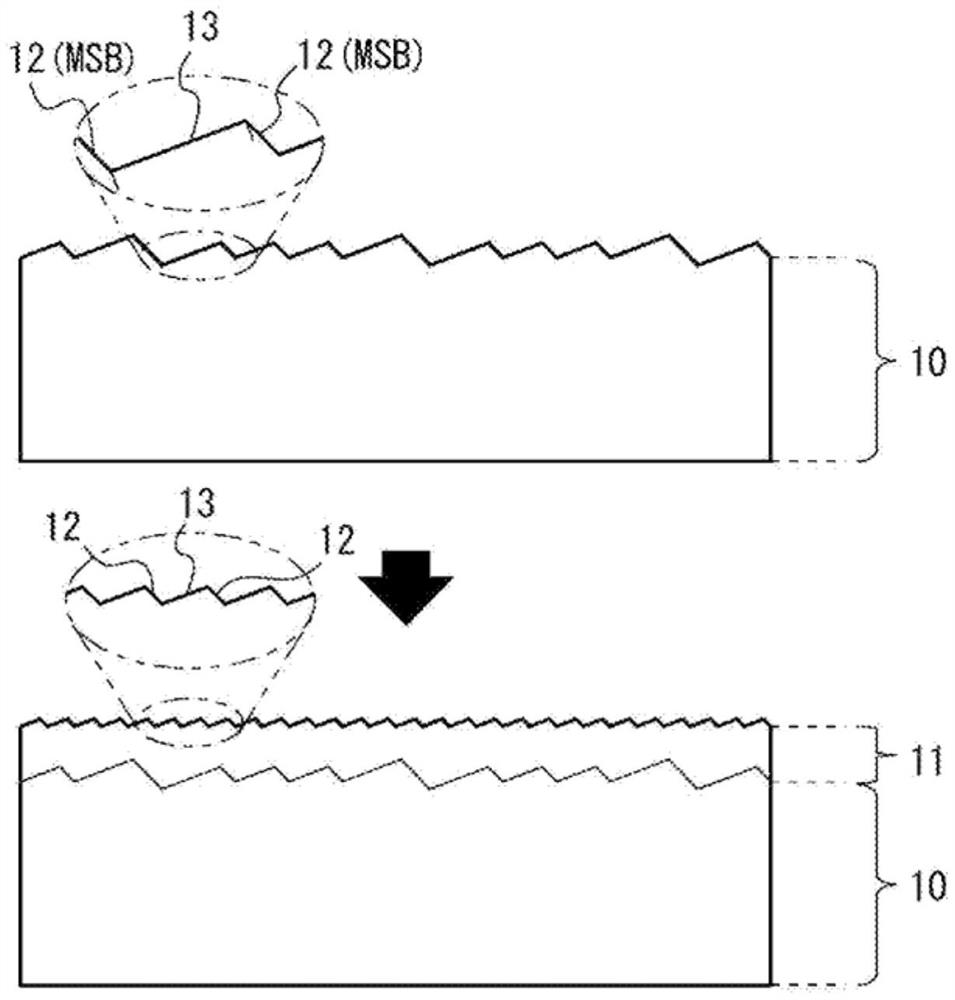

图1是一实施方式的SiC半导体衬底的制造方法的生长步骤的说明图。

图2是一实施方式的SiC半导体衬底的制造方法的生长步骤的说明图。

图3是一实施方式的SiC半导体衬底的制造方法的生长步骤的说明图。

图4是在一实施方式的SiC半导体衬底的制造方法中使用的高温真空炉的示意图。

图5是在一实施方式的SiC半导体衬底的制造方法的实施例1中观察到的SiC衬底表面的SEM图像。

图6是在一实施方式的SiC半导体衬底的制造方法的比较例1中观察到的SiC衬底表面的SEM图像。

图7是说明一实施方式的SiC半导体衬底的制造方法的生长步骤的生长条件的曲线图。

具体实施方式

以下,使用图1~图7对附图示出的优选的一实施方式进行详细说明。本发明的技术范围不限于附图所示的实施方式,并且能够在权利要求书记载的范围内适当改变。

[SiC半导体衬底的制造方法]

以下,对本发明的一实施方式的SiC半导体衬底的制造方法进行详细说明。

根据本发明的SiC半导体衬底的制造方法包括用于使SiC衬底10在SiC-Si平衡蒸气压环境下生长的生长步骤。这样,通过使SiC衬底10在SiC-Si平衡蒸气压环境下生长,可以制造具有生长层11的SiC半导体衬底,该生长层11中台阶12的高度被控制。

作为SiC衬底10,可以使用任何多型体的(polytype)SiC衬底。作为SiC半导体装置的衬底,使用从通过升华法等制造的体单晶加工而成的SiC衬底10。

在本说明书中的说明中,将SiC衬底10的用于生成半导体元件的面(具体地,用于沉积生长层11的面)称为主面,并且将与该主面相对的面称为背面。此外,将主面和背面统称为表面。

另外,作为主面,可以例示从(0001)面或(000-1)面设定了数度(例如0.4至8°)的偏离角的表面。(另外,在本说明书中,在米勒指数的表示法中,“-”是表示附于紧随其后的指数的短划)。

在以原子能级进行了平坦化的SiC衬底10的表面处确认了台阶-平台结构。该台阶-平台结构成为将一个分子层以上的台阶部位即台阶12和{0001}面露出的平坦部位即平台13交替排列而成的阶梯结构。

在台阶12中,一个分子层(0.25nm)为最小高度(最小单位),并且该1个分子层重叠多层,从而形成各种台阶高度。在本说明书中的说明中,将台阶12聚簇(bunching)而巨大化并且具有超过各多型体一个单位晶格的高度的台阶称为宏台阶聚簇(MSB:Macro StepBunching)。

即,MSB在4H-SiC的情况下是超过4个分子层(5个分子层以上)聚簇而成的台阶12,并且在6H-SiC的情况下是超过6个分子层(7个分子层以上)聚簇而成的台阶12。

由于在外延层的表面处发生由MSB引起的缺陷,并且该MSB是阻碍MOSFET的氧化膜的可靠性的因素之一,因而期望的是,在SiC衬底10的表面处不形成该MSB。

<生长步骤>

根据本发明的实施方式的生长步骤通过在SiC-Si平衡蒸气压环境下进行生长,可以在形成有MSB的SiC衬底10上使未形成有MSB的生长层11生长(参照图1)。

在该生长步骤中,可以采用升华法。升华法是将原料和SiC衬底10配置在原料供给空间S1(生长空间)内并加热来将从原料升华的原料气体输送到SiC衬底10上以进行再结晶和生长的方法。

即,在原料供给空间S1内,除了SiC衬底10之外,还配置有成为原料的Si原子的供给源和C原子的供给源,并且通过加热它们,将成为SiC衬底10的原料的Si原子和C原子供给到原料供给空间S1内。由于该Si原子和C原子被输送到SiC衬底10的表面并进行再结晶,因而形成生长层11。

此外,在根据本发明的实施方式的生长步骤中,期望的是,在通过Si蒸气压空间S2被排气(抽真空)的原料供给空间S1内配置有SiC衬底10。即,期望的是,如图2的(a)所示,在具有Si蒸气压空间S2的浸碳容器30内配置有具有原料供给空间S1的原料容器20,并且在该原料容器20内进一步配置有SiC衬底10。

原料容器20包括上容器21和能够与该上容器21嵌合的下容器22,并且在该容器内具有用于使SiC衬底10生长的原料供给空间S1。此时,在上容器21和下容器22的嵌合部处形成有微小的间隙23,并且从该间隙23将原料容器20内部进行排气(抽真空)。

作为Si原子供给源和C原子供给源,可以采用Si衬底等的能够供给Si原子的材料、石墨等的能够供给C原子的材料、SiC衬底等的能够供给Si原子和C原子的材料。此外,通过用多晶SiC(Poly-SiC)形成原料容器20的至少一部分,可以将原料容器20本身用作Si原子供给源和C原子供给源。

图2的(a)示出了采用多晶SiC制成的原料容器20、并且原料供给空间S1内配置有Si衬底24的形式。在该情况下,该形式为:原料容器20和Si衬底24将Si原子供给到原料供给空间S1内,并且原料容器20供给C原子。

Si原子供给源和C原子供给源的配置不限于该形式,只要是能够将Si原子和C原子供给到原料供给空间S1内的形式即可。例如,原料容器20既可以采用多晶SiC以外的材料,也可以采用在原料供给空间S1内配置Si材料、C材料、SiC材料的形式。

另外,在原料使用多晶SiC的情况下,可以将多晶SiC(原料)与单晶SiC(SiC衬底10)之间的蒸气压差(化学势差)用作生长驱动力。

此外,期望的是,在原料供给空间S1内设置有温度向着SiC衬底10下降的温度梯度。利用该温度梯度作为生长驱动力,引起Si原子和C原子向SiC衬底10的输送,因而生长层13的生长速度上升。

而且,为了使Si原子和C原子高效率地到达SiC衬底10,也可以使Si原子供给源和C原子供给源接近SiC衬底10。在图2(a)中示出了将成为Si原子供给源和C原子供给源的多晶SiC制的上容器21与SiC衬底10平行接近配置的形式。

该SiC衬底10的主面与上容器31的顶面之间的距离L优选设定在0.5~20mm的范围,更优选设定在0.7~10mm的范围。

在该距离L为0.5mm以上的情况下,SiC衬底10的主面与上容器31的顶面之间的温度差变大。结果,生长驱动力变大,并且生长速度增大。

另一方面,在距离L为20mm以下的情况下,原料与衬底之间的距离变近,有效地进行原料气体的输送,并且生长速度增大。

此外,如图2的(a)所示,原料容器20配置在形成有Si蒸气压环境的Si蒸气压空间S2内。这样,在Si蒸气压空间S2内配置有原料供给空间S1,并且通过Si蒸气压环境的空间将原料容器20内部进行排气(抽真空),从而可以抑制Si原子从原料供给空间S1内减少。由此,可以在原料供给空间S1内长时间保持对生长优选的原子数比Si/C。

即,在从原料供给空间S1直接排气的情况下,Si原子从间隙33被排气。在该情况下,原料供给空间S1内的原子数比Si/C显著减少,从而不能保持适于生长的环境。

另一方面,当通过Si蒸气压环境的Si蒸气压空间S2将原料容器20内部进行排气的情况下,可以抑制Si原子从原料供给空间S1被排气并保持原料供给空间S1内的原子数比Si/C。

Si蒸气压力空间S2只要在加热时形成有Si蒸气压环境即可,例如可以使用浸碳容器30来形成Si蒸气压环境。

该浸碳容器30只要是能够将原料容器20收纳在Si蒸气压空间S2内的形式即可,例如包括上容器31和能够与该上容器31嵌合的下容器32。该浸碳容器30与原料容器20一样,在上容器31和下容器32的嵌合部处形成有微小的间隙33,并且从该间隙23进行排气(抽真空)。

该浸碳容器30的内壁表面由多层构成,并且从Si蒸气压空间S2内部侧向外部侧依次具有硅化钽层(TaSi

这样,由于从内侧形成有硅化钽层、碳化钽层、钽层,因而可以将存在于Si蒸气压空间S2内的C原子引入(浸碳)到浸碳容器30自身内。此外,硅化钽层通过加热将Si原子供给到浸碳容器30的Si蒸气压空间S2。结果,可以在加热时使Si蒸气压空间S2内部处于高纯度的Si蒸气压环境(Si气氛)。

另外,只要能够引入C原子并在Si蒸气压空间S2中形成Si蒸气压环境,就可以用作浸碳容器30。

此外,期望的是,原料容器20和浸碳容器30形成为能够收纳6英寸晶片或8英寸晶片的直径。

图2的(b)是示出生长机构的概要的说明图。通过将配置有SiC衬底10的原料供给空间S1在1400℃以上且2300℃以下的温度范围内加热,持续进行以下1)~5)的反应,结果认为进行了生长。

1)Poly-SiC(s)→Si(v)+C(s)

2)2C(s)+Si(v)→SiC

3)C(s)+2Si(v)→Si

4)Si(v)+SiC

5)Si

1)的说明:由于原料容器20(Poly-SiC(s))被加热,因而Si原子(Si(v))通过热分解从SiC脱离。

2)和3)的说明:由于Si原子(Si(v))脱离而留下的C(C(s))与通过原料供给空间S1内的Si蒸气(Si(v))反应,成为Si

4)和5)的说明:所升华的Si

根据本发明的实施方式的生长步骤中的生长环境的特征在于是SiC-Si平衡蒸气压环境。以下,对SiC-Si平衡蒸气压环境和SiC-C平衡蒸气压环境进行详细说明。另外,本说明书中的SiC-Si平衡蒸气压环境和SiC-C平衡蒸气压环境包括满足从理论热平衡环境导出的生长速度和生长温度之间的关系的近热平衡蒸气压环境。

SiC-Si平衡蒸气压环境是指SiC(固相)、Si(液相)和气相的三相处于平衡状态时的蒸气压环境。

换句话说,本说明书中的“SiC-Si蒸气压环境”是指当SiC(固相)和Si(液相)通过气相处于相平衡状态时的蒸气压环境。

SiC-Si平衡蒸气压环境例如是通过对原子数比Si/C超过1的准闭锁空间进行热处理而形成的。具体地,当在满足化学计量比1∶1的SiC制的原料容器20内配置了满足化学计量比1∶1的SiC衬底10和Si蒸气供给源(Si衬底、Si粒料等)的情况下,原料容器20内的原子数比Si/C超过1。

另外,本说明书中的“准闭锁空间”是指容器内能够抽真空、但能够将容器内产生的蒸气的至少一部分封入的空间。该准闭锁空间可以形成在原料容器20内或浸碳容器30内。

此外,SiC-C平衡蒸气压环境是指SiC(固相)、C(固相)和气相的三相处于平衡状态时的蒸气压环境。

换句话说,本说明书中的“SiC-C平衡蒸气压环境”是指当SiC(固相)和C(固相)通过气相处于相平衡状态时的蒸气压环境。

SiC-C平衡蒸气压环境例如是通过对原子数比Si/C为1以下的准闭锁空间进行热处理而形成的。具体地,当在满足化学计量比1∶1的SiC制的原料容器20内配置了满足化学计量比1∶1的SiC衬底10的情况下,原料容器20内的原子数比Si/C为1。此外,也可以配置C蒸气供给源(C粒料等)以使原子数比Si/C为1以下。

SiC-Si平衡蒸气压环境的气相中的原子数比Si/C大于SiC-C平衡蒸气压环境的气相中的原子数比Si/C。

在本方法中,在SiC原料与SiC衬底之间的蒸气压环境成为SiC-Si平衡蒸气压环境的条件下,将多晶SiC(SiC原料)与单晶SiC(SiC衬底10)之间的蒸气压差(化学势差)或温度梯度用作生长驱动力,使SiC衬底10生长。

在此,在将SiC原料与SiC衬底之间的蒸气压差设定为生长量的情况下,可以通过以下的式1求出SiC的生长速度。

[式1]

在此,T为SiC原料侧的温度,m

此外,P

该SiC-Si平衡蒸气压环境可以通过配置Si原子供给源和C原子供给源并进行加热以使原料供给空间S1内的原子数比Si/C超过1来形成。

以下,对形成SiC-Si平衡蒸气压环境的原料供给空间S1的配置进行详细说明。

在本方法中,SiC-Si平衡蒸气压环境可以通过配置Si原子供给源和C原子供给源以使原料供给空间S1内的原子数比Si/C超过1来形成。而SiC-C平衡蒸气压环境通过配置成使原料供给空间S1内的原子数比Si/C为1以下来形成。

即,通过在加热之前将Si原子供给源比C原子供给源更多地配置在原料供给空间S1内,可以在原料供给空间S1内形成SiC-Si平衡蒸气压环境。

另外,作为Si原子供给源示出了Si衬底24,但只要是供给Si原子以使原料供给空间S1内的原子数比Si/C上升的材料,就当然可以采用。

另一方面,SiC-C平衡蒸气压环境可以通过配置Si原子供给源和C原子供给源并进行加热以使原料供给空间S1内的原子数比Si/C为1以下来形成。

图3的(a)示出了在SiC制的原料容器20内仅配置了SiC衬底10的形式。

本方法中的加热温度优选设定在1400~2200℃的范围内,更优选设定在1600~2000℃的范围内。

在图2和图3的形式中,从Si原子供给源和C原子供给源产生与加热温度相对应的Si原子和C原子的平衡蒸气压,并且充满原料供给空间S1内部。

本方法中的生长速度可以根据上述温度范围来控制,并且能够在0.001~1μm/min的范围内选择。

本方法中的生长量优选为5~15μm,更优选为8~10μm。

本方法中的生长时间可以设定为任意时间以达到期望的生长量。例如,当生长速度为10nm/min时,在要将生长量设定为10μm的情况下,生长时间只要100分钟即可。

本方法中的真空度(主加热室41)为10

在本方法中,还能够在生长中导入惰性气体。该惰性气体可以选择Ar等,并且通过在10

根据本发明的SiC半导体衬底的制造方法,包括用于使SiC衬底10在SiC-Si平衡蒸气压环境下生长的生长步骤。这样,通过使SiC衬底在SiC-Si平衡蒸气压环境下生长,可以使排列有一个单位晶格高度的台阶12的生长层11生长。

此外,根据本发明的SiC半导体衬底的制造方法,在通过Si蒸气压空间S2被排气(抽真空)的原料供给空间S1内配置SiC衬底10并使其生长。这样,原料供给空间S1由于通过Si蒸气压空间S2被排气,因而可以长时间保持原料供给空间S1内的SiC-Si平衡蒸气压环境。

另外,在图1中示出了对不具有作为耐压层的外延层的SiC衬底10实施了根据本发明的生长步骤的示例,但当然也可以对具有作为耐压层的外延层的SiC衬底10实施根据本发明的生长步骤。

此外,本发明是这样的方法:在包括用于使SiC衬底生长的生长步骤的SiC半导体衬底的制造方法中,通过使SiC衬底在SiC-Si平衡蒸气压环境下生长,使一个单位晶格高度的台阶排列在SiC半导体衬底的表面处。

此外,SiC-Si平衡蒸气压环境例如是通过配置Si原子供给源和C原子供给源以使原料供给空间内的原子数比Si/C超过1来形成的。

[SiC半导体衬底]

本发明的一实施方式的SiC半导体衬底的特征在于包括排列有一个单位晶格高度的台阶12的生长层11。如图5所示,在4H-SiC(0001)面侧生长的生长层11的表面沿<11-20>方向在100μm以上的范围内未形成有MSB,并且1nm(一个单位晶格)高度的台阶12以14nm的平台13宽度排列。另外,该台阶高度和平台宽度可以使用原子间力显微镜(AFM)或日本特开2015-179082号公报记载的扫描型电子显微镜(SEM)图像对比度评价方法来确认。

这样通过具有使台阶12的高度被控制为一个单位晶格的生长层11,当在生长层11上形成作为耐压层的外延层的情况下,可以抑制在外延层表面发生由台阶聚簇引起的缺陷。

此外,在将生长层11设定为耐压层的情况下,不会发生在MOSFET中由台阶-平台结构引起的问题,结果,可以提高动作性能和可靠性。即,可以有助于形成优选的氧化物绝缘膜。

[SiC半导体衬底的制造装置]

以下,参照图4对根据本发明的SiC半导体衬底的制造装置进行详细说明。根据本实施方式的制造装置包括:具有Si蒸气压空间S2的浸碳容器30;具有原料供给空间S1的原料容器20;以及能够加热原料供给空间S1的高温真空炉40。另外,在相同实施方式中,对与上述的SiC半导体衬底及其制造方法基本相同的构成要素赋予相同的附图标记并且简化其说明。

图4是在根据本发明的SiC半导体衬底的制造方法的生长步骤中使用的高温真空炉40(SiC半导体衬底的制造装置)的一例。

该高温真空炉40包括:主加热室41;预加热室42;以及能够将浸碳容器30从预加热室42移动到主加热室41的移动装置43(移动台)。主加热室41可以将SiC衬底10加热到1000℃以上且2300℃以下的温度。预加热室42是用于在利用主加热室41加热SiC衬底10之前对其进行预加热的空间。

主加热室41连接有真空形成用阀44、惰性气体注入用阀45和真空计46。真空形成用阀44与用于对主加热室41内部进行排气并抽真空的抽真空泵连接,并且可以调整主加热室41内的真空度。此外,惰性气体注入用阀45可以将惰性气体(例如,Ar等)导入到主加热室41内并调整其压力。真空计46可以测量主加热室41内的真空度。

此外,在主加热室41的内部配备有加热器47。而且,在主加热室41的侧壁和顶板处固定有热反射金属板(未图示),并且该热反射金属板构成为将加热器47的热量朝主加热室41的大致中央部反射。

由此,可以将SiC衬底10加热并升温到1000℃以上且2300℃以下的温度。另外,作为加热器47,例如可以使用电阻加热式的加热器或高频感应加热式的加热器。

预加热室42与主加热室41连接,并且构成为能够通过移动装置43移动浸碳容器20。由此,原料供给空间S1从主加热室41被输送到预加热室42,或者从预加热室42被输送到主加热室41。

另外,该预加热室42未设置有主加热室41那样的加热器47,并且利用主加热室41的余热来升温。例如,在主加热室41为2000℃的情况下,预加热室42构成为升温到约1000℃,并且可以进行浸碳容器20等的除气处理。

此外,由于主加热室41与预加热室42之间的输送通过移动装置43在最短约1分钟内完成,因而可以实现以1~1000℃/min的升温/降温。由于可以这样进行急速升温和急速降温,因而可以观察到在升温中和降温中不具有低温生长历史的表面形状,这在现有装置中是难以实现的。

此外,在图5中,在主加热室41的下方处配置有预加热室42,但不限于此,可以在任意的方向设置。

移动装置43是配置浸碳容器30的台,并且从与该浸碳容器30的接触部散发微小的热量。由此,在浸碳容器30内或在原料供给空间S1内产生温度梯度,该温度梯度成为SiC衬底10的生长驱动力。如图5所示,在从下方支撑浸碳容器30的情况下,设置温度梯度使得温度向着浸碳容器30的底面方向(自上而下)下降。

另外,该温度梯度可以通过改变移动装置43的设计而在任意方向上设置,例如,在移动装置43采用悬挂式等的情况下,热量向上方散发,因而温度梯度设置为温度向着浸碳容器30的顶面方向(自下而上)下降的少许的温度梯度。

根据本发明,包括:用于在通过Si蒸气压空间S2被排气(抽真空)的原料供给空间S1内配置SiC衬底10的配置步骤;和用于使SiC衬底10在SiC-Si平衡蒸气压环境下生长的生长步骤。

这样,用于使SiC衬底10生长的原料供给空间S1通过Si蒸气压空间S2被排气(抽真空),从而可以抑制原料供给空间S1内的Si原子被排气,将原料供给空间S1内的原子数比Si/C保持在适于生长的比率。

而且,通过使SiC衬底10在SiC-Si平衡蒸气压环境下生长,可以抑制在SiC衬底10的表面处形成MSB。此时,即使在SiC衬底10处存在“晶格无序层”的情况下,也可以抑制形成MSB。

实施例

通过以下方法制造实施例1和比较例1的SiC半导体衬底。

<实施例1>

(配置步骤)

在以下条件下,将SiC衬底10配置在原料供给空间S1和Si蒸气压空间S2内(参照图2的(a))。

[SiC衬底10]

多型体:4H-SiC

偏离方向和偏离角:<11-20>方向偏离4°

生长面:(0001)面

衬底尺寸:横宽10mm×纵宽10mm×厚度0.3mm

晶格无序层:5μm

另外,晶格无序层的深度通过SEM-EBSD确认。也可以通过TEM和μXRD确认。

[原料供给空间S1]

原料容器20材料:多晶SiC

原料容器20尺寸:直径60mm×高度4mm

这样通过将Si衬底24配置在原料容器20内,将原料供给空间S1内的原子数比Si/C设定为超过1(SiC-Si平衡蒸气压环境)。

[Si蒸气压空间S2]

浸碳容器30的硅化钽层:TaSi

浸碳容器30的碳化钽层:TaC或Ta

浸碳容器30的钽层:Ta

浸碳容器30尺寸:直径160mm×高度60mm

(生长步骤)

使在上述条件下配置的SiC衬底10在以下条件下生长。

升温速度:10℃/min

加热温度:1800℃

加热时间:60min

生长速度:68nm/min

主加热室真空度:10

降温速度:1000℃/min

图5是在上述条件下生长的实施例1的SiC衬底10的表面的SEM图像。图5的(a)是以倍率×1000观察到的SEM图像,图5的(b)是以倍率×100000观察到的SEM图像。

在本实施例1的SiC衬底10的表面处未形成MSB,并且1.0nm(全单位晶格)的台阶12以14nm的平台13宽度有规则地排列。另外,台阶12的高度通过AFM来测量。

此外,如本实施例1那样能够抑制台阶12的高度的生长环境从加热温度与生长速度之间的关系可知为SiC-Si平衡蒸气压环境(参照图7)。

<比较例1>

(配置步骤)

在以下条件下,将SiC衬底10配置在原料供给空间S1和Si蒸气压空间S2内(参照图3的(a))。

[SiC衬底10]

使用与实施例1相同的SiC衬底10。

[原料供给空间S1]

使用与实施例1相同的原料容器20。未配置Si衬底24,并且在原料容器20内仅配置SiC衬底10。结果,原料供给空间S1内的原子数比Si/C被设定为1以下(SiC-C平衡蒸气压环境)。

[Si蒸气压空间S2]

使用与实施例1相同的浸碳容器30。

(生长步骤)

使在上述条件下配置的SiC衬底10在与实施例1相同的条件下生长。

图6是在上述条件下生长的比较例1的SiC衬底10的表面的SEM图像。图6的(a)是以倍率为×1000观察到的SEM图像,图6的(b)是以倍率为×100000观察到的SEM图像。

在该比较例1的SiC衬底10的表面处形成有台阶端为锯齿形状的MSB,并且高度3nm的台阶12以平均42nm的台阶13的宽度排列。另外,台阶12的高度通过AFM来测定。

此外,如本比较例1那样形成有MSB的生长环境从加热温度与生长速度之间的关系可知为SiC-C平衡蒸气压环境(参照图7)。

图7是示出通过根据本发明的SiC半导体衬底的制造方法进行生长得到的加热温度与生长速度之间的关系的曲线图。该曲线图的横轴是温度的倒数,并且该曲线图的纵轴是生长速度的对数表示。将原料供给空间S1内的原子数比Si/C设定为超过1(参照图2的(a))并进行生长得到的结果由○标记表示,并且将原料供给空间S1内的原子数比Si/C设定为1或小于1(参照图3的(a))并进行生长得到的结果由×标记表示。○标记部位的SiC衬底10的表面均未形成MSB,并且台阶12是一个单位晶格的高度。另一方面,×标记部位的SiC衬底10的表面均形成有MSB。

此外,在图7的曲线图中,SiC-Si平衡蒸气压环境中的SiC衬底生长的热力学计算结果由虚线(阿累尼乌斯图)表示,并且SiC-C平衡蒸气压环境中的SiC衬底生长的热力学计算结果由双点划线(阿累尼乌斯图)表示。

即,虚线是在SiC(固相)、Si(液相)和气相的三相处于平衡状态的蒸气压环境中以多晶SiC为原料使单晶SiC生长时的热力学计算结果。具体地,使用式1在以下的条件(i)~(iv)下进行热力学计算。(i)是体积恒定的SiC+Si系;(ii)生长驱动力是原料供给空间S1内的温度梯度和多晶SiC与单晶SiC之间的蒸气压差(化学势差);(iii)原料气体为SiC、Si

此外,双点划线是在SiC(固相)、C(固相)和气相的三相处于平衡状态的蒸气压环境中以多晶SiC为原料使单晶SiC生长时的热力学计算结果。具体地,使用式1在以下的条件(i)~(iv)下进行热力学计算。(i)是体积恒定的SiC+C系;(ii)生长驱动力是原料供给空间S1内的温度梯度和多晶SiC与单晶SiC之间的蒸气压差(化学势差);(iii)原料气体为SiC、Si

另外,在热力学计算中使用的各化学种类的数据采用JANAF热化学表的值。

结果,在使SiC衬底10在SiC-Si平衡蒸气压环境下生长的图7的○标记部位的条件下,可以看出,MSB的形成被分解并被抑制,并且在生长层11的表面处排列有1nm(1个单位晶格)高度的台阶12。

另一方面,在使SiC衬底10在SiC-C平衡蒸气压环境下生长的图7的×标记部位的条件下,可以看出,形成有MSB。

根据本发明的SiC半导体衬底的制造方法,通过包括用于使SiC衬底10在SiC-Si平衡蒸气压环境下生长的生长步骤,可以使排列有一个单位晶格高度的台阶12的生长层11生长。

附图标记说明

10 SiC衬底 11 生长层

12 台阶 13 平台

20 原料容器 24 Si衬底

25 C原子吸藏部件 30 浸碳容器

40 高温真空炉 41 主加热室

42 预加热室 43 移动装置

S1 原料供给空间 S2 Si蒸气压空间

MSB 宏台阶聚簇

- SiC半导体衬底及其制造方法和制造装置

- SiC外延晶圆、SiC外延晶圆的制造装置、SiC外延晶圆的制造方法及半导体装置