用于模数转换器失调校准的动态比较器及方法

文献发布时间:2023-06-19 10:00:31

技术领域

本发明属于模拟集成电路技术领域,具体涉及一种用于模数转换器失调校准的动态比较器及方法。

背景技术

现实世界中,信号大多为连续的模拟量,而在信号处理领域,数字信号具有抗干扰能力强、加密性强,更易处理等特点。所以在信号处理过程中,一般会将模拟信号转化为数字信号;将信号在数字领域上进行各类处理。因此在信号处理系统中,需要模数转化器将实际的模拟信号进行采样、量化、编码转化为数字信号,再通过相应的处理系统进行数字信号处理。所以模数转化器是现在信号处理系统中一个重要功能模块。

用于模数转换器(包括逐次逼近寄存器模数转换器)失调校准的动态比较器(简称比较器)是模数转换器内部的一个关键的电路,为了保证模数转换器的各项性能指标,比较器的性能至关重要。目前,大部分模数转换器使用传统的两级比较器,包括预放大电路和锁存电路。传统的两级比较器所存在的主要缺陷是噪声大,而降低其噪声又往往需要增大输出节点的电容负载,从而导致芯片面积的增大,进而影响模数转换器的总体性能。

发明内容

本发明的目的旨在克服上述现有技术的缺陷,该目的是通过下述技术方案实现的:

一种用于模数转换器失调校准的动态比较器,包括依次相连的一级预放大器、二级预放大器、三级预放大器、四级预放大器和锁存器;

一级预放大器的输入端分别与输入信号开关和第一开关的一端连接,输入信号开关的另一端与输入信号连接,第一开关的另一端与共模信号连接;一级预放大器的输出端与第一校准电容的上级板连接;

二级预放大器的输入端分别与第二开关的一端和第一校准电容的下级板连接,第二开关的另一端与共模信号连接;二级预放大器的输出端与第二校准电容的上级板连接;

三级预放大器的输入端分别与第三开关的一端和第二校准电容的下级板连接,第三开关的另一端与共模信号连接;三级预放大器的输出端与第三校准电容的上级板连接;

四级预放大器的输入端分别与第四开关的一端和第三校准电容的下级板连接,第四开关的另一端与共模信号连接;四级预放大器的输出端与锁存器的输入端连接,锁存器的输出端与方向器连接。

在上述技术方案的基础上,本发明可附加下述技术手段,以便更好地或者更有针对性地实现本发明的目的:

所述一级、二级、三级、四级预放大器均具有相同的电路结构,每级预放大器均包括第一金属氧化物半导体管、第二金属氧化物半导体管、第三金属氧化物半导体管、第四金属氧化物半导体管、第五金属氧化物半导体管、第六金属氧化物半导体管。

进一步地,所述第一金属氧化物半导体管、第二金属氧化物半导体管组成差分输入对管;第一金属氧化物半导体管、第二金属氧化物半导体管的漏极与电源连接;第一金属氧化物半导体管的栅极分别与正差分输入信号连接,第二金属氧化物半导体管的栅极与负差分输入信号连接;第一金属氧化物半导体管的源极与第四金属氧化物半导体管的漏极连接,第二金属氧化物半导体管的源极与第五金属氧化物半导体管的漏极连接。

进一步地,所述第三金属氧化物半导体管的栅极与时钟信号连接,第三金属氧化物半导体管的漏极与第一金属氧化物半导体管的源极连接,第三金属氧化物半导体管的源极与第二金属氧化物半导体管的源极连接。

进一步地,所述第四金属氧化物半导体管、第五金属氧化物半导体管的连接方式为二极管连接;第四金属氧化物半导体管的漏极与第一金属氧化物半导体管的源极连接,第五金属氧化物半导体管的漏极与第二金属氧化物半导体管的源极相连;第四金属氧化物半导体管、第五金属氧化物半导体管的栅极分别与各自的漏极连接;第四金属氧化物半导体管、第五金属氧化物半导体管的源极共同连接到第六金属氧化物半导体管的漏极;第六金属氧化物半导体管作为尾电流源产生管,其栅极与偏置电压电路连接,其源极逻辑接地。

进一步地,所述锁存器包括五个N型金属氧化物半导体管和八个P型金属氧化物半导体管;五个N型金属氧化物半导体管依次为第一N型金属氧化物半导体管、第二N型金属氧化物半导体管、第三N型金属氧化物半导体管、第四N型金属氧化物半导体管、第五N型金属氧化物半导体管;八个P型金属氧化物半导体管依次为第一P型金属氧化物半导体管、第二P型金属氧化物半导体管、第三P型金属氧化物半导体管、第四P型金属氧化物半导体管、第五P型金属氧化物半导体管、第六P型金属氧化物半导体管、第七P型金属氧化物半导体管、第八P型金属氧化物半导体管。

进一步地,所述第一N型金属氧化物半导体管、第二N型金属氧化物半导体管为输入管;第一N型金属氧化物半导体管的漏极与第四N型金属氧化物半导体管、第五P型金属氧化物半导体管的源极连接,其栅极与正差分输入信号连接;第二N型金属氧化物半导体管的漏极与第五N型金属氧化物半导体管、第六P型金属氧化物半导体管的源极连接,其栅极与负差分输入信号连接;第一N型金属氧化物半导体管、第二N型金属氧化物半导体管的源极共同连接到第三N型金属氧化物半导体管的漏极;第三N 型金属氧化物半导体管的栅极与时钟信号连接,其源极接地。

进一步地,所述第四N型金属氧化物半导体管的漏极与第一P型金属氧化物半导体管的源极、第五N型金属氧化物半导体管、第二P型金属氧化物半导体管的栅极连接,且作为负电压输出节点;第四N型金属氧化物半导体管的栅极与第一P型金属氧化物半导体管的栅极、第八P型金属氧化物半导体管的漏极连接;第四N型金属氧化物半导体管的源极与第一P型金属氧化物半导体管的漏极、第五P型金属氧化物半导体管的源极连接。

进一步地,所述第五N型金属氧化物半导体管的漏极与第二P型金属氧化物半导体管的源极、第四N型金属氧化物半导体管、第一P型金属氧化物半导体管的栅极连接,且作为正电压输出节点;第五N型金属氧化物半导体管的栅极与第二P型金属氧化物半导体管的栅极、第八P型金属氧化物半导体管的漏极连接,其源极与第二N型金属氧化物半导体管的漏极、第六P型金属氧化物半导体管的源极连接。

进一步地,所述第一P型金属氧化物半导体管的漏极与电源连接,其栅极与第四N型金属氧化物半导体管的栅极、第五N型金属氧化物半导体管的漏极、第二P型金属氧化物半导体管的源极连接,其源极与第四N型金属氧化物半导体管的漏极、第三P型金属氧化物半导体管的源极连接。

本发明还提供了一种模数转换器失调校准的动态比较器的控制方法,其通过时钟信号CLK与校准控制信号OS进行状态控制,包括失调校准阶段、复位阶段和比较阶段三个工作状态,当校准控制信号OS=1时,所述动态比较器处于失调校准阶段;当校准控制信号OS=0,且时钟信号CLK=0 时,所述动态比较器处于复位阶段,当校准控制信号OS=0,且时钟信号 CLK=1时,所述动态比较器处于比较阶段。

本发明具有下述有益效果:

通过一、二、三、四级预放大器和锁存器的协调工作,本发明具有失调电压小,噪声低、速度快的优点,从而卓有成效地实现了模数转换器的高精度、高速度设计,显著地提高了模数转换器的速度和精度。

附图说明

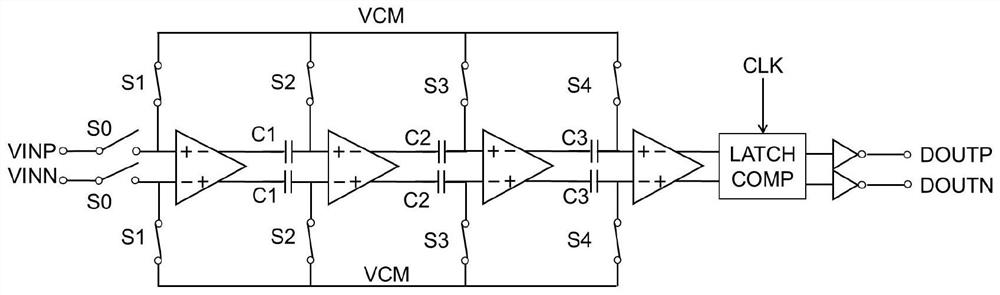

图1为本发明一个实施例的总体结构示意图;

图2为本发明一个实施例中的预放大器的电路结构示意图;

图3为本发明一个实施例中的锁存器的电路结构示意图;

图4为本发明一个实施例工作过程中的时钟信号与控制信号波形图。

具体实施方式

以下,通过一个实施例,并结合附图,详细介绍本发明的技术方案及其工作方法。

如图1所示,一种用于模数转换器失调校准的动态比较器,包括依次相连的一级预放大器、二级预放大器、三级预放大器、四级预放大器和锁存器(LATCH COMP)。

一级预放大器的输入端分别与输入信号开关S0和第一开关S1的一端连接,输入信号开关S0的另一端与输入信号连接,第一开关S1的另一端与共模信号VCM连接;一级预放大器的输出端与第一校准电容C1的上级板连接。

二级预放大器的输入端分别与第二开关S2的一端和校准电容C1的下级板连接,第二开关S2另一端与共模信号VCM连接;二级预放大器的输出端与第二校准电容C2的上级板连接。

三级预放大器的输入端分别与第三开关S3的一端和第二校准电容C2 的下级板连接,第三开关S3的另一端与共模信号VCM相连;三级预放大器的输出端与第三校准电容C3的上级板连接。

四级预放大器的输入端分别与第四开关S4的一端和第三校准电容C3 的下级板连接,第四开关S4的另一端与共模信号VCM连接;四级预放大器的输出端与锁存器(LATCHCOMP)的输入端连接,锁存器的输出端与方向器(DOUTP,DOUTN)连接。

如图2所示,在本实施例中,所述一级、二级、三级、四级预放大器均具有相同的电路结构,每级预放大器均包括六个金属氧化物半导体管 (MOS管),亦即第一金属氧化物半导体管M1、第二金属氧化物半导体管M2、第三金属氧化物半导体管M3、第四金属氧化物半导体管M4、第五金属氧化物半导体管M5、第六金属氧化物半导体管M6。

第一金属氧化物半导体管M1、第二金属氧化物半导体管M2组成差分输入对管;第一金属氧化物半导体管M1、第二金属氧化物半导体管M2 的漏极与电源VDD连接;第一金属氧化物半导体管M1的栅极与正差分输入信号VIN+连接,第二金属氧化物半导体管M2的栅极与负差分输入信号VIN-连接;第一金属氧化物半导体管M1的源极与第四金属氧化物半导体管M4的漏极连接,第二金属氧化物半导体管M2的源极与第五金属氧化物半导体管M5的漏极连接。

第三金属氧化物半导体管M3的栅极与时钟信号CLK连接,第三金属氧化物半导体管M3的漏极与第一金属氧化物半导体管M1的源极连接,第三金属氧化物半导体管M3的源极与第二金属氧化物半导体管M3的源极连接。

第四金属氧化物半导体管M4、第五金属氧化物半导体管M5的连接方式为二极管连接;第四金属氧化物半导体管M4的漏极与第一金属氧化物半导体管M1的源极连接,第五金属氧化物半导体管M5的漏极与第二金属氧化物半导体管M2的源极相连;第四金属氧化物半导体管M4、第五金属氧化物半导体管M5的栅极分别与各自的漏极连接;第四金属氧化物半导体管M4、第五金属氧化物半导体管M5的源极共同连接到第六金属氧化物半导体管M6的漏极;第六金属氧化物半导体管M6作为尾电流源产生管,其栅极与偏置电压电路VB连接,其源极逻辑接地。

如图3所示,在本实施例中,所述锁存器包括五个N型金属氧化物半导体管(NMOS管)和八个P型金属氧化物半导体管(PMOS管)。五个 N型金属氧化物半导体管依次为第一N型金属氧化物半导体管NM1、第二N型金属氧化物半导体管NM2、第三N型金属氧化物半导体管NM3、第四N型金属氧化物半导体管NM4、第五N型金属氧化物半导体管NM。八个P型金属氧化物半导体管依次为第一P型金属氧化物半导体管PM1、第二P型金属氧化物半导体管PM7、第三P型金属氧化物半导体管PM3、第四P型金属氧化物半导体管PM4、第五P型金属氧化物半导体管PM5、第六P型金属氧化物半导体管PM6、第七P型金属氧化物半导体管PM7、第八P型金属氧化物半导体管PM8。

第一N型金属氧化物半导体管NM1、第二N型金属氧化物半导体管 NM2为输入管;第一N型金属氧化物半导体管NM1的漏极与第四N型金属氧化物半导体管NM4、第五P型金属氧化物半导体管PM5的源极连接,第七P型金属氧化物半导体管PM7的源极连接,其栅极与正差分输入信号 VIN+连接;第二N型金属氧化物半导体管NM2的漏极与第五N型金属氧化物半导体管NM5、第六P型金属氧化物半导体管PM6的源极连接,且与第七P型金属氧化物半导体管PM7的漏极连接,其栅极与负差分输入信号VIN-连接(差分输入即四级预放大器的差分输出);第一N型金属氧化物半导体管NM1、第二N型金属氧化物半导体管NM2的源极共同连接到第三N型金属氧化物半导体管NM3的漏极;第三N型金属氧化物半导体管NM3的栅极与时钟信号CLK连接,其源极与地线GND连接。

第四N型金属氧化物半导体管NM4的漏极分别与第一P型金属氧化物半导体管PM1的源极、第三P型金属氧化物半导体管PM3的源极、第五N型金属氧化物半导体管NM5、第二P型金属氧化物半导体管PM2的栅极连接,且作为负电压输出节点VO-;第四N型金属氧化物半导体管NM4的栅极分别与第一P型金属氧化物半导体管PM1的栅极、第八P型金属氧化物半导体管PM8的漏极连接;第四N型金属氧化物半导体管NM4 的源极分别与第一N型金属氧化物半导体管NM1的漏极、第五P型金属氧化物半导体管PM5的源极连接。

第五N型金属氧化物半导体管NM5的漏极分别与第二P型金属氧化物半导体管PM2的源极、第四P型金属氧化物半导体管PM4的源极、第四N型金属氧化物半导体管NM4、第一P型金属氧化物半导体管PM1的栅极连接,且作为正电压输出节点VO+;第五N型金属氧化物半导体管 NM5的栅极与第二P型金属氧化物半导体管PM2的栅极、第八P型金属氧化物半导体管PM8的漏极连接,其源极与第二N型金属氧化物半导体管NM2的漏极、第六P型金属氧化物半导体管PM6的源极连接。

第一P型金属氧化物半导体管PM1的漏极与电源VDD连接,其栅极分别与第四N型金属氧化物半导体管NM4的栅极、第五N型金属氧化物半导体管的NM5漏极、第二P型金属氧化物半导体管PM2的源极连接,其源极与第四N型金属氧化物半导体管NM4的漏极、第三P型金属氧化物半导体管PM3的源极连接。

第二P型金属氧化物半导体管PM2的漏极与电源VDD连接,其栅极与第五N型金属氧化物半导体管NM5的栅极、第四N型金属氧化物半导体管NM4的漏极、第一P型金属氧化物半导体管PM1的源极连接,其源极与第五N型金属氧化物半导体管NM5的漏极、第四P型金属氧化物半导体管PM4的源极连接。

第三P型金属氧化物半导体管PM3的源极与电源VDD连接,其栅极与时钟信号电路CLK连接,其源极还与第四N型金属氧化物半导体管 NM4的漏极、第一P型金属氧化物半导体管PM1的源极连接。

第四P型金属氧化物半导体管PM4的源极与电源VDD连接,其栅极与时钟信号电路CLK连接,其源极还与第五N型金属氧化物半导体管 NM5的漏极、第二P型金属氧化物半导体管PM2的源极连接。

第五P型金属氧化物半导体管PM5的源极与电源VDD连接,其栅极与时钟信号电路CLK相连,其源极还与第一N型金属氧化物半导体管 NM1的漏极、第四N型金属氧化物半导体管NM4的源极、第七P型金属氧化物半导体管PM7的漏极连接。

第六P型金属氧化物半导体管PM6的源极与电源VDD连接,其栅极与时钟信号CLK相连,其源极还与第二N型金属氧化物半导体管NM2 的漏极、第五N型金属氧化物半导体管NM5源极、第七P型金属氧化物半导体管PM7的源极连接。

第七P型金属氧化物半导体管PM7的漏极分别与第一N型金属氧化物半导体管NM1的漏极、第五P型金属氧化物半导体管PM5的源极、第四N型金属氧化物半导体管NM4的源极连接,其栅极与第八P型金属氧化物半导体管PM8的栅极相连并接入时钟信号CLK,其源极与第二N型金属氧化物半导体管NM2的漏极、第六P型金属氧化物半导体管PM6的源极、第五N型金属氧化物半导体管NM5的源极连接。

第八P型金属氧化物半导体管PM8的漏极分别与第四N型金属氧化物半导体管NM4的栅极、第一P型金属氧化物半导体管PM1的栅极、第五N型金属氧化物半导体管NM5的漏极、第二P型金属氧化物半导体管 PM2的源极连接,其栅极与第七P型金属氧化物半导体管PM7的栅极相连并接入时钟信号CLK,其源极与第五N型金属氧化物半导体管NM5的栅极、第二P型金属氧化物半导体管PM2的栅极、第四N型金属氧化物半导体管NM4的漏极、第一P型金属氧化物半导体管PM1的源极连接。

以上,结合附图详细描述了本发明的一个实施例的结构特征,以下,进一步介绍其工作过程。

本发明用于模数转换器失调校准的动态比较器(以下简称比较器)工作时,通过时钟信号CLK与校准控制信号OS进行状态控制。比较器的工作过程基本上可分为失调校准阶段、复位阶段、比较阶段等三个主要工作状态。

在失调校准阶段,校准控制信号OS=1,此时存在两个子状态,分别为测量状态和校准状态。在测量状态中,预放大器的输入端通过开关接到共模信号VCM,第一至第三校准电容(C1-C3)的下级板也连接到共模信号VCM,此时预放大器的输出端为VOUT=A*VOS,即测试校准电容存储 A*VOS的电压。校准状态时,第一至第四开关(S1-S4)皆闭合,比较器的输入端连接到差分输入信号,此时输出电压值为VOUT=A*(VIN-VOS),经校准电容后,可得到输出电压VOUT=A*(VIN-VOS)+A*VOS)=A*VIN;进而实现失调电压校准功能,理论上可以完全消除失调电压。在进行校准电容的控制过程中,电容所连接的开关的打开时间要有一定的先后顺序,以保证比较器的正常工作。在此过程中的时钟信号与控制信号的波形如图 4所示。

复位阶段,校准控制信号OS=0,且时钟信号CLK=0时,图2中的第三金属氧化物半导体管M3断开,其他金属氧化物半导体管(MOS管)正常工作,此时整个电路结构实现了对每一级预放大器失调电压校准;此时,动态锁存器处于关闭状态,图3中的第四N型金属氧化物半导体管M4的尾电流源关闭,电路节点VO+、VO-、M+、M-通过第三至第六P型金属氧化物半导体管(PM3、PM4、PM5、PM6)等复位管充电至电源VDD电位,同时第七、第八P型金属氧化物半导体管(PM7、PM8)打开,保证电路节点M+和M-、VO+和VO-的电压平衡。

比较阶段,校准控制信号OS=0,且时钟信号CLK=1时,图2中的第三金属氧化物半导体管M3导通,其他金属氧化物半导体管(MOS管)正常工作,第四、第五金属氧化物半导体管(NM4、NM5)可视作为负载电阻,四级预放大器正常工作,对输入信号进行放大。图3所示的锁存器中的第三N型金属氧化物半导体管M3的尾电流打开,所有复位管关闭,此时,作为输入对管的第一、第二金属氧化物半导体管(NM1、NM2)开始工作。由于第一、第二金属氧化物半导体管(NM1、NM2)的栅极电压不同,导致其导通电流不同,从而导致M+和M-两点的放电速度不同,由此导致M+和M-的电位不同。若V IN+>VIN-,那么M-比M+下降的更快,因此,第四金属氧化物半导体管M4先进入导通状态,从而导致负电压输出VO-先下降。当VO-开始下降至第二P型金属氧化物半导体管 M7导通时,正电压输出VO+节点开始充电。通过第四、第五N型金属氧化物半导体管(NM4、NM5)和第一、第二P型金属氧化物半导体管(PM1、PM2)形成的反相器,最终使得负电压输出VO-下降至地线GND,正电压输出VO+充电至电源VDD,达到信息锁存的效果。

- 用于模数转换器失调校准的动态比较器及方法

- 一种应用于16位低功耗逐次逼近型模数转换器的比较器失调电压校准方法