一种半导体封装电磁屏蔽结构及其使用方法

文献发布时间:2023-06-19 11:21:00

技术领域

本发明涉及半导体封装技术领域,具体为一种半导体封装电磁屏蔽结构及其使用方法。

背景技术

在半导体片材上进行浸蚀,布线,制成的能实现某种功能的半导体器件。不只是硅芯片,常见的还包括砷化镓,锗等半导体材料,半导体器件最终是使用在PCB电路板上,通过电路板上的线路设计和半导体器件等电子元件的配置连接,可形成完整的电路架构,以提供电子设备所需要的功能,半导体器件与电路板之间是否可靠地连接决定了电子设备的功能正常与否,目前,传统半导体功率器件与电路板之间通常有通孔式和贴片式两种,在生产过程中,通孔式连接需要人工焊接,焊接效率低、成本高,且焊接过程中往往会由于人工操作不当对半导体器件造成损伤,导致产品生产良率低。而贴片式封装的半导体器件更容易实现电子设备大规模自动化生产,因此,越来越多的半导体器件采用贴片式与电路板进行连接。

现有的半导体封装结构不具有电磁屏蔽性能导致半导体芯片易受电磁影响从而造成自身损伤,少数具有电磁屏蔽性能的封装结构在使用及安装时易受到损坏从而造成电磁泄漏,同时半导体封装结构的电磁屏蔽存在一定的疏漏也可造成电磁泄漏,为此,我们提出一种半导体封装电磁屏蔽结构及其使用方法。

发明内容

本发明的目的在于提供一种半导体封装电磁屏蔽结构及其使用方法,以解决上述背景技术中提出的现有的半导体封装结构不具有电磁屏蔽性能导致半导体芯片易受电磁影响从而造成自身损伤,少数具有电磁屏蔽性能的封装结构在使用及安装时易受到损坏从而造成电磁泄漏,同时半导体封装结构的电磁屏蔽存在一定的疏漏也可造成电磁泄漏的问题。

为实现上述目的,本发明提供如下技术方案:一种半导体封装电磁屏蔽结构及其使用方法,包括基板和密封罩,所述基板的前后端设置有水平置孔,且基板的两侧设置有竖直置孔,所述基板的中部内侧设置有内容槽,且内容槽的表面中心设置有半导体芯片,所述内容槽的两侧中部设置有竖直卡槽,且竖直卡槽的两侧设置有竖直通孔,所述内容槽的前后端中部设置有水平卡槽,且水平卡槽的两侧设置有水平通孔,所述密封罩设置于半导体芯片的上方,且密封罩的内外表面涂设有炭黑层,所述密封罩的外侧前端中部设置有水平卡块,且水平卡块的两侧设置有水平缺口,所述密封罩的外部两侧中端设置有竖直卡块,且竖直卡块的两侧设置有竖直缺口,所述内容槽的下方设置有导热板,且内容槽的水平表面设置有出线槽,所述出线槽的内部设置有线路,且出线槽的外侧设置有扣条。

优选的,所述基板与内容槽之间为一体结构,且密封罩通过水平卡块与水平卡槽构成卡合结构。

优选的,所述水平卡块沿着密封罩的水平中轴线对称分布,且竖直卡块沿着密封罩的竖直中轴线对称分布。

优选的,所述密封罩与炭黑层之间紧密贴合,且密封罩的表面积与炭黑层的覆盖面相同。

优选的,所述水平置孔与水平缺口之间处于同一水平面上,且水平置孔与水平缺口之间相连通。

优选的,所述导热板包括导热金属层、氮化硅绝缘层和氧化铝绝缘层,且导热金属层的下方设置有氮化硅绝缘层,所述氮化硅绝缘层的下方设置有氧化铝绝缘层。

优选的,所述导热金属层与氮化硅绝缘层之间相粘结,且氮化硅绝缘层与氧化铝绝缘层之间相贴合。

优选的,所述内容槽通过出线槽与扣条构成卡扣结构,且内容槽与扣条之间为胶接连接。

优选的,所述其使用方法:基板的表面中部设置有内容槽,内容槽的上端与基板的表面齐平,内容槽的内侧底部四周设置有竖直卡槽和水平卡槽,将半导体芯片背面焊接在内容槽内部平面上,密封罩的外侧底部四周设置有水平卡块和竖直卡块,用于将密封罩卡合于内容槽内侧底部四周的竖直卡槽和水平卡槽中,将密封罩进行固定,密封罩的外侧涂设有炭黑层,对密封罩内部的半导体芯片进行电磁屏蔽,基板表面设置有出线槽,出线槽位于基板表面凹陷处,线路通过扣条进行限位,同时上表面通过封装树脂进行封装,线路通过竖直通孔和水平通孔穿过竖直置孔和水平置孔拉出,竖直置孔和水平置孔的孔端通过封装树脂进行封装,基板下端设置有导热板,有效的对半导体芯片及线路产生的热量进行扩散。

与现有技术相比,本发明的有益效果如下:

1、本发明通过基板、密封罩、水平卡块、水平卡槽和内容槽的设置,基板与内容槽之间为一体结构,基板与内容槽之间的一体结构增加了二者之间的稳定性,密封罩是具有一定弹性的金属片焊接而成,使用者手动捏住密封罩将其进行一定的微形变从而使得水平卡块卡至水平卡槽内部,便于将密封罩固定至内容槽内部,密封罩的上表面与基板上表面齐平,避免密封罩占用较多空间。

2、本发明通过密封罩、水平卡块和竖直卡块的设置,水平卡块沿着密封罩的水平中轴线对称分布,水平卡块设置有一组,分布在密封罩外侧底部前后端,竖直卡块设置有一组,分布在密封罩外侧底部左右侧,水平卡块与竖直卡块均和密封罩为固定连接,水平卡块与竖直卡块总体的均匀分布增加了密封罩的稳定性。

3、本发明通过密封罩、炭黑层和半导体芯片的设置,密封罩与炭黑层之间紧密贴合,炭黑层由不同极性的高聚物与炭黑混合而成,不同极性的高聚物与炭黑组成共混体系的极性越大,炭黑临界体积分数就越大,意味着体系的导电性下降,由于炭黑表面含有很强的极性基团,基体极性大,作用增强,这时强度增加,却妨碍导电粒子自身的凝集,以致导电性差,从而有效的对密封罩内部的半导体芯片进行电磁屏蔽,避免半导体芯片受电磁影响从而造成自身损伤。

4、本发明通过水平置孔、水平缺口、竖直通孔、水平通孔和线路的设置,水平置孔与水平缺口之间处于同一水平面上,使用者将线路通过竖直通孔和水平通孔穿过竖直置孔和水平置孔拉出,竖直置孔和水平置孔的孔端通过封装树脂进行封装,在便于排线的同时避免孔端存在一定的疏漏造成电磁泄漏。

5、本发明通过导热金属层、氮化硅绝缘层和氧化铝绝缘层的设置,导热金属层与氮化硅绝缘层之间相粘结,导热金属层用于对半导体芯片散发的热量进行导出扩散,氮化硅绝缘层具有较高的强度,同时可耐1200℃的高温,氧化铝绝缘层具有较强的耐火性,可以避免延烧现象的产生,使得导热板整体同时兼具导热耐火高硬度性。

附图说明

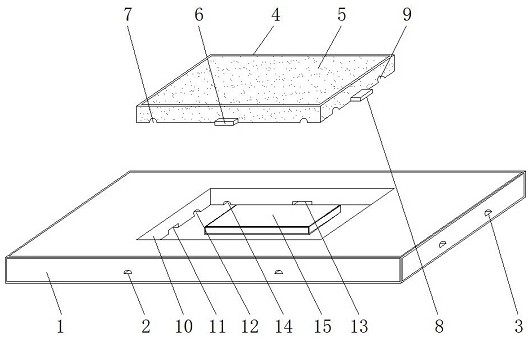

图1为本发明一种半导体封装电磁屏蔽结构及其使用方法的正视结构示意图;

图2为本发明一种半导体封装电磁屏蔽结构及其使用方法的爆炸结构示意图;

图3为本发明一种半导体封装电磁屏蔽结构及其使用方法的内部结构示意图;

图4为本发明一种半导体封装电磁屏蔽结构及其使用方法的导热板横截面结构示意图;

图5为本发明一种半导体封装电磁屏蔽结构及其使用方法的内容槽俯视结构示意图。

图中:1、基板;2、水平置孔;3、竖直置孔;4、密封罩;5、炭黑层;6、水平卡块;7、水平缺口;8、竖直卡块;9、竖直缺口;10、内容槽;11、竖直卡槽;12、竖直通孔;13、水平卡槽;14、水平通孔;15、半导体芯片;16、导热板;1601、导热金属层;1602、氮化硅绝缘层;1603、氧化铝绝缘层;17、出线槽;18、线路;19、扣条。

具体实施方式

下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

请参阅图1-5,本发明提供一种技术方案:一种半导体封装电磁屏蔽结构及其使用方法,包括基板1、水平置孔2、竖直置孔3、密封罩4、炭黑层5、水平卡块6、水平缺口7、竖直卡块8、竖直缺口9、内容槽10、竖直卡槽11、竖直通孔12、水平卡槽13、水平通孔14、半导体芯片15、导热板16、导热金属层1601、氮化硅绝缘层1602、氧化铝绝缘层1603、出线槽17、线路18和扣条19,基板1的前后端设置有水平置孔2,且基板1的两侧设置有竖直置孔3,基板1的中部内侧设置有内容槽10,且内容槽10的表面中心设置有半导体芯片15,内容槽10的两侧中部设置有竖直卡槽11,且竖直卡槽11的两侧设置有竖直通孔12,内容槽10的前后端中部设置有水平卡槽13,且水平卡槽13的两侧设置有水平通孔14,密封罩4设置于半导体芯片15的上方,且密封罩4的内外表面涂设有炭黑层5,密封罩4的外侧前端中部设置有水平卡块6,且水平卡块6的两侧设置有水平缺口7,密封罩4的外部两侧中端设置有竖直卡块8,且竖直卡块8的两侧设置有竖直缺口9,内容槽10的下方设置有导热板16,且内容槽10的水平表面设置有出线槽17,出线槽17的内部设置有线路18,且出线槽17的外侧设置有扣条19;

基板1与内容槽10之间为一体结构,且密封罩4通过水平卡块6与水平卡槽13构成卡合结构,基板1与内容槽10之间的一体结构增加了二者之间的稳定性,密封罩4是具有一定弹性的金属片焊接而成,使用者手动捏住密封罩4将其进行一定的微形变从而使得水平卡块6卡至水平卡槽13内部,便于将密封罩4固定至内容槽10内部,密封罩4的上表面与基板1上表面齐平,避免密封罩4占用较多空间;

水平卡块6沿着密封罩4的水平中轴线对称分布,且竖直卡块8沿着密封罩4的竖直中轴线对称分布,水平卡块6设置有一组,分布在密封罩4外侧底部前后端,竖直卡块8设置有一组,分布在密封罩4外侧底部左右侧,水平卡块6与竖直卡块8均和密封罩4为固定连接,水平卡块6与竖直卡块8总体的均匀分布增加了密封罩4的稳定性;

密封罩4与炭黑层5之间紧密贴合,且密封罩4的表面积与炭黑层5的覆盖面相同,炭黑层5由不同极性的高聚物与炭黑混合而成,不同极性的高聚物与炭黑组成共混体系的极性越大,炭黑临界体积分数就越大,意味着体系的导电性下降,由于炭黑表面含有很强的极性基团,基体极性大,作用增强,这时强度增加,却妨碍导电粒子自身的凝集,以致导电性差,从而有效的对密封罩4内部的半导体芯片15进行电磁屏蔽,避免半导体芯片15受电磁影响从而造成自身损伤;

水平置孔2与水平缺口7之间处于同一水平面上,且水平置孔2与水平缺口7之间相连通,使用者将线路18通过竖直通孔12和水平通孔14穿过竖直置孔3和水平置孔2拉出,竖直置孔3和水平置孔2的孔端通过封装树脂进行封装,在便于排线的同时避免孔端存在一定的疏漏造成电磁泄漏;

导热板16包括导热金属层1601、氮化硅绝缘层1602和氧化铝绝缘层1603,且导热金属层1601的下方设置有氮化硅绝缘层1602,氮化硅绝缘层1602的下方设置有氧化铝绝缘层1603,导热金属层1601与氮化硅绝缘层1602之间相粘结,且氮化硅绝缘层1602与氧化铝绝缘层1603之间相贴合,导热金属层1601用于对半导体芯片15散发的热量进行导出扩散,氮化硅绝缘层1602具有较高的强度,同时可耐1200℃的高温,氧化铝绝缘层1603具有较强的耐火性,可以避免延烧现象的产生,使得导热板16整体同时兼具导热耐火高硬度性;

内容槽10通过出线槽17与扣条19构成卡扣结构,且内容槽10与扣条19之间为胶接连接,出线槽17的设置便于线路18的排版,避免线路18混合造成线路18之间的磨损及缠绕,扣条19设置于内容槽10的上方并对内容槽10进行半包裹,对内容槽10内部的线路18进行限位,避免进行树脂封装时线路18移动造成封装误差。

本实施例的工作原理:该半导体封装电磁屏蔽结构及其使用方法,在使用时使用者先手动捏住密封罩4将其进行一定的微形变从而使得水平卡块6卡至水平卡槽13内部,密封罩4是具有一定弹性的金属片焊接而成,将密封罩4固定至内容槽10内部,密封罩4的上表面与基板1上表面齐平,避免密封罩4占用较多空间,水平卡块6设置有一组,分布在密封罩4外侧底部前后端,竖直卡块8设置有一组,分布在密封罩4外侧底部左右侧,水平卡块6与竖直卡块8均和密封罩4为固定连接,水平卡块6与竖直卡块8总体的均匀分布增加了密封罩4的稳定性,炭黑层5由不同极性的高聚物与炭黑混合而成,不同极性的高聚物与炭黑组成共混体系的极性越大,炭黑临界体积分数就越大,意味着体系的导电性下降,从而对密封罩4内部的半导体芯片15进行电磁屏蔽,避免半导体芯片15受电磁影响从而造成自身损伤,使用者将线路18通过竖直通孔12和水平通孔14穿过竖直置孔3和水平置孔2拉出,竖直置孔3和水平置孔2的孔端通过封装树脂进行封装,在便于排线的同时避免孔端存在一定的疏漏造成电磁泄漏,导热金属层1601用于对半导体芯片15散发的热量进行导出扩散,氮化硅绝缘层1602具有较高的强度,同时可耐1200℃的高温,氧化铝绝缘层1603具有较强的耐火性,可以避免延烧现象的产生,使得导热板16整体同时兼具导热耐火高硬度性,出线槽17的设置用于线路18的排版,避免线路18混合造成线路18之间的磨损及缠绕,扣条19设置于内容槽10的上方并对内容槽10进行半包裹,对内容槽10内部的线路18进行限位,避免进行树脂封装时线路18移动造成封装误差。

尽管参照前述实施例对本发明进行了详细的说明,对于本领域的技术人员来说,其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

- 一种半导体封装电磁屏蔽结构及其使用方法

- 一种半导体封装电磁屏蔽结构