集成装置的多层布置以及抛光期间保护存储器单元的方法

文献发布时间:2023-06-19 13:48:08

本申请案主张2019年5月15日申请的序列号为16/412,622的美国临时专利申请案的优先权及权益,所述申请案的公开内容以引用的方式并入本文中。

技术领域

集成装置的多层布置以及抛光期间保护存储器单元的方法。

背景技术

目前正在努力形成集成装置的多层布置。例如,可在包括驱动器、感测放大器等的层上方形成包括存储器的层。期望开发适合于电耦合上层的组件与下层的组件的结构及开发形成此类结构的方法。

附图说明

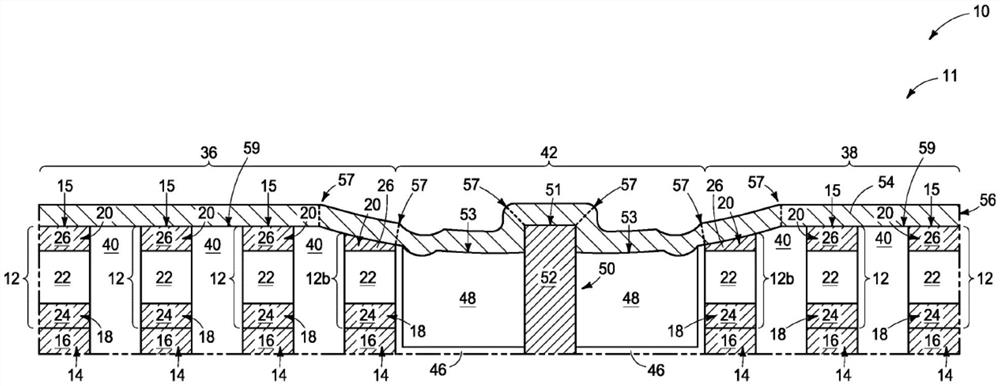

图1是组合件在实例实施例的实例过程阶段的示意性横截面侧视图。

图1A是可取代图1中展示的实例存储器单元使用的实例存储器单元的示意性横截面视图。

图2是图1的组合件在图1的过程阶段之后的实例过程阶段的示意性横截面侧视图。

图2A是图2的组合件的区的示意性俯视图。图2的横截面是沿图2A的线2-2。

图3是图1的组合件在图2的过程阶段之后的实例过程阶段的示意性横截面侧视图。

图3A是图3的组合件的区的示意性俯视图。图3的横截面是沿图3A的线3-3。

图4是实例多层配置的示意性横截面侧视图。

图5是组合件在实例实施例的实例过程阶段的示意性横截面侧视图。

图5A是可替代图5的组合件使用的实例组合件的示意性横截面侧视图。

图6是图5的组合件在图5的过程阶段之后的实例过程阶段的示意性横截面侧视图。

图6A是图6的组合件的区的示意性俯视图。图6的横截面是沿图6A的线6-6。

图7是图5的组合件在图6的过程阶段之后的实例过程阶段的示意性横截面侧视图。

图7A是图7的组合件的区的示意性俯视图。图7的横截面是沿图7A的线7-7。

图7B是图7的组合件的区的示意性俯视图,其说明与其它组件隔离的字线及位线。

图8是实例多层配置的示意性横截面侧视图。

图9是实例存储器阵列的示意图。

具体实施方式

一些实施例包含多层架构,其中存储器层在包括CMOS电路系统的层上方,且其中存储器层的组件通过导电互连件与CMOS电路系统电耦合。存储器层内的导电互连件可延伸穿过中介绝缘材料,且可邻近于绝缘支撑材料。中介绝缘材料可包括二氧化硅,且绝缘支撑材料可包括一或多个高介电常数组合物。一些实施例包含通过邻近于存储器单元提供支撑材料而在一或多个抛光工艺期间保护存储器单元的方法。参考图1到9描述实例实施例。

参考图1,在用于形成穿过存储器单元阵列的互连件的实例方法的实例过程阶段说明组合件10。组合件包含包括存储器单元12的存储器阵列11。存储器单元12由字线(存取线)14支撑。所说明存储器单元12可代表存储器阵列11内的大量大体上相同存储器单元;且在一些实施例中,存储器阵列11可包括数百、数千、数百万、数亿个等存储器单元。术语“大体上相同”意味着在合理制造及测量公差内相同。所说明字线14可代表存储器阵列内的大量大体上相同字线。

字线14包括导电材料16。导电材料16可包括任何合适导电组合物;例如,举例来说各种金属(例如,钛、钨、钴、镍、铂、钌等)、含金属组合物(例如,金属硅化物、金属氮化物、金属碳化物等)及/或导电掺杂半导体材料(例如,导电掺杂硅、导电掺杂锗等)中的一或多者。在一些实施例中,导电材料16可包括一或多个金属及/或含金属组合物;且可例如包括氮化钽上钨。

存储器单元12中的每一者包括底部电极18、顶部电极20及顶部电极与底部电极之间的可编程材料22。电极18及20分别包括导电电极材料24及26。电极材料24及26可包括任何合适导电组合物;例如,举例来说各种金属(例如,钛、钨、钴、镍、铂、钌等)、含金属组合物(例如,金属硅化物、金属氮化物、金属碳化物等)及/或导电掺杂半导体材料(例如,导电掺杂硅、导电掺杂锗等)中的一或多者。电极材料24及26可为彼此相同的组合物,或可为相对于彼此不同的组合物。在一些实例实施例中,电极材料24及26可包括TiSiN(氮化钛硅)、TiAlN(氮化钛铝)、TiN(氮化钛)、WN(氮化钨)、Ti(钛)、C(碳)及W(钨)中的一或多者、大体上由其构成或由其构成;其中式指示所列出物质内的组分而非指定此类组分的特定理想配比。

底部电极18与字线电耦合,且在所展示实施例中直接抵靠字线。

可编程材料22可包括任何合适组合物。在一些实施例中,可编程材料22可为双向存储器材料,且特定来说可为硫属化物。例如,可编程材料22可包括锗(Ge)、锑(Sb)、碲(Te)及铟(In)中的一或多者。在特定实施例中,可编程材料22可例如包括GeSbTe或InGeTe、大体上由GeSbTe或InGeTe构成或由GeSbTe或InGeTe构成,其中式指示所列出物质内的组分而非指定此类组分的特定理想配比。在一些实施例中,存储器单元可包括经配置以用于自选择装置中的可编程材料;例如,硫属化物材料可充当存储元件及选择装置两者。硫属化物可单独用于自选择装置中,或可与另一组合物组合使用。实例自选择PCM装置(其中PCM装置是包括相变材料的装置)在将爱康科技股份有限公司(Micron Technology,Inc.)为受让人的第8,847,186号美国专利(雷达埃利(Redaelli)等人)及第10,134,470号(托里拆利(Tortorelli)等人)中描述。

存储器单元12是可用于存储器阵列中的实例存储器单元。在其它实施例中,存储器单元可具有其它配置。例如,图1A展示具有另一实例配置的存储器单元12a。存储器单元12a包含电极18及20,且进一步包含第三电极28。在一些实施例中,电极28、18及20分别可被称为底部电极、中间电极及顶部电极。电极28包括电极材料30。此电极材料可包括上文关于电极材料24及26描述的组合物中的任一者;且可为与电极材料24及26中的一者或两者相同的组合物,或可在成分上不同于电极材料24及26中的至少一者。

双向材料22可被称为上电极20与中间电极18之间的第一双向材料。第二双向材料32在下电极28与中间电极18之间。第二双向材料32可并入到选择装置34的双向阈值开关(OTS)中。因此,存储器单元12a可包括与选择装置34组合的可编程材料22而非呈自选择配置。

双向材料32可包括任何合适组合物,且在一些实施例中可包括上文描述为适合于编程材料22的组合物中的一或多者。

再次参考图1,字线14可被视为相对于横截面视图延伸进出页面。绝缘材料40在字线之间,且将字线彼此隔开。绝缘材料40还将邻近存储器单元12彼此隔离。绝缘材料40可包括任何合适组合物;且在一些实施例中可包括二氧化硅、大体上由二氧化硅构成或由二氧化硅构成。

图1的横截面视图展示经布置以形成第一组36及第二组38的存储器单元12(在一些实施例中,第一组36及第二组38可被称为存储器阵列11的第一区及第二区)。耦合区42在存储器单元的第一组36与第二组38之间。最终,将在耦合区内形成导电互连件。

覆盖材料44在存储器单元12的第一组(36)与第二组(38)之间。覆盖材料44可包括任何合适组合物;且在一些实施例中可包括氮化硅、大体上由氮化硅构成或由氮化硅构成。

衬垫46在覆盖材料44上方且跨耦合区42延伸。衬垫46可包括任何合适组合物;且在一些实施例中可包括二氧化硅、大体上由二氧化硅构成、由二氧化硅构成。

绝缘材料48设置于衬垫46上方且跨耦合区42。绝缘材料48可包括任何合适组合物;且在一些实施例中可包括二氧化硅、大体上由二氧化硅构成、由二氧化硅构成。在本文中描述的一些应用中,绝缘材料48可被称为中介绝缘材料。

材料46及48可包括彼此相同的组合物(例如,都可包括二氧化硅),但被展示为单独材料以强调其可通过单独方法形成。

参考图2,在耦合区42内形成导电互连件50且在已利用一或多个抛光工艺暴露存储器单元12的上表面15及导电互连件50的上表面51之后展示组合件10。

导电互连件包括导电材料52。导电材料52可包括任何合适导电组合物;例如,举例来说各种金属(例如,钛、钨、钴、镍、铂、钌等)、含金属组合物(例如,金属硅化物、金属氮化物、金属碳化物等)及/或导电掺杂半导体材料(例如,导电掺杂硅、导电掺杂锗等)中的一或多者。导电互连件50可完全延伸穿过包括存储器阵列11的层(即,层叠、层级等)。导电互连件50可包括多个组合物,且可包括贯穿层的各种位置处的不同组合物。在一些实例实施例中,导电互连件50的所说明部分可包括钨、大体上由钨构成或由钨构成。

导电互连件50可使用任何合适处理形成。例如,在一些实例实施例中,可形成通孔以延伸穿过耦合区42内的材料,且接着可将合适导电材料设置于通孔内以形成导电互连件50。

用于暴露表面15及51的抛光可包含多个抛光步骤以穿透图1中展示的各种材料。在此抛光期间可发生的问题是凹陷(其在图2中示意性地说明),其中在邻近于导电互连件50的软材料48中具有非平面轮廓53。在图2的所说明应用中,耦合区42附近的一对存储器单元12被标记为12b,使得其可与其它存储器单元区分。非平面轮廓53不期望地延伸到存储器单元12b中,且侵蚀此类存储器单元的顶部电极20的导电材料26。侵蚀还可延伸到比图2中所说明更深的位置以穿透到存储器单元12b的可编程材料22中。

与尚未被侵蚀的其它存储器单元相比,存储器单元12b的一或多个材料的侵蚀可更改此类存储器单元的性能特性。这可使存储器单元12b中的一或多者不适合于其预期应用。此外,尽管仅最靠近耦合区50的存储器单元展示为被侵蚀,但在实践中,凹陷可延伸相当大距离到存储器阵列中,使得大量存储器单元可变得无法操作。

图2A展示组合件10在图2的处理阶段的俯视图。图2A的视图不相对于图2的视图按比例调整,且利用不同于图2中利用的组合件10的示意表示。无论如何,图2的横截面可被理解为大体上沿图2A的线2-2。

图2A展示存储器单元的第一组36与第二组38之间的耦合区42(个别存储器单元未在图2A中展示)。耦合区包括多个导电互连件50。导电互连件沿线布置,其中此线沿相对于图2的横截面的平面进出页面的方向延伸。导电互连件在俯视图中可具有方形形状(如展示),或可具有任何其它合适形状,包含例如圆形形状、矩形形状、椭圆形形状等。

应理解,即使图2的横截面仅包括耦合区42的所说明部分内的导电互连件50中的一者,在其它实施例中,仍可沿图2的横截面形成多个导电互连件。因此,即使图2A展示耦合区42内的互连件50的单个行,在其它实施例中,耦合区内仍可存在此类互连件的多个行以形成跨耦合区的互连件的矩阵。而且,应理解,图2及2A的所说明互连件50可代表形成于耦合区42内的大量大体上相同互连件。例如,在一些实施例中,可存在形成于耦合区42内的数百、数千、数百万、数十万等个导电互连件50。

参考图3,形成导电材料54以跨存储器单元12的第一组(36)及第二组(38)且跨耦合区42延伸;且图案化为数字线(感测线、存取线)56。导电材料54可包括任何合适导电组合物;例如,举例来说各种金属(例如,钛、钨、钴、镍、铂、钌等)、含金属组合物(例如,金属硅化物、金属氮化物、金属碳化物等)及/或导电掺杂半导体材料(例如,导电掺杂硅、导电掺杂锗等)中的一或多者。

图3的配置的问题是所说明深凹陷的非平面轮廓53提供不均匀表面来支撑位线56。因此,位线在所说明位置57处或其附近具有相对严重弯曲。位线在位置57处或其附近可部分断开或可变薄,这可导致此类位置处的位线内的非所要高电阻。此外,位线可无法遵循下层非平面形貌。因此,在位线的部分下方可仍有空间(间隙),这可导致在位线上方制造后续结构期间及/或在位线的操作期间的后续问题。

图3A利用类似于图2A的示意说明的示意说明展示组合件10在图3的处理阶段的俯视图。图3的位线56是跨存储器阵列11形成的多个位线中的一者。位线中的每一者跨所说明导电互连件50中的一者延伸。导电互连件50以虚线视图展示以指示其在位线56下方。

图1到3的描述指示字线14在存储器单元12下方,且位线56在存储器单元上方。在其它应用中,字线及位线的相对定向可颠倒,使得位线在存储器单元下方且字线在存储器单元上方。在其中所指示结构可为字线或位线的上下文中,术语“存取/感测线”、“字线/位线”、“位线/字线”及“感测/存取线”可在本文中用于一般地指代位线及字线。

图3及3A的导电互连件50可用于使来自一个层的电路系统能够与多层堆叠内的另一层的电路系统电耦合。例如,图4展示具有相对于彼此垂直偏移的三个层60、62及64的多层堆叠58。图4的垂直堆叠布置可向上延伸以包含额外层。层60、62及64可被视为彼此叠置的层级的实例。所述层级可在不同半导体裸片内,或所述层级中的至少两者可在相同半导体裸片内。底层60可包含控制电路系统及/或感测电路系统(例如,可包含字线驱动器、感测放大器等;且可包含CMOS电路系统,如展示)。上层62及64可包含存储器阵列,例如,举例来说图3及3A的存储器阵列11。各种层内的存储器阵列可彼此相同(例如,都可为PCM装置阵列)或可相对于彼此不同(例如,一些可为PCM装置阵列,而其它并非PCM装置阵列)。而且,上层中的一或多者可包含控制电路系统或其它逻辑电路系统。

导电互连件50被说明为实现从层62及64的电路系统到层60的电路系统的连接,其中利用虚线箭头61示意性地展示此类连接。在实例实施例中,层62(其可被称为存储器层)内的感测/存取线56通过互连件50与层60的电路系统耦合。例如,与层62内的存储器阵列11相关联的位线可与层60内的感测放大器耦合,或与层62内的存储器阵列11相关联的字线可与层60内的字线驱动器耦合。关于图3论述的问题可有问题地干扰从与层60、62及64中的一者相关联的电路系统到与此类层中的另一者相关联的电路系统的耦合。

一些实施例包含用于缓解图2及3的有问题非平面轮廓53的方法。

参考图5,在类似于上文参考图1描述的过程阶段的过程阶段展示组合件10。然而,组合件包含邻近于存储器单元12的第一组(36)及第二组(38)的支撑材料66。支撑材料66可包括绝缘材料,且可被称为绝缘支撑材料。支撑材料66包括不同于中介材料48的一组合物;且在一些实施例中可包括一或多个高介电常数材料。术语“高介电常数”意味着大于二氧化硅的介电常数(即,大于3.9)的介电常数。在一些实施例中,支撑材料66可包括氮化硅、氮氧化硅、氧化铝、氧化铪及氧化锆中的一或多者、大体上由其构成或由其构成。可期望材料66适合于在相对低温度下沉积(由于其在形成存储器单元12之后沉积),具有相对于二氧化硅的高蚀刻选择性,适合于以良好保形性沉积及/或具有比材料48更慢的抛光速率(即,对抛光工艺具有相对弹性,使得与材料66相比,通过抛光工艺选择性地移除材料48)。

支撑材料66被展示为在沿图5的横截面的两个结构(心轴)68及70内。在一些实施例中,结构68及70分别可被称为第一柱及第二柱。支撑材料66可围绕耦合位置42的外围延伸,使得所说明结构68及70是单连续结构的部分(在图6A中示意性地展示)。可通过将材料沉积于组合件10的区42内且接着使材料66经受间隔件蚀刻(即,各向异性蚀刻)而在图5的所展示配置中形成材料66。结构68及70具有由间隔件蚀刻导致的圆形上边缘。在其它实施例中,结构68及70可具有其它配置。

图5的横截面视图展示由包括中介绝缘材料48的中介区72彼此隔开的结构68及70。

结构68及70(即,支撑材料66)可形成为任何合适宽度W,且在一些实施例中具有从约

支撑材料66优选地形成为至少约等于存储器单元12的高度的高度,且在一些实施例中形成为大于或等于存储器单元的高度的高度。图5展示形成到第一高度H

参考图6,在图5的处理阶段之后且类似于图2的处理阶段的处理阶段展示组合件10。在耦合区42内形成导电互连件50,且延伸穿过中介绝缘材料48。导电互连件50具有沿图6的横截面的相对侧壁(即,侧壁表面)73及75。侧壁73及75分别可被称为第一侧壁及第二侧壁。第一侧壁73通过包含第一柱68的第一区74与存储器单元12的第一组36隔开,且第二侧壁75通过包含第二柱70的第二区76与存储器单元12的第二组38隔开。在一些实施例中,存储器单元组36及38可被称为片块,且柱68及70可被视为邻近于此类片块的边缘。

已使用类似于上文参考图2描述的抛光步骤的一或多个抛光步骤抛光组合件10的上表面,且此已减小组合件的总高度。在所说明实施例中,在图6的处理阶段(即,在一或多个抛光工艺之后),柱68及70与存储器单元12具有大致相同的高度。

第一柱68及第二柱70(即,支撑材料66)在抛光期间提供支撑以保护存储器单元12免受侵蚀。特定来说,非平面轮廓53被展示为在图6的处理阶段不如在图2的处理阶段严重(且在一些实施例中可不存在或至少大体上完全不存在)。图6的配置的非平面轮廓53仅延伸到支撑材料66而不延伸到存储器单元12b(与上文参考图2描述的配置相比)。因此,在其中支撑材料66保护此类存储器单元免受侵蚀的应用中,在用于暴露存储器单元及导电互连件50的上表面15及51的抛光之后,存储器单元12b可保持完整功能。

图6A利用类似于图2A的示意说明的示意说明展示组合件10在图6的处理阶段的俯视图。

参考图7,在图6的处理阶段之后且类似于图3的处理阶段的处理阶段展示组合件10。导电材料54经形成在组合件10的上表面上方,且图案化为位线56。然而,由于图7的非平面轮廓53远不如图3的非平面轮廓明显,所以可缓解或甚至完全避免上文参考图3描述的问题。因此,利用支撑材料66可有利地能够在具有比不存在支撑材料时将产生的困难更少的困难的情况下制造位线56。

图7A利用类似于图3A的示意说明的示意说明展示组合件10在图7的处理阶段的俯视图。图7A的图展示图7的导电互连件50是许多大体上相同导电互连件中的一者,其中导电互连件中的其它者在图7的横截面的平面外;且展示位线56是许多大体上相同位线中的一者,其中位线中的其它者在图7的横截面的平面外。支撑材料66在图7A中以虚线视图示意性地说明以提醒读者支撑材料66在数字线下方且支撑数字线的区。

图7B展示组合件10在图7的处理阶段的另一示意性俯视图。图7B展示布置为存储器单元12下方的第一系列感测/存取线的字线14,且展示布置为存储器单元12上方的第二系列感测/存取线的位线56(其中在所说明实施例中,第一系列的线14大体上正交于第二系列的线56)。存储器单元12在图7B中不可见,但应被理解为在存取/感测线56与存取/感测线14的交叉点处(在交叉点中的一者处以虚线箭头示意性地说明)。如参考图7可理解,存取/感测线56中的每一者与第一组36及第二组38的存储器单元12电连接且还与导电互连件50耦合。

图8展示类似于图4的多层组合件且沿第二层62包括图7的存储器阵列11的多层组合件58。存取/感测线56通过导电互连件50耦合到层60内的CMOS电路系统。在所说明实施例中,CMOS电路系统在包括存储器阵列11的层62下方。在其它实施例中,包括CMOS电路系统的层60可在相对于层62的其它位置中。

支撑材料66在图8中示意性地说明为在所说明存取/感测线56下方且支撑邻近于存储器阵列11的区36及38的存取/感测线56的区。

在一些实施例中可省略额外层64。替代地,层64可包括另一存储器阵列。层64的存储器阵列可为类似于图7中展示的阵列的PCM装置阵列,或可为不同类型的阵列。在其它实施例中,层64可包括除阵列以外的其它电路系统,例如,举例来说传感器电路系统。

上文论述的实施例的存储器阵列11可具有任何合适配置。图9示意性地说明实例存储器阵列11的实例配置。此配置包含字线(WL1到WL4)与位线(BL1到BL6)的交叉点处的存储器单元12。存储器单元中的每一者通过字线中的一者与位线中的一者的组合唯一地寻址。

上文论述的组合件及结构可用于集成电路内(其中术语“集成电路”意味着由半导体衬底支撑的电子电路);且可并入到电子系统中。此类电子系统可用于例如存储器模块、装置驱动器、电源模块、通信调制解调器、处理器模块及特定应用模块中,且可包含多层、多芯片模块。电子系统可为广泛系统范围中的任一者,例如,举例来说摄像机、无线装置、显示器、芯片集、机顶盒、游戏、照明、车辆、时钟、电视、蜂窝式电话、个人计算机、汽车、工业控制系统、飞机等。

除非另外指定,否则本文中描述的各种材料、物质、组合物等可使用现已知或将开发的任何合适方法形成,包含例如原子层沉积(ALD)、化学气相沉积(CVD)、物理气相沉积(PVD)等。

术语“介电”及“绝缘”可用于描述具有绝缘电性质的材料。所述术语在本发明中被视为同义的。在一些例子中利用术语“介电”且在其它例子中利用术语“绝缘”(或“电绝缘”)可在本发明内提供语言变化以简化所附权利要求书内的前置基础,且不用于指示任何显著化学或电差异。

术语“电连接”及“电耦合”都可用于本发明中。所述术语被视为同义的。在一些例子中利用一个术语且在其它例子中利用另一术语可在本发明内提供语言变化以简化所附权利要求书内的前置基础。

图式中的各种实施例的特定定向仅为阐释性目的,且所述实施例可在一些应用中相对于所展示定向旋转。本文中提供的描述及所附权利要求书涉及具有各种特征之间的所描述关系的任何结构,而不管所述结构是否处于图式的特定定向或相对于此定向旋转。

所附说明的横截面视图仅展示横截面的平面内的特征,且不展示横截面的平面后的材料(除非另外指示),以便简化图式。

当结构在上文被称为“在”另一结构“上”、“邻近于”或“抵靠”另一结构时,其可直接在其它结构上或还可存在中介结构。相比来说,当结构被称为“直接在”另一结构“上”、“直接邻近于”或“直接抵靠”另一结构时,不存在中介结构。术语“直接在…下方”、“直接在…上方”等不指示直接实体接触(除非另外明确陈述)而代替地指示直立对准。

结构(例如,层、材料等)可被称为“垂直延伸”以指示结构大体上从下层基底(例如,衬底)向上延伸。垂直延伸结构可大体上相对于基底的上表面正交地延伸或不如此。

一些实施例包含一种形成布置的方法。形成组合件,所述组合件沿横截面包括耦合区的一个侧上的第一组存储器单元及所述耦合区的相对侧上的第二组存储器单元。所述组合件沿所述横截面包含邻近于所述第一组存储器单元的第一柱及邻近于所述第二组存储器单元的第二柱。所述第一柱及所述第二柱包括第一组合物且由具有不同于所述第一组合物的第二组合物的中介绝缘材料彼此隔开。所述存储器单元在所述组合件内具有第一高度。所述第一柱及所述第二柱在所述组合件内具有大于或等于所述第一高度的第二高度。在所述耦合区内形成导电互连件且使其延伸穿过所述中介绝缘材料。所述导电互连件具有沿所述横截面的第一侧壁及第二侧壁,其中所述第一侧壁与所述第二侧壁呈相对关系。所述互连件的所述第一侧壁通过包含所述第一柱的第一区与所述存储器单元的所述第一组隔开,且所述互连件的所述第二侧壁通过包含所述第二柱的第二区与所述第二组存储器单元隔开。使用一或多个抛光步骤抛光所述组合件的上表面以减小所述组合件的总高度。所述第一柱及所述第二柱在所述抛光期间提供支撑以保护所述第一组及所述第二组的所述存储器单元在所述抛光期间免受侵蚀。

一些实施例包含一种形成布置的方法。形成第一层以包含CMOS电路系统。形成第二层以包含组合件,所述组合件具有耦合区的一个侧上的第一组存储器单元且具有所述耦合区的相对侧上的第二组存储器单元。所述组合件包含邻近于所述存储器单元的所述第一组及所述第二组的绝缘支撑材料且包含邻近于所述绝缘支撑材料的中介绝缘材料。所述绝缘支撑材料具有第一组合物且所述中介绝缘材料具有不同于所述第一组合物的第二组合物。在所述耦合区内形成导电互连件且使其延伸穿过所述中介绝缘材料。使用一或多个抛光步骤抛光所述组合件的上表面以减小所述组合件的总高度。所述绝缘支撑材料在所述抛光期间提供支撑以保护所述第一组及所述第二组的所述存储器单元在所述抛光期间免受侵蚀。耦合所述第二层的所述导电互连件与所述第一层的所述CMOS电路系统。

一些实施例包含一种布置,其包括存储器层,所述存储器层包含组合件,所述组合件包括耦合区的一个侧上的第一组存储器单元及所述耦合区的相对侧上的第二组存储器单元。所述组合件包含邻近于所述第一组存储器单元及所述第二组存储器单元的绝缘支撑材料及邻近于所述绝缘支撑材料的中介绝缘材料。所述绝缘支撑材料包括第一组合物且所述中介绝缘材料包括不同于所述第一组合物的第二组合物。所述绝缘支撑材料具有与所述第一组及所述第二组的所述存储器单元大致相同的高度。导电互连件在所述存储器层的所述耦合区内且延伸穿过所述中介绝缘材料。额外层在所述存储器层下方。所述额外层包括与所述导电互连件耦合的CMOS电路系统。

按照法规,已按或多或少关于结构及方法特征特定的语言描述本文中揭示的标的物。然而,应理解,权利要求书不限于所展示及描述的特定特征,这是因为本文中揭示的方法包括实例实施例。因此,权利要求书应被提供如字面措词的完整范围,且根据等效物的教义适当解释。

- 集成装置的多层布置以及抛光期间保护存储器单元的方法

- 存储器单元、集成装置及形成存储器单元的方法