倍频电路的占空比校正方法及校正系统

文献发布时间:2023-06-19 18:34:06

技术领域

本发明涉及集成电路领域,更具体地涉及一种倍频电路的占空比校正方法及校正系统。

背景技术

常规的倍频电路通常采用锁相环PLL形式来实现。而锁相环PLL是由一个鉴相器(PD)、低通滤波器(LPF)、压控振荡器(VCO)和分频器(N)组成。锁相环的最基本配置是将参考信号的相位与可调反馈信号的相位进行比较,如图1所示,此电路的中心为鉴相器。如果此两个信号之间有相位差存在时,便会产生相位误差信号输出。利用此一误差信号,可以控制压控振荡器VCO的振荡频率,使VCO的相位与基准信号的相位(也即是频率)成为一致,从而实现倍频的目的(N=2)。

但是采用PLL实现倍频时钟时功耗面积开销大,而且常规的这种倍频实现方式中并没有对时钟的占空比进行校正,使得倍频时的精度没法保证,有时可能没法正常实现倍频,影响整个倍频电路的正常工作。

因此,有必要提供一种改进的倍频电路的占空比校正方法及校正系统克服上述缺陷。

发明内容

本发明的目的是提供一种倍频电路的占空比校正方法及校正系统,本发明方案的芯片占用面积很小,更有利于实现芯片的高度集成化;还可实现多倍频,获得更多频率值的输出时钟,提高了使用范围;同时还对输出时钟的占空比进行精准校正,保证了输出时钟频率的稳定。

为实现上述目的,本发明提供了一种倍频电路的占空比校正方法,其包括如下步骤:

a.采样输入时钟的上升沿、下降沿并根据上升沿、下降沿信息转化为脉冲信号且获得频率信息;

b.将所述脉冲信号转化为锯齿波信号,并获取另一含有占空比偏移量的信号;

c.差分比较所述锯齿波信号和含有占空比偏移量的信号,获得对比结果;

d.差分放大对比结果并获得含有占空比偏移量的信号,重复步骤b至d,直到差分比较输出的时钟的占空比为50%。

较佳地,所述脉冲信号为采样上升沿和/或下降沿信息转化形成的脉冲信号,且输入时钟经若干次反向和延时后与原时钟/反向原时钟进行逻辑异或而形成所述脉冲信号,延时的长度为脉冲信号的脉冲宽度。

较佳地,所述脉冲信号转化为锯齿波具体为,当脉冲来到时,立刻输出低电平;当脉冲消失,由低电平匀速上升至高电平,直到下一个脉冲来到立刻拉低为低电平。

较佳地,所述含有占空比偏移量的信号为,差分放大对比结果后形成的信号。

较佳地,所述倍频电路的占空比校正方法还包括步骤,根据对比结果对含有占空比偏移量的信号进行电压调节,直到差分比较输出的时钟的占空比为50%。

相应地,本发明还提供了一种倍频电路的占空比校正系统,其包括至少两级倍频校正电路,各级倍频校正电路依次串联连接,所述第1级倍频校正电路对输入的时钟信号进行占空比校正,以使输出时钟的占空比达到50%,其它各级倍频校正电路依次对上一级倍频校正电路输出的时钟信号进行2倍频。

较佳地,每1级所述倍频校正电路均包括第一校正单元与第二校正单元,所述第一校正单元采样输入时钟的上升沿和/或下降沿并根据上升沿和下降沿信息转化为脉冲信号,所述第二校正单元根据所述脉冲信号对输出时钟的占空比进行校正。

较佳地,所述脉冲信号包括第一脉冲信号及第二脉冲信号,所述第一脉冲信号为采样输入时钟信号的上升沿或下降沿而转化形成的脉冲信号,所述第二脉冲信号为采样输入时钟的上升沿和下降沿而转化形成的脉冲信号,且所述第二脉冲信号的频率为第一脉冲信号频率的2倍。

较佳地,第1级所述倍频校正电路的第二校正单元根据其第一校正单元输出的第一脉冲信号对输出时钟的占空比进行校正,直到输出时钟的占空比为50%。

较佳地,其它各级倍频校正电路的第二校正单元根据其同级倍频校正电路的第一校正单元输出的第二脉冲信号对输出时钟的占空比进行校正,直到输出时钟的占空比为50%。

与现有技术相比,本发明的倍频电路的占空比校正方法及校正系统,通过倍频校正电路的简单多级叠加,即可实现对输入时钟的多次倍频,结构简单,而且没有使用锁相环结构,大大减小了芯片的占用面积,更有利于芯片的高度集成化发展;另外,在本发明的倍频电路的占空比校正系统中,各级对输入时钟的倍频均是在进行占空比校正后才进行的,使得占空比误差不会被累积,实现了对输出时钟占空比的精准校正,不仅保证了倍频的正常进行而且保证了倍频的高度精确化。

通过以下的描述并结合附图,本发明将变得更加清晰,这些附图用于解释本发明的实施例。

附图说明

图1为现有的倍频电路的结构框图。

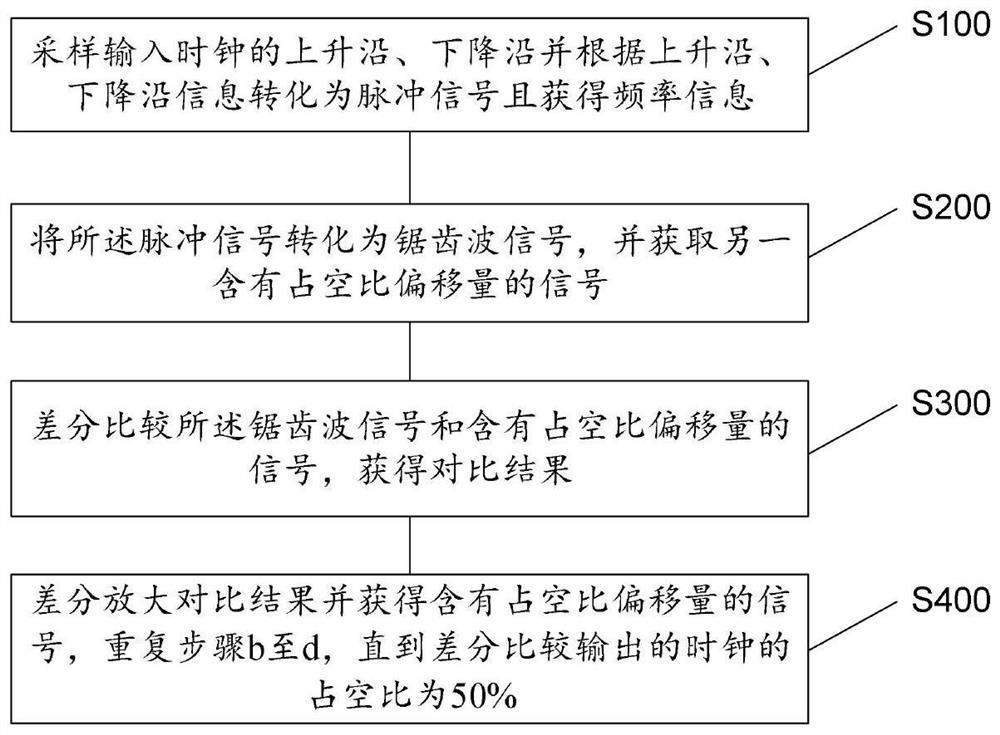

图2为本发明倍频电路的占空比校正方法流程图。

图3为本发明倍频电路的占空比校正系统的前两级的倍频校正电路连接的结构框图。

图4为本发明倍频电路的占空比校正系统的第1级倍频校正电路的输入时钟与脉冲时钟的时序图。

具体实施方式

现在参考附图描述本发明的实施例,附图中类似的元件标号代表类似的元件。如上所述,本发明提供了一种倍频电路的占空比校正方法及校正系统,本发明方案的芯片占用面积很小,更有利于实现芯片的高度集成化;还可实现多倍频,获得更多频率值的输出时钟,提高了使用范围;同时还对输出时钟的占空比进行精准校正,保证了输出时钟频率的稳定。

请参考图2,描述本发明占空比校正方法,图2为本发明倍频电路的占空比校正方法流程图,如图所示,本发明倍频电路的占空比校正方法包括如下步骤:

步骤S100,采样输入时钟的上升沿、下降沿并根据上升沿、下降沿信息转化为脉冲信号且获得频率信息;在本步骤中,通过采样上升沿、下降沿及同时采样上升沿与下降沿从而可得到不同的脉冲信号,采样上升沿、下降沿所获得的脉冲信号的频率是相同的,且与所述输入时钟的频率相同,从而可采用这两脉冲信号在后续步骤中实现对输出时钟的占空比校正;另外,显而易见地,同时采样上升沿与下降沿而形成的脉冲信号的频率是采样上升沿或下降沿形成的脉冲信号频率的2倍(具体可参考图4所示时序图中的CLK1X与CLK2X),若要对输出时钟的频率进行倍频则可使用该脉冲信号;在本发明的倍频电路的占空比校正方法中,仅对输出时钟的占空比进行校正,因此,在本步骤中进一步地,所述脉冲信号为采样上升沿或下降沿信息转化形成的脉冲信号,且输入时钟经若干次反向和延时后与原时钟/反向原时钟进行逻辑异或而形成所述脉冲信号,延时的长度为脉冲信号的脉冲宽度;其中,通过反相器实现对输入时钟的反向,延时通常由延时单元来实现,例如,每个延时单元可由多个反相器相互串联构成,反相器的个数由延时的长度来确定,在此不再细述;具体地,在本发明中,延时的长度为脉冲信号的脉冲宽度,根据后续步骤的要求,所述脉冲为窄脉冲,也即所述延时的长度不宜过长;在本发明所述方法的实际应用过程中,不同的使用场景可能需要用到的窄脉冲的实际宽度是各有区别的,因此,对所述输入时钟的反向次数各有不同,也即使得反向延时后的信号可能与原时钟信号进行异或也可能是与反向原时钟进行异或,在本发明中并不作具体限定。

步骤S200,将所述脉冲信号转化为锯齿波信号,并获取另一含有占空比偏移量的信号;在本步骤中,由于所述步骤S100所产生的脉冲为窄脉冲,从而使得在本步骤中将脉冲信号转化为锯齿波信号变得很容易;具体地,转化为锯齿波信号的过程为,当脉冲来到时,立刻输出低电平;当脉冲消失,由低电平匀速上升至高电平,直到下一个脉冲来到立刻拉低为低电平,如此完成窄脉冲信号到锯齿波信号的转换。

步骤S300,差分比较所述锯齿波信号和含有占空比偏移量的信号,获得对比结果;在本发明中,通常通过差分比较器来实现本步骤的差分比较过程,也即分别将所述锯齿波信号和含有占空比偏移量的信号输入差分比较器的两输入端,当然实现该过程并不仅限于此器件,在本发明中只是以差分比较器来举例说明本发明的方案;在本步骤中,可理解地,在一开始的时候,差分比较器的另一输入端所输入的信号为不定信号,只有经过如步骤S400所述示次重复后,该输入端的信号才为含有占空比偏移量的信号,在此基础上才能最终使得对比结果(输出的时钟)的占空比为50%。

步骤S400,差分放大对比结果并获得含有占空比偏移量的信号,重复步骤S200至S400,直到差分比较输出的时钟的占空比为50%;在本步骤中,经差分比较输出的对比结果再经差分放大后,使得所述差分比较后两输入信号的电压(所述锯齿波信号的电压值是指其平均电压值)差异能更直观地体现出来,便于后续对含有占空比偏移量的信号进行电压调节;具体地,在本步骤中,根据滤波理论可知占空比越大则得到的直流电压越高,反之占空比越小得到的直流电压越低,由于差分比较器一输入端所输入的锯齿波信号为固定的占空比为50%的信号,从而通过对比差分比较器另一输入端信号(含有占空比偏移量的信号)与锯齿波信号(平均电压值)的电压差,即可得出两信号占空比的差别,进而调节另一输入端信号的电压值,也就是当另一输入信号的电压大于所述锯齿波信号的电压,则将另一输入信号的电压调低,反之,当另一输入信号的电压小于所述锯齿波信号的电压,则将另一输入信号的电压调高;如此,重复执行步骤S200至S400,使得进行差分比较的两信号(锯齿波信号与含有占空比偏移量的信号)之间的电压差慢慢减小,直到两信号的电压差为0或接近0,也即是直到差分比较输出的时钟的占空比为50%;其中上述步骤S200和步骤S300中所述的含有占空比偏移量的信号即为差分放大对比结果后形成的信号,由前述可知,差分比较后输出的信号是所述锯齿波信号(占空比为50%的信号)与另一输入信号(占空比不是50%)对比而得出的,该输出信号再经差分放大后再输出,此时的输出信号就包含有所述锯齿波信号与另一输入信号两者之间的占空比偏移量信息,可理解地,所述含有占空比偏移量的信号是在本发明的倍频电路的占空比校正方法的运行实现过程中由一不定信号经不断对比调整而形成的,在输出时钟的占空比被校正为50%之前,其是一实时不断变化的信号,最终根据输出时钟占空比的稳定而趋于稳定。

由上述可知,本发明的倍频电路的占空比校正方法,每将含有占空比偏移量的信号与锯齿波信号(占空比固定为50%)差分对比一次,即调整含有占空比偏移量的信号的电压一次,调整后再与锯齿波信号进行对比,通过如此不断地循环,最终使得进行差分比较的两信号(锯齿波信号与含有占空比偏移量的信号)之间的电压差慢慢减小,直到两信号的平均电压差为0或接近0,也即是直到差分比较输出的时钟的占空比为50%,从而获得稳定的占空比为50%的输出时钟,实现了对输出时钟占空比的精准校正。

请参考图3,如图所示,本发明的倍频电路的占空比校正系统包括至少两级倍频校正电路(图示为两级),各级倍频校正电路依次串联连接,即,第1级倍频校正电路的输出端与第2级倍频校正电路和输入端连接,第2级倍频校正电路的输出端与第3级倍频校正电路和输入端连接,如此直至第N-1级倍频校正电路的输出端与第N级倍频校正电路的输入端连接,N为本发明倍频电路的占空比校正系统的倍频校正电路的级数,且为大于2的整数;其中,所述第1级倍频校正电路对输入的时钟信号进行占空比校正,以使输出时钟占空比达到50%,其它各级倍频校正电路依次对上一级倍频校正电路输出的时钟信号进行2倍频;如此,具体倍频电路的级数可根据输出时钟的频率要求而灵活设置,在本发明中并不做具体限制,最终输出时钟信号的频率Tout与输入时钟频率Tin的关系为Tout=2NTin,例如在图3中的第2级倍频校正电路中,其输入时钟CLKOUT1与最终输出时钟CLKOUT2的频率关系为:CLKOUT2=2*CLKOUT1。

进一步地,每1级所述倍频校正电路均包括第一校正单元与第二校正单元,所述第一校正单元采样输入时钟信号CLK0X的上升沿和和/或下降沿并根据上升沿和下降沿信息转化为脉冲信号;其中,所述脉冲信号包括第一脉冲信号CLK1X及第二脉冲信号CLK2X,所述第一脉冲信号CLK1X为采样输入时钟信号CLK0X的上升沿而转化形成的脉冲信号,如图4所示,由于所述第二脉冲信号CLK2X为采样输入时钟信号CLK0X的上升沿和下降沿而转化形成的脉冲信号,使得所述第二脉冲信号CLK2X的频率为第一脉冲信号频率的2倍,从而实现对输入时钟信号CLK0X的2倍频;另外,显而易见地,采样上升沿、下降沿所获得的脉冲信号的频率是相同的,如图4所示,在本发明中仅以采样上升沿为例进行说明,也即,所述第一脉冲信号CLK1X为采样输入时钟信号CLK0X的上升沿或下降沿信息而转化形成的脉冲信号所述第一脉冲信号CLK1X为采样输入时钟信号CLK0X的上升沿所述第一脉冲信号CLK1X为采样输入时钟信号CLK0X的上升沿所述第一脉冲信号CLK1X为采样输入时钟信号CLK0X的上升沿。另外,在本发明中,所述第二校正单元根据所述脉冲信号对输出时钟的占空比进行校正;具体地,在第1级所述倍频校正电路中,所述第二校正单元根据所述第一脉冲信号CLK1X对输出时钟的占空比进行校正,直到输出时钟占空比为50%。而在其它各级倍频校正电路中,所述第二校正单元根据其同级倍频校正电路的第一校正单元输出的第二脉冲信号CLK2X对输出时钟的占空比进行校正,直到输出时钟占空比为50%;其中,各级所述倍频校正电路的第二校正单元对输出时钟的校正方法与过程具体如上述本发明所描述的占空比校正方法所述,在此不再重复描述。

由上述可知,本发明的倍频电路的占空比校正系统通过倍频校正电路的简单多级叠加,即可实现对输入时钟的多次倍频,结构简单,而且没有使用锁相环结构,大大减小了芯片的占用面积,更有利于芯片的高度集成化发展;另外,在本发明的倍频电路的占空比校正系统中,各级对输入时钟的倍频均是在进行占空比校正后才进行的,使得占空比误差不会被累积,不仅保证了倍频的正常进行而且保证了倍频的高度精确化(占空比为稳定的50%)。

以上结合最佳实施例对本发明进行了描述,但本发明并不局限于以上揭示的实施例,而应当涵盖各种根据本发明的本质进行的修改、等效组合。

- 确定成像系统预校正参数方法及用于成像系统的预校正方法

- 刀具的智能校正系统及其校正方法

- 占空比校正电路和占空比校正方法

- 占空比校正电路和占空比校正方法