基板支承装置以及基板处理装置

文献发布时间:2023-06-19 18:32:25

相关申请的参照

本申请享受以日本专利申请2021-122404号(申请日:2021年7月27日)为基础申请的优先权。本申请通过参照该基础申请而包括基础申请的全部内容。

技术领域

本发明的实施方式涉及基板支承装置以及基板处理装置。

背景技术

在基板处理装置中,有时使用通过静电吸附基板或者通过吸引来吸附基板、从而在处理容器内支承基板的基板支承装置。但是,若基板具有翘曲,则有时向基板支承装置吸附时会对基板施加冲击而使其产生损伤。

发明内容

发明要解决的课题在于,提供能够抑制具有翘曲的基板损伤的基板支承装置以及基板处理装置。

实施方式的基板支承装置是在基板处理装置的处理容器内支承基板的基板支承装置,具备:载放板,包含陶瓷而构成,具有供上述基板载放的载放面;供电板,内置于上述载放板,使上述载放板静电地吸附上述基板;多个突起部,内部包括导电部件,至少配置在上述载放板的中央区域以及外缘区域,从上述载放面突出;多个弹性部件,与上述多个突起部对应地埋入于上述载放板,以使上述多个突起部从上述载放面突出的方式支承上述多个突起部,并且将上述供电板与上述导电部件电连接。

附图说明

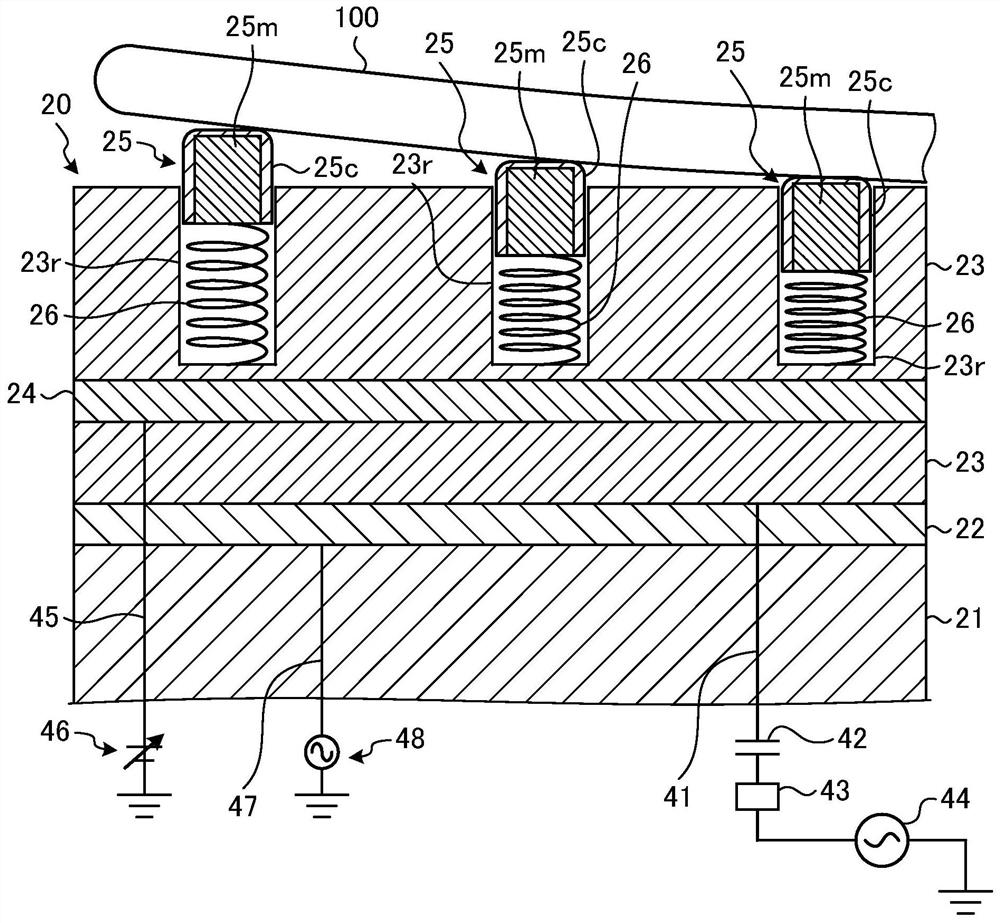

图1是示意地表示实施方式1的等离子处理装置的构成的一个例子的截面图。

图2是实施方式1的静电卡盘的俯视图。

图3是表示实施方式1的静电卡盘的截面构造的图。

图4A~图4C是表示实施方式1的等离子处理装置中的等离子处理的步骤的一个例子的截面图。

图5A~图5E是表示实施方式1的等离子处理装置中的等离子处理以及等离子处理以后的处理的步骤的一个例子的截面图。

图6A以及图6B是表示比较例的等离子处理装置中的预备加热处理的步骤的一个例子的截面图。

图7是表示实施方式1的变形例1的等离子处理装置所具备的静电卡盘的截面构造的图。

图8是表示实施方式1的变形例2的等离子处理装置所具备的静电卡盘的截面构造的图。

图9是表示实施方式1的变形例3的等离子处理装置所具备的静电卡盘的俯视图。

图10是实施方式1的变形例4的等离子处理装置所具备的静电卡盘的俯视图。

图11是示意地表示实施方式2的曝光装置的构成的一个例子的图。

图12是表示实施方式2的晶片卡盘的截面构造的图。

符号的说明

1…等离子处理装置,2…曝光处理装置,14p…真空泵,18…喷头,20、220、320、420、520…静电卡盘,22、622…加热器,23、623…陶瓷板,24…卡盘电极,25、225x~225z、325x~325z、525x~525y…突起部,25m、225m、325m…导电部件,25c、225c、325c…帽,26、626…弹簧部件,44…高频电源,46、48、648…电源,620…载放台,620b…晶片卡盘,625m…导热部件,625v…吸引孔。

具体实施方式

以下,参照附图对本发明进行详细说明。此外,本发明不受下述的实施方式限定。此外,下述实施方式中的构成要素,包括本领域技术人员容易想到的构成要素或者实质相同的构成要素。

[实施方式1]

以下,参照附图对实施方式1进行详细说明。

(等离子处理装置的构成例)

图1是示意地表示实施方式1的等离子处理装置1的构成的一个例子的截面图。等离子处理装置1例如构成为在晶片100上形成规定的膜的CVD(Chemical VaporDeposition)装置。

如图1所示那样,作为基板处理装置的等离子处理装置1,具备作为对晶片100进行处理的处理容器的腔室11。腔室11例如为铝制,能够气密地密封。

在腔室11的上部设置有气体供给口13。气体供给口13经由配管连接有未图示的气体供给装置,被供给对晶片100进行处理时使用的处理气体。

在气体供给口13的下方设置有作为上部电极起作用的喷头18。在喷头18,设置有沿着板厚方向贯通喷头18的多个气体喷出口18g。从气体供给口13供给的处理气体,经由气体喷出口18g导入到腔室11内。在喷头18的下方以与喷头18对置的方式配置有静电卡盘20。

作为基板支承装置的静电卡盘20为,在腔室11内将处理对象的晶片100支承为水平,并且静电地吸附晶片100,此外还作为下部电极起作用。在腔室11的侧面设置有未图示的晶片100的搬入搬出口,通过未图示的搬运臂从该搬入搬出口将晶片100载放到腔室11内的静电卡盘20上。

静电卡盘20被支承在支承部12上,该支承部12从腔室11的中央附近的底壁向铅垂上方以筒状突出。支承部12在从喷头18隔开规定距离的腔室11的中央附近,以与喷头18平行地对置的方式支承静电卡盘20。通过这种构造,喷头18与静电卡盘20构成1对平行平板电极。

此外,静电卡盘20具备对晶片100进行静电吸附的卡盘机构。卡盘机构具备作为供电板的卡盘电极24、供电线45、以及作为第1电源的电源46。卡盘电极24上经由供电线45连接有电源46。通过这种机构,从电源46向卡盘电极24供给直流电力,而使静电卡盘20的上表面静电地带电。静电卡盘20的其他内部构成将后述。

静电卡盘20连接有供电线41。供电线41上连接有隔直电容42、匹配器43以及高频电源44。在等离子处理时,从高频电源44向静电卡盘20供给规定频率的高频电力。通过这种机构,静电卡盘20还作为下部电极起作用。

在静电卡盘20的外周,以覆盖静电卡盘20的侧面以及底面的周边部的方式配置有绝缘环15。在绝缘环15的上方,以包围静电卡盘20的外周的方式设置有外周环16。外周环16将电场调整为,在晶片100的蚀刻时,电场在晶片100的周边部相对于铅垂方向、即与晶片100的表面垂直的方向不偏转。

在绝缘环15与腔室11的侧壁之间设置有档板17。档板17具有在板厚方向上贯通档板17的多个气体排出孔17e。

在腔室11的比档板17靠下部的位置设置有气体排气口14。气体排气口14连接有将腔室11内的环境气进行排气的真空泵14p。

腔室11内的由静电卡盘20及档板17与喷头18分隔出的区域,成为等离子处理室61。由喷头18分隔出的腔室11内上部的区域,成为气体供给室62。由静电卡盘20以及档板17分隔出的腔室11内下部的区域,成为气体排气室63。

等离子处理装置1具备对电源46、匹配器43、高频电源44、以及气体供给装置等的等离子处理装置1的各部分进行控制的控制部50。控制部50构成为具备未图示的CPU(Central Processing Unit)、ROM(Read Only Memory)以及RAM(Random Access Memory)等的计算机。控制部50也可以构成为具有面向等离子处理装置1用途的功能的ASIC(Application Specific Integrated Circuit)等。

在晶片100的等离子处理时,根据控制部50的控制,在静电卡盘20上载放作为处理对象的晶片100,并通过卡盘机构进行吸附。此外,通过与气体排气口14连接的真空泵14p将腔室11内抽真空。当腔室11内达到规定压力时,从未图示的气体供给装置向气体供给室62供给处理气体,并经由喷头18的气体喷出口18g向等离子处理室61供给。

此外,根据控制部50的控制,在将作为上部电极的喷头18接地的状态下,对作为下部电极的静电卡盘20施加高频电压,而使等离子处理室61内生成等离子体。在下部电极侧,由于基于高频电压的自偏压,而在等离子体与晶片100之间产生电位梯度,等离子体中的离子被向静电卡盘20加速,进行各向异性蚀刻处理。

(静电卡盘的构成例)

接下来,使用图2以及图3对静电卡盘20的详细构成进行说明。

图2是实施方式1的静电卡盘20的俯视图。如图2所示那样,静电卡盘20在上表面具备多个升降销存放孔27以及多个突起部25。

多个升降销存放孔27例如在静电卡盘20上表面的中央区域相互分离地配置,在静电卡盘20的内部分别存放未图示的升降销。在相对于腔室11搬出搬入晶片100时,使升降销从静电卡盘20上表面突出,在升降销上支承晶片100,由此在未图示的搬运臂与静电卡盘20之间进行晶片100的交接。

多个突起部25从静电卡盘20的上表面突出,并分散配置于静电卡盘20的上表面整体。更具体地说,多个突起部25例如从静电卡盘20的上表面中心部朝向外缘部以放射状配置。

静电卡盘20上表面所载放的晶片100,实质上由多个突起部25支承。由此,在静电卡盘20上表面与晶片100之间,产生突起部25的突出量的间隙。为了使静电卡盘20与晶片100之间的导热性提高,而向该间隙内流入氦气等惰性气体。

此外,图2是简化的图,突起部25例如为33个以上121个以下,且配置在静电卡盘20上。通过使突起部25的个数例如为33个以上,由此能够在多个突起部25之间分散晶片100的重量,能够缓和突起部25与晶片100抵接时的冲击。当突起部25的个数例如超过121个时,冲击缓和的效果成为大致一定。

多个突起部25的上表面形状例如为圆形。突起部25也可以具有椭圆形或者长圆型(橄榄形状)的上表面形状。此外,虽然也能够使突起部25的上表面形状成为多边形等,但为了缓和突起部25与晶片100抵接时的冲击,突起部25更优选为不具有角且带有圆度的形状。

图3是表示实施方式1的静电卡盘20的截面构造的图。在图3中,静电卡盘20的外缘部附近被放大表示。如图3所示那样,静电卡盘20作为截面构造而具有母材21、加热器22、陶瓷板23以及卡盘电极24。

母材21是静电卡盘20的主体,例如为铝制。母材21具有平坦的上表面。

作为电热板的加热器22具有规定的图案,遍及母材21上表面的大致整体配置。加热器22构成对晶片100进行加热的加热机构的一部分。即,加热机构具备加热器22、供电线47以及作为第2电源的电源48。加热器22经由供电线47而连接有向加热器22供给电力的电源48。

通过上述那样的机构,从电源48向加热器22供给交流电力而加热器22升温。由此,静电卡盘20上所载放的晶片100被加热到例如650℃以上的温度。

作为载放板的陶瓷板23,构成为隔着加热器22而覆盖母材21上表面的大致整体的平板状。陶瓷板23例如为氧化铝制或者氮化铝制的陶瓷部件。从高频电源44供给高频电力的供电线41例如与陶瓷板23的下表面连接。

陶瓷板23具有平坦的上表面。该陶瓷板23的上表面是静电卡盘20的上表面,成为供晶片100载放的载放面。在陶瓷板23的上表面设置有多个凹部23r。在各个凹部23r内,经由弹簧部件26而嵌入有上述突起部25。

作为供电板的卡盘电极24具有规定的图案,遍及陶瓷板23的大致整面地内置于陶瓷板23。

作为弹性部件的弹簧部件26例如是压缩螺旋弹簧等,具备氮化硅等陶瓷制的母材以及钨等导电性材料的被膜。但是,弹簧部件26的母材以及被膜的材质不限定于上述情况。

母材21只要是能够耐受上述加热器22进行的650℃以上的加热的耐热性材料即可。被膜只要是具有导电性以及650℃以上的耐热性的材料即可,例如优选具有3000℃以上的熔点的材料。作为被膜,除了上述钨以外,例如能够使用铂等。

上述那样的被膜例如能够通过对成型为压缩弹簧等形状的母材进行溅射处理或者无电镀处理等而形成。

突起部25构成为在内部包括由帽25c覆盖的导电部件25m,并以从陶瓷板23的上表面突出的方式由弹簧部件26支承。在导电部件25m的下表面接合有弹簧部件26。导电部件25m与弹簧部件26电导通。突起部25例如具有圆柱或者多棱柱等柱状的形状。突起部25的直径例如能够设为数mm程度,例如可以为2mm。

导电部件25m例如为钨等金属制。但是,导电部件25m只要是具有导电性以及650℃以上的耐热性的材料即可,例如优选具有3000℃以上的熔点的材料。作为导电部件25m,除了上述钨以外,例如能够使用铂等。

帽25c覆盖导电部件25m的除了下表面以外的表面。帽25c能够与陶瓷板23同样地设为例如氧化铝制或者氮化铝制的陶瓷。

通过这样的构成,在静电卡盘20上存在晶片100的情况和不存在晶片100的情况下,突起部25从陶瓷板23的突出量变化。即,当在静电卡盘20上载放晶片100时,由于晶片100的重量而上述弹簧部件26挠曲,突起部25的突出量减少。

关于突起部25的突出量,能够设为在施加了晶片100的重量等而向凹部23r内最大限度下沉的状态下为数十μm程度,例如可以为30μm。此外,优选将弹簧部件26的弹力调整为,突起部25的突出量的最大变化量例如成为数mm程度。

此外,有时在腔室11内处理的晶片100会产生翘曲。在半导体装置的制造工序中,在晶片100上形成有应力不同的各种膜,由于这些膜的应力,晶片100有时会翘曲为上凸状或者下凸状。在图3的例子中示出了载放有翘曲为下凸状的晶片100的样态。

在该情况下,越朝向静电卡盘20的中心,对突起部25施加的晶片100的重量越增加,突起部25向陶瓷板23的凹部23r内下沉越大。另一方面,在静电卡盘20的外缘部,对突起部25施加的晶片100的重量减少,与中心部相比突起部25的下沉量比较小,突起部25成为更突出的状态。

如此,通过使突起部25的突出量与晶片100的形状相对应地变化,由此遍及晶片100背面大致整体地维持突起部25接触的状态。由此,晶片100由多个突起部25的大致整体支承。

此外,通过上述构成,突起部25能够经由内部的导电部件25m以及与导电部件25m接合的弹簧部件26,将由卡盘电极26生成的静电力传递到晶片100的背面,使晶片100静电地吸附于静电卡盘20上表面。

此外,通过上述构成,突起部25能够经由内部的导电部件25m以及与导电部件25m接合的弹簧部件26,将来自加热器22的热传递到静电卡盘20上表面所载放的晶片100,对晶片100进行加热。

(等离子处理的例)

接下来,使用图4A~图5E,对实施方式1的等离子处理装置1中的晶片100的等离子处理的例子进行说明。

图4A~图4C是表示实施方式1的等离子处理装置1中的等离子处理的步骤的一个例子的截面图。图5A~图5E是表示实施方式1的等离子处理装置1中的等离子处理以及等离子处理以后的处理的步骤的一个例子的截面图。图4A~图5E的等离子处理以及其以后的处理被作为制造半导体装置的工序的一环来实施。

图4A以及图4B所示的处理是对晶片100进行预备加热的预备加热处理。

如图4A所示那样,根据控制部50的控制,将晶片100搬入到腔室11内,使升降销19上升而通过升降销19支承晶片100。在图4A的例子中,示出了具有下凸状翘曲的晶片100由升降销19支承的样态。晶片100处于从静电卡盘20上表面分离的位置,因此此时多个突起部25处于初始状态,从陶瓷板23上表面以大致最大的突出量突出。

此外,根据控制部50的控制,从电源48向加热器22供给交流电力,将加热器22例如升温到650℃以上。并且,从喷头18的气体喷出口18g向腔室11内供给处理气体或者惰性气体等。在该状态下,在静电卡盘20上方位置将晶片100维持规定时间。

由此,通过来自加热器22的放热对晶片100进行加热。此外,从气体喷出口18g供给的气体绕到晶片100的背面,通过气体也能够促进加热器22以及晶片100之间的热交换。

如图4B所示那样,在经过规定时间之后,根据控制部50的控制,使升降销19下降而存放到升降销存放孔27中。由此,晶片100被载放到静电卡盘20的陶瓷板23上。更严密地说,晶片100由从陶瓷板23上表面突出的多个突起部25支承。

晶片100例如具有下凸状翘曲,因此配置在陶瓷板23的中央附近的突起部25被施加更大的重量,弹簧部件26也更大地挠曲。因此,突起部25从陶瓷板23的突出量变小。

此外,配置在陶瓷板23的外缘部附近的突起部25仅被施加较小的重量,弹簧部件26的挠曲也变小。因此,突起部25从陶瓷板23的突出量仍维持较大的状态。

如此,根据陶瓷板23上的配置位置,突起部25的突出量变化,多个突起部25追随晶片100的背面形状。因此,在晶片100背面的大致整体维持晶片100与突起部25之间的接触。在该状态下将晶片100维持规定时间。

由此,通过来自加热器22的放热对晶片100进行加热。此外,经由弹簧部件26以及突起部25的导电部件25m,也将来自加热器22的热传递至晶片100,促进晶片100的加热。此时,晶片100背面的大致整体与多个突起部25接触,因此晶片100整体被大致均匀地加热。

如此,通过进行图4A以及图4B所示的预备加热,由此在之后的等离子处理时,能够使晶片100迅速升温到处理温度。此外,在晶片100产生翘曲的情况下,通过图4A以及图4B的预备加热,容易使晶片100软化而降低翘曲。由此,能够缓和使晶片100吸附于静电卡盘20时的冲击。

如图4C所示那样,在经过规定时间之后,根据控制部50的控制,从电源46对卡盘电极24供给直流电力,使晶片100静电吸附于陶瓷板23上。更严密地说,晶片100吸附于从陶瓷板23上表面突出的多个突起部25,在与陶瓷板23上表面之间维持若干的间隙。

由此,即使在晶片100具有翘曲的情况下,晶片100也成为大致平坦的状态地吸附在陶瓷板23上。此外,通过利用静电力来吸附晶片100,由此弹簧部件26的挠曲成为大致最大,突起部25从陶瓷板23的突出量成为大致最小。

如图5A所示那样,根据控制部50的控制,从喷头18的气体喷出口18g向腔室11内供给处理气体。此外,从高频电源44对陶瓷板23供给高频电力。由此,通过由喷头18与静电卡盘20构成的平行平板电极,在腔室11内的晶片100上方生成等离子体。

此外,根据控制部50的控制,使惰性气体等流入到晶片100背面与陶瓷板23之间的间隙中,促进加热器22与晶片100之间的热交换。

由此,腔室11内的晶片100被进行等离子处理。在图5A的例子中示出了通过等离子处理在晶片100的上表面形成有碳膜101的样态。碳膜101是通过CVD形成的有机类的膜,在半导体装置的制造工序中被用作为掩模材料等。

形成有碳膜101的晶片100被从等离子处理装置1中搬出,在其他装置中,在碳膜101上例如形成SOG膜(Spin On Glass),在SOG膜上形成抗蚀剂膜。

图5B~图5E所示的处理是等离子处理装置1中的处理结束之后的其他装置中的处理的一个例子。

如图5B所示那样,抗蚀剂膜被曝光而形成抗蚀剂图案103p,将抗蚀剂图案103p作为掩模来对SOG膜进行蚀刻处理,而形成SOG图案102p。

如图5C所示那样,将SOG图案102p作为掩模来对碳膜101进行蚀刻处理,而形成碳图案101p。通过该处理,例如抗蚀剂图案103p消失。

如图5D所示那样,将碳图案101p作为掩模对晶片100进行蚀刻处理,而在晶片100的表面形成图案100p。如图5E所示那样,碳图案101p例如被灰化除去。

通过反复进行以上那样的处理,制造半导体装置。

(比较例)

接下来,使用图6A以及图6B对比较例的等离子处理装置中的晶片100x的预备加热的一个例子进行说明。图6A以及图6B是表示比较例的等离子处理装置中的预备加热处理的步骤的一个例子的截面图。

如图6A所示那样,比较例的等离子处理装置具备静电卡盘120,该静电卡盘120具有母材121、加热器122、陶瓷板123、以及卡盘电极124。静电卡盘120的陶瓷板123在上表面上具有多个突起125。该多个突起125例如是对陶瓷板123的上表面进行印花加工而成的,具有与陶瓷板123相同的材质,且从陶瓷板123的上表面固定地突出。

在图6A所示的晶片100x的预备加热时,在晶片100x具有例如下凸状的翘曲的情况下,晶片100x的外缘部与突起部125之间维持非接触的状态。由此,晶片100x的预备加热需要较长时间,此外,晶片100x整体无法被均匀地加热,例如晶片100x的外缘部的温度仍然较低。

如图6B所示那样,在预备加热后,当对卡盘电极124供给直流电力而使晶片100x吸附于陶瓷板123时,有时晶片100x的外缘部会击打原本与晶片100x非接触的突起部125、而导致晶片100x的外缘部的背面受到较强的冲击。

由此,有时会使晶片100x背面产生损伤,此外,有时会在腔室内产生碎屑。此时,也有时晶片100x的位置会偏移而产生搬运错误。此外,当晶片100x的背面产生损伤时,除了在此以后的处理中会成为碎屑源以外,还可能成为晶片100破裂、缺损等的原因。

为了抑制由于与晶片100x摩擦而产生的损伤,例如还可以考虑使突起部由聚四氟乙烯(PTFE:Poly Tetra Fluoro Ethylene)等具有挠性的树脂形成。

然而,这样的突起部从陶瓷板123的突出量是固定的,例如对于具有翘曲的晶片100x无法得到充分的追随性。此外,例如PTFE的熔点为350℃程度,在650℃以上的高温下,突起部有可能变形或者改性。

根据实施方式的静电卡盘20,具备多个突起部25以及多个弹簧部件26。由此,在使晶片100吸附于静电卡盘20时,能够通过弹簧部件26来吸收冲击,能够抑制具有翘曲的晶片100的损伤。此外,能够使多个突起部25追随晶片100的背面形状,在对晶片100进行预备加热时,能够将晶片100整体均匀地加热。

根据实施方式的静电卡盘20,多个突起部25在内部包括导电部件25m,弹簧部件26具有将卡盘电极24与导电部件25m电连接的导电性的被膜。由此,能够与卡盘电极24电导通,而将晶片100更可靠地静电吸附于卡盘20。此外,向晶片100的热传递变得良好而能够缩短预备加热时间。

根据实施方式的静电卡盘20,多个突起部25例如以放射状分散地配置于陶瓷板23的载放面整体。由此,能够使晶片100的重量分散于多个突起部25,能够使对晶片100的冲击进一步缓和,能够抑制晶片100背面的损伤。

根据实施方式的静电卡盘20,多个突起部25以及多个弹簧部件26具有耐热性。由此,例如在650℃以上的热的情况下,也能够抑制这些突起部25以及弹簧部件26变形或者劣化。

此外,在上述实施方式1中,对晶片100具有下凸状翘曲的情况下的例子进行了说明,但实施方式1的静电卡盘20对于具有上凸状翘曲的晶片100也能够获得同样的效果。

此外,在上述实施方式1中,在等离子处理装置1中,对下部电极施加高频电力,但高频电力可以对上部电极施加,也可以对上下部电极施加。此外,等离子处理装置也可以是使用了ICP(Inductively Coupled Plasma)等其他等离子源的装置。

此外,在上述实施方式1中,等离子处理装置1是对晶片100形成规定膜的CVD装置,但不限定于此。例如,在蚀刻装置或者灰化装置等在低压下对晶片100进行处理的基板处理装置中,也能够应用上述静电卡盘20的构成。

(变形例1、2)

接下来,使用图7以及图8对实施方式1的变形例1、2的静电卡盘220、320进行说明。在变形例1、2的静电卡盘220、320中,与上述实施方式1的不同点在于,多个突起部从陶瓷板23的突出量相互不同。

图7是表示实施方式1的变形例1的等离子处理装置所具备的静电卡盘220的截面构造的图。如图7所示那样,静电卡盘220具备多个突起部225x、225y、225z。

多个突起部225x、225y、225z分别构成为在内部包括由帽225c覆盖的导电部件225m,并由弹簧部件26支承为从陶瓷板23的上表面突出。导电部件225m以及帽225c也可以由与上述实施方式1的导电部件25m以及帽25c相同的材料构成。

作为第1突起部的突起部225x配置在设置于陶瓷板23的中央区域的凹部23r内。在多个突起部225x、225y、225z中,突起部225x的纵向尺寸最短,在初始状态下从陶瓷板23的突出量最小。

突起部225y配置在设置于陶瓷板23的中央区域与外缘区域之间的凹部23r内。突起部225y的纵向尺寸长于突起部225x且短于突起部225z,在初始状态下,从陶瓷板23的突出量大于突起部225x且小于突起部225z。

作为第2突起部的突起部225z配置在设置于陶瓷板23的外缘区域的凹部23r内。在多个突起部225x、225y、225z中,突起部225z的纵向尺寸最长,在初始状态下从陶瓷板23的突出量最大。

这样的静电卡盘220能够应用于较多地处理产生了例如下凸状翘曲的晶片的等离子处理装置。在初始状态下,如上述那样,多个突起部225x、225y、225z的突出量不同,因此对下凸状的晶片的追随性进一步提高。

图8是表示实施方式1的变形例2的等离子处理装置所具备的静电卡盘320的截面构造的图。如图8所示那样,静电卡盘320具备多个突起部325x、325y、325z。

多个突起部325x、325y、325z分别构成为在内部包括由帽325c覆的导电部件325m,由弹簧部件26支承为从陶瓷板23的上表面突出。导电部件325m以及帽325c也可以由与上述实施方式1的导电部件25以及帽25c相同的材料构成。

作为第1突起部的突起部325x配置在设置于陶瓷板23的中央区域的凹部23r内。在多个突起部325x、325y、325z中,突起部325x的纵向尺寸最长,在初始状态下从陶瓷板23的突出量最大。

突起部325y配置在设置于陶瓷板23的中央区域与外缘区域之间的凹部23r内。突起部325y的纵向尺寸短于突起部325x且长于突起部325z,在初始状态下从陶瓷板23的突出量小于突起部325x且大于突起部325z。

作为第3突起部的突起部325z配置在设置于陶瓷板23的外缘区域的凹部23r内。在多个突起部325x、325y、325z中,突起部325z的纵向尺寸最短,在初始状态下从陶瓷板23的突出量最小。

这样的静电卡盘320能够应用于较多地处理产生了例如上凸状翘曲的晶片的等离子处理装置。在初始状态下,如上述那样,多个突起部325x、325y、325z的突出量不同,因此对上凸状的晶片的追随性进一步提高。

此外,多个突起部的突出量可以如上述那样以3个阶段变化,或者也可以以2个阶段或4个阶段以上变化。此外,也可以代替使多个突起部的纵向尺寸变化、或者在此基础上使弹簧部件26的纵向尺寸变化,由此使突起部的突出量变化。

(变形例3、4)

接下来,使用图9以及图10对实施方式1的变形例3、4的静电卡盘420、520进行说明。在变形例3、4的静电卡盘420、520中,多个突起部的配置或者形状与上述实施方式1不同。

图9是实施方式1的变形例3的等离子处理装置所具备的静电卡盘420的俯视图。如图9所示那样,静电卡盘420具备与上述实施方式1相同的多个突起部25。但是,多个突起部25通过与上述实施方式1不同的配置而配置于静电卡盘420的上表面。

更详细地说,多个突起部25以网格状分散配置于静电卡盘420的上表面整体。即,多个突起部25配置在格子状图案的各交叉部。

图10是实施方式1的变形例4的等离子处理装置所具备的静电卡盘520的俯视图。如图10所示那样,静电卡盘520具备多个突起部525x、525y、525z。

突起部525x例如具有圆柱或者多棱柱等柱状形状,配置于静电卡盘520上表面的中央区域。突起部525y、525z分别具有圆环状的形状,以同心圆状配置于静电卡盘520的上表面。突起部525y以包围突起部525x的方式配置于静电卡盘520上表面的中央区域与外缘区域之间。突起部525z以包围突起部525y的方式配置于静电卡盘520的外缘区域。

但是,各个突起部525x、525y、525z的数量是任意的。此外,突起部525y、525z可以如上述那样具有连续的圆环形状,或者,也可以具有断续的圆环形状、即将多个圆弧组合为圆状的形状。

这样的圆环状的突起部525y、525z,例如作为芯材而具备圆环状的未图示的导电部件。未图示的帽覆盖这些导电性部件的朝向中央区域侧的侧面、朝向外缘区域侧的侧面、以及导电部件的上表面。由此,能够将弹簧部件26与导电部件的下表面接合。

此外,在上述构成中,弹簧部件26也可以配置于各个突起部525y、525z下方的多个位置。在图10的例子中示出了如下样态:多个弹簧部件26沿着各个突起部525y、525z的周向,例如从静电卡盘520上表面的中心部朝向外缘部配置为放射状。

但是,多个弹簧部件26的配置不限定于此。此外,在各个突起部525y、525z被分割为几个圆弧的情况下,也可以在圆弧状的各个突起部525y、525z下方配置至少一个弹簧部件26。

根据变形例3、4的静电卡盘420、520,能够发挥与上述实施方式1的静电卡盘20同样的效果。

[实施方式2]

以下,参照附图对实施方式2进行详细说明。实施方式2的基板支承装置上述实施方式1的不同点在于,对晶片进行吸引吸附。

(曝光处理装置的构成例)

图11是示意地表示实施方式2的曝光处理装置2的构成的一个例子的图。

如图11所示那样,作为基板处理装置的曝光处理装置2具备照明部51、光罩载台(Reticle Stage)52、驱动装置53、57、干涉仪54、58、投影单元55、标记检测部56、载放台620、以及泵646。这些各部分由控制部650控制。

作为基板支承装置的载放台620具备主体620a以及晶片卡盘620b,将晶片100支承为能够移动。驱动装置57具备未图示的马达,使载放台620相对于晶片100在水平的X轴方向及Y轴方向、以及与晶片100垂直的Z轴方向上移动。

载放台620的位置由干涉仪58根据设置于载放台620的基准标记628来测定,测定结果被输入至驱动装置57。驱动装置57使用干涉仪58的测定结果来控制载放台620的位置。随着载放台620的移动而晶片100移动。

标记检测部56对设置于晶片100的标记Mk进行检测,并将位置信息输送至控制部650。控制部650根据位置信息对晶片100进行对准。标记检测部56例如是CCD、CMOS传感器等摄像元件。

标记检测部56的多个摄像元件对分别对应的标记Mk进行检测,控制部650根据检测到的标记Mk的位置对载放台620的位置进行调整,使晶片100的位置相对于照明部51被对准。

光罩载台52对在区域52p中描绘有电路图案的光罩52r进行支承。驱动装置53具备未图示的马达,使光罩载台52相对于晶片100至少在水平面上移动。

光罩载台52的位置由干涉仪54测定,测定结果被输入至驱动装置53。驱动装置53基于干涉仪54的测定结果来对光罩载台52的位置进行控制。随着光罩载台52的移动而光罩52r移动。

照明部51利用曝光用光对光罩52r上的区域52p的范围进行照射。投影单元55将透射了光罩52r的曝光用光投影到晶片100上的未图示的抗蚀剂膜的区域52w的范围。由此,光罩52r上所描绘的电路图案被转印到抗蚀剂膜上。

泵646经由排气口645而与载放台620连接。排气口645在载放台620的晶片卡盘620b内部分支为到达晶片100背面的多个吸引路。通过泵646对晶片100的背面进行吸引,能够将晶片100吸引吸附于晶片卡盘620b的上表面。

在具有以上构成的曝光处理装置2中对晶片100进行曝光处理,由此在晶片100上形成例如上述实施方式1的图5B所示的抗蚀剂图案103p。

(晶片卡盘的构成例)

接下来,使用图12对晶片卡盘620b的详细构成进行说明。

图12是表示实施方式2的晶片卡盘620b的截面构造的图。在图12中,晶片卡盘620b的外缘部附近被放大表示。如图12所示那样,晶片卡盘620在截面构造中具有母材621、加热器622以及陶瓷板623。

母材621是晶片卡盘620b的主体,例如为铝制。母材621具有平坦的上表面。在母材621设置有沿板厚方向贯通母材621的多个吸引路624。多个吸引路624与通向泵646的排气口645连接,并相对于母材621的上表面整体分散地配置。

作为电热板的加热器622具有规定的图案,遍及母材621上表面的大致整体配置。加热器622通过具有规定的图案而以避开母材621的吸引路624的方式配置。

加热器622构成对晶片100进行加热的加热机构的一部分。即,加热机构具备加热器622、供电线647、以及作为第3电源的电源648。加热器622经由供电线647连接有对加热器622供给电力的电源648。

通过上述那样的机构,从电源648向加热器622供给交流电力而使加热器622升温。由此,能够对晶片卡盘620b上所载放的晶片100进行加热。

作为载放板的陶瓷板623构成为隔着加热器622而覆盖母材621上表面的大致整体的平板状。陶瓷板623例如是氧化铝制或者氮化铝制的陶瓷部件。

陶瓷板623具有平坦的上表面。该陶瓷板623的上表面为晶片卡盘620b的上表面,且成为载放晶片100的载放面。在陶瓷板623的上表面设置有多个凹部623r。

各个凹部623r与设置于母材621的吸引路624连接。此外,在各个凹部623r内经由弹簧部件626而嵌入有突起部625。

作为弹性部件的弹簧部件626例如是压缩螺旋弹簧等,具备氮化硅等陶瓷制的母材、以及钨等具有导热性的材料的被膜。但是,弹簧部件626的母材以及被膜的材质不限定于上述。

母材只要是能够耐受上述加热器622的加热的耐热性材料即可。被膜只要是能够将上述加热器622的热传递至晶片100的导热性的材料即可。作为被膜,除了上述钨以外,例如能够使用铂等。此外,被膜能够与上述实施方式1的弹簧部件26的情况同样地形成。

多个突起部625从晶片卡盘620b的上表面突出,并分散地配置于晶片卡盘620b的上表面整体。更具体地说,多个突起部625分别具有圆柱或者多棱柱等柱状的形状,例如能够采用上述实施方式1以及变形例3等所示的各种配置。此时,突起部25的直径例如能够设为数mm程度,例如可以为2mm。多个突起部625也可以具有上述实施方式1的变形例4所示的同心圆状的圆环形状。

各个突起部625构成为在内部包括由帽625c覆盖的导热部件625m,由弹簧部件626支承为从陶瓷板623的上表面突出。

导热部件625m例如为钨等金属制。但是,导热部件625m只要是具有导热性以及耐热性的材料即可,例如除了铂等金属制以外,能够设为导热性的陶瓷制。弹簧部件626与导热部件625m的下表面接合。

帽625c覆盖导热部件625m的除了下表面以外的表面。帽625c与陶瓷板623同样,例如能够设为氧化铝制或者氮化铝制的陶瓷。

此外,各个突起部625具备吸引孔625v,该吸引孔625v贯通导热部件625m以及覆盖导热部件625m上表面的帽625c。由此,在晶片卡盘620b内,形成从母材621的吸引路624、经由陶瓷板623的凹部623r、弹簧部件626所内包的空隙及突起部625的吸引孔625v而到达晶片100背面的路径,能够通过泵626对晶片100进行吸引吸附。

通过这样的构成,当在晶片卡盘620b上载放有晶片100时,通过晶片100的重量而使上述弹簧部件626挠曲,突起部625的突出量减少。突起部625的突出量为,在向凹部623r内最大限度下沉的状态下能够成为数十μm程度,例如可以为30μm。此外,优选将弹簧部件626的弹力调整为,使突起部625的突出量的最大变化量例如成为数mm程度。

此外,例如即使在晶片100产生了翘曲的情况下,也能够使多个突起部625追随晶片100背面的形状地支承晶片100。在图12的例子中示出了载放有翘曲为下凸状的晶片100的样态。在这种情况下,也可以与上述实施方式1的变形例1、2同样,通过对突起部625以及弹簧部件626的至少任一个的纵向尺寸进行调整来使突起部625的突出量在陶瓷板623的中央区域与外缘区域不同。

此外,通过上述构成,突起部625能够经由设置于内部的吸引孔625v,将通过泵646的排气而产生的吸引力传递至晶片100的背面,而将晶片100吸引吸附于晶片卡盘620b上表面。

此外,通过上述构成,突起部625能够经由内部的导热部件625m以及与导热部件625m接合的弹簧部件626,将来自加热器622的热传递至晶片卡盘620上表面所载放的晶片100,对晶片100进行加热。

根据实施方式2的载放台620,能够发挥与上述实施方式1的静电卡盘20同样的效果。

此外,上述实施方式2的载放台620除了曝光处理装置2以外,例如还能够应用于压印处理装置、或者清洗处理装置等在常压下对晶片100进行处理的基板处理装置。压印处理装置是将具有电路图案的模板按压到晶片100上的抗蚀剂膜等上而形成抗蚀剂图案的装置。

此外,在一部分曝光处理装置中,有时采用在低压下对晶片100进行曝光处理的方式。对于这样的曝光处理装置,例如能够应用上述实施方式1的静电吸附式的静电卡盘20。

对本发明的几个实施方式进行了说明,但这些实施方式是作为例子提示的,不意图限定发明的范围。这些新的实施方式能够以其他各种方式来实施,在不脱离发明的主旨的范围内能够进行各种省略、置换及变更。这些实施方式及其变形包含于发明的范围及主旨,并且包含于权利要求所记载的发明及其等同的范围。

- 基板反转装置、基板处理装置及基板支撑装置以及其方法

- 基板翘曲监视装置、基板处理装置及基板翘曲监视方法

- 基板处理装置及基板处理装置的调整方法

- 基板处理装置、基板保持件以及半导体装置的制造方法

- 基板翘曲检测装置及方法和基板处理装置及方法

- 基板支承装置和包括基板支承装置的基板处理装置

- 基板支承装置、基板处理装置及基板支承方法