一种基于分组并行的数据流数字下变频方法

文献发布时间:2023-06-19 12:14:58

技术领域

本发明属于通信技术领域,具体涉及一种基于分组并行的数据流数字下变频方法。

背景技术

随着软件无线电技术的发展与应用,数字接收机在信号采集、处理与传输方面的性能大大提升,然而随着集成芯片的不断发展,模数转换器(analog to digitalconversion,ADC)的采样速率越来越高,这对后续的数据处理、传输和储存提出了新的要求。数字下变频作为接收机的核心技术之一,具有向下变频和降低采样速率等优点,是接收机提升处理速度的关键。

现有的数字下变频实现途径有专用数字下变频芯片、DSP(digital signalprocessing)技术和FPGA(field programmable gate array)技术等。FPGA在信号处理方面具有配置比较灵活、并行处理的优势,已成为工程人员首选方案。受限于FPGA的乘法器和加法器运算速度,当采样速率较低的时候,数字下变频在FPGA上能够直接实现,当采样速率非常高,达到GSPS或者更高的时候,FPGA就无法直接实现超高速数据流的数字下变频。然而随着通信技术的发展,数字接收机的处理速度势必达到几十上百GSPS,数字下变频也势必需要具有更高的处理速度,并行技术的引入可以有效解决FPGA无法直接实现超高速数据流数字下变频的问题。

发明内容

本发明的目的是为了解决FPGA无法直接对超高速数据流进行数字下变频的问题,提出了一种基于分组并行的数据流数字下变频方法。

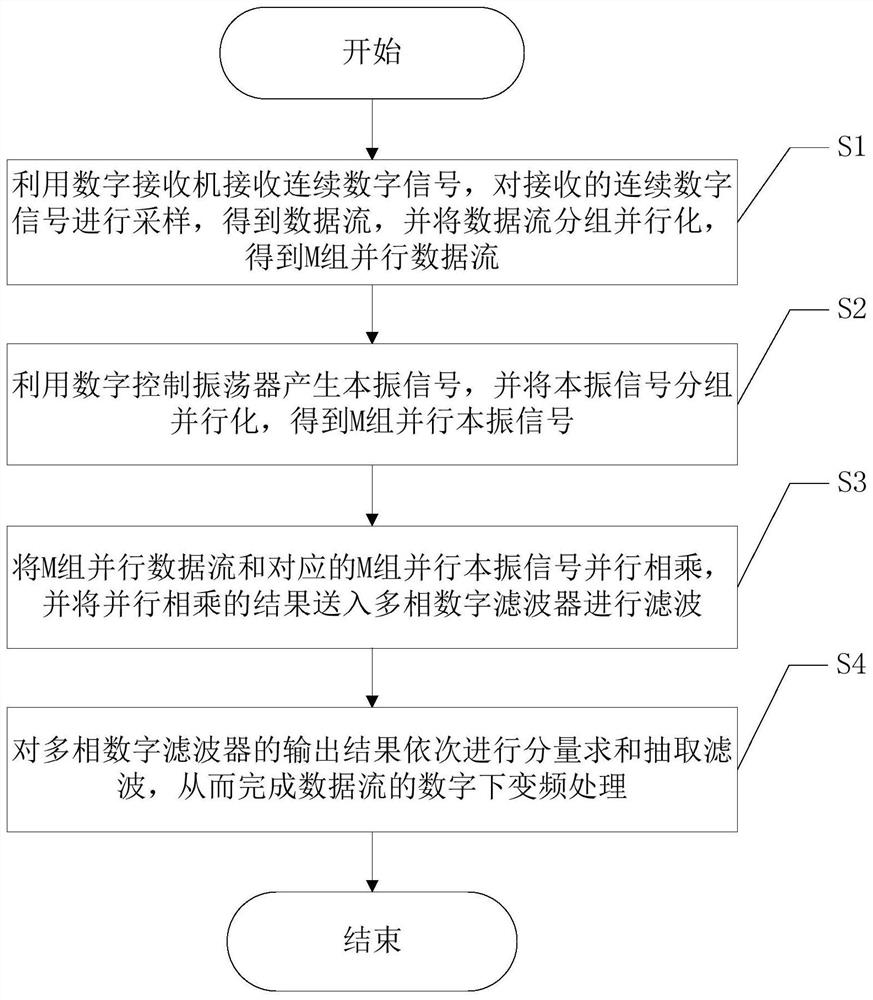

本发明的技术方案是:一种基于分组并行的数据流数字下变频方法包括以下步骤:

S1:利用数字接收机接收连续数字信号,对接收的连续数字信号进行采样,得到数据流,并将数据流分组并行化,得到M组并行数据流;

S2:利用数字控制振荡器产生本振信号,并将本振信号分组并行化,得到M组并行本振信号;

S3:将M组并行数据流和对应的M组并行本振信号并行相乘,并将并行相乘的结果送入多相数字滤波器进行滤波;

S4:对多相数字滤波器的输出结果依次进行分量求和及抽取滤波,完成数据流的数字下变频处理。

进一步地,步骤S1包括以下子步骤:

S11:利用数字接收机接收连续数字信号x(t),并对连续数字信号x(t)进行采样,得到数据流x(n);

S12:通过串并转换将数据流x(n)分组并行化,得到各支路的数字信号;

S13:将各支路的数字信号重新合成M组并行数据流x

进一步地,步骤S11中,数据流x(n)的表达式为:

其中,T

步骤S12中,令m=rM+i,将数据流x(n)分组并行化过程的计算公式为:

其其中,r表示第一设定系数,M表示分组路数,i表示数据流分组后的对应路数,x(rMT

步骤S13中,各组并行数据流x

进一步地,步骤S2包括以下子步骤:

S21:利用数字控制振荡器产生本振信号Lo(n);

S22:通过多相分解将本振信号Lo(n)分组并行化,得到各支路的本振信号;

S23:将各支路的本振信号重新合成M组并行本振信号Lo

进一步地,步骤S21中,本振信号Lo(n)的表达式为:

其中,Lo(gT

步骤S22中,令g=pM+q,p=0,1,...,M-1,将本振信号Lo(n)分组并行化过程的计算公式为:

其中,p表示第二设定系数,q表示本振信号分组后的对应路数,M表示分组路数,Lo(pMT

步骤S23中,各组并行本振信号Lo

步骤S1中超高速数据流采样率不低于1GSPS,分组路数根据输入信号采样率、所选FPGA芯片处理时钟确定;步骤S2中数字控制振荡器产生的本振信号频率和输入信号中心频率相同,分组路数和输入信号分组路数相同。

进一步地,步骤S3包括以下子步骤:

S31:利用FPGA乘法器,将M组并行数据流和对应的M组并行本振信号并行相乘,得到混频信号y(n);

S32:根据各组并行数据流x

S33:根据分组并行化的分组路数对多相数字滤波器进行多相划分,将各分支混频信号y

S34:调节子滤波器的参数,滤除各分支混频信号y

进一步地,步骤S31中,混频信号y(n)的计算公式为:

其中,x(n)表示采样数据流,Lo(n)表示本振信号,M表示分组路数,x

步骤S32中,各分支混频信号y

其中,r表示第一设定系数,p表示第二设定系数,i表示分组后的对应路数,x[r(MT

进一步地,步骤S4包括以下子步骤:

S41:根据多相数字滤波器的输出结果,对输出结果中的同相分量和正交分量进行分类,并分别对数据流进行求和;

S42:采用抽取的方式对求和后的数据流进行2倍抽取;

S43:采用FIR滤波器对2倍抽取后的数据流进行整形,得到最终基带信号,完成数据流数字下变频处理。

本发明的有益效果是:

(1)本发明考虑FPGA乘法器和加法器的运算速度,针对现有FPGA芯片无法直接对超高速的数据流进行下变频操作,设计了一种从ADC末端开始的分组并行结构,将输入信号直接进行分组划分,避免了传统多相结构通过延时抽取时抽取器的使用使整个数字下变频过程都运行在较低速率下;

(2)本发明提供了一种除数字混频正交变换结构、最小公倍数结构和二次下变频结构等结构的数字下变频新方法;方法灵活,适用于超高速采样数据流的下变频,具有很强的推广应用价值;

(3)本发明采用分组并行的方式使工作速率低于ADC的采样速率,有效缓解数字处理芯片的时钟资源压力,解决了FPGA无法直接提供与采样率相匹配的数据处理速度问题。

附图说明

图1为本发明的数据流数字下变频方法流程图;

图2为本发明中数字下变频框图;

图3为本发明中信号分组示意图;

图4为本发明中并行相乘框图。

具体实施方式

下面结合附图对本发明的实施例作进一步的说明。

如图1所示,本发明提供了一种基于分组并行的数据流数字下变频方法,包括以下步骤:

S1:利用数字接收机接收连续数字信号,对接收的连续数字信号进行采样,得到数据流,并将数据流分组并行化,得到M组并行数据流;

S2:利用数字控制振荡器产生本振信号,并将本振信号分组并行化,得到M组并行本振信号;

S3:将M组并行数据流和对应的M组并行本振信号并行相乘,并将并行相乘的结果送入多相数字滤波器进行滤波;

S4:对多相数字滤波器的输出结果依次进行分量求和及抽取滤波,从而完成数据流的数字下变频处理。

本发明具体实现框图如图2所示。本发明利用FPGA并行处理的优势,将输入的10GHz采样数据流和NCO产生的本振信号直接分组并行化为25个通道的数据流;然后把分组后的25组输入信号和25组本振信号并行相乘,实现混频,并将混频产生的50组信号送入多相数字滤波器进行低通滤波;最后分别对滤波后的同相分量、正交分量求和,并将求和后的信号进行2倍抽取滤波,得到最终数字下变频后的基带信号。

本实施例中,针对步骤S1中超高速数据流的分组并行化设计,首先考虑输入数据流采样率,根据FPGA对数字下变频的实现原则可知采样速率越大,下变频需要消耗的硬件资源就越多,当采样速率达到GHz或者更高的时候,FPGA就无法直接实现数据流的数字下变频。采用并行的处理方式,将输入信号直接分组并行化为多组低速率的信号,以此适应FPGA的最大处理速度。在本实施例中,输入采样数据流为10GHz,分组并行化路数为25,分组后每一路数据流的速率为400MHz。步骤S1包括以下子步骤:

S11:利用数字接收机接收连续数字信号x(t),并对连续数字信号x(t)进行采样,得到数据流x(n);

S12:通过串并转换将数据流x(n)分组并行化,得到各支路的数字信号;

S13:将各支路的数字信号重新合成M组并行数据流x

在本发明实施例中,步骤S11中,数据流x(n)的表达式为:

其中,T

步骤S12中,令m=rM+i,数据流x(n)的采样数据流为10GHz,对其进行分组,降低其数据率,令m=rM+i,i=0,1,...,M-1,M=25,则分组过程如下:

其中,r表示第一设定系数,M表示分组路数,i表示数据流分组后的对应路数,x(rMT

步骤S13中,本实施例中,10GHz采样率数据流x(n)通过25路分组并行,重新组合成25组并行数据流,各组并行数据流x

每一组数据流的采样速率均为400MHz,比10GHz降低了25倍,信号的分组示意图如图3所示。

在本发明实施例中,输入数据流通过与NCO产生的本振信号相乘实现混频,完成信号频谱的基带搬移,由于混频后信号的频率为f

S21:利用数字控制振荡器产生本振信号Lo(n);

S22:通过多相分解将本振信号Lo(n)分组并行化,得到各支路的本振信号;

S23:将各支路的本振信号重新合成M组并行本振信号Lo

分组后的本振信号相位为2πqf

在本发明实施例中,步骤S21中,本振信号Lo(n)的表达式为:

其中,Lo(gT

步骤S22中,令g=pM+q,p=0,1,...,M-1,将本振信号Lo(n)分组并行化过程的计算公式为:

其中,p表示第二设定系数,q表示本振信号分组后的对应路数,M表示分组路数,Lo(pMT

步骤S23中,本振信号Lo(n)通过25路分组并行,重新组合成25组并行数据流,各组并行本振信号Lo

分组后的本振信号相位为2πqf

步骤S1中超高速数据流采样率不低于1GSPS,分组路数根据输入信号采样率、所选FPGA芯片处理时钟确定;步骤S2中数字控制振荡器产生的本振信号频率和输入信号中心频率相同,分组路数和输入信号分组路数相同。

在本发明实施例中,通过分组并行的方式将输入数据流和NCO产生的本振信号分解为多个通道的低速率信号,混频方式从传统的数字正交混频变为多相的数字正交混频;并将混频后的多路信号送入多相数字滤波器,滤除混频产生的高频分量,步骤S3包括以下子步骤:

S31:利用FPGA乘法器,将M组并行数据流和对应的M组并行本振信号并行相乘,得到混频信号y(n);

S32:根据各组并行数据流x

S33:根据分组并行化的分组路数对多相数字滤波器进行多相划分,将各分支混频信号y

S34:调节子滤波器的参数,滤除各分支混频信号y

混频会将采样信号的频谱进行搬移,其中会被搬移至基带,也会以一定的间隔搬移至其他地方,但需要的是基带上的信号,因此其他位置的信号就叫高频信号,即基带外的高频信号。

在本发明实施例中,步骤S31中,混频信号y(n)的计算公式为:

其中,x(n)表示采样数据流,Lo(n)表示本振信号,M表示分组路数,x

步骤S32中,输入采样数据率为10GHz,分组路数取25,根据正交变换,混频后产生25路同相分量和25路正交分量共50组信号,并行相乘框图如图4所示,取i=0,1,...,24,各分支混频信号y

其中,r表示第一设定系数,p表示第二设定系数,i表示分组后的对应路数,x[r(MT

在本发明实施例中,将传统滤波器进行多相划分,使混频后产生的50路数据流进入多相分解后的子滤波器,每个短的子滤波器并行运行,快速高效地完成各自的滤波任务。步骤S4包括以下子步骤:

S41:根据多相数字滤波器的输出结果,对输出结果中的同相分量和正交分量进行分类,并分别对数据流进行求和;

本实施例中,经过滤波后共输出50组的数据,其中同相分量和正交分量各25组,它们分别包含了经过混频滤波后信号的实部信息和虚部信息,通过加法器分别将它们求和,即得两组数据率为400MHz的信号;

S42:采用抽取的方式对求和后的数据流进行2倍抽取;

S43:采用FIR滤波器对2倍抽取后的数据流进行整形,得到最终基带信号,完成数据流数字下变频处理。

本发明的工作原理及过程为:

本发明的有益效果为:

(1)本发明考虑FPGA乘法器和加法器的运算速度,针对现有FPGA芯片无法直接对超高速的数据流进行下变频操作,设计了一种从ADC末端开始的分组并行结构,将输入信号直接进行分组划分,避免了传统多相结构通过延时抽取时抽取器的使用使整个数字下变频过程都运行在较低速率下;

(2)本发明提供了一种除数字混频正交变换结构、最小公倍数结构和二次下变频结构等结构的数字下变频新方法;方法灵活,适用于超高速采样数据流的下变频,具有很强的推广应用价值;

(3)本发明采用分组并行的方式使工作速率低于ADC的采样速率,有效缓解数字处理芯片的时钟资源压力,解决了FPGA无法直接提供与采样率相匹配的数据处理速度问题。

本领域的普通技术人员将会意识到,这里所述的实施例是为了帮助读者理解本发明的原理,应被理解为本发明的保护范围并不局限于这样的特别陈述和实施例。本领域的普通技术人员可以根据本发明公开的这些技术启示做出各种不脱离本发明实质的其它各种具体变形和组合,这些变形和组合仍然在本发明的保护范围内。

- 一种基于分组并行的数据流数字下变频方法

- 一种基于申威众核处理器的核组内多程序多数据流分区并行的运行方法