一种MOSFET芯片的封装工艺

文献发布时间:2023-06-19 19:18:24

技术领域

本发明申请属于芯片封装技术领域,尤其涉及一种MOSFET芯片的封装工艺。

背景技术

随着电子工业的不断发展,集成电路封装技术也不断的进步,印刷电路板(Printed Circuit Board即PCB)上集成的电子器件种类和数量也越来越多,MOSFET芯片是其中的一种,为了能在电路板上集成更多的器件,因此单个器件的小型化已经成为器件封装工艺发展的必然趋势。

MOSFET芯片是指金属-氧化物半导体场效应晶体管,简称金氧半场效晶体管(Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)是一种可以广泛使用在模拟电路与数字电路的场效晶体管,传统的半导体器件MOSFET产品的封装一般是通过打线的工艺实现电性连接的,即利用铝或铜或金等引线将半导体芯片中的电极引向引脚进行焊接,从而实现电气连接,但是这样的打线工艺较为复杂,引线较多较长导致内阻较大,除了打线还有铜桥连接,即铜跳线工艺(Clip Bonding),即使用焊接到焊料的固体铜桥以实现芯片与框架或基板连接的封装工艺,铜桥是由铜片构成,铜片设计成具有高低落差的拱桥形状,封装尺寸较大,体积、厚度整体均较大,应力大,工艺复杂,故需要提供一种结构简单、成本低、可靠性高、封装尺寸小的MOSFET芯片封装结构以及实现该结构的工艺。

发明内容

为解决上述现有技术中的问题,本发明申请提供了一种MOSFET芯片的封装工艺。

为实现上述目的,本发明申请提出的一种MOSFET芯片的封装工艺,包括以下步骤:

贴片包封步骤:将芯片的A面装贴在焊盘的基岛上,芯片的B面镀上一层金属层,包封料将芯片和焊盘完全包封,封装体顶面高于与A面相对的芯片的B面;

钻孔步骤:将包封料顶面区域钻孔形成电性引出孔和电性连接孔,电性连接孔底部与芯片的B面之间间隔包封料,电性引出孔的底部与焊盘的外焊脚直接接触;

蚀刻步骤:蚀刻去除间隔的包封料,电性连接孔直接与芯片的B面上的金属层接触;

电镀并包封步骤:通过电镀技术电镀重布线层,以实现芯片与电性连接孔、电性引出孔以及外焊脚的电性连接,整体包封,并切割为单一产品。

进一步,所述贴片包封步骤中,还包括,提供一承载板,焊盘和外焊脚设置在承载板上,且焊盘与外焊脚之间填充有绝缘层,所述焊盘与外焊脚表面平整且等高,其相对于绝缘层为凸出、凹陷或者齐平。

进一步,所述贴片包封步骤中,芯片的B面的金属层为厚度≥2μm的镍、金或者铜,包封后芯片的B面到封装料顶面的厚度范围为40~80μm。

进一步,所述钻孔步骤中,通过激光钻孔形成电性引出孔和电性连接孔,钻孔后留下的间隔包封料的厚度范围为5~30μm,阻隔激光灼烧热量。

进一步,所述蚀刻步骤中,通过等离子技术整面蚀刻去除间隔的包封料。

进一步,所述电镀并包封步骤中,还包括,包封后整体形成封装体,剥离承载板,并在暴露于封装体底部的焊盘和外焊脚底面镀锡或金。

本发明申请:1、通过打孔后重布线,进一步缩小封装厚度,封装尺寸远低于C lipBonding结构、打线结构以及其他结构的封装体积和厚度,但散热性、稳定性等其他性能媲美Clip Bonding的性能,且工艺简单,不需要开发更多的设备治具;

2、通过激光钻孔和等离子蚀刻的方式相结合形成电性引出孔和电性连接孔,直接作用于芯片表层的热量大幅度减小,作业安全性和芯片稳定性更高,工艺简单,成本降低,适用于大功率和高导热芯片封装;

3、钻孔和蚀刻后的电性连接孔,彼此之间间隔塑封料,形成隔离层,可以防止芯片的Gate和Source之间电性互通,保证电性稳定。

附图说明

图1为本发明申请一种MOSFET芯片的封装工艺的贴片包封步骤中的承载板的示意图;

图2为本发明申请一种MOSFET芯片的封装工艺的贴片包封步骤中的装贴芯片的示意图;

图3为本发明申请一种MOSFET芯片的封装工艺的贴片包封步骤中的包封的示意图;

图4为本发明申请一种MOSFET芯片的封装工艺的钻孔步骤中的钻孔的示意图;

图5为本发明申请一种MOSFET芯片的封装工艺的蚀刻步骤中的蚀刻的示意图;

图6为本发明申请一种MOSFET芯片的封装工艺的电镀并包封步骤中的电镀重布线层的示意图;

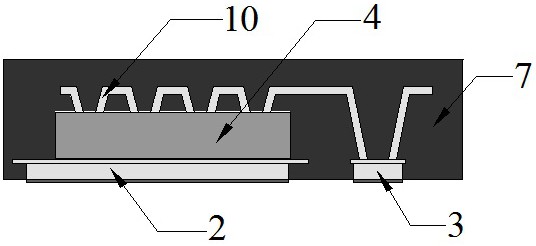

图7为本发明申请一种MOSFET芯片的封装工艺的电镀并包封步骤中的包封的示意图;

图8为本发明申请一种MOSFET芯片的封装工艺的最终成品的剖视图。

图中标记说明:承载板1、焊盘2、外焊脚3、芯片4、B面5、A面6、封装体7、电性连接孔8、电性引出孔9、重布线层10。

具体实施方式

MOSFET芯片又可以称为MOS管,根据植入的离子种类不同可以分为PMOS和NMOS,MOS管的特征有输入电阻高、噪声小、功耗低、动态范围大、易于集成、没有二次击穿现象、安全工作区域宽等优点,MOS管是电路设计中常用的功率开关器件,是压控型的,有三个电极,分别是:栅极G、源极S和漏极D,栅极G是控制端,名字为Gate,在G端加入高低电平即可控制MOS管的开断,对于NMOS而言,要求Vgs>0时,MOS管导通,否则MOS关断,对于PMOS而言,要求Vgs<0时,MOS管导通,否则MOS关断;源极S,名字为Source,对于NMOS而言,源极S是流出端,对PMOS而言,源极S是流入端,漏极D,名字为Drain,对于NMOS而言,漏极D是流入端,对于PMOS而言,源极S是流出端,本申请以NMOS为例。

MOSFET芯片封装时,需要将其的三个电极的电性引出,一般的工艺会使用打线方式引出电性,具体的工艺过程为将MOS管的无源面通过DAF胶、银浆或锡膏粘接在引线框架或者基板上,在引线框架或者基板的焊盘与MOS管的电极之间形成连接线,该连接线可以是金(Au)、铜(Cu)或铝(Al)等材质,之后将整体包封,MOS管的电性通过连接线传导后由焊盘引出封装体,打线需要更大的空间走线,整体封装尺寸较大,连接线数量和线长不等,内阻较大,电性可靠性低。

铜桥工艺中是将MOS管的无源面通过锡膏焊接在引线框架或基板上,MOS管的有源面也通过锡膏焊接铜桥,铜桥是由铜片构成,铜片设计成具有高低落差的拱桥形状,封装尺寸也较大,锡膏焊接导致热应力大,热应力与热膨胀系数有关,膨胀系数是表征物体热膨胀性质的物理量,即表征物体受热时其长度、面积、体积增大程度的物理量,热膨胀系数越高,说明在受热的状况下,自身体积膨胀变化大,热膨胀系数越大,热应力越大,即物体单位面积上所承受的力越大,查阅资料可知,硅的热膨胀系数是2.5,测定温度条件为26.85℃,铜的热膨胀系数为17.5,测定温度条件为20℃,锡的热膨胀系数为2.0,测定温度为20℃,单位均为10-6/K,因各材质纯度不同,热膨胀系在数值上数略有浮动,暂且不考虑该浮动,以测定数值为准,锡膏回流焊后剩余锡固化形成焊接,铜桥变温应力无法被锡吸收,容易造成芯片的损伤,而且回流焊需要370℃及以上的高温条件,工艺复杂,安全性低。

也有通过在MOS管电极处形成电性连接的凸起后,再进行重新布线以实现电性引出,具体的工艺流程为,先在MOS管电极处形成电性连接的凸起,可以是植球(Bump),可以是铜柱,进行包封并研磨暴露出凸起顶面,之后进行重新布线引出电路,之后再次包封将重布线组包封,为了防止电极之间的电性干扰,需要将凸起设置一定的高度,封装尺寸虽然减小,但是还有压缩的空间。

为了更好地了解本发明申请的目的、结构及功能,下面结合附图1-8,对本发明申请提出的一种MOSFET芯片的封装工艺,做进一步详细的描述。

具体包括以下步骤:

贴片包封步骤:将芯片4的A面6装贴在焊盘2的基岛上,芯片4的B面5镀上一层金属层,包封料将芯片4和焊盘2完全包封,封装体顶面高于与A面6相对的芯片4的B面5;

钻孔步骤:将包封料顶面区域钻孔形成电性引出孔9和电性连接孔8,电性连接孔8底部与芯片4的B面5之间间隔包封料,电性引出孔9的底部与焊盘2的外焊脚3直接接触;

蚀刻步骤:蚀刻去除间隔的包封料,电性连接孔8直接与芯片4的B面5上的金属层接触;

电镀并包封步骤:通过电镀技术电镀重布线层10,以实现芯片4与电性连接孔8、电性引出孔9以及外焊脚3的电性连接,整体包封,并切割为单一产品。

其中,贴片包封步骤中,请参阅附图1-附图3,还包括,提供一承载板1,该承载板1是本领域常用的基板或框架,焊盘2和外焊脚3通过电镀的方式设置在承载板1上,且焊盘2与外焊脚3之间填充有绝缘层,该绝缘层可以是环氧树脂塑封料或者其他绝缘有机物,焊盘2与外焊脚3表面平整且等高,焊盘基岛,其相对于绝缘层为凸出、凹陷或者齐平,整体形成引线框架或者预制基板,其具体的工艺流程为:S1、在基板或者框架上通过电镀工艺形成满足工艺要求的焊盘2和外焊脚3;S2、使用包封料将焊盘2和外焊脚3之间空隙填充并固化,形成绝缘层;S3、焊盘2和外焊脚3相对于周围绝缘层为凸出、凹陷或者齐平,本申请以凸出为例,焊盘2和外焊脚3表面平整;S4、在焊盘基岛表面镀金、银或其他金属,形成防氧化层。

其中,贴片包封步骤中,芯片4的B面5的金属层为厚度≥2μm的镍、金或者铜,本申请以通过溅射的方式在芯片4的B面5形成3μm的铜金属层为例,作为后续工艺中电性连接的基础,同时也在钻孔阶段和蚀刻阶段,在芯片4的B面5即有源面上形成保护,避免芯片4损坏,包封后芯片4的B面5到封装料顶面的厚度范围为40~80μm,本申请在芯片4表层(B面5)覆盖60μm厚度的封装料,此厚度范围的设定,主要既是为了后续钻孔的工作正常推进,又可以保证密封效果、节省用料。

其中,钻孔步骤中,请参阅附图4,通过激光钻孔形成电性引出孔9和电性连接孔8,电性引出孔9形成在芯片4的Source、Gate、Drain上,将芯片4电极电性引出,钻孔后留下的间隔包封料的厚度范围为5~30μm,本申请留下的间隔包封料的厚度为20μm,阻隔激光灼烧热量,同时保证后续蚀刻工艺的进行,激光钻孔为本领域常用的技术手段,而钻孔的时候会有大量的热。

其中,蚀刻步骤中,请参阅附图5,通过等离子技术整面蚀刻去除间隔的包封料,等离子蚀刻利用其蚀刻的特点,蚀刻时作用于芯片4的B面5的热量远低于激光灼烧,采用四氟化碳(CF

其中,电镀并包封步骤中,请参阅附图6-附图8,在塑封料上,芯片4的B面5金属层、电性引出孔9、电性连接孔8和外焊脚3之间通过电镀的方式进行重新布线形成重布线层10,本申请中电镀的重布线层10的材质为铜,包封后整体形成封装体7,通过机械剥离的方式剥离承载板1,此时焊盘2和外焊脚3底面外露,并在暴露于封装体7底部的焊盘2和外焊脚3底面镀锡或金等,或者进行其他防止氧化的处理,最后将整体在切割道切割为单一产品,并测试和包装,重布线层10将芯片4的电性通过电性连接孔引出后重新布局再通过电性引出孔9引出到外焊脚3,实现电性走向,同时芯片4的A面6(即无源面)通过锡膏焊接的方式粘接到焊盘2的基岛上,保证芯片4的散热效果,Mosfet的芯片4直接通过打孔后重布线,进一步缩小封装厚度,减小体积,封装尺寸远低于C lip Bonding结构、打线结构以及其他结构的封装体积和厚度,但散热性、稳定性等其他性能媲美Clip Bonding的性能,且工艺简单,不需要开发更多的设备治具。

本申请所有使用电镀工艺的步骤,均是先通过曝光、显影的光刻技术在表面形成电镀保护,之后再通过溅射或者沉铜的方式在待电镀区域形成金属种子层,本申请的金属种子层采用的是铜材质,金属种子层是为了保证后续电镀的金属与塑封料之间的结合力,同时为电镀提供导电离子附着的表面,保证电镀效果。

本申请所有使用封装工艺的步骤,均是使用塑封料注塑的方式配合模压形成封装,本申请采用的塑封料是环氧树脂塑封料,成本低,固化性能好。

本申请通过打孔后重布线,进一步缩小封装厚度,封装尺寸远低于C lip Bonding结构、打线结构以及其他结构的封装体积和厚度,但散热性、稳定性等其他性能媲美ClipBonding的性能,且工艺简单,不需要开发更多的设备治具,通过激光钻孔和等离子蚀刻的方式相结合形成电性引出孔9和电性连接孔8,直接作用于芯片表层的热量大幅度减小,作业安全性和芯片稳定性更高,工艺简单,成本降低,适用于大功率和高导热芯片封装,钻孔和蚀刻后的电性连接孔8,彼此之间间隔塑封料,形成隔离层,可以防止芯片4的Gate和Source之间电性互通,保证电性稳定。

可以理解,本发明申请是通过一些实施例进行描述的,本领域技术人员知悉的,在不脱离本发明申请的精神和范围的情况下,可以对这些特征和实施例进行各种改变或等效替换。另外,在本发明申请的教导下,可以对这些特征和实施例进行修改以适应具体的情况及材料而不会脱离本发明申请的精神和范围。因此,本发明申请不受此处所公开的具体实施例的限制,所有落入本发明申请的权利要求范围内的实施例都属于本发明申请所保护的范围内。