一种基于QSFP接口的存储微阵列设备

文献发布时间:2023-06-19 13:45:04

技术领域

本发明属于计算机领域,具体涉及一种基于QSFP接口的存储微阵列设备。

背景技术

随着信息大爆炸时代的迅速发展,信息存储技术的提升逐渐被大众重视;从磁盘存储到光盘存储、Flash存储的容量逐步增大,各种接口形式的存储介质顺势而生,SATA接口硬盘和SAS接口硬盘是主流的大容量单存储介质,但仍不满足超大信息存储的需求,将单存储单元集成在一起形成存储阵列成为趋势。

传统的存储阵列即通过堆叠大量普通接口的硬盘以实现超大容量存储的堆叠,耗费空间大小;传统的存储阵列常见的接口形式有SATA、SAS、PCIe等,各种接口只能以单独的形式出现或者通过转接线连接,接口不灵活且扩展性差;传统的存储阵列形式,譬如SATA接口,理论上读写速度仅为6Gb/s,远不能满足超高速存储的需求。

发明内容

(一)要解决的技术问题

本发明要解决的技术问题是如何提供一种基于QSFP接口的存储微阵列设备,以解决现有的存储阵列远不能满足超高速存储的需求的问题。

(二)技术方案

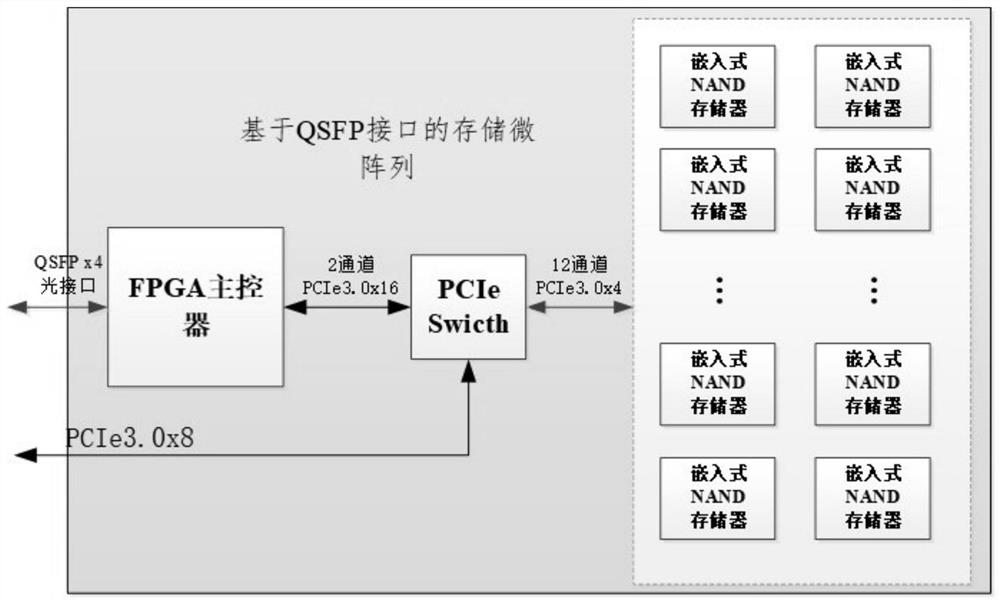

为了解决上述技术问题,本发明提出一种基于QSFP接口的存储微阵列设备,该设备包括FPGA主控器、PCIe Switch转换模块、M.2接口形式的多路嵌入式NAND存储阵列、QSFP光接口和多通道PCIe3.0接口;基于QSFP接口的存储微阵列设备的控制处理中心为FPGA主控器,通过QSFPx4光接口连接外部设备接收数据,并对数据进行处理及协议转换,FPGA主控器通过两通道的PCIe3.0x16接口连接PCIe Switch,PCIe Switch通过12通道的PCIe3.0x4接口连接嵌入式NAND存储阵列,同时,PCIe Switch通过PCIe3.0x8接口连接外部设备。

进一步地,所述嵌入式NAND存储阵列由N个M.2接口形式存储器组成,M.2接口存储器的容量及数量通过插拔的方式进行调整。

进一步地,N=12,每个NAND存储器微存储容量大小为1TB。

进一步地,FPGA主控制器前端通过四个QSFP+光模块物理接口与PC端连接,以实现PC端对基于QSFP接口的存储微阵列设备的数据传输。

进一步地,FPGA主控器由PS和主控制PL两部分组成,PS即Process ing System,实现的是ARM的SOC部分功能,PL即Programmable Logic,即实现的可编程逻辑;FPGA的PS端实现Arm功能,提供工作时钟,包括提供PCIe通信时钟、PCIe Switch转换模块时钟和QSFP+光接口时钟,同时PS端提供可扩展的千兆网络接口及UART接口;FPGA的主控制PL端实现了动态调度、收发控制、DDR控制器功能,完成对存储阵列高速读写,并通过实现RAID0高并发方式控制模块完成对DDR4数据缓存池中数据的处理。

进一步地,板载两块64bit DDR4存储器连接在FPGA主控器的PS端用作数据缓存池使用;板载QSPI Flash及EMMC Flash连接在FPGA主控器的PS端,独立于嵌入式NAND存储阵列空间,能够实时存储备份配置参数及运行参数,对关键参数实现双备份功能;FPGA使用QSPI串行加载模式,EMMC Flash用于存储FPGA的配置文件。

进一步地,该存储微阵列设备还包括POWER,POWER在基于QSFP接口的存储微阵列设备中为其他组件提供电源,模块采用“DCDC+LDO”的方式,DCDC用于大电流、大压降场合,LDO用于模拟电源轨道、小电流场合。

本发明还提供一种存储方法,该方法包括如下步骤:

S1、系统连接即存储微阵列设备上电后,PC端的远控软件通过QSFP+光接口获取到基于QSFP接口的存储微阵列设备的设备信息;

S2、系统自检,当存储微阵列设备系统连接成功后,通过自检获取基于QSFP接口的存储微阵列设备的剩余容量和基于QSFP接口的存储微阵列设备中的文件总个数;

S3、配置文件下载,系统自检完成后,通过千兆网口接收从PC端传递过来的主控FPGA的配置bin文件,并将文件转存至EMMC Flash中;

S4、配置文件加载,基于QSFP接口的存储微阵列设备通过从EMMC Flash中读取配置文件并在PS端进行加载配置;

S5、PC端通过千兆网口以NAS方式连接存储微阵列设备,查询、读写存储设备中的文件数据;

S6、高速读写包括高速写和高速读,高速写时,基于QSFP接口的存储微阵列设备通过FPGA通过向DDR写入递增数,再通过DDR经过PCIe Switch将递增数写入存储阵列,此时可通过远控软件查看写盘状态并获取写盘性能信息;高速读时,基于QSFP接口的存储微阵列的数据经过PCIe Switch写入DDR,再由FPGA通过接口读出DDR中的数据,此时可通过远控软件查看读盘状态并获取读盘性能信息;

S7、Raid0高并发存储,基于QSFP接口的存储微阵列设备在需要写入数据时,FPGA主控器的PL端实现RAID控制器功能,并通过该控制器把要写入的数据分解为多个数据块,并行写入嵌入式NAND存储阵列;读取数据时,RAID控制器并行读取分散在嵌入式NAND存储阵列中各个M.2接口硬盘上的数据,通过重新组合数据提供给读写接口。

进一步地,步骤S1中的设备信息包括设备名称、设备IP信息、设备是否就绪的状态、设备的存储空间容量和文件个数。

进一步地,所述步骤S3在存储微阵列设备第一次启动及更新设备配置文件时启用。

(三)有益效果

本发明提出一种基于QSFP接口的存储微阵列设备,与现有技术相比,本发明提出的设备中采用定制化的FPGA软件架构,通过动态调度CPU软核、软件定义互联模块、收发控制单元、NVMe Host加速模块及数据缓存池等技术实现数据传输的超大吞吐量。

采用本发明所述的M.2形式的PCIe接口的固态硬盘,具有方便拆解,容量可扩展,读写速度快的特点;通过对本发明的固态硬盘进行测试,当并行配用N块M.2形式的PCIe接口固态硬盘时,其可支持数据吞吐速率可达到N*30Gb/s;不仅如此,通过接入大容量存储颗粒,满足微存储阵列小型化大容量的需求,本发明接入的固态存储颗粒是12颗1TB容量的固态硬盘。

附图说明

图1为本发明架构设计图;

图2为本发明的硬件组成结构图;

图3为本发明的FPGA软件架构实现图。

具体实施方式

为使本发明的目的、内容和优点更加清楚,下面结合附图和实施例,对本发明的具体实施方式作进一步详细描述。

本发明的目的在于面对已有现存储阵列设备技术缺陷的情况下,提出一种存储容量大、适用于小型化/便携化场景及通过高速QSFP光接口进行读写交互的存储阵列设备。

本发明采用M.2形态接口硬盘,其具有丰富的可扩展性,可通过外接盘的形式扩展容量大小;可支持PCIe3.0硬盘接口,理论速度可达到超高速32Gb/s的超高速读写速率;通过对M.2形态接口硬盘集成嵌入式NAND存储阵列,并采用扩展的QSFP+光接口与PC端互联对接,通过传输Aurora协议数据对光电数据转换,可以进行大容量数据的高带宽传输和存储,以提高传输性能。

图1基于QSFP接口的存储微阵列设备包括FPGA主控器、PCIe Switch转换模块、M.2接口形式的多路嵌入式NAND存储器集成的存储阵列(后简称嵌入式NAND存储阵列)、QSFP光接口和多通道PCIe3.0接口。基于QSFP接口的存储微阵列设备的控制处理中心为FPGA主控器,通过QSFPx4光接口连接外部设备接收数据,并对数据进行处理及协议转换,FPGA主控器通过两通道的PCIe3.0x16接口连接PCIe Switch,PCIe Switch通过12通道的PCIe3.0x4接口连接嵌入式NAND存储阵列,同时,PCIe Swi tch通过PCIe3.0x8接口连接外部设备。数据通过QSFPx4光接口进入基于QSFP接口的存储微阵列中,并经由FPGA主控制器对数据进行处理及协议转换,然后转发至嵌入式NAND存储阵列中;在基于QSFP接口的存储微阵列中,FPGA主控器及PCIe Swi tch通过两通道的PCIe3.0x16接口连接,PCIe Switch与嵌入式NAND存储阵列通过12通道的PCIe3.0x4接口连接。

图2基于QSFP接口的存储微阵列设备主要由如下部分组成:

(1)嵌入式NAND存储阵列由N个M.2接口形式存储器组成,M.2接口存储器的容量及数量均可以通过插拔的方式进行调整,减小不必要的功耗,本设备选择N=12,每个NAND存储器微存储容量大小为1TB。

(2)FPGA主控制器前端通过四个QSFP+光接口物理接口与PC端连接,以实现PC端对基于QSFP接口的存储微阵列设备的数据传输;FPGA主控器由PS和主控制PL两部分组成,PS即Process ing System,实现的是ARM的SOC部分功能,PL即Programmable Logic,即实现的可编程逻辑;FPGA的PS端实现Arm功能,提供工作时钟,包括提供PCIe通信时钟、PCIeSwitch转换模块时钟、QSFP+光接口时钟等,同时PS端提供可扩展的千兆网络接口及UART接口等;FPGA的主控制PL端主要实现了动态调度、收发控制、DDR控制器等功能,完成对存储阵列高速读写,并通过实现RAID0高并发方式控制模块完成对DDR4数据缓存池中数据的处理。

(3)板载两块64bit DDR4存储器连接在FPGA主控器的PS端用作数据缓存池使用;板载QSPI Flash及EMMC Flash连接在FPGA主控器的PS端,独立于嵌入式NAND存储阵列空间,能够实时存储备份配置参数及运行参数,对关键参数可实现双备份功能,大大提高系统运行的可靠性,实现灵活的数据存储需求;FPGA使用QSPI串行加载模式,EMMC Flash用于存储FPGA的配置文件;板载FPGA+EMMC Flash+嵌入式NAND存储阵列可搭载自定义的文件系统,其比较与传统的基于FPGA的存储系统,具有可脱离上位机使用的特点,满足实时性要求,从文件系统级别提高设备性能。

(4)板载PCIe Swi tch模块扩展12路PCIe3.0x4接口连接嵌入式NAND存储阵列,减轻FPGA处理负担及软件工作量,降低软件开发难度。

(5)POWER在基于QSFP接口的存储微阵列设备中为其他组件提供电源,模块采用“DCDC+LDO”的方式,DCDC用于大电流、大压降场合,LDO用于模拟电源轨道、小电流场合。

图3基于QSFP接口的存储微阵列设备软件实现流程图:

S1、系统连接即存储微阵列设备上电后,PC端的远控软件通过QSFP+光接口获取到基于QSFP接口的存储微阵列设备的设备名称、设备IP信息、设备是否就绪的状态、设备的存储空间容量(总容量及已存储容量)、文件个数等信息;

S2、系统自检,当存储微阵列设备系统连接成功后,通过自检获取基于QSFP接口的存储微阵列设备的剩余容量和基于QSFP接口的存储微阵列设备中的文件总个数;

S3、配置文件下载,系统自检完成后,通过千兆网口接收从PC端传递过来的主控FPGA的配置bin文件,并将文件转存至EMMC Flash中,此过程只在设备第一次启动及更新设备配置文件时启用;

S4、配置文件加载,基于QSFP接口的存储微阵列设备通过从EMMC Flash中读取配置文件并在PS端进行加载配置;

S5、NAS(Network Attached Storage:网络附属存储)访问,即以数据为中心,分离存储设备及服务端,集成化管理数据,提高数据存储效率;PC端通过千兆网口以NAS方式连接存储微阵列设备,查询、读写存储设备中的文件数据;

S6、高速读写包括高速写和高速读,高速写时,基于QSFP接口的存储微阵列设备通过FPGA通过向DDR写入递增数,再通过DDR经过PCIe Switch将递增数写入存储阵列,此时可通过远控软件查看写盘状态并获取写盘性能信息;高速读时,基于QSFP接口的存储微阵列的数据经过PCIe Switch写入DDR,再由FPGA通过接口读出DDR中的数据,此时可通过远控软件查看读盘状态并获取读盘性能信息;

S7、Raid0高并发存储,基于QSFP接口的存储微阵列设备在需要写入数据时,FPGA主控器的PL端实现RAID控制器功能,并通过该控制器把要写入的数据分解为多个数据块,并行写入嵌入式NAND存储阵列;读取数据时,RAID控制器并行读取分散在嵌入式NAND存储阵列中各个M.2接口硬盘上的数据,通过重新组合数据提供给读写接口。

与现有技术相比,本发明提出的设备中采用定制化的FPGA软件架构,通过动态调度CPU软核、软件定义互联模块、收发控制单元、NVMe Host加速模块及数据缓存池等技术实现数据传输的超大吞吐量。

采用本发明所述的M.2形式的PCIe接口的固态硬盘,具有方便拆解,容量可扩展,读写速度快的特点;通过对本发明的固态硬盘进行测试,当并行配用N块M.2形式的PCIe接口固态硬盘时,其可支持数据吞吐速率可达到N*30Gb/s;不仅如此,通过接入大容量存储颗粒,满足微存储阵列小型化大容量的需求,本发明接入的固态存储颗粒是12颗1TB容量的固态硬盘。

以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员来说,在不脱离本发明技术原理的前提下,还可以做出若干改进和变形,这些改进和变形也应视为本发明的保护范围。