半导体装置

文献发布时间:2024-01-17 01:19:37

技术领域

本公开涉及半导体装置。

背景技术

以往,在半导体元件的电极连接有由Al(铝)构成的丝线。近年来,使用了以SiC(碳化硅)为主的半导体材料的功率半导体元件得到开发。在这种功率半导体元件中,由于流向电极的电流密度较高,在电极接合有由Cu构成的引线部件、由Cu构成的丝线来代替由Al构成的丝线。另外,在接合有由Cu构成的丝线的情况下,在电极接合有由Cu构成的板部件作为缓冲件。也就是,在这种功率半导体元件中,在电极接合有由Cu构成的连接部件。在专利文献1中,公开了一种半导体装置,其使用烧结金属来作为在半导体元件的电极接合连接部件的接合材料。在专利文献1中,在半导体元件与作为连接部件的卡夹之间配置烧结用金属材料(能够烧结的银膜),并进行烧结处理,由此将烧结用金属材料作为烧结金属(烧结银),将卡夹接合于半导体元件。在该烧结处理中,通过用加压部件将卡夹按压于半导体元件,来利用该按压力对烧结用金属材料进行加压。然后,在加压的状态下,进行烧结用金属材料的加热处理。

在多个半导体元件搭载于一个半导体装置的情况下,连接部件向各半导体元件的接合同时进行。各半导体元件以及各连接部件的厚度允许若干的误差。另外,也有在搭载有各半导体元件的基板等存在若干翘曲的情况。另外,分别配置在各半导体元件的电极与连接部件之间、以及基板与半导体元件之间的烧结用金属材料的厚度也有不均。由此,与各半导体元件接合的连接部件的上表面(与半导体元件朝向相反的一侧的面)的位置(整体的高度)存在变得不均等的情况。该情况下,在用一个加压部件按压各连接部件时,施加于各半导体元件的载荷不均匀。因此,施加有较大载荷的半导体元件有被破坏的情况。另外,一般地,半导体装置多个同时制造。因此,在仅搭载有一个半导体元件的半导体装置中,也存在如下情况,即,在伴随加压的烧结处理时,因基于高度的不均匀的载荷的偏颇,而产生半导体元件的破坏。

现有技术文献

专利文献

专利文献1:日本特表2018-504788号公报

发明内容

发明所要解决的课题

鉴于上述的事情,本公开的一个课题是提供一种半导体装置,其在伴随加压的烧结处理时,能够抑制对半导体元件施加偏颇的载荷。

用于解决课题的方案

由本公开提供的半导体装置具备第一半导体元件、第一连接部件、以及第一部件。上述第一半导体元件具有在厚度方向上相互朝向相反的一侧的第一元件主面及第一元件背面、以及配置于上述第一元件主面的第一电极。上述第一连接部件与上述第一电极导通。上述第一部件在上述厚度方向观察时与上述第一电极重叠,维氏硬度比上述第一连接部件的维氏硬度小,而且具有导电性。

发明效果

根据上述结构,在伴随加压的烧结处理时,能够抑制对半导体元件施加偏颇的载荷。

本公开的其它特征以及优点通过参照附图在以下进行的详细的说明而变得更加清楚。

附图说明

图1是表示本公开的第一实施方式的半导体装置的立体图。

图2是表示图1的半导体装置的立体图,省略了封固树脂。

图3是表示图1的半导体装置的俯视图。

图4是表示图1的半导体装置的俯视图,省略了封固树脂。

图5是放大了图4的一部分的局部放大图。

图6是表示图1的半导体装置的主视图。

图7是表示图1的半导体装置的仰视图。

图8是表示图1的半导体装置的左侧视图。

图9是表示图1的半导体装置的右侧视图。

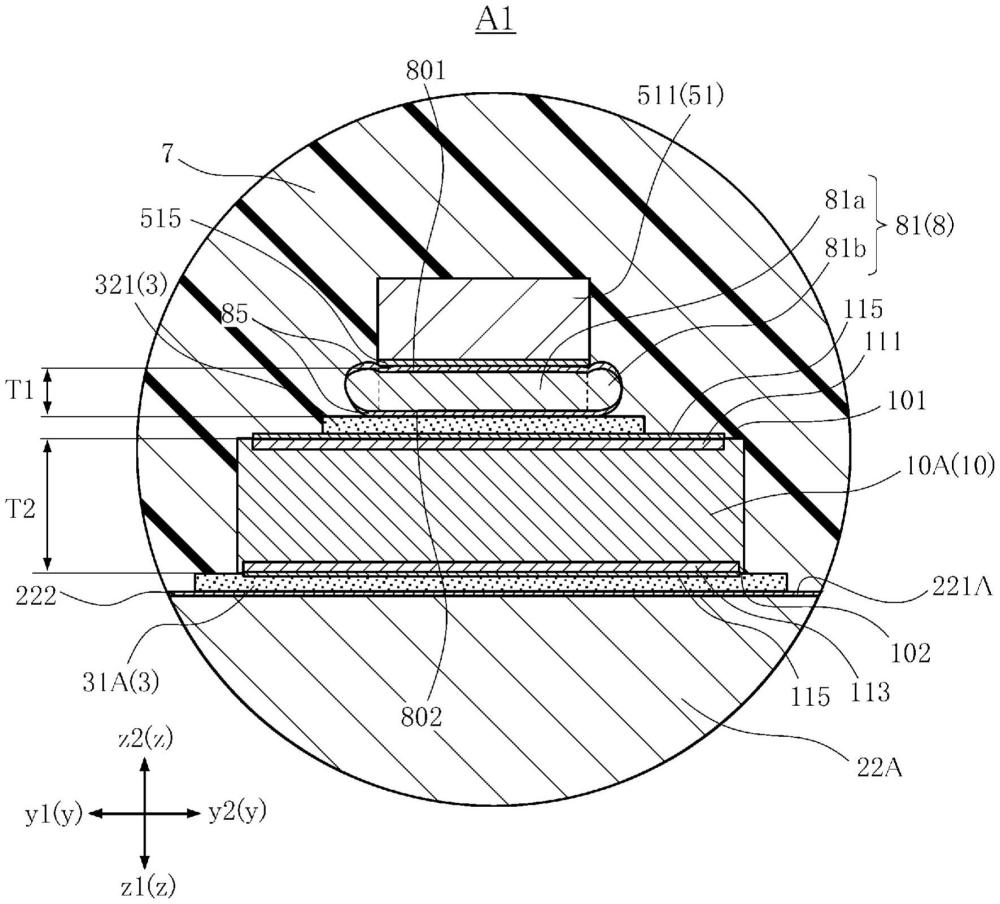

图10是表示沿图4的X-X线的剖视图。

图11是放大了图2的一部分的局部放大图。

图12是放大了图4的一部分的局部放大图。

图13是沿图12的XIII-XIII线的剖视图。

图14是放大了图4的一部分的局部放大图。

图15是沿图14的XV-XV线的剖视图。

图16A是用于说明加压加热工序的示意图,表示两个缓冲部件变形前的状态。

图16B是用于说明加压加热工序的示意图,表示一方的缓冲部件变形的状态。

图17是表示本公开的第二实施方式的半导体装置的局部放大俯视图。

图18是表示图17的半导体装置的局部放大剖视图。

图19是表示本公开的第三实施方式的半导体装置的局部放大立体图。

图20是表示图19的半导体装置的局部放大剖视图。

图21是表示本公开的第四实施方式的半导体装置的局部放大剖视图。

图22是表示本公开的第五实施方式的半导体装置的局部放大剖视图。

图23是表示本公开的第六实施方式的半导体装置的局部放大剖视图。

图24是表示本公开的第七实施方式的半导体装置的局部放大剖视图。

图25是表示本公开的第八实施方式的半导体装置的局部放大剖视图。

图26是表示本公开的第九实施方式的半导体装置的立体图。

图27是沿图26的XXVII-XXVII线的剖视图。

图28A是用于说明图26的半导体装置的制造工序中的加压加热工序的示意图,表示各缓冲部件变形前的状态。

图28B是用于说明图26的半导体装置的制造工序中的加压加热工序的示意图,表示一方的缓冲部件变形后的状态。

具体实施方式

以下,参照附图对本公开的优选的实施方式进行具体说明。

在本公开中,“某物A形成于某物B”以及“某物A形成于某物B上”,只要没有特别说明,则包含“某物A直接形成于某物B”、以及“使其它物介于某物A与某物B之间,并且某物A形成于某物B”。同样,“某物A配置于某物B”以及“某物A配置于某物B上”,只要没有特别说明,则包含“某物A直接配置于某物B”、以及“使其它物介于某物A与某物B之间,并且某物A配置于某物B”。同样,“某物A位于某物B上”,只要没有特别说明,则包含“某物A与某物B相接,某物A位于某物B上”、以及“使其它物介于某物A与某物B之间,并且某物A位于某物B上”。另外,“某物A在位于某物B的方向观察时重叠”,只要没有特别说明,则包含“某物A与某物B的全部重叠”、以及“某物A与某物B的一部分重叠”。

基于图1~图15,对本公开的第一实施方式的半导体装置A1进行说明。半导体装置A1具备多个半导体元件10、支撑基板20、多个导电性接合层3、输入端子41、42、输出端子43、一对栅极端子44A、44B、一对检测端子45A、45B、多个虚拟端子46、一对侧方端子47A、47B、绝缘部件49、多个引线部件51、多个缓冲部件8、多个丝线6、以及封固树脂7。此外,有时将输入端子41、42、输出端子43、一对栅极端子44A、44B、一对检测端子45A、45B、多个虚拟端子46、以及一对侧方端子47A、47B总称为端子40。

图1是表示半导体装置A1的立体图。图2是表示半导体装置A1的立体图,是省略了封固树脂7的图。图3是表示半导体装置A1的俯视图。图4是表示半导体装置A1的俯视图,是省略了封固树脂7的图。此外,在图4中,用想象线(双点划线)示出封固树脂7。图5是放大了图4的一部分的局部放大图。图6是表示半导体装置A1的主视图。图7是表示半导体装置A1的仰视图。图8是表示半导体装置A1的左侧视图。图9是表示半导体装置A1的右侧视图。图10是沿图4的X-X线的剖视图。图11是表示在图2所示的立体图中放大了包含引线部件51的一部分的局部放大图。此外,在图11中,省略了丝线6。图12是在图4所示的俯视图中放大了包含某半导体元件10A(后述)的一部分的局部放大图。此外,在图12中,透过引线部件51并用想象线(双点划线)来示出。图13是沿图12的XIII-XIII线的剖视图。图14是在图4所示的俯视图中放大了包含某半导体元件10B(后述)的一部分的局部放大图。此外,在图14中,透过输入端子42并用想象线(双点划线)来示出。图15是沿图14的XV-XV线的剖视图。

半导体装置A1在厚度方向观察(俯视)时的形状为矩形形状。为了便于说明,将半导体装置A1的厚度方向(俯视方向)设为z方向,将与z方向正交的沿半导体装置A1的一方的边的方向(图3以及图4中的左右方向)设为x方向,将与z方向以及x方向正交的方向(图3以及图4中的上下方向)设为y方向。另外,将z方向的一方侧(图6、图8以及图9中的下侧)设为z1侧,将另一方侧(图6、图8以及图9中的上侧)设为z2侧。将x方向的一方侧(图3以及图4中的左侧)设为x1侧,将另一方侧(图3以及图4中的右侧)设为x2侧。将y方向的一方侧(图3以及图4中的下侧)设为y1侧,将另一方侧(图3以及图4中的上侧)设为y2侧。z方向是“厚度方向”的一例。半导体装置A1的各尺寸没有限定。

多个半导体元件10分别使用以SiC(碳化硅)为主的半导体材料来构成。此外,该半导体材料不限定于SiC,也可以是Si(硅)、GaAs(砷化镓)或者GaN(氮化镓)等。另外,在本实施方式中,各半导体元件10是功率MOSFET(Metal-Oxide-Semiconductor Field-EffectTransistor,金属氧化物半导体场效应晶体管)。此外,各半导体元件10不限定于MOSFET,也可以是包含MISFET(Metal-Insulator-Semiconductor FET,金属绝缘体半导体场效应管)的场效应晶体管、IGBT(Insulated Gate Bipolar Transistor,绝缘栅双极晶体管)、双极晶体管、LSI等IC芯片。在本实施方式中,各半导体元件10均为同一元件,而且表示为n通道型的MOSFET的情况。在z方向观察(俯视)时,各半导体元件10为矩形形状。另外,在本实施方式中,各半导体元件10的厚度(z方向尺寸)为350~370μm左右,但也可以是100μm左右。此外,各半导体元件10的形状以及各尺寸没有限定。

如图10、图13、以及图15所示,各半导体元件10具有元件主面101以及元件背面102。在各半导体元件10中,元件主面101以及元件背面102在z方向上隔开间隔,而且相互朝向相反的一侧。在本实施方式中,元件主面101朝向z方向z2侧,元件背面102朝向z方向z1侧。各半导体元件10是“第一半导体元件”或者“第二半导体元件”的一例。

如图5、图11~图15所示,各半导体元件10具备源极电极111、栅极电极112、漏极电极113、以及绝缘膜13。

源极电极111以及栅极电极112配置在元件主面101。源极电极111比栅极电极112大。另外,在本实施方式中,示出了源极电极111在一个区域构成的情况,但也可以分割成多个区域。漏极电极113配置在元件背面102。在本实施方式中,漏极电极113遍及元件背面102的大致整体而形成。如图13以及图15所示,在源极电极111、栅极电极112、以及漏极电极113的表面形成有镀敷层115。在本实施方式中,镀敷层115例如由以Ni、Pd、Au的顺序层叠的多个金属镀敷层构成。此外,镀敷层115的结构没有限定。镀敷层115在最外侧形成与导电性接合层3金属结合的金属层即可。源极电极111是“第一电极”或者“第二电极”的一例。

绝缘膜13设于元件主面101。绝缘膜13具有电绝缘性。绝缘膜13在z方向观察时包围源极电极111以及栅极电极112。绝缘膜13例如是SiO

多个半导体元件10包含多个半导体元件10A以及多个半导体元件10B。在本实施方式中,半导体装置A1构成半桥型的开关电路。多个半导体元件10A构成该开关电路中的上支电路,多个半导体元件10B构成该开关电路中的下支电路。如图2以及图4所示,半导体装置A1包含四个半导体元件10A以及四个半导体元件10B。此外,半导体元件10的个数不限于本结构,能够根据半导体装置A1所要求的性能来自由设定。

如图2、图4、图5、图11~图13所示,多个半导体元件10A分别搭载于支撑基板20(后述的导电部件22A)。在本实施方式中,多个半导体元件10A在y方向上等间隔地排列,且相互隔开间隔。各半导体元件10A在搭载于导电部件22A的姿势下,元件背面102与导电部件22A对置。如图4、图5、图11~图13所示,各半导体元件10A经由导电性接合层3(后述的元件接合层31A)而与支撑基板20(导电部件22A)导通接合。

如图2、图4、图5、图14、以及图15所示,多个半导体元件10B分别搭载于支撑基板20(后述的导电部件22B)。在本实施方式中,多个半导体元件10B在y方向上等间隔地排列,且相互隔开间隔。各半导体元件10B在搭载于导电部件22B的姿势下,元件背面102与导电部件22B对置。如图4、图5、图10、图14、以及图15所示,各半导体元件10B经由导电性接合层3(后述的元件接合层31B)而与支撑基板20(导电部件22B)导通接合。

支撑基板20是支撑多个半导体元件10的支撑部件。支撑基板20具备绝缘基板21、多个导电部件22、一对绝缘层23A、23B、一对栅极层24A、24B、以及一对检测层25A、25B。

如图10所示,绝缘基板21配置有多个导电部件22。绝缘基板21具有电绝缘性。绝缘基板21的构成材料例如是热传导性优异的陶瓷。作为这样的陶瓷,例如可列举AlN(氮化铝)、SiN(氮化硅)、Al

如图10所示,绝缘基板21具有主面211以及背面212。主面211和背面212在z方向上隔开间隔,而且相互朝向相反的一侧。主面211朝向z方向z2侧,且配置有多个导电部件22。主面211与多个导电部件22以及多个半导体元件10一起被封固树脂7覆盖。背面212朝向z方向z1侧,如图7以及图10所示,从封固树脂7露出。在背面212,例如连接有未图示的散热器等。此外,绝缘基板21的结构不限定于上述的结构。例如,绝缘基板21也可以在多个导电部件22的每个单独设置。

多个导电部件22分别是金属板。该金属板的构成材料是Cu或者Cu合金。多个导电部件22与多个端子40一起构成与多个半导体元件10的导通路径。多个导电部件22相互隔开间隔,而且分别配置在绝缘基板21的主面211。各导电部件22例如通过银糊料、焊锡等那样的接合材料而与绝缘基板21的主面211接合。此外,该接合材料既可以是导电性材料、也可以是绝缘性材料。在本实施方式中,导电部件22的z方向的尺寸为0.4~3.0mm左右,但不限定于此。在本实施方式中,如图13以及图15所示,在各导电部件22的表面形成有镀敷层222。镀敷层222以与各导电部件22的表面相接的方式形成,至少覆盖搭载有半导体元件10的部分。此外,镀敷层222也可以覆盖各导电部件22的整面。在本实施方式中,镀敷层222例如含有Ag。此外,镀敷层222的材料没有限定,只要是与导电性接合层3金属结合的金属材料即可。

多个导电部件22包含导电部件22A以及导电部件22B。在本实施方式中,导电部件22A、22B在x方向上排列在绝缘基板21上。如图2、图4以及图10所示,导电部件22A配置在比导电部件22B靠x方向x2侧。导电部件22A具有朝向z方向z2侧的主面221A,在该主面221A上搭载多个半导体元件10A。导电部件22B具有朝向z方向z2侧的主面221B,在该主面221B上搭载多个半导体元件10B。在本实施方式中,导电部件22A、22B在z方向观察时均为矩形形状。此外,多个导电部件22的结构不限定于上述的结构,能够基于多个半导体元件10的个数以及配置来适当变更。导电部件22A、22B是“导电体”的一例。

一对绝缘层23A、23B具有电绝缘性,其构成材料例如是玻璃环氧树脂。如图2以及图4所示,一对绝缘层23A、23B分别是在y方向上延伸的带状。绝缘层23A与导电部件22A的主面221A接合。绝缘层23A位于比多个半导体元件10A靠x方向x2侧。绝缘层23B与导电部件22B的主面221B接合。绝缘层23B位于比半导体元件10B靠x方向x1。

一对栅极层24A、24B具有导电性,其构成材料例如是Cu。如图2以及图4所示,一对栅极层24A、24B分别是在y方向上延伸的带状。栅极层24A配置在绝缘层23A上。栅极层24A经由丝线6(后述的栅极丝线61)而与各半导体元件10A的栅极电极112导通。栅极层24B配置在绝缘层23B上。栅极层24B经由丝线6(后述的栅极丝线61)而与各半导体元件10B的栅极电极112导通。

一对检测层25A、25B具有导电性,其构成材料例如是Cu。如图2以及图4所示,一对检测层25A、25B分别是在y方向上延伸的带状。检测层25A与栅极层24A一起配置在绝缘层23A上。检测层25A在绝缘层23A上位于栅极层24A的旁边,且从栅极层24A隔开间隔。在本实施方式中,检测层25A在x方向上配置在比栅极层24A靠多个半导体元件10A的附近。因而,检测层25A位于栅极层24A的X方向x1侧。此外,栅极层24A与检测层25A在X方向上的配置也可以相反。检测层25A经由丝线6(后述的检测丝线62)而与各半导体元件10A的源极电极111导通。检测层25B与栅极层24B一起配置在绝缘层23B上。检测层25B在绝缘层23B上位于栅极层24B的旁边,且从栅极层24B隔开间隔。在本实施方式中,检测层25B在x方向上配置在比栅极层24B靠多个半导体元件10B的附近。由此,检测层25B位于栅极层24B的X方向x2侧。此外,栅极层24B与检测层25B在X方向上的配置也可以相反。检测层25B经由丝线6(后述的检测丝线62)而与各半导体元件10B的源极电极111导通。

多个基台部29分别具有电绝缘性,其构成材料例如是陶瓷。如图2以及图10所示,各基台部29与导电部件22A的主面221A接合。在本实施方式中,各基台部29在z方向观察时呈矩形形状。多个基台部29在y方向上等间隔地排列,且相互隔开间隔。各基台部29的z方向的尺寸与输入端子41的z方向的尺寸和绝缘部件49的z方向的尺寸的合计大致相同。各基台部29供输入端子42的一部分接合,并支撑该输入端子42,使输入端子42的姿势稳定。此外,半导体装置A1也可以不具备多个基台部29。

输入端子41、42分别是金属板。该金属板的构成材料是Cu或者Cu合金。在本实施方式中,输入端子41、42的z方向尺寸均为0.8mm左右,但不限定于此。如图4以及图10所示,输入端子41、42在半导体装置A1中均位于偏靠x方向x2侧。在输入端子41与输入端子42之间例如施加有电源电压。此外,也可以从未图示的电源(省略图示)对输入端子41、42直接施加电源电压。另外,也可以以夹入输入端子41、42的方式连接母线(省略图示),经由该母线施加电源电压。另外,也可以在输入端子41与输入端子42之间并列连接缓冲电路等。输入端子41是正极(P端子),输入端子42是负极(N端子)。输入端子42在z方向上相对于输入端子41以及导电部件22A双方隔开间隔地配置。

输入端子41经由导电部件22A而与多个半导体元件10A的各漏极电极113导通。如图4以及图10所示,输入端子41具备焊盘部411以及端子部412。

焊盘部411是输入端子41中被封固树脂7覆盖的部分。焊盘部411的X方向x1侧的端部成为梳齿状,且包含多个梳齿部411a。多个梳齿部411a分别与导电部件22A的主面221A导通接合。该接合方法可以是使用了激光的激光焊接的接合、也可以是超声波接合、也可以是使用了导电性接合材料的接合。

端子部412是输入端子41中从封固树脂7露出的部分。如图7、图9以及图10所示,端子部412在z方向观察时从封固树脂7向x方向x2侧延伸。

输入端子42与多个半导体元件10B的各源极电极111导通。如图4以及图10所示,输入端子42具备焊盘部421以及端子部422。

焊盘部421是输入端子42中被封固树脂7覆盖的部分。焊盘部421具备连结部421a、多个伸出部421b、以及多个突出部421c。连结部421a是在y方向上延伸的带状。连结部421a与端子部422连接。多个伸出部421b是从连结部421a朝向x方向x1侧延伸的带状。在本实施方式中,各伸出部421b从连结部421a延伸至在z方向观察时与半导体元件10B重叠。在z方向观察时,多个伸出部421b在y方向上排列,而且相互隔开间隔。各伸出部421b的朝向z方向z1侧的面的一部分与各基台部29相接,经由该各基台部29支撑于导电部件22A。多个突出部421c在各伸出部421b的前端部分(x方向x1侧的端部)中是从伸出部421b向z方向z1侧突出的部分。通过各突出部421c,消除伸出部421b与半导体元件10B在z方向上的高低差。各突出部421c经由缓冲部件8以及导电性接合层3(后述的端子接合层33)而与半导体元件10B的源极电极111导通连接。在z方向观察时,突出部421c与半导体元件10B的源极电极111重叠。在本实施方式中,如图15所示,在各突出部421c的与半导体元件10B对置的面形成有镀敷层421d。此外,镀敷层421d也可以覆盖输入端子42的其它面、也可以覆盖所有的面。在本实施方式中,镀敷层421d例如由Ag构成。此外,镀敷层421d的材料没有限定。

端子部422是输入端子42中从封固树脂7露出的部分。如图4以及图10所示,在z方向观察时,端子部422从封固树脂7向x方向x2侧延伸。端子部422在z方向观察时呈矩形形状。如图4以及图10所示,在z方向观察时,端子部422与输入端子41的端子部412重叠。端子部422相对于端子部412在z方向z2侧隔开间隔。此外,在本实施方式中,端子部422的形状与端子部412的形状相同。输入端子42是“第一连接部件的一例。

输出端子43是金属板。该金属板的构成材料例如是Cu或者Cu合金。如图2以及图4所示,输出端子43在半导体装置A1中位于偏靠x方向x1侧。输出端子43经由导电部件22B而与多个半导体元件10B的各漏极电极113导通。另外,输出端子43经由导电部件22B以及引线部件51而与多个半导体元件10A的各源极电极111导通。通过多个半导体元件10的通断而转换的电压从该输出端子43输出。如图2以及图4所示,输出端子43具备焊盘部431以及端子部432。

焊盘部431是输出端子43中被封固树脂7覆盖的部分。焊盘部431的X方向x2侧的部分成为梳齿状,且包含多个梳齿部431a。多个梳齿部431a分别与导电部件22B的主面221B导通接合。该接合方法可以是使用了激光的激光焊接的接合、也可以是超声波接合、也可以是使用了导电性接合材料的接合。

端子部432是输出端子43中从封固树脂7露出的部分。如图3、图6、图7、图8以及图10所示,端子部432从封固树脂7向x方向x1侧伸出。

如图1~图7所示,一对栅极端子44A、44B在y方向上位于各导电部件22A、22B的旁边。在栅极端子44A施加有用于使多个半导体元件10A驱动的栅极电压。在栅极端子44B施加有用于使多个半导体元件10B驱动的栅极电压。

如图4以及图5所示,一对栅极端子44A、44B均具备焊盘部441以及端子部442。在各栅极端子44A、44B中,焊盘部441被封固树脂7覆盖。由此,各栅极端子44A、44B支撑于封固树脂7。此外,也可以在焊盘部441的表面实施例如银镀敷。端子部442与焊盘部441连接,而且从封固树脂7露出。端子部442在x方向观察时呈L字状。

如图1~图7所示,一对检测端子45A、45B在x方向上位于一对栅极端子44A、44B的旁边。由检测端子45A检测施加于多个半导体元件10A的各源极电极111的电压。由检测端子45B检测施加于多个半导体元件10B的各源极电极111的电压。

如图4以及图5所示,一对检测端子45A、45B均具备焊盘部451以及端子部452。在各检测端子45A、45B中,焊盘部451被封固树脂7覆盖。由此,各检测端子45A、45B支撑于封固树脂7。此外,也可以在焊盘部451的表面实施例如银镀敷。端子部452与焊盘部451连接,而且从封固树脂7露出。端子部452在x方向上观察呈L字状。

如图1~图7所示,多个虚拟端子46在x方向上相对于一对栅极端子44A、44B位于与一对检测端子45A、45B相反的一侧。在本实施方式中,虚拟端子46的个数是六个。其中三个虚拟端子46位于x方向的一方侧(x方向x2侧)。剩余的三个虚拟端子46位于x方向的另一方侧(x方向x1侧)。此外,多个虚拟端子46不限定于上述的结构。另外,半导体装置A1也可以是不具备多个虚拟端子46的结构。

如图4以及图5所示,多个虚拟端子46分别具备焊盘部461以及端子部462。在各虚拟端子46中,焊盘部461被封固树脂7覆盖。由此,多个虚拟端子46支撑于封固树脂7。此外,也可以在焊盘部461的表面实施例如银镀敷。端子部462与焊盘部461连接,而且从封固树脂7露出。端子部462在x方向上观察呈L字状。此外,端子部462的形状与一对栅极端子44A、44B的各端子部442的形状、以及一对检测端子45A、45B的各端子部452的形状相同。

如图4所示,在z方向观察时,一对侧方端子47A、47B与封固树脂7的y方向y1侧的端部重叠。另外,侧方端子47A与封固树脂7的X方向x2侧的端部重叠,侧方端子47B与封固树脂7的X方向x1侧的端部重叠。侧方端子47A与导电部件22A接合,除了朝向x方向x2侧的端面以外,被封固树脂7覆盖。侧方端子47B与导电部件22B接合,除了朝向x方向x1侧的端面以外,被封固树脂7覆盖。在本实施方式中,在z方向观察时,各侧方端子47A、47B的全部与封固树脂7重叠。各侧方端子47A、47B的接合方法可以是激光焊接的接合、也可以是超声波接合、也可以是使用了导电性接合材料的接合。各侧方端子47A、47B中,一部分在z方向观察时屈曲,另外,其它一部分在z方向上屈曲。此外,各侧方端子47A、47B的结构不限定于此。例如,在z方向观察时,也可以从封固树脂7分别延伸至突出。另外,半导体装置A1也可以不具备各侧方端子47A、47B。

如图1~图7所示,在z方向观察时,一对栅极端子44A、44B、一对检测端子45A、45B以及多个虚拟端子46沿x方向排列。在半导体装置A1中,一对栅极端子44A、44B、一对检测端子45A、45B、多个虚拟端子46以及一对侧方端子47A、47B均由同一引线框形成。

绝缘部件49具有电绝缘性,其构成材料例如是绝缘纸等。绝缘部件49的一部分是平板,如图6、图9以及图10所示,在z方向上被输入端子41的端子部412与输入端子42的端子部422所夹。在z方向观察时,输入端子41的全部与绝缘部件49重叠。另外,在z方向观察时,输入端子42的焊盘部421的一部分和端子部422的全部与绝缘部件49重叠。通过绝缘部件49,两个输入端子41、42相互绝缘。绝缘部件49的一部分(x方向x1侧的部分)被封固树脂7覆盖。

如图10所示,绝缘部件49具备夹设部491以及伸出部492。在z方向上,夹设部491介于输入端子41的端子部412与输入端子42的端子部422之间。夹设部491的全部被端子部412与端子部422所夹。伸出部492从夹设部491比端子部412以及端子部422更进一步朝向x方向x2侧延伸。

多个引线部件51分别与不同的半导体元件10A的源极电极111导通。各引线部件51使半导体元件10A的源极电极111与导电部件22B导通连接。在z方向观察时,各引线部件51是在x方向上延伸的矩形形状。各引线部件51是板状的连接部件。各引线部件51具备第一接合部511、第二接合部512以及连络部513。

第一接合部511是经由缓冲部件8以及导电性接合层3(后述的引线接合层321)而与半导体元件10A的源极电极111导通连接的部分。在z方向观察时,第一接合部511与半导体元件10A的源极电极111重叠。在本实施方式中,如图13所示,在第一接合部511的与半导体元件10A对置的面形成有镀敷层515。此外,镀敷层515也可以覆盖引线部件51的其它面,也可以覆盖所有的面。在本实施方式中,镀敷层515例如由Ag构成。此外,镀敷层515的材料没有限定。在本实施方式中,第一接合部511的z方向的尺寸(厚度)为160~200μm左右。此外,第一接合部511的厚度不限定于此。

第二接合部512是经由导电性接合层3(后述的引线接合层322)而与导电部件22B接合的部分。在本实施方式中,在第二接合部512的与导电部件22B对置的面也形成有镀敷层515。第二接合部512的厚度比第一接合部511的厚度大。在本实施方式中,第二接合部512的z方向的尺寸(厚度)为500~700μm左右。此外,第二接合部512的厚度不限定于此。

连络部513是与第一接合部511和第二接合部512连接的部分。连络部513的朝向z方向z1侧的面与封固树脂7相接。连络部513的厚度与第一接合部511的厚度相同,为160~200μm左右。此外,连络部513的厚度不限定于此。引线部件51是“第一连接部件”或者“第二连接部件”的一例。

在后述的加压加热工序中,多个缓冲部件8自身变形为对各半导体元件10的载荷变得均等。多个缓冲部件8包含多个缓冲部件81以及多个缓冲部件82。如图12以及图13所示,多个缓冲部件81分别介于半导体元件10A的源极电极111与引线部件51的第一接合部511之间。在z方向观察时,多个缓冲部件81与半导体元件10A的源极电极111重叠。如图14以及图15所示,多个缓冲部件82分别介于半导体元件10B的源极电极111与输入端子42的各突出部421c之间。在z方向观察时,多个缓冲部件82与半导体元件10B的源极电极111重叠。在不区别地说明缓冲部件81和缓冲部件82的情况下,记载为缓冲部件8。

如图13以及图15所示,各缓冲部件8具有主面801以及背面802。主面801以及背面802在z方向上隔开间隔,而且相互朝向相反的一侧。在本实施方式中,主面801朝向z方向z2侧,与引线部件51的第一接合部511或者输入端子41的各突出部421c对置。背面802朝向z方向z1侧,与半导体元件10的源极电极111对置。在主面801以及背面802的整面形成有镀敷层85。镀敷层85形成为与主面801或者背面802相接。在本实施方式中,镀敷层85例如由Ag构成。如图13所示,缓冲部件81与引线部件51的第一接合部511通过形成于缓冲部件81的主面801的镀敷层85(Ag)和形成于第一接合部511的镀敷层515(Ag)的固相扩散接合来接合。另外,如图15所示,缓冲部件82与输入端子42的突出部421c通过形成于缓冲部件82的主面801的镀敷层85(Ag)和形成于突出部421c的镀敷层421d(Ag)的固相扩散接合来接合。另外,如图13以及图15所示,缓冲部件8与半导体元件10的源极电极111通过导电性接合层3而接合。缓冲部件8与第一接合部511或者突出部421c也可以通过导电性接合层3而接合。此外,镀敷层85的材料没有限定。

各缓冲部件8的维氏硬度比各引线部件51以及输入端子41的维氏硬度小,且具有导电性。在本实施方式中,各引线部件51以及输入端子41的构成材料为Cu,因此各缓冲部件8由作为维氏硬度比Cu小的材料的Al构成。在此,维氏硬度(单位:HV)是表示硬度的尺度,是利用试验载荷将由金刚石构成的金字塔形的压头推入到材料表面,用所形成的凹陷的表面面积除以试验载荷得到的值。此外,各缓冲部件8的构成材料没有限定,只要维氏硬度比各引线部件51以及输入端子41小即可。各缓冲部件8的维氏硬度优选为50HV以下且1HV以上,例如也可以为Sn、In、Zn等。在加压加热工序中,在各引线部件51或者输入端子42被按压于半导体元件10时,各缓冲部件8自身变形,从而不会对半导体元件10施加偏颇的载荷。

图16A以及图16B是用于说明在加压加热工序中,缓冲部件8自身变形,从而使对各半导体元件10的载荷变得均等的状态的示意图。图16A表示搭载于导电部件22A的两个半导体元件10A、分别与各半导体元件10A导通连接的引线部件51、以及分别配置在半导体元件10A与引线部件51之间的缓冲部件81。各缓冲部件81在该阶段还未变形。左侧的半导体元件10A比右侧的半导体元件10A厚,另外,比配置在与导电部件22A之间的导电性接合层3的厚度厚。因此,从导电部件22A的主面221A至引线部件51的上表面(与半导体元件10A朝向相反的一侧的面)的高度中,左侧比右侧高。

图16B表示加压部件90按压各引线部件51来进行加压的状态。配置于左侧的半导体元件10A之上的缓冲部件81通过加压而变形,成为压瘪的形状。由此,该缓冲部件8的厚度变薄,从导电部件22A的主面221A至引线部件51的上表面的高度中,右侧与左侧成为相同程度。由此,施加于左侧的半导体元件10A的载荷与施加于右侧的半导体元件10A的载荷成为相同程度,对两个半导体元件10A均等地施加载荷。

存在多个缓冲部件8均未变形而维持加压加热工序之前的形状的情况。另一方面,存在多个缓冲部件8的任一个都在加压加热工序中变形的情况。图12以及图13表示变形的缓冲部件81。在本实施方式中,在z方向观察时,变形前的缓冲部件81的形状是与引线部件51的第一接合部511相同程度的大小的矩形形状。如图12所示,在z方向观察时,该缓冲部件81是因加压被压瘪而具有外形线呈曲线状鼓出的部分的形状。另外,如图13所示,剖面成为与z方向正交的方向的两端呈圆弧状地向外方突出的形状。如图12以及图13所示,该缓冲部件81具备第一部81a以及第二部81b。在z方向观察时,第一部81a是与引线部件51重叠的部分。第二部81b是与第一部81a连接且在z方向观察时从引线部件51突出的部分。在图11以及图12中,对第二部81b标注有影线。在图13中,用虚线示出了第一部81a与第二部81b的边界。

图14以及图15表示变形后的缓冲部件82。在本实施方式中,在z方向观察时,变形前的缓冲部件82的形状是与输入端子41的各突出部421c相同程度的大小的矩形形状。如图14所示,在z方向观察时,该缓冲部件82是因加压被压瘪而具有外形线呈曲线状鼓出的部分的形状。另外,如图15所示,剖面成为与z方向正交的方向的两端呈圆弧状地向外方突出的形状。如图14以及图15所示,该缓冲部件82具备第一部82a以及第二部82b。在z方向观察时,第一部82a是与输入端子42重叠的部分。第二部82b是与第一部82a连接且在z方向观察时从输入端子42突出的部分。在图14中,对第二部82b标注有影线。在图15中,用虚线示出了第一部82a与第二部82b的边界。

如图13以及图15所示,缓冲部件8的厚度(z方向的尺寸)T1为半导体元件10的厚度(z方向的尺寸)T2的10%以上且30%以下。未变形的(变形之前的)缓冲部件8的厚度T1也为厚度T2的10%以上且30%以下。若厚度T1过小,则无法通过变形来使载荷均等化。另一方面,从抑制所需的材料的观点出发,不需要使厚度T1过大。在本实施方式中,厚度T2为350~370μm左右,因此将未变形的(变形之前的)缓冲部件8的厚度T1设为50~100μm左右。此外,厚度T1没有限定,可适当设定。由于厚度T1需要某种程度的大小,因此在厚度T2较小的情况(例如100μm左右的情况)下,厚度T1设定为厚度T2的50~100%左右。各缓冲部件8是“第一部件”或者“第二部件”的一例。

多个导电性接合层3分别由通过烧结处理而形成的烧结金属构成。在本实施方式中,各导电性接合层3的构成材料例如是烧结银。此外,各导电性接合层3的构成材料不限定于此,也可以是烧结铜等其它烧结金属。各导电性接合层3是具有多个细微孔的多孔质,在本实施方式中,该细微孔设为空隙,但也可以在该细微孔填充有例如环氧树脂。即,各导电性接合层3也可以是含有环氧树脂的烧结金属。但是,若环氧树脂的含有量较多,则使导电性接合层3的导电性下降,考虑半导体装置A1中的电流量来设定环氧树脂的含有量。导电性接合层3通过对烧结用金属材料进行烧结处理来形成。此外,在本实施方式中,各导电性接合层3例如如图13以及图15所示那样示出了剖面成为矩形形状的情况,但也可以是台形状、侧方也可以弯曲、也可以形成有圆角。

在本实施方式中,多个导电性接合层3包含多个元件接合层31A、31B、多个引线接合层321、322、以及多个端子接合层33。

多个元件接合层31A分别用于将各半导体元件10A接合于导电部件22A。如图13所示,各元件接合层31A介于各半导体元件10A的元件背面102与导电部件22A之间,使该半导体元件10A的漏极电极113与导电部件22A导通。各元件接合层31A的厚度为30~100μm左右。此外,各元件接合层31A的厚度不限定于此。

多个元件接合层31B分别用于将各半导体元件10B接合于导电部件22B。如图15所示,各元件接合层31B介于各半导体元件10B的元件背面102与导电部件22B之间,使该半导体元件10B的漏极电极113与导电部件22B导通。各元件接合层31B的厚度与各元件接合层31A同样,为30~100μm左右。此外,各元件接合层31B的厚度不限定于此。元件接合层31A、31B是“第二导电性接合层”的一例。

多个引线接合层321、322分别用于接合各引线部件51。

如图11~图13所示,多个引线接合层321分别用于将接合于各引线部件51的第一接合部511的缓冲部件81接合于各半导体元件10A的源极电极111。各引线接合层321介于各半导体元件10A的源极电极111与各引线部件51的第一接合部511之间,使该半导体元件10A的源极电极111与该引线部件51导通。各引线接合层321的厚度为30~100μm左右。此外,各引线接合层321的厚度不限定于此。引线接合层321是“导电性接合层”的一例。

如图11所示,多个引线接合层322分别用于将各引线部件51的第二接合部512接合于导电部件22B。各引线接合层322介于各引线部件51的第二接合部512与导电部件22B的一部分之间,使该引线部件51与导电部件22B导通。各引线接合层322的厚度为30~100μm左右。此外,各引线接合层322的厚度不限定于此。

如图14以及图15所示,多个端子接合层33分别用于将接合于输入端子42的各突出部421c的缓冲部件82接合于各半导体元件10B的源极电极111。各端子接合层33介于各半导体元件10B的源极电极111与输入端子42的各突出部421c之间,使该半导体元件10B的源极电极111与输入端子42导通。各端子接合层33的厚度为30~100μm左右。此外,各端子接合层33的厚度不限定于此。端子接合层33是“导电性接合层”的一例。

多个丝线6分别是所谓的接合引线。各丝线6具有导电性,其构成材料例如为Al(铝)、Au(金)、Cu的任一种。在本实施方式中,如图4以及图5所示,多个丝线6包含多个栅极丝线61、多个检测丝线62、一对第一连接丝线63以及一对第二连接丝线64。

如图4以及图5所示,多个栅极丝线61各自的一端与各半导体元件10的栅极电极112接合,其另一端与一对栅极层24A、24B的任一个接合。多个栅极丝线61使各半导体元件10A的栅极电极112与栅极层24A导通,以及使各半导体元件10B的栅极电极112与栅极层24B导通。

如图4以及图5所示,多个检测丝线62各自的一端与各半导体元件10的源极电极111接合,其另一端与一对检测层25A、25B的任一个接合。多个检测丝线62使各半导体元件10A的源极电极111与检测层25A导通,以及使各半导体元件10B的源极电极111与检测层25B导通。

如图4以及图5所示,一对第一连接丝线63的一方将栅极层24A与栅极端子44A连接,其另一方将栅极层24B与栅极端子44B连接。一方的第一连接丝线63的一端与栅极层24A接合,另一端与栅极端子44A的焊盘部441接合,使栅极层24A与栅极端子44A导通。另一方的第一连接丝线63的一端与栅极层24B接合,另一端与栅极端子44B的焊盘部441接合,使栅极层24B与栅极端子44B导通。

如图4以及图5所示,一对第二连接丝线64的一方将检测层25A与检测端子45A连接,其另一方将检测层25B与检测端子45B连接。一方的第二连接丝线64的一端与检测层25A接合,另一端与检测端子45A的焊盘部451接合,使检测层25A与检测端子45A导通。另一方的第二连接丝线64的一端与检测层25B接合,另一端与检测端子45B的焊盘部451接合,使检测层25B与检测端子45B导通。

如图1、图3、图4、图6~图10所示,封固树脂7覆盖多个半导体元件10、支撑基板20的一部分、多个导电性接合层3、各端子40的各一部分、多个引线部件51、多个丝线6。封固树脂7的构成材料例如是环氧树脂。如图1、图3、图4、图6~图10所示,封固树脂7具有树脂主面71、树脂背面72以及多个树脂侧面731~734。

树脂主面71以及树脂背面72在z方向上隔开间隔,而且相互朝向相反的一侧。树脂主面71朝向z方向z2侧,树脂背面72朝向z方向z1侧。如图7所示,树脂背面72在z方向观察时是包围绝缘基板21的背面212的框状。绝缘基板21的背面212从该树脂背面72露出。多个树脂侧面731~734分别与树脂主面71以及树脂背面72双方连接,而且在z方向上被它们所夹。在本实施方式中,树脂侧面731、732在x方向上隔开间隔,而且相互朝向相反的一侧。树脂侧面731朝向x方向x2侧,树脂侧面732朝向x方向x1侧。另外,树脂侧面733、734在y方向上隔开间隔,而且相互朝向相反的一侧。树脂侧面733朝向y方向y2侧,树脂侧面734朝向y方向y1侧。

在本实施方式中,如图6、图7以及图10所示,封固树脂7分别具有从树脂背面72沿z方向凹陷的多个凹部75。此外,封固树脂7也可以不具备这些凹部75。多个凹部75分别在y方向上延伸,在z方向观察时,从树脂背面72的y方向y1侧的端缘连接至y方向y2侧的端缘。在本实施方式中,在z方向观察时,多个凹部75隔着绝缘基板21的背面212而在x方向上分别各形成有三个。

以下,对第一实施方式的半导体装置A1的制造方法进行说明。

首先,准备支撑基板20。在准备支撑基板20的工序(支撑基板准备工序)中,在绝缘基板21上相互隔开间隔地接合多个导电部件22(导电部件22A、22B)。并且,在导电部件22A、22B上接合一对绝缘层23A、23B、一对栅极层24A、24B、一对检测层25A、25B、以及多个基台部29。

接着,准备多个引线部件51。在准备引线部件51的工序(引线准备工序)中,通过在构成材料为Cu或者Cu合金的金属板例如进行轧制等的金属加工来形成引线部件51。接着,在各引线部件51形成镀敷层515。并且,在各引线部件51的第一接合部511接合形成有镀敷层85的缓冲部件81。该接合通过形成于缓冲部件81的主面801的镀敷层85(Ag)与形成于第一接合部511的镀敷层515(Ag)的固相扩散接合来进行。

接着,形成多个烧结用金属材料301。各烧结用金属材料301成为元件接合层31A、31B的基础。在本实施方式中,作为各烧结用金属材料301,使用糊料状的烧结用银。该糊料状的烧结用银是在溶剂中混合微米尺寸或者纳米尺寸的银粒子而成的结构。在本实施方式中,烧结用银的溶剂不含环氧树脂(或者几乎不含)。在形成烧结用金属材料301的工序(第一烧结用金属材料形成工序)中,例如通过使用了掩模的丝网印刷,将各烧结用金属材料301涂敷在导电部件22A、22B上。此外,涂敷在导电部件22A上的各烧结用金属材料301之后成为半导体装置A1的元件接合层31A,涂敷在导电部件22B上的各烧结用金属材料301之后成为半导体装置A1的元件接合层31B。多个烧结用金属材料301的形成方法不限定于上述的丝网印刷。例如,也可以利用分配器来涂敷烧结用金属材料301。所涂敷的烧结用金属材料301的厚度为50~110μm左右。

接着,进行多个烧结用金属材料301的干燥处理。在进行该干燥处理的工序(干燥工序)中,以大致130℃的温度对各烧结用金属材料301加热大致20min。此外,加热条件不限定于此。由此,各烧结用金属材料301的溶剂气化。

接着,在烧结用金属材料301上分别逐个搭载半导体元件10A、10B的任一个。具体而言,在形成于导电部件22A上的烧结用金属材料301上分别逐个载置半导体元件10A,在形成于导电部件22B上的烧结用金属材料301上分别逐个载置半导体元件10B。在搭载半导体元件10A、10B的工序(安装工序)中,在导电部件22A与半导体元件10A的元件背面102对置的姿势下,将各半导体元件10A载置于导电部件22A上。另外,在导电部件22B与半导体元件10B的元件背面102对置的姿势下,将各半导体元件10B载置于导电部件22B上。

接着,在多个半导体元件10A、10B的源极电极111以及导电部件22B之上分别形成烧结用金属材料302。烧结用金属材料302成为引线接合层321、322以及端子接合层33的基础。在本实施方式中,作为各烧结用金属材料302,使用预成型状的烧结用银。该预成型状的烧结用银例如在对上述的糊料状的烧结用银进行干燥处理之后形成为预定的形状。此外,预成型状的烧结用银也可以在形成为预定的形状之后进行干燥处理。在形成烧结用金属材料302的工序(第二烧结用金属材料形成工序)中,在多个半导体元件10A、10B的源极电极111以及导电部件22B之上分别逐个载置多个烧结用金属材料302。此外,形成于各半导体元件10A的源极电极111上的各烧结用金属材料302之后成为半导体装置A1的引线接合层321,形成于导电部件22B上的各烧结用金属材料302之后成为半导体装置A1的引线接合层322。另外,形成于各半导体元件10B的源极电极111上的各烧结用金属材料302之后成为半导体装置A1的端子接合层33。载置的烧结用金属材料302的厚度为50~110μm左右。

接着,使用在上述引线准备工序中准备的、在第一接合部511接合有缓冲部件81的引线部件51,将各半导体元件10A与导电部件22B连接。在由该引线部件51连接的工序(连接工序)中,在z方向观察时,以第一接合部511以及缓冲部件81与形成于半导体元件10A的源极电极111上的烧结用金属材料302重叠、而且第二接合部512与形成于导电部件22B上的烧结用金属材料302重叠的方式,配置引线部件51。

接着,接合多个端子40。在输入端子41的接合中,将梳齿部411a接合于导电部件22A的主面221A。该接合既可以是利用了激光焊接的接合、也可以是超声波接合。在输出端子43的接合中,将梳齿部431a接合于导电部件22B的主面221B接合。该接合既可以是利用了激光焊接的接合、也可以是超声波接合。一对栅极端子44A、44B、一对检测端子45A、45B、多个虚拟端子46以及一对侧方端子47A、47B形成于一个引线框上,它们连接在一起。并且,将该引线框中的与侧方端子47A、47B对应的部分分别接合于导电部件22A的主面221A以及导电部件22B的主面221B。该接合既可以是利用了激光焊接的接合、也可以是超声波接合。

接着,将输入端子42连接于各半导体元件10B。在输入端子42的各突出部421c形成镀敷层421d,供缓冲部件82接合。突出部421c与缓冲部件82的接合通过形成于缓冲部件82的主面801的镀敷层85(Ag)和形成于突出部421c的镀敷层421d(Ag)的固相扩散接合来进行。输入端子42在中间夹着绝缘部件49地配置在输入端子41上。此时,在z方向观察时,输入端子42以多个突出部421c以及缓冲部件82分别与形成于半导体元件10B的源极电极111上的烧结用金属材料302重叠的方式配置。

接着,进行用于使各烧结用金属材料301、302成为烧结金属的加压加热处理。在进行该加压加热处理的工序(加压加热工序)中,如图16A以及图16B所示,通过利用加压部件90来按压各引线部件51,从而对多个烧结用金属材料301、302施加压力。此时,一部分的缓冲部件81以各引线部件51的上表面在z方向上的位置成为同等的方式变形(参照图16B)。由此,施加于各半导体元件10A的载荷变得均等。另外,同时,通过利用加压部件90或者与加压部件90不同的加压部件来按压输入端子42,从而对多个烧结用金属材料301、302施加压力。此时,一部分的缓冲部件82以输入端子42的各突出部421c的上表面(朝向与半导体元件10B相反的一侧的面)在z方向上的位置成为同等的方式变形。由此,施加于各半导体元件10B的载荷变得均等。然后,例如以大致250℃的温度对经由引线部件51加压的烧结用金属材料301、302以及经由输入端子42加压的烧结用金属材料301、302加热大约90秒。此外,加热条件不限定于此。由此,在多个烧结用金属材料301、302的每个中,银粒子彼此结合而成为烧结金属。此外,介于半导体元件10A与导电部件22A之间的烧结金属是半导体装置A1的元件接合层31A,介于半导体元件10B与导电部件22B之间的烧结金属是半导体装置A1的元件接合层31B。介于引线部件51的第一接合部511与半导体元件10A之间的烧结金属是半导体装置A1的引线接合层321。介于引线部件51的第二接合部512与导电部件22B之间的烧结金属是半导体装置A1的引线接合层322。介于输入端子42的各突出部421c与半导体元件10B之间的烧结金属是半导体装置A1的端子接合层33。

接着,形成多个丝线6。在形成丝线6的工序(丝线形成工序)中,例如使用众所周知的引线接合机。在丝线形成工序中,形成将各半导体元件10A的栅极电极112与栅极层24A连接的多个栅极丝线61、以及将各半导体元件10B的栅极电极112与栅极层24B连接的多个栅极丝线61。另外,形成将各半导体元件10A的源极电极111与检测层25A连接的多个检测丝线62、以及将各半导体元件10B的源极电极111与检测层25B连接的多个检测丝线62。并且,形成将栅极层24A与栅极端子44A连接的第一连接丝线63、以及将栅极层24B与栅极端子44B连接的第一连接丝线63。并且,形成将检测层25A与检测端子45A连接的第二连接丝线64、以及将检测层25B与检测端子45B连接的第二连接丝线64。此外,多个丝线6的形成顺序没有特别限定。

接着,形成封固树脂7。在形成封固树脂7的工序(树脂形成工序)中,例如基于传递模塑成形。封固树脂7例如是环氧树脂。在本实施方式中,以覆盖多个半导体元件10、支撑基板20的一部分、多个导电性接合层3、多个端子40的各一部分、多个引线部件51以及多个丝线6的方式形成封固树脂7。各端子40的各一部分、以及支撑基板20的一部分(具体而言为绝缘基板21的背面212)从所形成的封固树脂7露出。

然后,切断多个端子40的不需要的部分(例如上述引线框的一部分)、或者折弯多个端子40,由此制造出图1~图15所示的半导体装置A1。此外,上述的制造方法是一例,并不限定于此,也可以适当调换顺序。

以下,对半导体装置A1的作用效果进行说明。

根据本实施方式,在各引线部件51的第一接合部511与半导体元件10A的源极电极111之间分别夹设有缓冲部件81。缓冲部件81由Al构成,维氏硬度比由Cu构成的引线部件51小。因此,在加压加热工序中,在加压部件90按压各引线部件51进行加压时,一部分的缓冲部件81因加压被压瘪而变薄,从而各引线部件51的上表面在z方向上的位置(导电部件22A的主面221A至各引线部件51的上表面的高度)成为相同程度。由此,对各半导体元件10A均等地施加载荷,因此能够抑制对一部分的半导体元件10A施加偏颇的载荷。另外,根据本实施方式,在输入端子42的各突出部421c与半导体元件10B的源极电极111之间分别夹设有缓冲部件82。缓冲部件82由Al构成,维氏硬度比由Cu构成的输入端子42小。因此,在加压加热工序中,在加压部件90按压输入端子42进行加压时,一部分的缓冲部件82因加压被压瘪而变薄,从而各突出部421c的上表面在z方向上的位置(导电部件22B的主面221B至各突出部421c的上表面的高度)成为相同程度。由此,对各半导体元件10B均等地施加载荷,因此能够抑制对一部分的半导体元件10B施加偏颇的载荷。

另外,根据本实施方式,在各缓冲部件8的主面801以及背面802的整面形成有由Ag构成的镀敷层85。另外,在各引线部件51的第一接合部511形成有由Ag构成的镀敷层515,在输入端子42的各突出部421c形成有由Ag构成的镀敷层421d。由此,各缓冲部件8能够通过Ag的固相扩散接合而与引线部件51的第一接合部511或者输入端子42的突出部421c接合。另外,在各半导体元件10的源极电极111形成有在最外侧层叠Au的层而成的镀敷层115。由此,各缓冲部件8能够通过由烧结银构成的导电性接合层3而与半导体元件10的源极电极111牢固地接合。此外,各缓冲部件8与第一接合部511或者突出部421c也能够通过导电性接合层3而牢固地接合。

另外,根据本实施方式,对形成于各半导体元件10A之下的烧结用金属材料301和形成于各半导体元件10A之上的烧结用金属材料302同时进行加压加热处理。即,对元件接合层31A和引线接合层321同时进行烧结处理。通过一次的加压加热处理,由这些烧结用金属材料301、302形成元件接合层31A和引线接合层321,因此能够提高半导体装置A1的生产性。另外,根据本实施方式,对形成于各半导体元件10B之下的烧结用金属材料301和形成于各半导体元件10B之上的烧结用金属材料302同时进行加压加热处理。即,对元件接合层31B和端子接合层33同时进行烧结处理。通过一次的加压加热处理,由这些烧结用金属材料301、302形成元件接合层31B和端子接合层33,因此能够提高半导体装置A1的生产性。

另外,根据本实施方式,元件接合层31A、31B由作为糊料状的烧结用银的烧结用金属材料301形成。糊料状的烧结用银与预成型状的烧结用银比较,价格低廉。因此,半导体装置A1能够抑制制造成本。此外,在本实施方式中,元件接合层31A、31B也可以由预成型状的烧结用银形成。即,作为烧结用金属材料301,也可以使用预成型状的烧结用银。该情况下,由于不需要使糊料状的烧结用银干燥的工序,因此能够提高生产性。

此外,在本实施方式中,说明了对形成于各半导体元件10之下的烧结用金属材料301和形成于各半导体元件10之上的烧结用金属材料302同时进行加压加热处理的情况,但并不限于此。形成于各半导体元件10之下的烧结用金属材料301的加压加热处理和形成于各半导体元件10之上的烧结用金属材料302的加压加热处理也可以分开进行。

此外,在本实施方式中,对导电性接合层3由烧结金属构成的情况进行了说明,但并不限于此。导电性接合层3例如也可以是银糊料等。

图17~图28B表示本公开的其它实施方式。此外,在这些图中,对于与上述实施方式相同或者类似的要素标注与上述实施方式相同的符号。

图17以及图18是用于说明本公开的第二实施方式的半导体装置A2的图。图17是表示半导体装置A2的局部放大俯视图,是与图12对应的图。此外,在图17中,透过引线部件51用想象线(双点划线)示出。图18是表示半导体装置A2的局部放大剖视图,是与图13对应的图。本实施方式的半导体装置A2与第一实施方式的半导体装置A1的不同点在于,缓冲部件8的在z方向观察时的大小较小。

第二实施方式的各缓冲部件8与第一实施方式的半导体装置A1比较,在z方向观察时的大小较小。该缓冲部件8在变形之前的状态下,在z方向观察时,是内包于引线部件51的第一接合部511或者输入端子41的突出部421c的大小,在变形后也被内包。与第一实施方式的情况相同,在z方向观察时,该缓冲部件8的形状是因加压被压瘪而具有外形线呈曲线状鼓出的部分的形状。另外,如图17所示,剖面成为与z方向正交的方向的两端呈圆弧状地向外方突出的形状。另一方面,该缓冲部件8在z方向观察时不从第一接合部511或者突出部421c伸出,不具有与第一实施方式中的第二部81b(82b)相当的部分。

在本实施方式中,在各引线部件51的第一接合部511与半导体元件10A的源极电极111之间也分别夹设有缓冲部件81。因此,能够抑制对一部分的半导体元件10A施加偏颇的载荷。另外,在输入端子42的各突出部421c与半导体元件10B的源极电极111之间分别夹设有缓冲部件82。因此,能够抑制对一部分的半导体元件10B施加偏颇的载荷。另外,半导体装置A2通过采用与半导体装置A1共同的结构,从而起到与半导体装置A1同等的效果。

图19以及图20是用于说明本公开的第三实施方式的半导体装置A3的图。图19是表示半导体装置A3的局部放大立体图,是与图11对应的图。此外,在图19中,省略了栅极丝线61以及检测丝线62。图20是表示半导体装置A3的局部放大剖视图,是与图13对应的图。本实施方式的半导体装置A3与第一实施方式的半导体装置A1的不同点在于,具备源极丝线65来代替引线部件51。

第三实施方式的半导体装置A3不具备多个引线部件51,而是另外具备多个源极丝线65以及多个板部件55。在半导体装置A3中,半导体元件10A的源极电极111与导电部件22B由源极丝线65导通连接,来代替引线部件51。

各源极丝线65是所谓的接合引线。各源极丝线65使半导体元件10A的源极电极111与导电部件22B导通。各源极丝线65例如由Cu构成,以便能承受较大的电流。各源极丝线65的一端接合于与各半导体元件10A的源极电极111导通的板部件55,其另一端接合于导电部件22B。

板部件55是缓冲件,该缓冲件用于保护半导体元件10A的源极电极111免受源极丝线65接合时的冲击,例如是由Cu构成的板部件。在z方向观察时,板部件55是矩形形状,与半导体元件10A的源极电极111重叠。在本实施方式中,在板部件55的与半导体元件10A对置的面形成有镀敷层515。此外,与第一实施方式相同,镀敷层515例如由Ag构成。此外,镀敷层515的材料没有限定。在本实施方式中,板部件55的z方向的尺寸(厚度)为100~200μm左右。此外,板部件55的厚度不限定于此。与第一实施方式相同,缓冲部件81介于半导体元件10A的源极电极111与板部件55之间。在加压加热工序中,在加压部件90按压各板部件55时,一部分的缓冲部件81变形。在本实施方式中,板部件55是“第一连接部件”或者“第二连接部件”的一例。

根据本实施方式,在各板部件55与半导体元件10A的源极电极111之间分别夹设有缓冲部件81。因此,能够抑制对一部分的半导体元件10A施加偏颇的载荷。另外,在输入端子42的各突出部421c与半导体元件10B的源极电极111之间分别夹设有缓冲部件82。因此,能够抑制对一部分的半导体元件10B施加偏颇的载荷。另外,半导体装置A3通过采用与半导体装置A1共同的结构,从而能够起到与半导体装置A1同等的效果。

图21是表示本公开的第四实施方式的半导体装置A4的局部放大剖视图,是与图13对应的图。本实施方式的半导体装置A4与第一实施方式的半导体装置A1的不同点在于,不具备引线接合层321以及端子接合层33。

第四实施方式的形成于缓冲部件8的镀敷层85由Au构成。另外,形成于引线部件51的第一接合部511的镀敷层515、以及形成于输入端子42的突出部421c的镀敷层421d由Au构成。缓冲部件81与引线部件51的第一接合部511通过镀敷层85(Au)和镀敷层515(Au)的固相扩散接合来接合。另外,缓冲部件82与输入端子42的各突出部421c通过镀敷层85(Au)和镀敷层421d(Au)的固相扩散接合来接合。

与引线部件51的第一接合部511接合的缓冲部件81和半导体元件10A的源极电极111通过镀敷层85(Au)和镀敷层115(最外侧的层为Au)的固相扩散接合来接合。与输入端子42的各突出部421c接合的缓冲部件82和半导体元件10B的源极电极111通过镀敷层85(Au)和镀敷层115(最外侧的层为Au)的固相扩散接合来接合。

在本实施方式中,在各引线部件51的第一接合部511与半导体元件10A的源极电极111之间也分别夹设有缓冲部件81。因此,能够抑制对一部分的半导体元件10A施加偏颇的载荷。另外,在输入端子42的各突出部421c与半导体元件10B的源极电极111之间分别夹设有缓冲部件82。因此,能够抑制对一部分的半导体元件10B施加偏颇的载荷。另外,半导体装置A4通过采用与半导体装置A1共同的结构,从而起到与半导体装置A1同等的效果。并且,半导体装置A4中,缓冲部件8与半导体元件10的源极电极111通过镀敷层85(Au)和镀敷层115(最外侧的层为Au)的固相扩散接合来接合。因此,不需要具备引线接合层321以及端子接合层33。

此外,在本实施方式中,对镀敷层115的最外侧的层、镀敷层515、镀敷层421d、以及镀敷层85分别由Au构成的情况进行了说明,但不限于此。镀敷层115的最外侧的层、镀敷层515、镀敷层421d、以及镀敷层85也可以分别由Ag构成。该情况下,通过Ag彼此的固相扩散接合来接合。

图22是表示本公开的第五实施方式的半导体装置A5的局部放大剖视图,是与图13对应的图。本实施方式的半导体装置A5与第一实施方式的半导体装置A1的不同点在于缓冲部件81的配置位置。

在第五实施方式的半导体装置A5中,缓冲部件81配置在引线部件51的第一接合部511的与半导体元件10A相反的一侧(z方向z2侧)。另外,引线部件51的第一接合部511经由引线接合层321而与半导体元件10A的源极电极111接合。此外,同样,缓冲部件82也可以配置在输入端子41的突出部421c的与半导体元件10B相反的一侧(z方向z2侧)。

根据本实施方式,缓冲部件81配置在各引线部件51的第一接合部511的z方向z2侧。因此,在加压加热工序中,在加压部件90按压与各引线部件51接合的缓冲部件81而进行加压时,一部分的缓冲部件81因加压被压瘪而变薄,从而各缓冲部件81的上表面(朝向与半导体元件10A相反的一侧的面)在z方向上的位置(导电部件22A的主面221A至各缓冲部件81的上表面的高度)成为相同程度。由此,对各半导体元件10A均等地施加载荷,因此能够抑制对一部分的半导体元件10A施加偏颇的载荷。另外,半导体装置A5通过采用与半导体装置A1共同的结构,从而起到与半导体装置A1同等的效果。

图23是表示本公开的第六实施方式的半导体装置A6的局部放大剖视图,是与图13对应的图。本实施方式的半导体装置A6与第一实施方式的半导体装置A1的不同点在于,在引线部件51的第一接合部511的z方向的两面分别配置有缓冲部件81。

在第六实施方式的半导体装置A6中,缓冲部件81配置在引线部件51的第一接合部511的z方向的两面。在本实施方式中,作为引线部件的材料,使用包层材料,该包层材料是在由Cu构成的板部件的两面贴合由Al构成的板部件而成的材料。由该包层材料的Cu构成的板部件是引线部件51,由Al构成的板部件分别是缓冲部件81。在包层材料的两面(相当于各缓冲部件81的外侧的面)形成有镀敷层85。此外,同样,缓冲部件82也可以配置在输入端子41的突出部421c的z方向的两面。

根据本实施方式,在各引线部件51的第一接合部511的z方向的两侧分别配置有缓冲部件81。因此,在加压加热工序中,在加压部件90按压与各引线部件51的z方向z2侧的面接合的缓冲部件81(以下记载为“上侧的缓冲部件81”)并进行加压时,一部分的缓冲部件81因加压被压瘪而变薄,从而各上侧的缓冲部件81的上表面(朝向与半导体元件10A相反的一侧的面)在z方向上的位置(导电部件22A的主面221A至各上侧的缓冲部件81的上表面的高度)成为相同程度。由此,对各半导体元件10A均等地施加载荷,因此能够抑制对一部分的半导体元件10A施加偏颇的载荷。另外,半导体装置A6通过采用与半导体装置A1共同的结构,从而起到与半导体装置A1同等的效果。

图24是表示本公开的第七实施方式的半导体装置A7的局部放大剖视图,是与图13对应的图。本实施方式的半导体装置A7中,引线部件51的材料与第一实施方式的半导体装置A1不同。

第七实施方式的半导体装置A7不具备缓冲部件81,引线部件51发挥作为缓冲部件的功能。第七实施方式的引线部件51由维氏硬度比Cu小且具有导电性的材料构成,例如由Al构成。与第一实施方式相同,在该引线部件51的第一接合部511的与半导体元件10A对置的面形成有镀敷层515(Ag)。引线部件51的第一接合部511与半导体元件10A的源极电极111通过引线接合层321来接合。一部分的引线部件51的第一接合部511在加压加热工序中变形,在z方向观察时,是因加压被压瘪而具有外形线呈曲线状鼓出的部分的形状。另外,如图24所示,剖面成为与z方向正交的方向的两端呈圆弧状地向外方突出的形状。在本实施方式中,引线部件51是“第一连接部件”的一例。此外,同样,输入端子41例如也可以由Al构成。

根据本实施方式,各引线部件51由维氏硬度比Cu小的Al构成。因此,在加压加热工序中,在加压部件90按压各引线部件51进行加压时,一部分的引线部件51的第一接合部511因加压被压瘪而变薄,从而各第一接合部511的上表面(朝向与半导体元件10A相反的一侧的面)在z方向上的位置(导电部件22A的主面221A至各第一接合部511的上表面的高度)成为相同程度。由此,对各半导体元件10A均等地施加载荷,因此能够抑制对一部分的半导体元件10A施加偏颇的载荷。另外,半导体装置A7通过采用与半导体装置A1共同的结构,从而起到与半导体装置A1同等的效果。

图25是表示本公开的第八实施方式的半导体装置A8的局部放大剖视图,是与图13对应的图。本实施方式的半导体装置A8中,缓冲部件81的配置位置与第一实施方式的半导体装置A1不同。

在第八实施方式的半导体装置A8中,缓冲部件81介于导电部件22A与半导体元件10A之间。缓冲部件81与导电部件22A通过形成于缓冲部件81的主面801的镀敷层85(Ag)和形成于导电部件22A的主面221A的镀敷层222(Ag)的固相扩散接合来接合。另外,缓冲部件81与半导体元件10通过元件接合层31A来接合。一部分的缓冲部件81在加压加热工序中变形,在z方向观察时,是因加压被压瘪而具有外形线呈曲线状鼓出的部分的形状。此外,同样,缓冲部件82也可以介于导电部件22B与半导体元件10B之间。另外,缓冲部件81也可以介于元件接合层31A与半导体元件10A之间,缓冲部件82也可以介于元件接合层31B与半导体元件10B之间。

根据本实施方式,缓冲部件81介于导电部件22A与半导体元件10A之间。因此,在加压加热工序中,在加压部件90按压各引线部件51进行加压时,一部分的缓冲部件81因加压被压瘪而变薄,从而各引线部件51的上表面在z方向上的位置(导电部件22A的主面221A至各引线部件51的上表面的高度)成为相同程度。由此,对各半导体元件10A均等地施加载荷,因此能够抑制对一部分的半导体元件10A施加偏颇的载荷。另外,半导体装置A8通过采用与半导体装置A1共同的结构,从而起到与半导体装置A1同等的效果。

图26~图28B是用于说明本公开的第九实施方式的半导体装置A9的图。图26是表示半导体装置A9的立体图,用想象线(双点划线)示出封固树脂7。图27是沿图26的XXVII-XXVII线的剖视图。此外,在图27中,省略了各镀敷层。图28A以及图18B是用于说明半导体装置A9的制造工序的加压加热工序的示意图。本实施方式的半导体装置A9与第一实施方式的半导体装置A1的不同点在于,仅具备一个半导体元件10A。

第九实施方式的半导体装置A9是所谓的引线框构造,如图26所示,具备引线框92。引线框92的构成材料没有特别限定,例如是Cu或者Cu合金。引线框92具备芯片焊垫部921以及端子部922。芯片焊垫部921是搭载半导体元件10A的部分。在本实施方式中,在芯片焊垫部921搭载有一个半导体元件10A,经由元件接合层31而与半导体元件10A接合。芯片焊垫部921与半导体元件10A的漏极电极113导通。在本实施方式中,芯片焊垫部921是“导电体”的一例。端子部922的一部分从封固树脂7露出。端子部922经由引线部件51而与半导体元件10A的源极电极111导通。

第九实施方式的引线部件51的第一接合部511经由缓冲部件81以及引线接合层321而与半导体元件10A的源极电极111导通连接。第二接合部512经由引线接合层322而与端子部922接合。

缓冲部件81介于半导体元件10A的源极电极111与引线部件51的第一接合部511之间。如图28A以及图28B所示,在半导体装置A9的制造工序的加压加热工序中,一次进行多个半导体装置A9的加压加热处理。

图28A示出了两个引线框92、分别搭载于各引线框的半导体元件10A、分别与各半导体元件10A导通连接的引线部件51、以及分别配置在半导体元件10A与引线部件51之间的缓冲部件81。引线框92的底面至引线部件51的上表面的高度中,左侧比右侧高。图28B表示加压部件90按压各引线部件51进行加压的状态。配置在左侧的半导体元件10A之上的缓冲部件81通过加压变形而成为压瘪的形状。由此,该缓冲部件81的厚度变薄,引线框92的底面至引线部件51的上表面的高度中,右侧与左侧成为相同程度。由此,施加于左侧的半导体元件10A的载荷与施加于右侧的半导体元件10A的载荷成为相同程度,对两个半导体元件10A均等地施加载荷。

同时制造出的多个半导体装置A9的任一个缓冲部件81通过在加压加热工序中自身变形,从而使对各半导体元件10A的载荷变得均等。图26以及图27所示的半导体装置A9表示缓冲部件81在加压加热工序中变形的情况。在z方向观察时,缓冲部件81是因加压被压瘪而具有外形线呈曲线状鼓出的部分的形状。另外,剖面成为与z方向正交的方向的两端呈圆弧状地向外方突出的形状。在图26中,对第二部81b标注了影线。在图27中,用虚线示出了第一部81a与第二部81b的边界。此外,在半导体装置A9中,也有缓冲部件81不变形而保持长方体形状的部件。

根据本实施方式,缓冲部件81介于引线部件51的第一接合部511与半导体元件10A的源极电极111之间。因此,在一次制造多个半导体装置A9的加压加热工序中,能够抑制对一部分的半导体元件10A施加偏颇的载荷。另外,半导体装置A9通过采用与半导体装置A1共同的结构,从而起到与半导体装置A1同等的效果。此外,在本实施方式中,对半导体装置A9具备半导体元件10A的情况进行了说明,但不限于此。半导体装置A9也可以具备二极管或者IC等其它半导体元件来代替半导体元件10A。

本公开的半导体装置不限定于上述的实施方式。本公开的半导体装置的各部的具体的结构自由地进行各种设计变更。本公开包含以下的附记所记载的实施方式。

附记1.

一种半导体装置,具备:

第一半导体元件,其具有在厚度方向上相互朝向相反的一侧的第一元件主面及第一元件背面、以及配置于上述第一元件主面的第一电极;

第一连接部件,其与上述第一电极导通;以及

第一部件,其在上述厚度方向观察时与上述第一电极重叠,维氏硬度比上述第一连接部件的维氏硬度小,而且具有导电性。

附记2.

根据附记1所记载的半导体装置,

上述第一部件在上述厚度方向观察时具有外形线呈曲线状鼓出的部分。

附记3.

根据附记1或者2所记载的半导体装置,

上述第一部件的维氏硬度比Cu的维氏硬度小。

附记4.

根据附记3所记载的半导体装置,

上述第一部件的维氏硬度为50HV以下且1HV以上。

附记5.

根据附记4所记载的半导体装置,

上述第一部件由Al构成。

附记6.

根据附记1至5任一项中所记载的半导体装置,

上述第一部件介于上述第一电极与上述第一连接部件之间。

附记7.

根据附记6所记载的半导体装置,

还具备导电性接合层,该导电性接合层介于上述第一部件与上述第一电极之间。

附记8.

根据附记7所记载的半导体装置,

上述导电性接合层由烧结金属构成。

附记9.

根据附记8所记载的半导体装置,

上述烧结金属是烧结银。

附记10.

根据附记6至9任一项中所记载的半导体装置,

还具备镀敷层,该镀敷层介于上述第一部件与上述第一电极之间,而且与上述第一部件相接。

附记11.

根据附记6至10任一项中所记载的半导体装置,

上述第一部件具备:在上述厚度方向观察时与上述第一连接部件重叠的第一部;以及与上述第一部连接且在上述厚度方向观察时从上述第一连接部件突出的第二部。

附记12.

根据附记6至11任一项中所记载的半导体装置,还具备:

第二半导体元件,其具有在上述厚度方向上相互朝向相反的一侧的第二元件主面及第二元件背面、以及配置于上述第二元件主面的第二电极;以及

第二部件,其在上述厚度方向观察时与上述第二电极重叠,维氏硬度比上述第一连接部件小,而且具有导电性。

附记13.

根据附记12所记载的半导体装置,

还具备第二连接部件,该第二连接部件经由上述第二部件而与上述第二电极导通。

附记14.

根据附记12所记载的半导体装置,

上述第一连接部件经由上述第二部件而与上述第二电极导通。

附记15.

根据附记1至14任一项中所记载的半导体装置,

上述第一部件的上述厚度方向的尺寸为上述第一半导体元件的上述厚度方向的尺寸的10%以上且30%以下。

附记16.

一种半导体装置,具备:

第一半导体元件,其具有在厚度方向上相互朝向相反的一侧的第一元件主面及第一元件背面、以及配置于上述第一元件主面的第一电极;以及

第一连接部件,其在上述厚度方向观察时与上述第一电极重叠,而且与上述第一电极导通,

上述第一连接部件的维氏硬度比Cu的维氏硬度小,而且具有导电性。

附记17.

根据附记1至16任一项中所记载的半导体装置,还具备:

导电体,其搭载上述第一半导体元件;以及

第二导电性接合层,其介于上述第一半导体元件与上述导电体之间,

上述第二导电性接合层由烧结银构成。

附记18.

根据附记1至17任一项中所记载的半导体装置,

还具备与上述第一连接部件接合的丝线。

附记19.

根据附记1至18任一项中所记载的半导体装置,

上述第一半导体元件是功率MOSFET。

符号说明

A1~A9—半导体装置,10、10A、10B—半导体元件,101—元件主面,102—元件背面,111—源极电极,112—栅极电极,113—漏极电极,115—镀敷层,13—绝缘膜,20—支撑基板,21—绝缘基板,211—主面,212—背面,22、22A、22B—导电部件,221A、221B—主面,222—镀敷层,23A、23B—绝缘层,24A、24B—栅极层,25A、25B—检测层,29—基台部,3—导电性接合层,301、302—烧结用金属材料,31、31A、31B—元件接合层,321、322—引线接合层,33—端子接合层,40—端子,41—输入端子,411—焊盘部,411a—梳齿部,412—端子部,42—输入端子,421—焊盘部,421a—连结部,421b—伸出部,421c—突出部,421d—镀敷层,422—端子部,43—输出端子,431—焊盘部,431a—梳齿部,432—端子部,44A、44B—栅极端子,441—焊盘部,442—端子部,45A、45B—检测端子,451—焊盘部,452—端子部,46—虚拟端子,461—焊盘部,462—端子部,47A、47B—侧方端子,49—绝缘部件,491—夹设部,492—伸出部,51—引线部件,511—第一接合部,512—第二接合部,513—连络部,515—镀敷层,55—板部件,6—丝线,61—栅极丝线,62—检测丝线,63—第一连接丝线,64—第二连接丝线,65—源极丝线,7—封固树脂,71—树脂主面,72—树脂背面,731~734—树脂侧面,75—凹部,8、81、82—缓冲部件,801—主面,802—背面,81a、82a—第一部,81b、82b—第二部,85—镀敷层,90—加压部件,92—引线框,921—芯片焊垫部,922—端子部。

- 半导体装置、半导体装置的制造方法以及半导体封装的制造方法

- 半导体装置以及包括该半导体装置的显示装置

- 等离子体处理装置、半导体制造装置及半导体装置的制造方法

- 半导体装置分拣系统及半导体装置

- 金属互连,制造金属互连的方法,半导体装置和制造半导体装置的方法

- 晶体、结晶性氧化物半导体、包含结晶性氧化物半导体的半导体膜、包含晶体和/或半导体膜的半导体装置以及包含半导体装置的系统

- 光半导体反射器用环氧树脂组合物、光半导体装置用热固性树脂组合物及使用其得到的光半导体装置用引线框、封装型光半导体元件以及光半导体装置