一种多通道安全芯片的并行保密通信方法及其系统

文献发布时间:2023-06-19 10:14:56

技术领域

本发明涉及加解密安全芯片技术领域,具体是一种多通道安全芯片的并行保密通信方法及其系统。

背景技术

近几年来,物联网、云计算、人工智能、移动互联网和大数据等新型的应用持续发展,大规模、高实时性要求的移动数据通信需求呈爆炸式增长,对通信系统的传输能力提出了更高的要求。与此同时,新的黑客技术、更先进的电子窃听和信息截获篡改等技术的出现,使得信息的安全性受到很大的威胁。因此,数据传输能力和安全性两方面兼顾已逐渐成为通信系统设计必须考虑的因素。

采用专门安全芯片架构的通信系统是面向上述大规模、高实时性、高安全性要求的数据传输的一个解决方案。其利用专门的安全芯片提供硬件逻辑运算能力,实现数据的加解密计算。其中,为了增加通信系统的并行处理能力,改进数据传输的实时性,安全芯片可以构造多个通道,并行执行加解密计算。并且,利用主控芯片实现对各个通道的资源配置,以及对各个通道执行加解密计算的动态分配和切换。

目前,现有技术中主控芯片根据加解密计算的数据量,确定启用的通道数,并且由启用的各个通道并行生成加解密计算的密钥数据流,并且各个通道轮流获取待加解密的初始数据流,将密钥数据流与初始数据流执行异或运算,获得加密数据流或者解密数据流。

现有技术中,单位时间周期内密钥数据流的生成量是由各个通道的逻辑运算能力决定的,受到散热、资源配置等因素的制约,具有一定的波动;而单位时间周期内初始数据流的获取量是由通信过程中的实时数据传输决定的,受到通信负荷、带宽、信道质量等因素影响,存在一定的时变性;因此,密钥数据流和初始数据流之间往往存在不匹配的问题。现有技术中主控芯片往往只能根据测算或者预估的初始数据流的总数据量设定启用的通道数,并且按照每个通道理论的加解密计算能力配置存储空间等配套资源,对于以上不匹配的状况产生后缺乏有效的应对办法。

发明内容

鉴于上述问题,本发明的目的是提供一种基于多通道安全芯片执行加解密计算的并行保密通信方法及其系统。本发明将保密通信过程的加解密数据流特征与安全芯片各个通道的加解密计算参量进行匹配,生成安全芯片的多通道配置方案;并且,适应实际保密通信过程以及安全芯片运行的时变性,实现安全芯片多通道的动态管理。

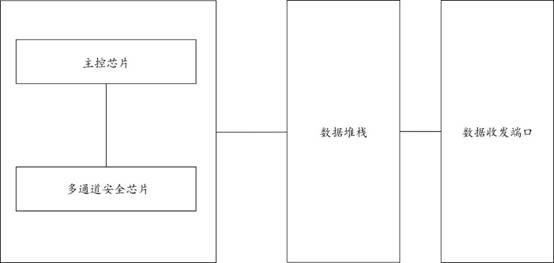

本发明实施例提供一种多通道安全芯片的并行保密通信系统,其特征在于,包括:数据收发端口、数据堆栈、主控芯片、多通道安全芯片;

所述数据收发端口用于在本系统执行保密通信过程中进行数据的通信发送和接收;

所述数据堆栈用于缓存所述数据收发端口发送和接收的数据流;

所述主控芯片对于数据堆栈中的加解密数据流,分析加解密数据流特征,并且根据该加解密数据流特征确定多通道安全芯片启用的通道数量;还评估所启用的各个通道的加解密计算参量,将加解密数据流特征与各个通道的加解密计算参量进行匹配,生成安全芯片的多通道配置方案;并且,用于对数据堆栈中的需要加解密处理的数据流,指令所述多通道安全芯片启用多个通道,多个通道并行读取数据堆栈中的数据流的数据帧单元并执行加密或者解密运算;

多通道安全芯片的每个通道对于获取的数据流的每个数据帧单元,执行加解密运算。

优选的是,主控芯片对于加解密数据流的特征分析包括:对数据堆栈中该数据流的数据帧单元的帧单元特征分析;以及根据该数据流对应的数据帧单元在数据堆栈中的缓存变化状况,对该数据流的传输特征分析。

优选的是,帧单元特征包括:数据帧单元长度、数据帧单元总数量、数据帧单元的最大允许延迟、数据帧单元的优先级;所述数据流的传输特征包括:单位时间的数据帧单元收发数、单位时间数据帧单元的收发变化率。

优选的是,所述主控芯片根据对加解密数据流的特征分析的结果,根据该加解密数据流的数据帧单元长度、数据帧单元总数量,结合单位时间数据帧单元的收发变化率,预测单位时间内数据帧单元加解密计算的总计算量,并且根据数据帧单元的最大允许延迟,确定在符合该最大允许延迟的条件下多通道安全芯片启用的通道数。

优选的是,多通道安全芯片预置多个备选的通道配置方案,每种通道配置方案涉及的单核线程分配数、临时暂存空间大小、随机码获取数量均不相同,并且,对每种备选的通道配置方案均映射为相应的加解密计算参量,即表明该种通道配置方案下该通道的加解密计算量;主控芯片对前述加解密数据流特征与各个备选通道配置方案的加解密计算参量进行匹配,根据最优的匹配关系生成安全芯片的多通道配置方案。

本发明的实施例提供了一种多通道安全芯片的并行保密通信方法,其特征在于,包括:

通过数据收发端口进行数据的通信发送和接收,并且通过数据堆栈缓存所述数据收发端口发送和接收的数据流;

通过主控芯片对于数据堆栈中的加解密数据流,分析加解密数据流特征,并且根据该加解密数据流特征确定多通道安全芯片启用的通道数量;还评估所启用的各个通道的加解密计算参量,将加解密数据流特征与各个通道的加解密计算参量进行匹配,生成安全芯片的多通道配置方案;并且,用于对数据堆栈中的需要加解密处理的数据流,指令所述多通道安全芯片启用多个通道,多个通道并行读取数据堆栈中的数据流的数据帧单元并执行加密或者解密运算;

通过多通道安全芯片的每个通道对于获取的数据流的每个数据帧单元,执行加解密运算。

优选的是,对于加解密数据流的特征分析包括:对数据堆栈中该数据流的数据帧单元的帧单元特征分析;以及根据该数据流对应的数据帧单元在数据堆栈中的缓存变化状况,对该数据流的传输特征分析。

优选的是,帧单元特征包括:数据帧单元长度、数据帧单元总数量、数据帧单元的最大允许延迟、数据帧单元的优先级;所述数据流的传输特征包括:单位时间的数据帧单元收发数、单位时间数据帧单元的收发变化率。

优选的是,根据对加解密数据流的特征分析的结果,根据该加解密数据流的数据帧单元长度、数据帧单元总数量,结合单位时间数据帧单元的收发变化率,预测单位时间内数据帧单元加解密计算的总计算量,并且根据数据帧单元的最大允许延迟,确定在符合该最大允许延迟的条件下多通道安全芯片启用的通道数。

优选的是,多通道安全芯片预置多个备选的通道配置方案,每种通道配置方案涉及的单核线程分配数、临时暂存空间大小、随机码获取数量均不相同,并且,对每种备选的通道配置方案均映射为相应的加解密计算参量,即表明该种通道配置方案下该通道的加解密计算量;通过主控芯片对加解密数据流特征与各个备选通道配置方案的加解密计算参量进行匹配,根据最优的匹配关系生成安全芯片的多通道配置方案。

从而,本发明适应了加解密安全芯片在保密通信中承担加解密运算的过程中,安全芯片多个通道的逻辑运算能力与通信过程中的实时数据传输时变性不匹配的状况;能够根据数据流的特征以及每个通道加解密计算能力,匹配适应性的通道分配方案,并且安全芯片多通道的动态管理。

本发明的其它特征和优点将在随后的说明书中阐述,并且,部分地从说明书中变得显而易见,或者通过实施本发明而了解。本发明的目的和其他优点可通过在所写的说明书、权利要求书、以及附图中所特别指出的结构来实现和获得。

下面通过附图和实施例,对本发明的技术方案做进一步地详细描述。

附图说明

附图用来提供对本发明的进一步理解,并且构成说明书的一部分,与本发明的实施例一起用于解释本发明,并不构成对本发明的限制。在附图中:

图1为本发明实施例提供的多通道安全芯片的并行保密通信系统结构图;

图2为本发明实施例提供的多通道安全芯片的并行保密通信方法总体流程图;

图3为本发明实施例提供的多通道安全芯片的并行保密通信方法的多通道配置流程图;

图4为本发明实施例提供的多通道安全芯片的并行保密通信方法的加解密计算流程图。

具体实施方式

下面将参照附图更详细地描述本公开的示例性实施例。虽然附图中显示了本公开的示例性实施例,然而应当理解,可以以各种形式实现本公开而不应被这里阐述的实施例所限制。相反,提供这些实施例是为了能够更透彻地理解本公开,并且能够将本公开的范围完整的传达给本领域的技术人员。

参照图1所示,本发明实施例提供的一种多通道安全芯片的并行保密通信系统。本发明将保密通信的加解密数据流特征与安全芯片各个通道的加解密计算参量进行匹配,生成安全芯片的多通道配置方案;并且,适应实际保密通信过程以及安全芯片运行的时变性,实现安全芯片多通道的动态管理。该保密通信系统包括:数据收发端口、数据堆栈、主控芯片、多通道安全芯片。

所述数据收发端口用于在本系统执行保密通信过程中进行数据的通信发送和接收;该通信过程中收发的数据可以是未经加解密处理的数据流,也可以是经过加解密处理的数据流。所述数据流被缓存在所述数据堆栈内。并且,所述主控芯片对数据堆栈中的该数据流,根据通信协议所定义的帧结构识别其中的数据帧单元,根据帧结构中的特定标识符号判断数据流的数据帧单元是否需要加密或者解密处理。对于需要加解密处理的数据流的数据帧单元,主控芯片指令所述多通道安全芯片启用多个通道,多个通道并行读取数据堆栈中的数据流的数据帧单元并执行加密或者解密运算;加密或者解密运算之后的数据帧单元组成的数据流被安全芯片提供给所述数据堆栈另外的堆栈区,再由数据收发端口进行读取和传输。

多通道安全芯片的每个通道对于获取的数据流的每个数据帧单元,根据帧结构中的特定标识符号判定该数据帧单元是待加密数据帧单元还是待解密数据帧单元。对于待加密数据帧单元,该通道生成随机码,并且利用预置算法(例如DES算法)根据随机码生成密钥数据流,密钥数据流包括密钥单元,待加密的数据帧单元与密钥单元进行异或运算产生加密数据帧单元,从而加密数据帧单元组合为加密数据流。并且,所述随机码被经过一定的转换和纠错编码处理后加入到加密数据帧单元。对于待解密的数据帧单元,该通道从该数据帧单元中还原出随机码,将随机码提供给预置算法,产生与该数据帧单元进行加密时相同的密钥数据流,将密钥数据流中的密钥单元与待解密的数据帧单元进行异或运算产生解密数据帧单元,从而将解密数据帧单元组合为解密数据流。

主控芯片对于数据堆栈中的加解密数据流,分析加解密数据流特征,并且根据该加解密数据流特征确定多通道安全芯片启用的通道数量;主控芯片还评估所启用的各个通道的加解密计算参量,将加解密数据流特征与各个通道的加解密计算参量进行匹配,生成安全芯片的多通道配置方案。

主控芯片对于加解密数据流的特征分析包括:对数据堆栈中该数据流的数据帧单元的帧单元特征分析;以及根据该数据流对应的数据帧单元在数据堆栈中的缓存变化状况,对该数据流的传输特征分析。帧单元特征包括:数据帧单元长度、数据帧单元总数量、数据帧单元的最大允许延迟、数据帧单元的优先级。数据流的传输特征包括:单位时间的数据帧单元收发数、单位时间数据帧单元的收发变化率。所述主控单元对于数据堆栈中的该数据流,根据通信协议所定义的帧结构识别其中的数据帧单元,并根据通信协议定义的帧结构对数据帧单元进行解析,获得数据堆栈中数据帧单元的长度,即一个单元的比特位数量(为了适应加解密需要,数据帧单元的长度都是固定的),并且统计该加解密数据流在数据堆栈中具有的数据帧单元的总数量;并且,通过对数据帧单元中最大延迟相关标识位的解析,获得每个数据帧单元允许的最大延迟,即完成加解密计算所允许的最大延迟时间;如果数据帧单元具有不同的优先级区分,优先级越高则需要越快完成加解密,则通过对数据帧单元中优先级标志位的解析获得数据帧单元的优先级。进而,主控单元设定一个观测窗口,利用观测窗口内该加解密数据流对应的数据帧单元在数据堆栈中的记录,测算统计单位时间的数据帧单元收发数、单位时间数据帧单元的收发变化率。

所述主控芯片根据对加解密数据流的特征分析的结果,根据该加解密数据流的数据帧单元长度、数据帧单元总数量,结合单位时间数据帧单元的收发变化率,预测单位时间内数据帧单元加解密计算的总计算量,并且根据数据帧单元的最大允许延迟,确定在符合该最大允许延迟的条件下多通道安全芯片启用的通道数。

主控芯片还评估所启用的各个通道的加解密计算参量,将加解密数据流特征与各个通道的加解密计算参量进行匹配,生成安全芯片的多通道配置方案。多通道安全芯片为所启用的每个通道分配一个或者多个单核线程,每个单核线程独立执行生成密钥数据流的所述预置算法以及密钥数据流的密钥单元与数据帧单元的异或运算;并且,多通道安全芯片为所启用的每个通道分配执行加解密运算的临时暂存空间;安全芯片一般采用一个随机发生器产生所述随机码,多通道安全芯片在单位时间内为每个通道分配一定数量的随机码或者随机码的获取权限。多通道安全芯片预置多个备选的通道配置方案,每种通道配置方案涉及的单核线程分配数、临时暂存空间大小、随机码获取数量均不相同,并且,对每种备选的通道配置方案均映射为相应的加解密计算参量,即表明该种通道配置方案下该通道的加解密计算量。主控芯片对前述加解密数据流特征与各个备选通道配置方案的加解密计算参量进行匹配,根据最优的匹配关系生成安全芯片的多通道配置方案。

为了适应实际保密通信过程以及安全芯片运行的时变性,所述主控芯片在多通道安全芯片被启用的各个通道加解密运算过程中,继续执行对加解密数据流的特征分析,包括帧单元特征分析以及数据流的传输特征分析;并且,主控芯片监测被启用的各个通道的实际加解密计算参量,包括所分配的单核线程的实际运算次数、临时暂存空间占用率、实际随机码使用数量。并且,当主控芯片判定加解密数据流的特征变化超出预计范围,或者实际加解密计算参量偏离通道配置方案的加解密计算参量的标准值超出预计范围,则重新对加解密数据流特征与各个备选通道配置方案的加解密计算参量进行再次匹配,根据最优的匹配关系再次生成安全芯片的多通道配置方案,从而实现安全芯片多通道的动态管理。

参见图2,本发明实施例提供的一种多通道安全芯片的并行保密通信方法,该方法将保密通信的加解密数据流特征与安全芯片各个通道的加解密计算参量进行匹配,生成安全芯片的多通道配置方案;并且,适应实际保密通信过程以及安全芯片运行的时变性,实现安全芯片多通道的动态管理。

如图2,该多通道安全芯片的并行保密通信方法包括以下步骤:

S201:执行保密通信过程中数据的通信发送和接收;该通信过程中收发的数据可以是未经加解密处理的数据流,也可以是经过加解密处理的数据流;

S202:将所述数据流缓存在所述数据堆栈内;并且,通过所述主控芯片对数据堆栈中的该数据流,根据通信协议所定义的帧结构识别其中的数据帧单元,根据帧结构中的特定标识符号判断数据流的数据帧单元是否需要加密或者解密处理。

S203:通过主控芯片对于数据堆栈中的加解密数据流,分析加解密数据流特征,并且根据该加解密数据流特征确定多通道安全芯片启用的通道数量;主控芯片还评估所启用的各个通道的加解密计算参量,将加解密数据流特征与各个通道的加解密计算参量进行匹配,生成安全芯片的多通道配置方案。

具体来说,如图3所示,S203可以分为以下子步骤:S2031:通过主控芯片对于加解密数据流执行特征分析,具体包括:对数据堆栈中该数据流的数据帧单元的帧单元特征分析;以及根据该数据流对应的数据帧单元在数据堆栈中的缓存变化状况,对该数据流的传输特征分析。帧单元特征包括:数据帧单元长度、数据帧单元总数量、数据帧单元的最大允许延迟、数据帧单元的优先级。数据流的传输特征包括:单位时间的数据帧单元收发数、单位时间数据帧单元的收发变化率。所述主控单元对于数据堆栈中的该数据流,根据通信协议所定义的帧结构识别其中的数据帧单元,并根据通信协议定义的帧结构对数据帧单元进行解析,获得数据堆栈中数据帧单元的长度,即一个单元的比特位数量(为了适应加解密需要,数据帧单元的长度都是固定的),并且统计该加解密数据流在数据堆栈中具有的数据帧单元的总数量;并且,通过对数据帧单元中最大延迟相关标识位的解析,获得每个数据帧单元允许的最大延迟,即完成加解密计算所允许的最大延迟时间;如果数据帧单元具有不同的优先级区分,优先级越高则需要越快完成加解密,则通过对数据帧单元中优先级标志位的解析获得数据帧单元的优先级。进而,主控单元设定一个观测窗口,利用观测窗口内该加解密数据流对应的数据帧单元在数据堆栈中的记录,测算统计单位时间的数据帧单元收发数、单位时间数据帧单元的收发变化率。S2032:通过所述主控芯片根据对加解密数据流的特征分析的结果,根据该加解密数据流的数据帧单元长度、数据帧单元总数量,结合单位时间数据帧单元的收发变化率,预测单位时间内数据帧单元加解密计算的总计算量,并且根据数据帧单元的最大允许延迟,确定在符合该最大允许延迟的条件下多通道安全芯片启用的通道数。S2033:通过主控芯片评估所启用的各个通道的加解密计算参量,将加解密数据流特征与各个通道的加解密计算参量进行匹配,生成安全芯片的多通道配置方案。多通道安全芯片为所启用的每个通道分配一个或者多个单核线程,每个单核线程独立执行生成密钥数据流的所述预置算法以及密钥数据流的密钥单元与数据帧单元的异或运算;并且,多通道安全芯片为所启用的每个通道分配执行加解密运算的临时暂存空间;安全芯片一般采用一个随机发生器产生所述随机码,多通道安全芯片在单位时间内为每个通道分配一定数量的随机码或者随机码的获取权限。多通道安全芯片预置多个备选的通道配置方案,每种通道配置方案涉及的单核线程分配数、临时暂存空间大小、随机码获取数量均不相同,并且,对每种备选的通道配置方案均映射为相应的加解密计算参量,即表明该种通道配置方案下该通道的加解密计算量。主控芯片对前述加解密数据流特征与各个备选通道配置方案的加解密计算参量进行匹配,根据最优的匹配关系生成安全芯片的多通道配置方案。

S204:对于需要加解密处理的数据流的数据帧单元,通过主控芯片指令所述多通道安全芯片启用多个通道,多个通道并行读取数据堆栈中的数据流的数据帧单元并执行加密或者解密运算;加密或者解密运算之后的数据帧单元组成的数据流被安全芯片提供给所述数据堆栈另外的堆栈区,再由数据收发端口进行读取和传输。

如图4所示,所述步骤S204具体又可以分为以下子步骤:S2041由多通道安全芯片的每个通道对于获取的数据流的每个数据帧单元,根据帧结构中的特定标识符号判定该数据帧单元是待加密数据帧单元还是待解密数据帧单元;S2042:对于待加密数据帧单元,该通道生成随机码,并且利用预置算法(例如DES算法)根据随机码生成密钥数据流,密钥数据流包括密钥单元,待加密的数据帧单元与密钥单元进行异或运算产生加密数据帧单元,从而加密数据帧单元组合为加密数据流。并且,所述随机码被经过一定的转换和纠错编码处理后加入到加密数据帧单元。S2043:对于待解密的数据帧单元,该通道从该数据帧单元中还原出随机码,将随机码提供给预置算法,产生与该数据帧单元进行加密时相同的密钥数据流,将密钥数据流中的密钥单元与待解密的数据帧单元进行异或运算产生解密数据帧单元,从而将解密数据帧单元组合为解密数据流。

为了适应实际保密通信过程以及安全芯片运行的时变性,所述方法还包括步骤:通过所述主控芯片在多通道安全芯片被启用的各个通道加解密运算过程中,继续执行对加解密数据流的特征分析,包括帧单元特征分析以及数据流的传输特征分析;并且,主控芯片监测被启用的各个通道的实际加解密计算参量,包括所分配的单核线程的实际运算次数、临时暂存空间占用率、实际随机码使用数量;并且,当判定加解密数据流的特征变化超出预计范围,或者实际加解密计算参量偏离通道配置方案的加解密计算参量的标准值超出预计范围,则重新对加解密数据流特征与各个备选通道配置方案的加解密计算参量进行再次匹配,根据最优的匹配关系再次生成安全芯片的多通道配置方案,从而实现安全芯片多通道的动态管理。

从而,本发明适应了加解密安全芯片在保密通信中承担加解密运算的过程中,安全芯片多个通道的逻辑运算能力与通信过程中的实时数据传输时变性不匹配的状况;能够根据数据流的特征以及每个通道加解密计算能力,匹配适应性的通道分配方案,并且安全芯片多通道的动态管理。

本说明书中各个实施例采用递进的方式描述,每个实施例重点说明的都是与其他实施例的不同之处,各个实施例之间相同相似部分互相参见即可。对于实施例公开的装置而言,由于其与实施例公开的方法相对应,所以描述的比较简单,相关之处参见方法部分说明即可。

对所公开的实施例的上述说明,使本领域专业技术人员能够实现或使用本发明。对这些实施例的多种修改对本领域的专业技术人员来说将是显而易见的,本文中所定义的一般原理可以在不脱离本发明的精神或范围的情况下,在其它实施例中实现。因此,本发明将不会被限制于本文所示的这些实施例,而是要符合与本文所公开的原理和新颖特点相一致的最宽的范围。

- 一种多通道安全芯片的并行保密通信方法及其系统

- 一种多通道安全芯片的并行保密通信方法及其系统