一种减少电容阵列的逐次逼近型模数转换器及其工作方法

文献发布时间:2023-06-19 09:51:02

技术领域

本发明涉及微电子领域,特别是涉及一种减少电容阵列的逐次逼近型模数转换器及其工作方法。

背景技术

集成电路自发明以来便沿着摩尔定律飞速发展,工艺线宽不断减小,集成度不断增大。工艺的不断改良对于数字电路的发展至关重要,到当今社会,数字信号的处理能力,数字存储技术发展都已经相当成熟。作为模拟世界和数字世界的桥梁,模数转换器(AnalogDigital Converter,ADC)是非常重要的一个模块,它在各个领域包括通信、能源、医疗、仪器仪表甚至现在正快速发展的AI领域等都有广泛应用。

逐次逼近型模数转换器(SARADC)是中等采样率,中等至高分辨率应用的常见结构。通过采用二分搜索算法不断缩小模拟输入信号可能的范围实现量化。SARADC的分辨率一般为8位至16位,具有低功耗小尺寸等特点。这些特点使SARADC获得了很广的应用范围,例如便携式电池供电仪表、输入量化器,工业控制和数据信号采集器等。

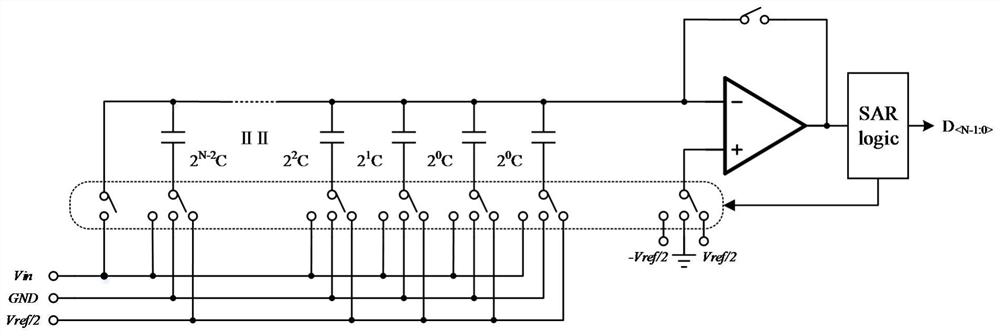

传统SARADC的电路结构和电压比较器输入电压变化示意图分别如图1和图2所示,其中电容阵列所占面积比例最大,常常占到整个SARADC的1/3甚至更大,而且电容会随着SARADC分辨率的增长呈指数型增长,严重的限制了SARADC芯片的面积和速度。

发明内容

本发明所要解决的技术问题是提供一种减少电容阵列的逐次逼近型模数转换器及其工作方法,可以减少电容阵列。

本发明解决其技术问题所采用的技术方案是:提供一种减少电容阵列的逐次逼近型模数转换器,包括电容阵列、开关阵列、电压比较器和逻辑控制模块,所述电容阵列的两个极板分别连接于所述开关阵列的一端和所述电压比较器的负输入端之间;所述逻辑控制模块的输入端与所述电压比较器的输出端连接,输出端与所述开关阵列连接,所述逻辑控制模块用于寄存所述电压比较器的输出并依照比较的结果生成逻辑控制信号来控制所述开关阵列的工作;所述电压比较器的负输入端通过一个复位开关与所述电压比较器的输出端连接,所述电容阵列包括N个并联的电容,其中,第一个电容的容值为单位电容的容值C,所述第i个电容的电容的容值为2

所述预比较开关的一端与所述电压比较器的负输入端连接,另一端与Vin端连接。

所述电容开关阵列包括N个四端开关,每个四端开关的一端连接于对应电容的一个极板,另外三端分别连接于Vin端、GND端和Vref/2端。

所述电压比较器参考电压开关的一端与所述电压比较器的正输入端连接,另外三端分别连接于GND端、+Vref/2端和-Vref/2端。

所述电容阵列通过所述开关阵列控制电荷的重分配进而实现电压二分搜索的算法。

本发明解决其技术问题所采用的技术方案是:还提供一种上述减少电容阵列的逐次逼近型模数转换器的工作方法,包括:

预比较阶段:所述预比较开关闭合,所述电容开关阵列断开,所述电压比较器参考电压开关接GND端,所述复位开关闭合,所述电压比较器将输入电压信号与参考电压进行比较并将比较结果输出到所述逻辑控制模块;

采样阶段:所述预比较开关断开并在整个周期内不再变化,所述电容开关阵列接Vin端,所述电压比较器参考电压开关接GND端,所述复位开关闭合,输入电压信号Vin被采样到所述电容阵列的极板上;

保持阶段:所述预比较开关断开,所述电容开关阵列接GND端,所述电压比较器参考电压开关依照所述预比较阶段的输出结果接-Vref/2端或Vref/2端,并在整个周期内作为参考电压不再变化,所述复位开关断开并在整个周期内不再变化,所述电压比较器的负输入端保持为-Vin;

循环置位比较阶段:所述电容阵列开关在所述逻辑控制模块的控制下从次高位开始进行N-1次的逐次逼近型比较,主要包括置位、比较和确定。

所述电压比较器参考电压开关依照所述预比较阶段的输出结果接-Vref/2端或Vref/2端具体为:当预比较阶段的输出结果为1时,所述电压比较器参考电压开关接-Vref/2端,当预比较阶段的输出结果为0时,,所述电压比较器参考电压开关接Vref/2端。

所述置位是指所述电容开关阵列中相应的电容开关从GND端改接Vref/2端;所述比较是指所述电压比较器将置位后的负输入端电压与参考电压进行比较并将比较结果输出至所述逻辑控制模块;所述确定是指所述逻辑控制模块根据本次循环内所述电压比较器的输出结果控制所述电容开关阵列中相应的电容开关的连接。

所述逻辑控制模块根据本次循环内所述电压比较器的输出结果控制所述电容开关阵列中相应的电容开关的连接具体为:当本次循环内所述电压比较器的输出结果为1时,所述逻辑控制模块控制所述电容开关阵列中相应的电容开关保持与Vref/2连接;当本次循环内所述电压比较器的输出结果为0时,所述逻辑控制模块控制所述电容开关阵列中相应的电容开关恢复与GND连接。

在预比较阶段前还包括复位阶段,在复位阶段时,所述预比较开关断开,所述电容开关阵列和所述电压比较器参考电压开关接GND,所述复位开关闭合,整个电路复位至初始状态。

有益效果

由于采用了上述的技术方案,本发明与现有技术相比,具有以下的优点和积极效果:本发明的逐次逼近型模数转换器在信号采样阶段对输入信号与初始参考电压的预比较来决定ADC输出的最高位MSB,同时根据比较的结果改变后续的参考电压,从次高位开始,与传统SARADC从最高位开始的工作过程保持一致。这样一来,在分辨率一样的前提下,本发明的逐次逼近型模数转换器中的电容阵列只有传统SARADC中电容阵列的一半,不仅大幅度减少了芯片的面积,降低了成本,还会因为输入电容的减少而提高ADC的速度,具有极高的商业价值。

附图说明

图1是现有技术的SARADC的电路结构框图;

图2是现有技术的SARADC在工作中电压比较器输入电压变化的示意图;

图3是本发明实施方式的SARADC的电路结构框图;

图4是本发明实施方式的SARADC在工作中电压比较器输入电压变化的示意图。

具体实施方式

下面结合具体实施例,进一步阐述本发明。应理解,这些实施例仅用于说明本发明而不用于限制本发明的范围。此外应理解,在阅读了本发明讲授的内容之后,本领域技术人员可以对本发明作各种改动或修改,这些等价形式同样落于本申请所附权利要求书所限定的范围。

本发明的实施方式涉及一种减少电容阵列的逐次逼近型模数转换器,如图3所示,主要分为电容阵列、开关阵列、电压比较器和逻辑控制模块。其中:

所述电容阵列的两个极板分别连接于所述开关阵列的一端和所述电压比较器的负输入端之间,所述电容阵列由N个电容并联构成,N为所述模数转换器的分辨率位数,其中,第一个电容的容值为单位电容的容值C,所述第i个电容的电容的容值为2

所述开关阵列分为预比较开关,电容开关阵列和电压比较器参考电压开关,其中,所述预比较开关由一个两端开关组成,其中一端与所述电压比较器的负输入端连接,另一端与Vin连接,所述预比较开关在所述逻辑控制模块的控制下将所述电压比较器的负输入端与Vin相连接,以实现在采样阶段对输入电压信号的预比较;所述电容开关阵列由N个四端开关组成,每个电容开关的一端连接于对应电容的一个极板,另外三端分别连接于Vin、GND和Vref/2,所述电容开关阵列在所述逻辑控制模块的控制下按照逐次逼近的逻辑将所述电容阵列分别与Vin、GND和Vref/2相连接,以实现采样、保持与电荷重分配的过程;所述电压比较器参考电压开关的一端与所述电压比较器的正输入端连接,另外三端分别连接于GND、+Vref/2和-Vref/2,所述电压比较器参考电压开关在所述逻辑控制模块的控制下将所述电压比较器的正输入端分别与Vin、GND和Vref/2相连接,以实现所述电压比较器参考电压的选择。

所述电压比较器的正输入端与所述电压比较器参考电压开关连接,所述电压比较器的负输入端与电容阵列的一端连接,所述电压比较器的负输入端还通过一个复位开关与所述电压比较器的输出端连接,所述电压比较器的输出端与逻辑控制模块连接,所述电压比较器用于比较输入电压和参考电压的大小,并将比较结果传送至逻辑控制模块。

所述逻辑控制模块的输入端与所述电压比较器的输出端连接,所述逻辑控制模块的输出端与所述电容阵列连接,所述逻辑控制模块用于寄存所述电压比较器的输出并依照比较的结果生成逻辑控制信号来控制所述开关阵列的工作,在整个工作周期结束后将所寄存的数据一次性输出。

逐次逼近型模数转换器的工作方法主要包括复位阶段,预比较阶段,采样阶段,保持阶段和循环置位比较阶段,其中:

所述复位阶段,所述预比较开关断开,所述电容开关阵列和所述电压比较器参考电压开关接GND,所述复位开关闭合,整个电路复位至初始状态;

所述预比较阶段,所述预比较开关闭合,所述电容开关阵列断开,所述电压比较器参考电压开关接GND,所述复位开关闭合,所述电压比较器将输入电压信号与参考电压进行比较并将比较结果输出到所述逻辑控制模块;

所述采样阶段,所述预比较开关断开并在整个周期内不再变化,所述电容开关阵列接Vin,所述电压比较器参考电压开关接GND,所述复位开关闭合,输入电压信号Vin被采样到所述电容阵列的极板上;

所述保持阶段,所述预比较开关断开,所述电容开关阵列接GND,所述电压比较器参考电压开关依照所述预比较阶段的输出结果MSB为1或0分别接-Vref/2或Vref/2,并在整个周期内作为参考电压不再变化,所述复位开关断开并在整个周期内不再变化,所述电压比较器的负输入端保持为-Vin;

所述循环置位比较阶段,所述电容阵列开关在所述逻辑控制模块的控制下从次高位开始进行N-1次的逐次逼近型比较,主要包括置位、比较和确定,其中:

所述置位是指所述电容开关阵列中相应的电容开关从GND改接Vref/2;

所述比较是指所述电压比较器将置位后的负输入端电压与参考电压进行比较并将比较结果输出至所述逻辑控制模块;

所述确定是指所述逻辑控制模块根据本次循环内所述电压比较器的输出结果为1或0来控制所述电容开关阵列中相应的电容开关保持与Vref/2连接或者恢复与GND连接。

对比图3中传统SAR ADC工作中电压比较器输入电压变化的示意图,图4显示了本实施方式提出的SARADC工作中电压比较器输入电压变化的示意图。本实施方式所提出的SARADC,在信号采样阶段对输入信号与初始参考电压的预比较来决定ADC输出的最高位MSB,同时根据比较的结果改变后续的参考电压,从次高位开始,与传统SARADC从最高位开始的工作过程保持一致。这样一来,在分辨率一样的前提下,本实施方式通过预比较的方式取代了传统SARADC中容值为2

- 一种减少电容阵列的逐次逼近型模数转换器及其工作方法

- 一种分段电容阵列型逐次逼近模数转换器校准结构及方法