半导体元件及其制作方法

文献发布时间:2023-06-19 10:58:46

技术领域

本发明有关于一种半导体装置及其制作方法,特别是有关于一种在阵列区域以及周边分区图案化的半导体装置及其制作方法。

背景技术

现在的半导体集成电路(integrated circuit,IC)工业正快速得成长。制造集成电路的工艺随着技术进步已经发展出多个世代,且这些世代依序至做出更小、更复杂的电路。图案化线路的决定性大小可以通过提升光刻工艺的分辨率,但此方法也通常会产生更大量的花费。为了改善此状况,更有人提出双重曝光(Double-patterning)的技术。然而,现有技术仍无法满足各方面的需求,还需要更符合成本效应的新方法。

发明内容

本发明的目的在于提供一种半导体元件及其制作方法,其可以在制作工艺中保护阵列以及导电结构。

本发明一实施例的半导体元件包括基板、多个阵列、多个导电结构以及一衬垫层。基板包括阵列区以及周边区。这些阵列配置在阵列区,每个阵列包括多个导电柱。这些导电结构配置在周边区,且每个导电结构具有至少一个导电侧壁。衬垫层覆盖这些导电柱的上表面以及这些导电结构的上表面。导电结构的导电侧壁免于被衬垫层覆盖。这些导电柱具有多个朝着第一方向的第一侧壁,且这些导电柱在每个阵列中沿着第二方向排列,且第一方向与第二方向不同。衬垫层沿着基板延伸至这些导电柱以及这些导电结构。

在本发明的一实施例中,上述的衬垫层的材料包括二氧化硅以及氮化硅。

在本发明的一实施例中,每个上述的导电柱包括多个朝向第二方向的第二侧壁以及上表面,且这些导电柱的这些上表面以及这些朝向第二方向的第二侧壁被衬垫层覆盖。

在本发明的一实施例中,在每个上述的阵列中,这些导电柱的其中之一上的衬垫层连接另一导电柱上的衬垫层。

在本发明的一实施例中,上述的衬垫层在周边区包括多个开口,且剩余的周边区被衬垫层覆盖,且每个导电结构的导电侧壁的位置对应至衬垫层的这些开口的其中之一的位置。

在本发明的一实施例中,上述的衬垫层包括多个长条,且这些阵列各自被这些长条覆盖。

在本发明的一实施例中,上述的每个导电柱在第一方向上的宽度以及每个长条的宽度实质上相同。

本发明一实施例的制作半导体元件的方法,包括以下步骤:在基板的阵列区以及周边区上图案化目标金属层,其中图案化后的目标金属层包括多个位于阵列区的导电长条以及多个位于周边区的周边结构;在这些导电长条以及这些周边结构上配置衬垫层;在衬垫层上配置底部硬遮罩;蚀刻阵列区域上的底部硬遮罩;蚀刻周边区域上的底部硬遮罩;以及利用底部硬遮罩蚀刻这些导电长条为多个阵列并蚀刻这些周边结构为多个导电结构。这些导电长条沿着第一方向延伸,且蚀刻后的底部硬遮罩在阵列区定义多个沿着第二方向延伸的沟槽,且第二方向与第一方向不同。蚀刻后的底部硬遮罩在周边区包括多个孔,且蚀刻这些周边结构的步骤将这些周边结构切为多个导电结构。

在本发明的一实施例中,上述的衬垫层是通过原子层沉积配置于这些导电长条以及这些周边结构上,且衬垫层自基板延伸至这些导电长条以及这些周边结构的上表面。

在本发明的一实施例中,上述的方法包括:在配置衬垫层于这些导电长条以及这些周边结构上之后,配置底部有机硬遮罩在衬垫层,其中底部有机硬遮罩填补衬垫层形成的多个沟槽。

附图说明

图1是本发明一实施例中半导体元件制作方法的流程示意图;

图2A至图6A是本发明一实施例的制作方法中图案化目标金属层在各步骤的俯视示意图;

图2A至图6B各是根据图2A至图6A中割面线B所绘的剖面示意图;

图7A是本发明一实施例的制作方法中配置衬垫层的步骤的俯视示意图;

图7B是根据图7A中割面线B所绘的剖面示意图;

图8A至图15A是本发明一实施例的制作方法中图案化底部硬遮罩以及蚀刻目标金属层在各步骤的俯视示意图;

图8B至图15B各是根据图8A至图15A中割面线B所绘的剖面示意图;

图8C至图15C各是根据图8A至图15A中割面线C所绘的剖面示意图。

主要附图标记说明:

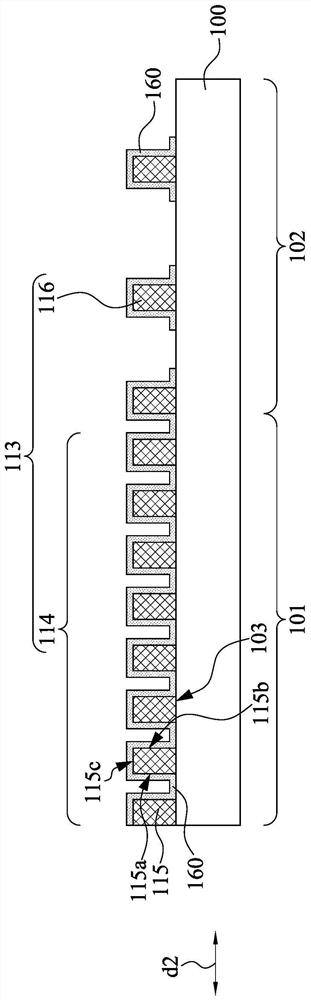

d1-第一方向,d2-第二方向,S11、S12、S13、S14、S15、S16-步骤,W1、W2-宽度,100-基板,101-阵列区,102-周边区,103-表面,110-目标金属层,111-导电长条,112-周边结构,113-导电层,114-阵列,115-导电柱,115a、115b-第二侧壁,115c-上表面,115d、115e-第一侧壁,116-导电结构,120-底部硬遮罩,130-上部硬遮罩,140-有机硬遮罩,141-有机核,142-第一间隔物,143-有机层,144-硬遮罩结构,150-光阻层,151-开口,160-衬垫层,161-长条,162-开口,170-底部有机硬遮罩,171-底部硬遮罩,172-上部有机硬遮罩,173-光阻层,174-第二间隔物,175-有机层,176-沟槽,177-光阻层,178-孔,179-孔。

具体实施方式

本发明有关一种改良的半导体元件及其制作方法。以下描述旨在让本领域的技术人员能够制造和使用下文中提供的公开内容,包含其特殊应用及需求。本领域的技术人员可以轻易对以下实施例作各种修改,并且以下定义的原理可以应用于其他实施例。因此,本公开内容不旨在限于以下所描述实施例,而是与符合本文公开的原理和新颖特征所形成的最宽范围一致。

为了清楚起见,附图中放大了层、膜、面板、区域等的厚度。在整个说明书中,相同的元件会以相同的附图标记表示。应当理解,当诸如层、膜、区域或基板的元件被称为在另一元件“上”或“连接到”另一元件时,其可以直接在另一元件上或与另一元件连接,或者中间元件可以也存在。相反,当元件被称为“直接在另一元件上”或“直接连接到”另一元件时,不存在中间元件。如本文所使用的,“连接”可以指物理及/或电性连接。再者,“电性连接”或“耦合”是可为二元件间存在其它元件。

应当理解,尽管术语“第一”、“第二”等在本文中可以用于描述各种元件,但是这些元件不应受这些术语的限制。这些术语仅用于将一个元件与另一个元件分开。因此,下面讨论的“第一元件”可以被称为第二元件而不脱离本文的教导。

这里使用的术语仅仅是为了描述特定实施例的目的,而不是限制性的。如本文所使用的,除非内容清楚地指示,否则单数形式“一”、“一个”和“该”旨在包括复数形式,包括“至少一个”。还应当理解,当在本说明书中使用时,术语“包含”及/或“包括”指定所述特征、区域、整体、步骤、操作、元件的存在及/或部件,但不排除一个或多个其它特征、区域整体、步骤、操作、元件、部件及/或其组合的存在或添加。

此外,诸如“下”或“底部”和“上”或“顶部”的相对术语可在本文中用于描述一个元件与另一元件的关系,如图所示。应当理解,相对术语旨在包括除了图中所示的方位之外的装置的不同方位。例如,如果一个附图中的装置翻转,则被描述为在其他元件的“下”侧的元件将被定向在其他元件的“上”侧。因此,示例性术语“下”可以包括“下”和“上”的取向,取决于附图的特定取向。类似地,如果一个附图中的装置翻转,则被描述为在其它元件“下面”或“下方”的元件将被定向为在其它元件“上方”。因此,示例性术语“下面”或“下方”可以包括上方和下方的取向。

此处所用的“形成”、“配置”、“放置”等用语是用以描述放置材料层至另一层。上述用语旨在描述任何可行的材料层制作技术,包括热增长(thermal growth)、溅镀(sputtering)、蒸镀(evaporation)、化学气相沉积(chemical vapor deposition)、累晶成长(epitaxial growth)、电子电镀(electroplating)等,但本发明不限于此。举例而言,根据各实施例,配置方法可以通过任何适合的技术。举例而言,配置可以包括在一层上作任何材料成长、镀膜或转移,配置技术可以包含物理气相沉积(physical vapor deposition,PVD)、化学气相沉积(chemical vapor deposition,CVD)、电化学沉积(electrochemicaldeposition,ECD)、原子束累晶(molecular beam epitaxy,MBE)、原子层沉积(atomiclayer deposition,ALD)以及等离子加强CVD(plasma-enhanced CVD,PECVD)。

图1是本发明一实施例中半导体元件的制作方法的流程示意图。请参照图1,本实施例的半导体元件的制作方法包括以下步骤:在基板上的阵列区以及周边区图案化目标金属层(步骤S11),其中图案化后的目标金属层包括多个导电长条以及多个周边结构;在目标金属层配置衬垫层(步骤S12);在衬垫层上配置底部硬遮罩(步骤S13);蚀刻阵列区上的底部硬遮罩(步骤S14);蚀刻周边区上的底部硬遮罩(步骤S15);以及利用底部硬遮罩蚀刻目标金属层(步骤S16)。衬垫层配置于这些导电长条以及这些周边结构上,且这些导电长条利用底部硬遮罩蚀刻为多个阵列,这些周边结构利用底部硬遮罩蚀刻为多个导电结构。

在本实施例中,图案化后的目标金属层的这些导电长条位于阵列区,且这些导电长条沿着第一方向延伸。蚀刻后的底部硬遮罩在阵列区定义多个沿着第二方向延伸的沟槽,且第一方向与第二方向不同。蚀刻目标金属层的步骤使这些导电长条蚀刻为多个阵列,且每个阵列包含多个导电柱。在本实施例中,半导体元件在阵列区包含多个阵列。

图案化后的目标金属层的周边结构位于周边区,且蚀刻后的底部硬遮罩在周边区包含多个开口。部分周边结构沿着第一方向延伸,另一部分周边结构沿着第二方向延伸,且蚀刻目标金属层的步骤将这些周边区的周边结构切为多个导电结构。在本发明的一些实施例中,导电结构可以是上述这些阵列的周边线路,且周边线路可以包含读写线路(read-write circuit)、感测放大线路(sense amp circuit)或电源管理线路(power managementcircuit)。

在本实施例中,半导体元件的制作方法配置衬垫层在目标金属层上,且衬垫层覆盖这些导电长条以及这些周边结构的上表面以及侧壁,且衬垫层也覆盖位于这些导电长条和周边结构之间的部分基板。在后续的工艺中,衬垫层可以保护并提供结构支撑给图案化后的目标金属层。以下会详细说明本发明实施例中半导体元件的制作方法。然而,本发明并不限于以下的实施例内容。

图2A至图6A是本发明一实施例的制作方法中图案化目标金属层在各步骤的俯视示意图,而图2A至图6B各是根据图2A至图6A中割面线B所绘的剖面示意图。

具体而言,请参照图2A以及图2B,在本发明的一实施例中,半导体元件的制作方法提供基板100、目标金属层110、底部硬遮罩120、上部硬遮罩130、有机硬遮罩140以及光阻层150。目标金属层110位于基板100和底部硬遮罩120之间,上部硬遮罩130以及有机硬遮罩140依序配置在底部硬遮罩120上。位于有机硬遮罩140上的光阻层150具有多个暴露有机硬遮罩140的开口151,用以定义有机硬遮罩140的蚀刻区域。

在本实施例中,基板100包含阵列区101以及周边区102。举例而言,光阻层150的开口151定义多个长条区域在阵列区101中,并定义多个互相交叉的区域在周边区102中。

本发明所属领域的技术人员可以适当调整目标金属层110、底部硬遮罩120、上部硬遮罩130、有机硬遮罩140以及光阻层150的厚度。

本实施例的上部硬遮罩130的材质可以包含氮氧化硅(silicon oxynitride,SiON),底部硬遮罩120的材质可以包含碳。在本发明的一些实施例中,上部硬遮罩130的材质也可以包含氮化硅(silicon nitride,SiN)或氧化硅(silicon monoxide,SiO)。

参照图2A,目标金属层110的材质可以包含钨(tungsten,W)。在本发明的其他实施例中,目标金属层110的材质可以包含氮化钛(titanium nitride,TiN)。

参照图3A以及图3B,本实施例的半导体元件制作方法蚀刻部分被光阻层150暴露的有机硬遮罩140,使被光阻层150覆盖的部分有机硬遮罩140形成多个有机核141。本实施例的半导体元件制作方法形成多个位于有机核141的侧壁的第一间隔物142在阵列区101以及周边区102。

第一间隔物142的形成方法可以包括以原子层沉积(atomic layer deposition,ALD)形成第一间隔层在这些有机核141以及上部硬遮罩130上,接着移除部分位于有机核141上方以及上部硬遮罩130上方的第一间隔层。上述的移除可以通过移除水平分布的第一间隔层。

在本实施例中,在阵列区101的有机核141具有朝向第二方向d2的侧壁,而第一间隔物142配置在这些侧壁上。因此,在阵列区101的这些第一间隔物142沿着第一方向d1延伸。

在周边区102的这些有机核141具有朝向第一方向d1和朝向第二方向d2的侧壁,且在周边区102的第一间隔物142可以具有沿着第一方向d1延伸的几何结构,以及与上述几何结构交叉连接并沿着第二方向d2延伸的几何结构。

举例而言,在本实施例中,第一间隔物142的材质可以包含氮化硅或一氧化硅等。

参照图4A以及图4B,本实施例的半导体元件制作方法覆盖有机层143,且有机层143填补这些第一间隔物142之间的区域。有机层143的材料以及有机核141的材料相同,都包含有机材料。

本实施例的半导体元件制作方法配置覆盖有机核141、第一间隔物142以及上部硬遮罩130的上表面有机层143,接着通过化学机械平坦化(chemical-mechanicalplanarization,CMP)移除部分超过有机核141以及第一间隔物142的上表面的有机层143。因此,本实施例的有机层143和有机核141提供一个平坦平面,以形成供后续蚀刻作用的适当表面。

参照图5A以及图5B,本实施例的半导体元件制作方法接着蚀刻第一间隔物142,且部分被第一间隔物142覆盖的上部硬遮罩130以及底部硬遮罩120也被移除。另一部分被有机层143或有机核141覆盖的上部硬遮罩130形成多个硬遮罩结构144在目标金属层110上。

每个硬遮罩结构144包含部分位于顶端的有机核141或有机层143,且上部硬遮罩130以及底部硬遮罩120依序排列在每个硬遮罩结构144的有机核141或有机层143下方。硬遮罩结构144在阵列区101中具有沿着第一方向d1延伸的图案,并在周边区102具有沿着第一方向d1延伸的图案以及沿着第二方向d2延伸的图案。

请参照图6A以及图6B,本实施例的半导体元件的制作方法接着利用这些硬遮罩结构144的图案做为遮罩蚀刻目标金属层110,因此形成多个导电长条111以及多个周边结构112。位于阵列区101的导电长条111沿着第一方向d1延伸,而周边结构112则位于周边区102。周边区102中的周边结构112具有沿着第一方向d1延伸的几何结构以及沿着第二方向d2延伸的几何结构,且几何结构交叉连接这些沿着第一方向d1延伸的几何结构。

在本发明的一些实施例中,蚀刻目标金属层110的工艺会以全面蚀刻的方式以使硬遮罩结构144可以完全被移除,而仅移除部分目标金属层110。

图7A是本发明一实施例的制作方法中配置衬垫层的步骤的俯视示意图,而图7B是根据图7A中割面线B所绘的剖面示意图。

在本实施例中,衬垫层160可以覆盖部分基板100的表面,而导电长条111以及周边结构112的上表面也被衬垫层160覆盖。进一步而言,衬垫层160可以自基板100的表面103延伸至导电长条111以及周边结构112的上表面,且导电长条111以及周边结构112的侧壁也都被衬垫层160覆盖,以提供保护以及结构支撑。举例而言,衬垫层160的材质可以包含二氧化硅(silicon oxide,SiO

图8A至图15A是本发明一实施例的制作方法中图案化底部硬遮罩以及蚀刻目标金属层在各步骤的俯视示意图。图8B至图15B各是根据图8A至图15A中割面线B所绘的剖面示意图。图8C至图15C各是根据图8A至图15A中割面线C所绘的剖面示意图。

参照图8A、图8B以及图8C,在本实施例中,底部有机硬遮罩170、底部硬遮罩171以及上部有机硬遮罩172依序配置在被衬垫层160覆盖的导电长条111和周边结构112上。

底部有机硬遮罩170的材质和上部有机硬遮罩172的材质相同。本实施例的底部有机硬遮罩170填补衬垫层160之间的空间,且在配置底部有机硬遮罩170后可以再实施化学机械平坦化。因此,底部有机硬遮罩170可以形成平坦平面供底部硬遮罩171沉积。上部有机硬遮罩172可以再配置于底部硬遮罩171上。

参照图9A、图9B以及图9C,本实施例的半导体元件制作方法配置一图案化的光阻层173在上部有机硬遮罩172上。在阵列区101中,光阻层173具有沿着第二方向d2延伸的图案,且光阻层173覆盖周边区102的全部区域。换句话说,只有在阵列区101的光阻层173有被图案化。

参照图10A、图10B以及图10C,本实施例的半导体元件制作方法以光阻层173的图案为遮罩蚀刻上部有机硬遮罩172,再在阵列区101中形成多个第二间隔物174在蚀刻后的上部有机硬遮罩172的侧壁上。

第二间隔物174的形成方式类似于上述第一间隔物142的形成方式,相同叙述将不在此赘述。第二间隔物174的材质可以包含二氧化硅或氮化硅。

参照图11A、图11B以及图11C,本实施例的半导体元件制作方法形成有机层175在第二间隔物174以及上部有机硬遮罩172上,且有机层175填补阵列区101中这些第二间隔物174之间的空隙。有机层175的材质与上部有机硬遮罩172的材质相同。

参照图12A、图12B以及图12C,本实施例的半导体元件的制作方法以上部有机硬遮罩172以及有机层175作为遮罩蚀刻底部硬遮罩171。

举例而言,超过第二间隔物174的上表面的部分有机层175被移除。接着被第二间隔物174覆盖的部分底部硬遮罩171被移除,因此,底部硬遮罩171在阵列区101定义了多个沿着第二方向d2延伸的沟槽176。

参照图13A、图13B以及图13C,光阻层177接着被配置在底部硬遮罩171上,且光阻层177通过图案化来形成多个孔178在周边区102。

举例而言,在本发明的一些实施例中,光阻层177在周边区102的孔178的位置至少对应至部分周边结构112的位置,而对应至被孔178暴露的区域的周边结构112将被移除。

请参照图14A、图14B以及图14C,在周边区102的底部硬遮罩171被以光阻层177为遮罩蚀刻。蚀刻后的底部硬遮罩171定义多个沟槽176在被衬垫层160覆盖的导电长条111上以及多个孔179在被衬垫层160覆盖的周边结构112上。这些沟槽176沿着第二方向d2延伸并位于阵列区101中。这些孔179位于周边区102。孔179暴露部分覆盖周边结构112的底部有机硬遮罩170。

参照图15A、图15B以及图15C,导电长条111以及周边结构112以及衬垫层160被以底部硬遮罩171为遮罩蚀刻。导电长条111以及周边结构112的剩余部分构成基板100上的导电层113。导电层113在阵列区101具有多个阵列114,并在周边区102具有多个导电结构116。

参照图15B,本实施例的阵列114包括多个导电柱115。进一步而言,导电柱115具有朝向第二方向d2的第二侧壁115a以及115b,以及连接第二侧壁115a以及115b的上表面115c。在每个导电柱115中,第二侧壁115a以及115b被衬垫层160覆盖。进一步而言,在每个阵列114中,衬垫层160自位于这些导电柱115之间的基板100的表面103延伸,且位于导电柱115上的衬垫层160会连接至阵列114中相邻的导电柱115上的衬垫层160。

换句话说,请参照图15A、图15B以及图15C,衬垫层160形成多个沿着第二方向d2延伸的长条161,且每个阵列114被这些长条161的其中之一共形地覆盖。同时,在第一方向d1上,阵列区101中导电柱115的宽度W2以及衬垫层160的长条161的宽度W1相同。

请参照图15C,导电柱115具有朝向第一方向d1的第一侧壁115d、115e。衬垫层160暴露导电柱115的这些第一侧壁115d、115e。换句话说,本实施例的衬垫层160只覆盖导电柱115的上表面115c、第二侧壁115a、115b,而导电柱115的第一侧壁115d、115e免于被衬垫层160覆盖。

举例而言,本实施例的导电柱115可以是金属氧化半导体(metal-oxidesemiconductor,MOS)晶体管以及电容之间的连接垫,而衬垫层160可以提供有效的保护以及结构支撑。

在本实施例的周边区102中,每个导电结构116具有至少一个连接侧壁117,其免于被衬垫层160覆盖,且导电结构116的其他侧壁都被衬垫层160覆盖。进一步而言,在周边区102的衬垫层160具有多个开口162,而剩余的周边区102则都被衬垫层160覆盖。导电结构116的导电侧壁117的位置对应至衬垫层160的开口162的位置。

举例而言,在本实施例的半导体元件中,导电结构116可以是阵列114的周边电路,而配置其上的衬垫层160会延伸至基板100的表面,衬垫层160可以形成完整的密封结构在大部分的导电结构116上。因此,本实施例的衬垫层160可以提供阵列114以及导电结构116良好的保护以及结构支撑。

在上述实施例中,第一方向d1垂直于第二方向d2,但本发明并不限于此。在本发明的一些实施例中,第一方向d1和第二方向d2之间可以夹其他角度。

尽管上述内容参照本发明的一些实施例详细描述本发明内容,但本发明仍具有其他实施例。因此,前述的权利要求的精神及范围不应限于以上所述的这些实施例。

在不脱离本发明的范围以及精神的前提下,本领域的技术人员可以对本发明实施例中的元件以及结构作各种修改及调整。如上所述,本发明包含其他经修改及调整且落在前述的权利要求中的实施例。

- 半导体元件用外延基板、半导体元件、半导体元件用外延基板的制作方法、以及半导体元件的制作方法

- 半导体元件用外延基板、半导体元件及半导体元件用外延基板的制作方法