铜电镀方法

文献发布时间:2023-06-19 11:49:09

技术领域

本发明涉及集成电路制造技术领域,尤其涉及一种铜电镀方法。

背景技术

在半导体器件的后段(Back-End-Of-Line,BEOL)工艺中,电化学镀工艺(Electrical Chemical Plating,ECP)作为一种通过电镀的方式在晶圆的表面沉积铜膜并完成铜布线工艺的制程,被广泛应用于先进的集成电路制造领域。

现有技术中,在沟槽和连接孔内填充金属铜一般先在沟槽和连接孔的底部和侧壁上形成阻挡层,接着在阻挡层上沉积铜籽晶层(seed layer),然后对铜籽晶层进行表面处理,最后在该铜籽晶层上以电化学镀工艺填充生长铜互连层。铜电镀填充的好坏对器件的性能有着重要影响。参阅图1和图2,提供衬底100,所述衬底100上形成有层间介质层110,所述层间介质层110内形成有沟槽111;在所述层间介质层110上及所述沟槽111内沉积阻挡层和铜籽晶层(图中未示出);然后在铜籽晶层上以电化学镀工艺填充生长铜互连层120。其中,电化学镀工艺通常会在电镀液中引入加速剂(accelerator)、抑制剂(suppressor)和平整剂(leveler)三种添加剂,来达到从底部到顶部的孔填充(bottom-up gap-fill)的效果。然而,参阅图3,沉积形成的所述阻挡层或所述铜籽晶层会在沟槽的开口处形成突起,使得沟槽顶部的工艺窗口变小,影响后续ECP填充工艺的填充效果。参阅图3和图4,随着关键尺寸的减小,铜电镀机台无法满足日益严苛的工艺要求,使得所述铜互连层120在铜电镀填充时很容易产生空洞(void或seam)。

常用的解决铜电镀产生空洞的方法有两种,其中一种方法是通过减小介电氧化层(例如TEOS、FSG、low K、ULK等)的厚度来减小沟槽或通孔的深宽比(AR),促进电化学镀工艺的填充效果。另外一种方法是通过形成更薄的阻挡层(barrier)和铜籽晶层(seed)来减弱突起(over hang),从而增大电化学镀工艺的填充窗口。然而,沟槽的深宽比(AR)不能无限的降低,物理气相沉积(PVD)机台也存在沉积极限,难以无限减薄阻挡层(barrier)和铜籽晶层(seed)的厚度。例如,现有的PVD机台中,所述阻挡层的沉积极限为

发明内容

本发明的目的在于提供一种铜电镀方法,通过刻蚀部分阻挡层和/或种子层以减小所述阻挡层和/或所述种子层在沟槽开口处形成的突起,扩大后续电化学镀工艺的工艺窗口,从而减少甚至避免铜电镀填充时产生空洞。

为了达到上述目的,本发明提供了一种铜电镀方法,包括:

提供衬底,所述衬底上依次形成有层间介质层和硬掩模层,所述硬掩模层和所述层间介质层内形成有沟槽;

在所述沟槽的侧壁和底部及所述硬掩模层的表面形成阻挡层和/或种子层,所述沟槽的开口处的所述阻挡层和/或所述种子层内形成有突起;

刻蚀部分厚度的所述阻挡层和/或种子层,以缩小所述突起;

进行电化学镀填充工艺,在所述沟槽内形成铜互连层。

可选的,采用湿法刻蚀工艺刻蚀部分厚度的所述阻挡层和/或种子层。

可选的,所述湿法刻蚀工艺的刻蚀剂包括氢氟酸、稀释氢氟酸或缓冲氧化硅腐蚀液。

可选的,所述湿法刻蚀工艺中,所述阻挡层和/或所述种子层的厚度减少量为

可选的,所述阻挡层的材料包括金属钽。

可选的,所述种子层和所述铜互连层的材料相同。

可选的,所述硬掩模层的材料包括氮化钛。

可选的,所述硬掩模层和所述层间介质层之间还设置有介电抗反射层,所述衬底和所述层间介质层之间还设置有刻蚀停止层。

可选的,所述介电抗反射层为无氮介电抗反射层。

可选的,所述刻蚀停止层的材料包括氮化硅。

综上所述,本发明提供一种铜电镀方法,包括:提供衬底,所述衬底上依次形成有层间介质层和硬掩模层,所述硬掩模层和所述层间介质层内形成有沟槽;在所述沟槽的侧壁和底部及所述硬掩模层的表面形成阻挡层和/或种子层,所述沟槽的开口处的所述阻挡层和/或所述种子层内形成有突起;刻蚀部分厚度的所述阻挡层和/或种子层,以缩小所述突起;进行电化学镀填充工艺,在所述沟槽内形成铜互连层。本发明通过刻蚀部分阻挡层和/或种子层以减小所述阻挡层和/或所述种子层在沟槽开口处形成的突起,扩大后续电化学镀工艺的工艺窗口,从而减少甚至避免铜电镀填充时产生空洞。

附图说明

图1和图2为一铜电镀填充方法中各个步骤对应的部分结构示意图;

图3为一铜电镀填充工艺中阻挡层和/或种子层出现突起的电镜图;

图4为一铜电镀填充工艺中产生的空洞的电镜图;

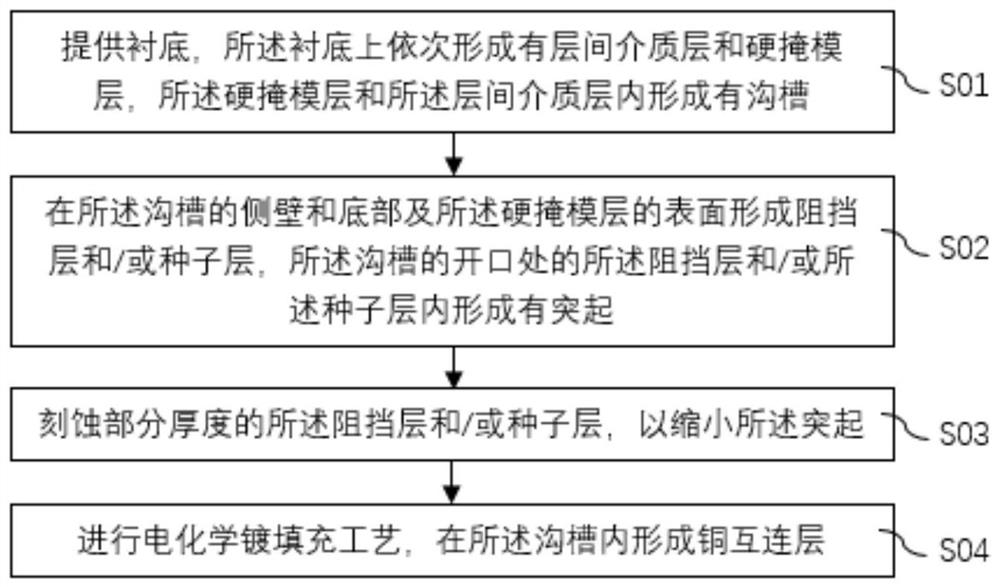

图5为本发明一实施例提供的铜电镀方法的流程图;

图6-图12为本发明一实施例提供的铜电镀方法中各个步骤对应的结构示意图;

图13为本发明一实施例所述的铜电镀方法形成的铜互连结构的剖面电镜图;

图14为本发明一实施例提供的铜电镀方法形成的铜互连结构的表面电镜图;

其中,附图标记如下:

100-衬底;110-层间介质层;111-沟槽;120-铜互连层;

200-衬底;210-刻蚀停止层;220-层间介质层;230-介电抗反射层;240-硬掩模层;250-沟槽;260-阻挡层;270-种子层;280-铜互连层;281-互连材料层。

具体实施方式

下面将结合示意图对本发明的具体实施方式进行更详细的描述。根据下列描述,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

图5为本发明一实施例提供的铜电镀方法的流程图。参阅图5,本实施例所述的铜电镀方法包括:

步骤S01:提供衬底,所述衬底上依次形成有层间介质层和硬掩模层,所述硬掩模层和所述层间介质层内形成有沟槽;

步骤S02:在所述沟槽的侧壁和底部及所述硬掩模层的表面形成阻挡层和/或种子层,所述沟槽的开口处的所述阻挡层和/或所述种子层内形成有突起;

步骤S03:刻蚀部分厚度的所述阻挡层和/或种子层,以缩小所述突起;

步骤S04:进行电化学镀填充工艺,在所述沟槽内形成铜互连层。

图6-图12为本实施例提供的铜电镀方法中各个步骤对应的结构示意图。下面结合图6-图12详细说明本实施例所述的铜电镀方法。

首先,参阅图6,执行步骤S01,提供衬底200,所述衬底200上依次形成有层间介质层220和硬掩模层240,所述硬掩模层240和所述层间介质层220内形成有沟槽250。具体的,形成所述沟槽250的过程包括:在所述硬掩模层240的表面形成图案化的光刻胶层(图中未示出),以所述图案化的光刻胶层为掩模对所述硬掩模层240和所述层间介质层220进行干法刻蚀,以形成所述沟槽250。可选的,由于所述干法刻蚀工艺的过程中会产生聚合物,因此,可以进行湿法清洗去除所述聚合物,避免所述聚合物对后续的铜电镀填充工艺产生影响,本实施例中,所述湿法清洗的清洗剂为氢氟酸溶液,在本发明的其他实施例中,所述清洗剂可以根据实际需要进行调整,本发明对此不作限制。

本实施例中,所述衬底200和所述层间介质层220之间还设置有刻蚀停止层210,所述刻蚀停止层210的材料包括氮化硅,在本发明的其他实施例中,所述衬底200和所述刻蚀停止层210之间还可以包括连接通孔层或其他半导体结构,本发明对此不作限制。所述硬掩模层240和所述层间介质层220之间还设置有介电抗反射层230。可选的,所述介电抗反射层230为无氮介电抗反射层,即所述介电抗反射层230中不包含氮元素。可选的,采用等离子体增强化学气相沉积工艺形成所述介电抗反射层230,且反应气体包括硅烷和二氧化碳。

本实施例中,所述衬底200所选用的材料可以是以下所提到的材料中的至少一种:Si、Ge、SiGe、SiC、SiGeC、InAs、GaAs、InP或者其它III/V化合物半导体,所述衬底200还可以是这些半导体材料构成的多层结构或者为绝缘体上硅(SOI)、绝缘体上层叠硅(SSOI)、绝缘体上层叠锗化硅(S-SiGeOI)、绝缘体上锗化硅(SiGeOI)以及绝缘体上锗(GeO)等,以上为本领域技术人员所熟知的内容,不再一一举例。可选的,所述层间介质层220可以为硅酸乙酯(TEOS)层、氟掺杂的硅酸盐玻璃(FSG)层、低介电常数材料(Low K)层或超低介电常数材料(ULK)层。本实施例中,所述硬掩模层240的材料为氮化钛(TiN),在本发明的其他实施例中,所述硬掩模层240的材料可以根据实际需要进行调整,本发明对此不作限制。

需要说明的是,图6所展示的半导体结构包括多个深宽比不完全相同的沟槽250,以说明本实施例提供的所述铜电镀方法对深宽比不同的沟槽均适用。

随后,参阅图7,执行步骤S02,在所述沟槽250的侧壁和底部及所述硬掩模层240的表面形成阻挡层260和/或种子层270,所述沟槽250的开口处的所述阻挡层260和/或所述种子层270内形成有突起。本实施例中,所述阻挡层260的材料包括金属钽(Ta),所述种子层270的材料为金属铜,在本发明的其他实施例中,所述阻挡层260和所述种子层270的材料可以根据实际需要进行调整,本发明对此不作限制。

参阅图8-图10,执行步骤S03,刻蚀部分厚度的所述阻挡层260和/或种子层270,以缩小所述突起。本实施例中,采用湿法刻蚀工艺刻蚀所述阻挡层260和/或种子层270。可选的,所述湿法刻蚀工艺的刻蚀剂包括氢氟酸、稀释氢氟酸或缓冲氧化硅腐蚀液。可选的,为了不影响所述阻挡层260和所述种子层270的正常功能,所述阻挡层260和所述种子层270在湿法刻蚀工艺中的厚度减少量为

当所述沟槽的侧壁和底部及所述硬掩模层的表面只形成阻挡层时,采用湿法刻蚀工艺刻蚀部分厚度的所述阻挡层以缩小所述阻挡层在沟槽开口处形成的突起;当所述沟槽的侧壁和底部及所述硬掩模层的表面只形成种子层时,采用湿法刻蚀工艺刻蚀部分所述种子层以缩小所述种子层在沟槽开口处形成的突起;当所述沟槽的侧壁和底部及所述硬掩模层的表面依次形成有阻挡层和种子层时,可以先在形成所述阻挡层后进行第一次湿法刻蚀工艺,缩小所述阻挡层在沟槽开口处形成的突起,再在形成所述种子层后进行第二次湿法刻蚀工艺,缩小所述种子层在沟槽开口处形成的突起;当所述沟槽的侧壁和底部及所述硬掩模层的表面依次形成有阻挡层和种子层时,也可以在形成所述阻挡层和所述种子层之后进行一次湿法刻蚀工艺,以缩小所述阻挡层和所述种子层在沟槽开口处形成的突起。

接着,参阅图11和图12,执行步骤S04,进行电化学镀填充工艺,在所述沟槽250内形成铜互连层280。具体的,形成所述铜互连层280的过程包括:在所述种子层270的表面形成互连材料层281;对所述互连材料层281进行平坦化处理以在所述沟槽250内形成铜互连层280。本实施例中,所述铜互连层280的材料包括金属铜,在本发明的其他实施例中,所述铜互连层280的材料可以根据实际需要进行调整,本发明对此不作限制。可选的,采用化学机械研磨(CMP)工艺对所述互连材料层281进行平坦化处理,以形成所述铜互连层280。

图13为本发明一实施例所述的铜电镀方法形成的铜互连结构的剖面电镜图。对比图3和图13可知,传统的铜电镀方法中,半导体结构的阻挡层和/或种子层会出现突起,影响后续金属填充工艺的工艺窗口,使得后续形成的金属互连结构中产生空洞(即图3中框出的区域);本实施例提供的所述铜电镀方法通过刻蚀部分阻挡层和/或种子层以减小所述阻挡层和/或所述种子层在沟槽开口处形成的突起,扩大后续电化学镀工艺的工艺窗口,从而减少甚至避免铜电镀填充时产生空洞。

图14为本发明一实施例提供的铜电镀方法形成的铜互连结构的表面电镜图。对比图4和图14可知,本实施例提供的所述铜电镀方法制成的铜互连结构中空洞的数量和密度均明显小于传统方法制成的铜互连结构。

综上,本发明提供一种铜电镀方法,包括:提供衬底,所述衬底上依次形成有层间介质层和硬掩模层,所述硬掩模层和所述层间介质层内形成有沟槽;在所述沟槽的侧壁和底部及所述硬掩模层的表面形成阻挡层和/或种子层,所述沟槽的开口处的所述阻挡层和/或所述种子层内形成有突起;刻蚀部分厚度的所述阻挡层和/或种子层,以缩小所述突起;进行电化学镀填充工艺,在所述沟槽内形成铜互连层。本发明通过刻蚀部分阻挡层和/或种子层以减小所述阻挡层和/或所述种子层在沟槽开口处形成的突起,扩大后续电化学镀工艺的工艺窗口,从而减少甚至避免铜电镀填充时产生空洞。

上述仅为本发明的优选实施例而已,并不对本发明起到任何限制作用。任何所属技术领域的技术人员,在不脱离本发明的技术方案的范围内,对本发明揭露的技术方案和技术内容做任何形式的等同替换或修改等变动,均属未脱离本发明的技术方案的内容,仍属于本发明的保护范围之内。

- 可溶性铜阳极、电解铜电镀装置、电解铜电镀方法及酸性电解铜电镀液的保存方法

- 电解铜电镀用含磷铜阳极、其制造方法及电解铜电镀方法