半导体结构连接性的测试方法及其测试系统

文献发布时间:2023-06-19 18:29:06

技术领域

本申请实施例涉及半导体领域,特别涉及一种半导体结构连接性的测试方法及其测试系统。

背景技术

随着半导体结构的集成度的提高,通常利用硅穿孔结构(TSV,Through SiliconVia)穿透多个堆叠芯片,使得多个芯片彼此电连接,以形成包括多个堆叠芯片的3维半导体结构。由于半导体结构包括多个TSV,则芯片可以借助于TSV接收各种信号。

然而,一方面,TSV自身可能出现各种缺陷,造成TSV自身导电性能的降低,从而降低借助于TSV电连接的芯片之间的连接性;另一方面,TSV没有正确连接,例如TSV实际电连接的芯片与设计时需要TSV电连接的芯片不同,也会降低半导体结构的良率。上述两方面均会影响半导体结构的工作速率。

因此,需要一种测试方法,检测半导体结构中芯片之间连接性,从而确定半导体结构的质量是否合格。

发明内容

本申请实施例提供一种半导体结构连接性的测试方法及其测试系统,至少有利于通过获取硅穿孔结构的阻值,以检测半导体结构的连接性。

根据本申请一些实施例,本申请实施例一方面提供一种半导体结构连接性的测试方法,包括:提供半导体结构和检测晶体管,所述半导体结构包括具有相对的第一端和第二端的硅穿孔结构,所述检测晶体管具有检测栅极、第一端口以及第二端口,所述检测栅极用于接收测试信号,所述第一端口用于接收工作电压,所述第二端口电连接所述第一端;获取所述检测晶体管的本征导电因子,所述本征导电因子为,所述检测晶体管工作于饱和区,且所述检测晶体管中的电流具有第一电流方向的条件下,载流子迁移率与单位面积栅氧化层的电容的乘积;所述检测晶体管接收所述测试信号导通,且向所述第二端提供测试电压,使所述检测晶体管中的电流具有第二电流方向,所述第一电流方向与所述第二电流方向相反,以使所述检测晶体管工作于深三极管区,并获取所述检测晶体管工作于深三极管区期间流经所述第二端的电流;基于所述本征导电因子、所述工作电压、所述测试电压以及流经所述第二端的电流,获取所述硅穿孔结构的电阻。

根据本申请一些实施例,本申请实施例另一方面还提供一种检测半导体结构连接性的测试系统,包括:半导体结构,所述半导体结构包括具有相对的第一端和第二端的硅穿孔结构,所述第一端与第一芯片电连接,所述第二端与第二芯片电连接;检测晶体管,位于所述第一芯片中,所述检测晶体管包括:检测栅极、第一端口以及第二端口,所述检测栅极用于接收测试信号,所述第一端口用于接收工作电压,所述第二端口电连接所述第一端;测试电压施加模块,在所述检测晶体管接收所述测试信号导通时,给所述第二端提供测试电压,使所述检测晶体管工作于深三极管区;电流获取模块,用于获取所述检测晶体管工作于深三极管区期间流经所述第二端的电流;电阻获取模块,基于所述本征导电因子、所述工作电压、所述测试电压以及流经所述第二端的电流,获取所述硅穿孔结构的电阻。

本申请实施例提供的技术方案至少具有以下优点:

上述技术方案中,提供检测晶体管,将检测晶体管的第二端口与硅穿孔结构的第一端电连接,检测晶体管的检测栅极接收测试信号,测试信号用于使得检测晶体管导通,然后在硅穿孔结构的第二端提供测试电压,以改变检测晶体管的工作状态,使得检测晶体管工作于深三极管区,通过获取检测晶体管工作于深三极管区期间流经第二端的电流和获取检测晶体管的本征导电因子,获取硅穿孔结构的电阻,将硅穿孔结构实际获取的电阻值与理想的硅穿孔结构电阻值进行比较,从而可以判断出半导体结构的连接性是否良好,还可以通过判断硅穿孔结构实际获取的电阻值与理想的硅穿孔结构电阻值之间差异的大小,初步推测出半导体结构中连接性出现问题的原因,从而有针对性的对半导体结构进行修复。此外,当半导体结构处于正常工作模式时,可以通过测试信号使得检测晶体管处于截止状态,从而不会影响半导体结构的正常工作。

附图说明

一个或多个实施例通过与之对应的附图中的图片进行示例性说明,这些示例性说明并不构成对实施例的限定,除非有特别申明,附图中的图不构成比例限制。

图1为本申请一实施例提供的测试半导体结构连接性的一种流程图;

图2是示意性地说明根据本申请一实施例的用于测试半导体结构连接性的电路的配置框图;

图3为本申请另一实施例提供的检测半导体结构连接性的测试系统的功能模块示意图。

具体实施方式

由背景技术可知,目前需要一种半导体结构连接性的测试方法。

经分析发现,半导体结构中利用硅穿孔结构连接芯片时,硅穿孔结构的缺陷以及硅穿孔结构与芯片之间没有正确连接,均会对半导体结构的工作速率造成不利的影响。其中,硅穿孔结构的缺陷包括硅穿孔结构中导电材料的不完全填充而产生的空隙、硅穿孔结构本身的破裂,以及由于芯片的翘曲或者凸块材料的迁移导致的硅穿孔结构与芯片之间的接触失效。硅穿孔结构与芯片之间的不正确连接可能导致硅穿孔结构发生短路。

因而,需要一种半导体结构连接性的测试方法,通过测量硅穿孔结构的阻值,来判定半导体结构的连接性是否良好。

下面将结合附图对本申请的各实施例进行详细的阐述。然而,本领域的普通技术人员可以理解,在本申请各实施例中,为了使读者更好地理解本申请而提出了许多技术细节。但是,即使没有这些技术细节和基于以下各实施例的种种变化和修改,也可以实现本申请所要求保护的技术方案。

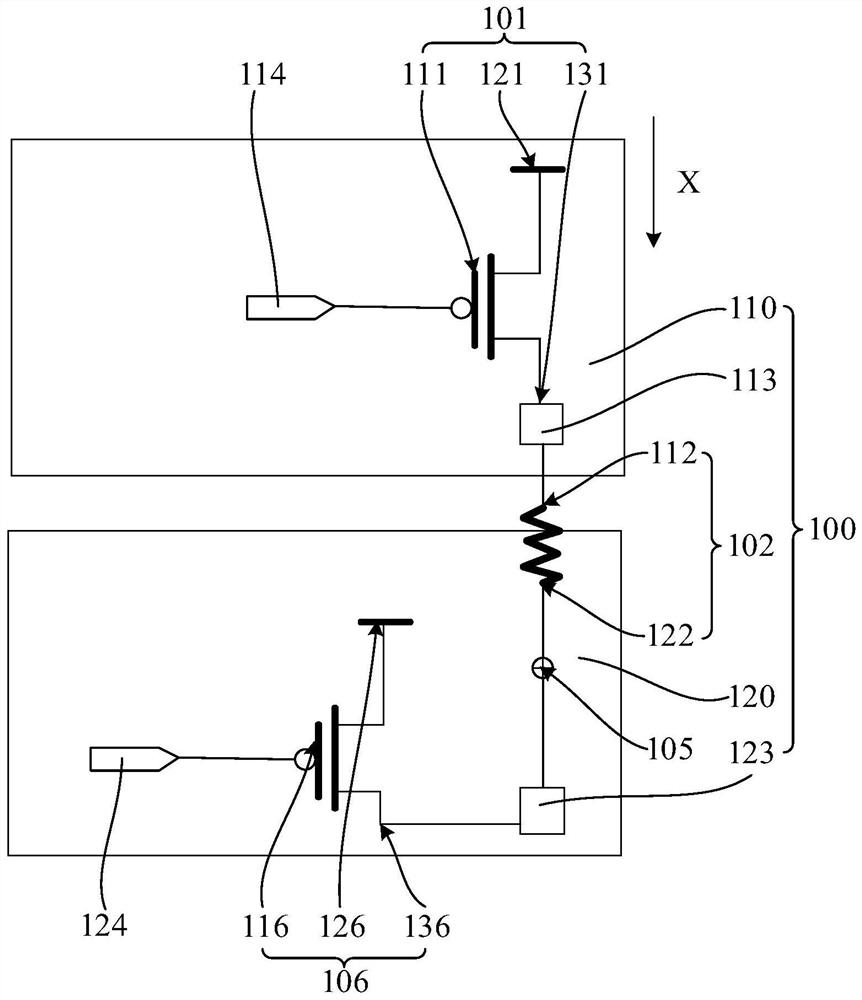

本申请一实施例提供一种半导体结构连接性的测试方法,以下将结合附图对本申请一实施例提供的半导体结构连接性的测试方法进行详细说明。图1为本申请一实施例提供的测试半导体结构连接性的一种流程图;图2是示意性地说明根据本申请一实施例的用于测试半导体结构连接性的电路的配置框图。

结合参考图1和图2,半导体结构连接性的测试方法包括如下步骤:

S101:提供半导体结构100和检测晶体管101,半导体结构100包括具有相对的第一端112和第二端122的硅穿孔结构102,检测晶体管101具有检测栅极111、第一端口121以及第二端口131,检测栅极111用于接收测试信号,第一端口121用于接收工作电压,第二端口131电连接第一端112。

在一些实施例中,半导体结构还可以包括第一电连接层113,第二端口131和第一端112均与第一电连接层113电连接,以实现第二端口131电连接第一端112。

S102:获取检测晶体管101的本征导电因子,本征导电因子为:检测晶体管101工作于饱和区,且检测晶体管101中的电流具有第一电流方向X的条件下,载流子迁移率与单位面积栅氧化层的电容的乘积。

其中,检测晶体管101为PMOS晶体管(P沟道金属氧化物半导体场效应晶体管,Positive channel Metal Oxide Semiconductor)。测试方法还包括:提供标准PMOS晶体管,标准PMOS晶体管具有标准宽长比、标准饱和电流、标准栅源电压和标准阈值电压,检测晶体管101的本征导电因子与标准PMOS晶体管的本征导电因子相同。需要说明的是,标准PMOS晶体管是由代工厂提供的,则标准PMOS晶体管的标准宽长比、标准饱和电流、标准栅源电压和标准阈值电压均为代工厂提供的基本性能参数,无需人工测量。

获取检测晶体管101的本征导电因子具体包括如下步骤:

基于标准栅源电压、标准宽长比、标准饱和电流和标准阈值电压获取本征导电因子,本征导电因子、标准栅源电压、标准宽长比、标准饱和电流和标准阈值电压满足如下关系:

其中,I

S103:检测晶体管101接收测试信号导通,且向第二端122提供测试电压,使检测晶体管101中的电流具有第二电流方向,第一电流方向X与第二电流方向相反,以使检测晶体管101工作于深三极管区,并获取检测晶体管101工作于深三极管区期间流经第二端122的电流。

在一些实施例中,测试方法还可以包括提供测试信号施加结构114,用于将测试信号施加在检测晶体管101的检测栅极111上。半导体结构还可以包括第二电连接层123,机台提供第一探针,并使第一探针与第二电连接层123接触电连接,用于将测试电压施加在第二电连接层123上,从而向第二端122提供测试电压;半导体结构还可以包括探针接触点105,机台还提供第二探针,并使第二探针与探针接触点105接触电连接,用于获取检测晶体管101工作于深三极管区期间流经探针接触点105的电流,从而获取检测晶体管101工作于深三极管区期间流经第二端122的电流。在其他实施例中,机台提供第一探针,可以使第一探针直接与第二端直接接触,以将测试电压施加在第二端;机台还提供第二探针,并使第二探针直接与第二端直接接触,用于获取检测晶体管工作于深三极管区期间流经第二端的电流。

当检测晶体管101为PMOS晶体管时,测试信号为低电平使得检测晶体管101导通,且测试电压大于工作电压,检测晶体管101工作于深三极管区时,第二电流方向为第二端口131指向第一端口121。此外,当半导体结构100处于正常工作模式时,可以使测试信号为高电平,以使得检测晶体管101处于截止状态,从而不会影响半导体结构100的正常工作。

工作在深三级管区的PMOS晶体管可以看成一个由过驱动电压控制的等效可控电阻,当栅源电压为定值时,沟道直流导通电阻近似为一个恒定的电阻。

因此,在获取硅穿孔结构102的电阻之前,测试方法还包括:在检测晶体管101工作于深三极管区时,基于本征导电因子、工作电压和检测晶体管101的阈值电压,获取检测晶体管101的等效电阻。

具体可以根据如下关系式计算检测晶体管101的等效电阻:

其中,R

需要说明的是,检测晶体管101的宽长比W

其中,检测晶体管101导通时检测栅极111的电压V

因此,

S104:基于本征导电因子、工作电压、测试电压以及流经第二端122的电流,获取硅穿孔结构102的电阻。

具体可以根据如下关系式计算所述硅穿孔结构的电阻:

其中,R

获取硅穿孔结构102的电阻R

因此,本申请实施例不仅有利于通过获取硅穿孔结构102的阻值R

继续参考图1,测试方法还可以包括:提供校准晶体管106,校准晶体管106具有校准栅极116、第三端口126以及第四端口136,校准栅极116用于接收控制信号,第三端口126用于接收校准工作电压,第四端口136电连接第二端122;检测晶体管101接收测试信号导通时,校准晶体管106接收控制信号处于截止状态。

在一些实施例中,测试方法还可以包括提供控制信号施加结构124,用于将控制信号施加在校准晶体管106的校准栅极116上。

其中,校准晶体管106与检测晶体管101一样也为PMOS晶体管,检测晶体管101工作于深三极管区时,测试信号为低电平,且控制信号为高电平,使校准晶体管106处于截止状态。测试信号为高电平时,检测晶体管101处于截止状态,且控制信号为低电平,使校准晶体管106工作于深三极管区。

在获取硅穿孔结构102的电阻之后,测试方法还可以包括:获取校准晶体管106的校准本征导电因子,校准本征导电因子为:校准晶体管106工作于饱和区,且校准晶体管106中的电流具有第三电流方向的条件下,载流子迁移率与单位面积栅氧化层的电容的乘积;改变测试信号,使检测晶体管101处于截止状态;同时改变控制信号,使校准晶体管106导通,且向第一端112提供校准测试电压,使校准晶体管106中的电流具有第四电流方向,第三电流方向与第四电流方向相反,以使校准晶体管106工作于深三极管区,并获取校准晶体管106工作于深三极管区期间流经第一端112的校准电流;基于校准本征导电因子、校准工作电压、校准测试电压以及流经第一端112的校准电流,获取硅穿孔结构102的校准电阻。

其中,由于校准晶体管106与检测晶体管101均为PMOS晶体管,则获取校准晶体管106的校准本征导电因子的方法与前述获取检测晶体管101的本征导电因子的方法相同,在此不做赘述。

在一些实施例中,在获取检测晶体管101工作于深三极管区期间流经第二端122的电流之后,撤去机台提供第一探针和第二探针,并通过机台提供第三探针,使第三探针与第一电连接层113接触电连接,用于将校准测试电压施加在第一电连接层113上,从而向第一端112提供校准测试电压;机台还提供第四探针,并使第四探针与第一电连接层113接触电连接,用于获取校准晶体管106工作于深三极管区期间流经探针接触点105的电流,从而获取校准晶体管106工作于深三极管区期间流经第一电连接层113的电流。在其他实施例中,机台提供第三探针,可以使第三探针直接与第一端直接接触,以将校准测试电压施加在第一端;机台还提供第四探针,并使第四探针直接与第一端直接接触,用于获取校准晶体管工作于深三极管区期间流经第一端的电流。

校准晶体管106工作于深三极管区时,校准测试电压大于校准工作电压,第四电流方向为第四端口136指向第三端口126。此外,当半导体结构100处于正常工作模式时,可以使测试信号和控制信号均为高电平,以使得检测晶体管101和校准晶体管106均处于截止状态,从而不会影响半导体结构100的正常工作。

具体可以根据如下关系式计算校准晶体管106的等效电阻:

其中,R′

需要说明的是,校准晶体管106的宽长比W′

其中,校准晶体管106导通时校准栅极116的电压V′

因此,

此外,具体可以根据如下关系式计算所述硅穿孔结构的校准电阻:

其中,R′

在获取硅穿孔结构102的校准电阻之后,比较硅穿孔结构102的电阻R

综上所述,依据代工厂提供的PMOS晶体管的基本性能参数,获取检测晶体管101的本征导电因子;通过调整测试信号以及将测试电压施加在硅穿孔结构102的第二端122,使得检测晶体管101工作于深三极管区,以获取检测晶体管101的等效电阻;获取检测晶体管101工作于深三极管区期间流经第二端122的电流,并基于检测晶体管101的本征导电因子、工作电压、测试电压以及流经第二端122的电流,获取硅穿孔结构102的电阻。将获取的硅穿孔结构102的电阻与理想的硅穿孔结构102的电阻进行比较,从而可以判断出半导体结构100的连接性是否良好,还可以通过判断获取的硅穿孔结构102的电阻与理想的硅穿孔结构102的电阻之间差异的大小,初步推测出半导体结构100中连接性出现问题的原因,从而有针对性的对半导体结构100进行修复。此外,当半导体结构100处于正常工作模式时,可以通过测试信号使得检测晶体管101处于截止状态,从而不会影响半导体结构100的正常工作。

本申请另一实施例还提供一种检测半导体结构连接性的测试系统,用于实现上述的检测半导体结构连接性的测试方法。图3为本申请另一实施例提供的检测半导体结构连接性的测试系统的功能模块示意图。

结合参考图2和图3,检测半导体结构连接性的测试系统109包括:半导体结构100,半导体结构100包括具有相对的第一端112和第二端122的硅穿孔结构102,第一端112与第一芯片110电连接,第二端122与第二芯片电120连接;检测晶体管101,位于第一芯片110中,检测晶体管101包括:检测栅极111、第一端口121以及第二端口131,检测栅极111用于接收测试信号,第一端口121用于接收工作电压,第二端口131电连接第一端112;测试电压施加模块107,在检测晶体管101接收测试信号导通时,给第二端122提供测试电压,使所述检测晶体管工作于深三极管区;电流获取模块117,用于获取所述检测晶体管工作于深三极管区期间流经所述第二端的电流;电阻获取模块127,基于本征导电因子、工作电压、测试电压以及流经第二端122的电流,获取硅穿孔结构102的电阻。

其中,检测晶体管101为PMOS晶体管,第一端口121接收工作电压,检测栅极111接收测试信号,使得检测晶体管101导通,且未给第二端122提供测试电压时,检测晶体管101工作于饱和区,检测晶体管101中的电流具有第一电流方向。测试电压施加模块107用于改变检测晶体管101的工作状态,具体地,测试电压施加模块107给第二端122提供测试电压,使得检测晶体管101中的电流具有第二电流方向,第一电流方向与第二电流方向相反,以使检测晶体管101工作于深三极管区。

在一些实施例中,测试系统109还可以包括:校准晶体管106,位于第二芯片120中,校准晶体管106包括:校准栅极116、第三端口126以及第四端口136,校准栅极116用于接收控制信号,第三端口126用于接收校准工作电压,第四端口136与第二端122电连接,检测晶体管101接收测试信号导通时,校准晶体管106接收控制信号处于截止状态。

测试系统109还可以包括:校准测试电压施加模块108,在检测晶体管101接收测试信号处于截止状态且校准晶体管106接收控制信号导通时,给第一端112提供校准测试电压,使校准晶体管106工作于深三极管区;校准电流获取模块118,用于获取校准晶体管106工作于深三极管区期间流经第一端112的电流;校准电阻获取模块128,基于校准本征导电因子、校准工作电压、校准测试电压以及流经第一端112的电流,获取硅穿孔结构102的校准电阻。其中,校准晶体管106与检测晶体管101一样,均为PMOS晶体管。

其中,第三端口126接收校准工作电压,校准栅极116接收控制信号,使得校准晶体管106导通,且未给第一端112提供校准测试电压时,校准晶体管106工作于饱和区,校准晶体管106中的电流具有第三电流方向。校准测试电压施加模块108用于改变校准晶体管106的工作状态,具体地,校准测试电压施加模块108给第一端112提供校准测试电压,使得校准晶体管106中的电流具有第四电流方向,第四电流方向与第三电流方向相反,以使校准晶体管106工作于深三极管区。

综上所述,通过调整测试信号以及通过测试电压施加模块107在硅穿孔结构102的第二端122施加测试电压,使得检测晶体管101工作于深三极管区;通过电流获取模块117获取检测晶体管101工作于深三极管区期间流经第二端122的电流;通过电阻获取模块127,基于检测晶体管101的本征导电因子、工作电压、测试电压以及流经第二端122的电流,获取硅穿孔结构102的电阻。将获取的硅穿孔结构102的电阻与理想的硅穿孔结构102的电阻进行比较,从而可以判断出半导体结构100的连接性是否良好。此外,可以通过判断获取的硅穿孔结构102的电阻与理想的硅穿孔结构102的电阻之间差异的大小,初步推测出半导体结构100中连接性出现问题的原因,从而有针对性的对半导体结构100进行修复。

本领域的普通技术人员可以理解,上述各实施方式是实现本申请的具体实施例,而在实际应用中,可以在形式上和细节上对其作各种改变,而不偏离本申请的精神和范围。任何本领域技术人员,在不脱离本申请的精神和范围内,均可作各自更动与修改,因此本申请的保护范围应当以权利要求限定的范围为准。

- 半导体测试装置、半导体测试系统以及半导体测试方法

- 半导体结构、测试系统、测试方法及半导体结构的制作方法

- 半导体结构、测试系统、测试方法及半导体结构的制作方法